1.本公开涉及半导体装置以及半导体装置的制造方法。

背景技术:

2.近年来,将多个基板层叠并贴合而成的层叠型的图像传感器等半导体装置在实现高密度化、小型化或薄型化这方面被有效地运用。作为层叠多个基板时的1种技术,贯通电极受到关注。专利文献1所公开的固体拍摄装置(半导体装置)的层叠基板具有将作为下侧基板的逻辑基板和作为上侧基板的像素传感器基板沿着上下方向贴合而成的构造。下侧基板具备作为由硅(si)构成的硅基板的半导体基板和形成在半导体基板的上侧的多层布线层。通过多层布线层构成控制电路、逻辑电路等。通过在半导体基板的给定的位置形成多个贯通孔,在各个贯通孔埋入连接导体,从而形成贯通电极。在下侧基板和上侧基板各自的贴合面形成电极,这些电极相互连接。贯通电极与这些电极电连接。

3.在先技术文献

4.专利文献

5.专利文献1:国际公开第2019/069669号

技术实现要素:

6.本公开的一个实施例涉及的半导体装置具备:第1基板,具有第1端面和与所述第1端面相反侧的第2端面;多个第1电极,设置在所述第1端面;第2电极,设置在所述第2端面,与贴合在所述第2端面的第2基板的电极电连接;内部布线,设置在所述第1基板的内部,与所述第2电极电连接;多个第3电极,设置在所述第1基板的内部,将所述第1电极和所述内部布线电连接;和应变传感器,设置在所述第1基板的内部,测定在所述第1基板内产生的应变,所述第3电极的线膨胀系数大于所述第1基板的线膨胀系数。

7.本公开的一个实施例涉及的半导体装置的制造方法包括:在基材形成第1绝缘层的工序;在该第1绝缘层上形成应变传感器的工序;以覆盖所述应变传感器的方式形成第2绝缘层的工序;在该第2绝缘层形成内部布线的工序;以覆盖该内部布线的方式形成多层内部布线层的工序;在所述基材的与该多层内部布线层侧相反的一侧形成孔的工序;在该孔中以与所述应变传感器相邻的方式形成电极的工序;将外部连接电极与该电极连接的工序,所述外部连接电极将由所述应变传感器检测到的电压传递到外部设备;和以覆盖所述内部布线的方式贴合基板的工序。

附图说明

8.图1是本公开的第1实施方式涉及的半导体装置200的整体剖视图。

9.图2是将图1所示的半导体装置200的主要部分放大的剖视图。

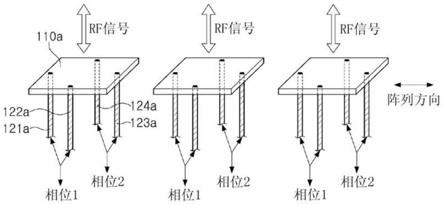

10.图3是示出应变传感器3c、4个贯通电极5a、5b、5c、5d和内部布线2b的配置例的示意图。

11.图4是用于说明应变传感器3c与贯通电极5的位置关系的图。

12.图5是用于说明应变传感器3c与贯通电极5的位置关系的图。

13.图6是用于说明应变传感器3c与贯通电极5的位置关系的图。

14.图7是用于说明本公开的第1实施方式涉及的半导体装置200的制造方法的图。

15.图8是用于说明本公开的第1实施方式涉及的半导体装置200的制造方法的图。

16.图9是用于说明本公开的第1实施方式涉及的半导体装置200的制造方法的图。

17.图10是用于说明本公开的第1实施方式涉及的半导体装置200的制造方法的图。

18.图11是用于说明本公开的第1实施方式涉及的半导体装置200的制造方法的图。

19.图12是用于说明在本公开的第1实施方式涉及的半导体装置200与贴合基板201的贴合面产生剥离的机理的图。

20.图13是用于说明在本公开的第1实施方式涉及的半导体装置200与贴合基板201的贴合面产生剥离的机理的图。

21.图14是示出本公开的第1实施方式涉及的半导体装置200的检查流程的图。

22.图15是示出本公开的应变传感器3c的测定值(应变量)与市场不良(在贴合面产生的应力)的关联例的图。

23.图16是将本公开的第2实施方式涉及的半导体装置200的主要部分放大的剖视图。

24.图17是将本公开的第3实施方式涉及的半导体装置200的主要部分放大的剖视图。

25.图18是将本公开的第4实施方式涉及的半导体装置200的主要部分放大的剖视图。

26.符号说明

27.1:贴合电极(第2电极);

28.2:多层内部布线层(第1基板);

29.2a:绝缘层;

30.2b:内部布线;

31.2c:微过孔;

32.3:应变传感器形成层(第1基板);

33.3a:半导体层;

34.3b:绝缘层;

35.3c:传感器;

36.3d:绝缘膜;

37.4:基材(第1基板);

38.4a:主面;

39.5:贯通电极(第3电极);

40.5a、5b、5c、5d:贯通电极;

41.6:再布线层;

42.6a:绝缘层;

43.6b:再布线;

44.7:外部连接电极(第1电极);

45.8:晶体取向;

46.10:第1端面;

47.11:第2端面;

48.101a:基材;

49.101a1:主面;

50.101b:绝缘层(第1绝缘层);

51.102a:半导体基板;

52.102a1:主面;

53.102b:绝缘层;

54.102c:元件;

55.102d:传感器;

56.102e:半导体层;

57.103a:沟槽;

58.103b:绝缘膜;

59.104:绝缘膜;

60.104a:主面;

61.105a:微过孔图案;

62.105b:微过孔;

63.106:绝缘层(第2绝缘层);

64.107a:内部布线图案;

65.107b:内部布线;

66.108:多层内部布线层;

67.108a:贯通孔;

68.108b:贯通电极;

69.109:应变传感器形成层;

70.110:再布线;

71.111:外部连接电极;

72.131:再布线;

73.200:半导体装置;

74.201:贴合基板(第2基板);

75.203:电极;

76.204:硅基板;

77.210:层叠型半导体装置。

具体实施方式

78.然而,在这种层叠基板中,半导体基板和设置在半导体基板的内部的贯通电极各自的线膨胀系数不同。因此,在向上侧基板贴合下侧基板时加热(一般为350~500℃)然后冷却到常温为止的工序中,应变残留在半导体基板内。因而,在半导体基板和贴合面产生压缩、膨胀等垂直应力。由此,上侧基板以及下侧基板的贴合面中的电连接丧失,可能产生导通不良。因此,在现有技术中,在抑制由半导体基板与贯通电极的线膨胀系数差异引起的故障的产生这方面有改善的余地。

79.本公开的非限定性的实施例有助于提供抑制由半导体基板与贯通电极的线膨胀系数差异引起的故障的产生的半导体装置以及制造方法。

80.本公开的一个实施例涉及的半导体装置具备:第1基板,具有第1端面和与所述第1端面相反侧的第2端面;多个第1电极,设置在所述第1端面;第2电极,设置在所述第2端面,与贴合在所述第2端面的第2基板的电极电连接;内部布线,设置在所述第1基板的内部,与所述第2电极电连接;多个第3电极,设置在所述第1基板的内部,将所述第1电极和所述内部布线电连接;应变传感器,设置在所述第1基板的内部,测定在所述第1基板内产生的应变,所述第3电极的线膨胀系数大于所述第1基板的线膨胀系数。

81.本公开的一个实施例涉及的半导体装置的制造方法包括:在基材形成第1绝缘层的工序;在该第1绝缘层上形成应变传感器的工序;以覆盖所述应变传感器的方式形成第2绝缘层的工序;在该第2绝缘层形成内部布线的工序;以覆盖该内部布线的方式形成多层内部布线层的工序;在所述基材的与该多层内部布线层侧相反的一侧形成孔的工序;在该孔中以与所述应变传感器相邻的方式形成电极的工序;将外部连接电极与该电极连接的工序,所述外部连接电极将由所述应变传感器检测到的电压传递到外部设备;以覆盖所述内部布线的方式贴合基板的工序。

82.根据本公开的一个实施例,能够构建抑制由半导体基板与贯通电极的线膨胀系数差异引起的故障的产生的半导体装置以及制造方法。

83.本公开的一个实施例的进一步的优点以及效果根据说明书以及附图来明确。该优点以及/或效果分别通过若干实施方式和说明书以及附图所记载的特征来提供,但是并不需要全部提供以获得1个或其以上的相同的特征。

84.以下,一边参照附图,一边对本公开的优选的实施方式详细地进行说明。另外,在本说明书以及附图中,对于实质上具有相同的功能的构成要素,通过标注相同的符号来省略重复说明。在以下的图中,分别示出的结构构件的形状、厚度、长度等在附图的制作上与实际的结构构件的形状、厚度、长度等不同。进而,各结构构件的材质不限定于本实施方式所记载的材质。此外,在本公开的实施方式中,设置在半导体装置的贯通电极、再布线、外部连接电极、贴合电极、微过孔、内部布线、绝缘层等的个数还包括与实际的个数不同的情况。

85.在图1之后,x轴方向、y轴方向以及z轴方向分别表示与x轴平行的方向、与y轴平行的方向、与z轴平行的方向。x轴方向和y轴方向相互正交。x轴方向和z轴方向相互正交。y轴方向和z轴方向相互正交。xy平面表示与x轴方向以及y轴方向平行的假想平面。xz平面表示与x轴方向以及z轴方向平行的假想平面。yz平面表示与y轴方向以及z轴方向平行的假想平面。此外,x轴方向之中由箭头示出的方向设为正x轴方向,与该方向相反的方向设为负x轴方向。y轴方向之中由箭头示出的方向设为正y轴方向,与该方向相反的方向设为负y轴方向。z轴方向之中由箭头示出的方向设为正z轴方向,与该方向相反的方向设为负z轴方向。z轴方向例如等于垂直方向、层叠方向或上下方向,x轴方向以及y轴方向例如等于水平方向或左右方向。

86.[第1实施方式]

[0087]

<半导体装置200的结构例>

[0088]

一边参照图1以及图2,一边对本公开的第1实施方式涉及的半导体装置200的结构例进行说明。图1是本公开的第1实施方式涉及的半导体装置200的整体剖视图,图2是将图1

所示的半导体装置200的主要部分放大的剖视图。另外,在图2中,将被由图1的符号a示出的虚线包围的部位放大而进行示出。

[0089]

半导体装置200具备多个贴合电极1、多层内部布线层2、应变传感器形成层3、基材4、多个贯通电极5、再布线层6和多个外部连接电极7。

[0090]

贴合电极1、多层内部布线层2、应变传感器形成层3、基材4、再布线层6以及外部连接电极7以该顺序在负z轴方向上层叠。

[0091]

多个贴合电极1设置在多层内部布线层2的上侧的面(正z轴方向的面)。多个贴合电极1在x轴方向上相互分离地排列。

[0092]

多层内部布线层2具有在上下方向上层叠了多个绝缘层2a的构造。在多层内部布线层2中形成有:设置在相邻的绝缘层2a之间的内部布线2b;和将设置在相邻的绝缘层2a之间的内部布线2b彼此连接的多个微过孔2c。

[0093]

绝缘层2a是在上下方向上将相邻的内部布线2b彼此绝缘,此外将内部布线2b与贴合电极1绝缘,进而将微过孔2c的周围绝缘的绝缘构件。在多个绝缘层2a之中设置在正z轴方向的最外侧的绝缘层2a,形成有多个贴合电极1。

[0094]

关于多个微过孔2c之中位于多层内部布线层2的最下侧的微过孔2c,其一部分设置于半导体层3a。该微过孔2c的下端与贯通电极5的上表面相接。

[0095]

另外,该微过孔2c的形状不限定于图示例。例如,该微过孔2c也可以是其下端以贯通应变传感器形成层3的方式延伸且与贯通电极5连接的形状。

[0096]

绝缘层2a例如由氧化硅膜(sio2)、氮化硅膜(sin)、氮氧化硅膜(sion)等形成。内部布线2b、微过孔2c以及贴合电极1例如使用铜(cu)、铝(al)、钨(w)、金(au)等形成。另外,贴合电极1、内部布线2b、微过孔2c以及绝缘层2a各自既可以由相同的材料形成,也可以根据多个绝缘层2a的位置而由不同的材料形成。

[0097]

应变传感器形成层3具备半导体层3a、2个绝缘层3b、应变传感器3c以及绝缘膜3d。应变传感器形成层3是通过这些构成要素作为整体而形成应变传感器部的层。

[0098]

半导体层3a由锗、单晶硅、多晶硅、非晶硅、碳化硅等形成。

[0099]

2个绝缘层3b既可以由相互相同的材料形成,也可以由不同的材料形成。2个绝缘层3b之中的应变传感器3c的上侧的绝缘层3b是将构成多层内部布线层2的绝缘层2a与应变传感器3c之间绝缘的绝缘构件。2个绝缘层3b之中的应变传感器3c的下侧的绝缘层是将后述的绝缘层101b与应变传感器3c之间绝缘的绝缘构件。另外,在半导体层3a,不仅可以形成应变传感器3c,还可以形成应变传感器3c以外的电路例如晶体管。

[0100]

应变传感器3c通过在半导体层3a的由绝缘膜3d隔离的一部分中扩散硼、磷等杂质而形成。应变传感器3c例如与贯通电极5相邻地设置。应变传感器3c的位置既可以是与贯通电极5的上端面相向的位置,也可以是与贯通电极5的侧面相向的位置。贯通电极5的上端面是贯通电极5的正z轴方向的端面。贯通电极5的侧面是贯通电极5的外周面之中与xy平面正交的面。应变传感器3c以及贯通电极5的详细情况在后面描述。

[0101]

绝缘膜3d是将应变传感器3c与半导体层3a之间绝缘的绝缘构件。绝缘膜3d例如由氧化硅膜(sio2)、氮化硅膜(sin)、氮氧化硅膜(sion)等形成。

[0102]

基材4与绝缘层3b的负z轴方向的端面对置地设置。基材4例如由硅(si)、玻璃、聚酰亚胺膜、pet膜等形成。在基材4的主面4a(基材4的表面)形成有应变传感器形成层3。

[0103]

多个贯通电极5在上下方向上贯通多个绝缘层3b和基材4,在x轴方向上相互分离地排列。在图2的左侧示出的贯通电极5的上端与应变传感器3c连接。在图2的右侧示出的贯通电极5的上端与微过孔2c连接,经由微过孔2c与内部布线2b电连接。

[0104]

另外,贯通电极5也可以经由微过孔2c、内部布线2b等与应变传感器3c电连接。此外,在图2中,贯通电极5在上下方向上贯通多个绝缘层3b和基材4,但贯通电极5例如也可以设置为贯通多个绝缘层3b、基材4、半导体层3a以及绝缘层2a。

[0105]

贯通电极5例如具备将金属形成为筒状的导电体、和形成在该导电体的周围的绝缘膜。绝缘膜具有防止在基材4与半导体层3a之间产生的漏电的功能。另外,例如也可以通过在该导电体的一部分埋入树脂等有机物、或在该导电体的周围设置空隙,从而在保证绝缘的同时降低该导电体的使用量。由此,该导电体的使用量减少,能够削减半导体装置200的制造成本。

[0106]

在贯通电极5连接再布线6b。再布线6b是形成在基材4的背面(基材4的与主面4a侧相反侧的面)的导电性的电极,与外部连接电极7连接。贯通电极5以及再布线6b例如能够由铜(cu)、钨(w)、钛(ti)、钽(ta)、钛钨合金(tiw)、多晶硅等形成。再布线6b由绝缘层6a绝缘。

[0107]

外部连接电极7例如是焊料球、在表面形成有导电性覆膜的树脂球、通过引线键合而形成的凸块等。在外部连接电极7是焊料球的情况下,在外部连接电极7中,能够使用sn

‑

ag

‑

cu系、sn

‑

ag

‑

bi系等各种组成的焊料。在外部连接电极7是通过引线键合而形成的凸块的情况下,在外部连接电极7中,能够使用金(au)、铜(cu)等。

[0108]

另外,在贯通电极5以及外部连接电极7中包括2种用途的电极。一种是经由微过孔2c与贴合电极1电连接的电极,另一种是与应变传感器3c电连接的电极。前者是通常的产品的动作用的电极,后者是利用应变传感器3c的应变测定用的电极。这样,通过使用用途不同的两种电极,能够使应变传感器3c从作为通常的产品而实现功能的电路(产品电路)中独立出来。

[0109]

这样,通过使应变传感器3c的功能从产品电路的功能中独立出来,能够防止应变传感器3c的测定对产品的特性产生影响。进而,能够防止在该产品电路中产生的噪声进入应变传感器3c的测定值。产品电路例如是搭载于汽车、家电、fa设备等的电路。

[0110]

应变传感器3c经由贯通电极5以及再布线6b(根据情况有时还包括内部布线2b以及微过孔2c)而与外部连接电极7连接,进而通过与外部连接电极7连接的布线而与未图示的外部的设备电连接。

[0111]

通过这样的连接,与一般的布线方法也就是将布线与基材4的主面4a连接的方法相比,能够缩短到外部的设备为止的电布线长度。这样,通过电布线长度变短,噪声不易叠加于在布线路径中传递的应变传感器3c的测定值,应变测定的精度提高。

[0112]

此外,不需要在基材4的主面4a设置用于获取应变传感器3c的测定值的内部布线,进而,不需要用于设置与该内部布线连接的测定焊盘的多余的空间。因而,能够实现半导体装置200的小型化。

[0113]

在此,在构成半导体装置200的构件之中,贯通电极5的线膨胀系数比较高,并且占据比较大的体积。因而,关于贯通电极5的热膨胀收缩,在构成半导体装置200的构件之中,贯通电极5的热膨胀收缩最大。线膨胀系数表示物体的长度、体积等由于温度上升而膨胀的比例。通过将应变传感器3c设置为与这样的贯通电极5相邻,能够高精度地测定由于热的变

化而在半导体装置200内产生的应变,从而市场不良(在市场上发现的不良)的估计精度提高。详细情况在后面描述。

[0114]

<应变传感器3c的结构>

[0115]

应变传感器3c是通过在半导体层3a中扩散硼、磷等杂质而形成的半导体计量器。应变传感器3c具有厚度非常薄的构造,例如,应变传感器3c的垂直方向的尺寸(厚度)为10~500[nm],应变传感器3c的平面方向(水平方向)的尺寸为10~900[um]。垂直方向等于层叠第1基板和第2基板的层叠方向。第1基板可以由本实施方式的多层内部布线层2、108、应变传感器形成层3、109以及基材4构成。第2基板可以由本实施方式的贴合基板201构成。

[0116]

如果由于向供给了一定的电流的应变传感器3c施加外部应力而应变传感器3c发生应变,则由应变传感器3c检测到的电压值变化。利用该电压值的变化量,并基于电阻变化率以及应变率(gauge rate)来计算应变。即,对于应变计算,利用在向计量器施加机械应变时其电阻变化的压电电阻效应。

[0117]

参照图3,对具体的电流供给的方法、电位测定的方法进行说明。图3是示出应变传感器3c、4个贯通电极5a、5b、5c、5d和内部布线2b的配置例的示意图。

[0118]

4个贯通电极5a、5b、5c、5d分别与图1以及图2所示的多个贯通电极5之中配置为包围应变传感器3c的4个贯通电极5对应。由于这些贯通电极5a、5b、5c、5d与外部连接电极7连接,因而在各工序中,能够流动从外部连接电极7的外部供给的电流,此外被施加在应变传感器3c中产生的电压。

[0119]

在应变传感器3c中,例如能够通过4端子法来测定应变。4端子法是例如在a、b、c以及d这4根电极之中的2根电极ad间流动一定的电流,并测定在其余2根电极bc间产生的电压的电位差,从而求得电阻的方法。具体地,经由微过孔2c以及内部布线2b而间接地(根据情况有时不经由它们而直接地)从2个贯通电极5a、5d对应变传感器3c流动电流,此时检测在2个贯通电极5b、5c之间产生的电位差,由此进行使用应变传感器3c的应变测定。

[0120]

另外,关于由应变传感器3c测定的应变,除4端子法以外还能够使用2端子法。2端子法例如是在应变传感器3c的两端设置2个电极端子,通过2个电极端子来测定流经应变传感器3c的电流和此时产生的电位差的方法,与4端子法相比,具有装置的制作简便且能够容易地测定电位差这样的优点。

[0121]

不过,已知2端子法与4端子法相比,容易受到与外部连接电极7连接的未图示的布线(敷设在半导体装置200的外部的金属的线缆等)的布线电阻、接触电阻等的影响。因而,容易在应变测定值中产生偏差。通过利用4端子法,能够不受该布线的布线电阻、接触电阻等的影响而高精度地测定应变。因而,在应变传感器3c中,优选使用4端子法。

[0122]

另外,应变传感器3c不限定于前述的半导体型(半导体计量器),也可以是金属型。金属型的应变传感器3c一般由cu

‑

ni系合金、ni

‑

cr系合金形成,为了提高灵敏度,也可以由铂金属、镍形成。

[0123]

不过,半导体型的应变传感器3c的测定灵敏度与金属型的应变传感器3c的测定灵敏度相比优异数十倍,因而能够通过采用半导体型的应变传感器3c来测定精细的应变。

[0124]

此外,半导体型的应变传感器3c能够根据扩散的杂质的种类而分类为p型半导体(扩散硼等)、n型半导体(扩散磷等)等。p型半导体的应变传感器3c能够测定水平方向(x轴或y轴方向)的应变。n型半导体的应变传感器3c能够测定垂直方向的应变。通过使用n型半

导体的应变传感器3c,能够测定由贯通电极5的热膨胀收缩导致的半导体装置200内部的垂直方向的应变。

[0125]

此外,能够通过在形成应变传感器3c的半导体层3a中取代锗、多晶硅、非晶硅、碳化硅等而使用单晶硅来进一步提高应变的测定灵敏度。此外,由此,能够抑制半导体层3a的形成所需要的材料成本的上升。

[0126]

接下来,参照图4~图6,对应变传感器3c与贯通电极5的位置关系、应变传感器3c的水平方向的形状、应变传感器3c与半导体层3a的晶体取向8的关系等进行说明。图4~图6是用于说明应变传感器3c与贯通电极5的位置关系的图。

[0127]

沿着垂直方向俯视观察应变传感器3c的形状例如是长方形。在长方形的应变传感器3c中,例如在应变传感器3c的2个短边部进行电流的供给,并且测定在该2个短边部产生的电压的电位差。

[0128]

长方形的应变传感器3c例如如图4所示,在半导体层3a形成为沿着形成应变传感器3c的半导体层3a的晶体取向8[010]而延伸。即,应变传感器3c配置为:应变传感器3c的长边部与半导体层3a的晶体取向平行。

[0129]

进而,应变传感器3c配置在4个贯通电极5之中设置于靠基材4的负y轴方向的2个贯通电极5之间,并且配置在这2个贯通电极5之中靠负x轴方向的贯通电极5的附近。

[0130]

通过这样配置应变传感器3c,例如针对n型半导体的应变传感器3c,与晶体取向8平行地供给电流,通过测定此时检测到的电位差,水平方向的应变的影响被极小化,能够进一步高灵敏度地测定垂直方向的应变。

[0131]

这样,通过将应变传感器3c形成为长边部与4个贯通电极5之中的1个贯通电极5对置,能够进一步高灵敏度地测定产生由贯通电极5的热膨胀收缩引起的应变的部位的应变。

[0132]

另外,如果短边部变长,则应变传感器3c与未产生应变的部位(例如基材4之中被4个贯通电极5包围的区域的中心部)的接触面积变大。由此,即使产生贯通电极5的膨胀和收缩,相对地,应变传感器3c的每单位面积的应变量变小,电阻值的变化率也变小,因而应变的测定灵敏度也会下降。因此,在将应变传感器3c的形状设定为长方形的情况下,短边部的长度优选构成为尽量短。

[0133]

另外,俯视观察应变传感器3c的形状不限定于长方形,只要是能够应用前述的4端子法的形状、即能够向应变传感器3c供给电流且能够测定在应变传感器3c产生的电压的电位差的形状即可,也可以是长方形以外的形状。关于长方形以外的形状,例如能够例示正方形、椭圆形、环状(圆环形状)、缺少环状的一部分的c字形状等。不过,在半导体型的应变传感器3c中,通过在与形成应变传感器3c的半导体层的晶体取向8平行的方向上供给电流,能够获得期望的应变特性。因而,例如,在使用上述的圆环形状、c字形状等半导体型的应变传感器3c的情况下,不能在与该晶体取向8平行的方向上供给电流,难以测定期望的应变量。因此,半导体型的应变传感器3c的形状优选设为长方形。

[0134]

另外,应变传感器3c也可以如图5以及图6所示那样配置。图5所示的应变传感器3c以沿着晶体取向8[100]延伸的方式配置在半导体装置200。图6所示的应变传感器3c以沿着晶体取向8[110]延伸的方式配置在半导体装置200。

[0135]

<半导体装置200的制造方法例>

[0136]

接下来,参照图7~图11,对第1实施方式涉及的半导体装置200的制造方法进行说

明。图7~图11是用于说明本公开的第1实施方式涉及的半导体装置200的制造方法的图。另外,在图7~图11中,将被由图1的符号a示出的虚线包围的部位放大而示出。

[0137]

如图7的从上方起第1个图所示,在基材101a的主面101a1形成绝缘层101b,进而,在半导体基板102a的主面102a1形成绝缘层102b。绝缘层101b以及绝缘层102b既可以形成在基材101a以及半导体基板102a这两者,也可以形成在任一者。关于绝缘层101b以及绝缘层102b的形成方法,在氧化硅膜(sio2)的情况下,能够例示热氧化、cvd(chemical vapor deposition,化学气相沉积)法、溅射法等。

[0138]

如图7的从上方起第2个图所示,在通过硫酸过氧化氢混合液等对将基材101a和半导体基板102a贴合的面进行亲水化处理之后,将半导体基板102a的绝缘层102b与基材101a的绝缘层101b贴合。在贴合的工艺中,有热处理的方法、表面活性化法等。在表面活性化法中,通过在真空中利用氩的离子束来对贴合的面进行溅射,从而使其活性化,在真空中,半导体基板102a的绝缘层102b被贴合在基材101a的绝缘层101b。

[0139]

如图7的从上方起第3个图所示,通过利用cmp(chemical mechanical polishing,化学机械抛光)等工艺来对半导体基板102a的背面(半导体基板102a的与绝缘层102b侧相反侧的面)进行研磨以及薄膜化,从而形成半导体层102e。

[0140]

如图7的从上方起第4个图所示,以抗蚀图案为掩模,对半导体层102e进行蚀刻,挖出沟槽(浅槽)103a,由此在半导体层102e上,使成为应变传感器3c的元件102c独立出来。之后,清洗抗蚀图案而将其除去。

[0141]

如图8的从上方起第1个图所示,使用cvd法等,在半导体层102e的背面(半导体层102e的与绝缘层102b侧相反侧的面)形成绝缘层,使得在沟槽103a中埋入绝缘材料。

[0142]

之后,通过cmp等除去形成在半导体层102e的背面(半导体层102e的与绝缘层102b侧相反侧的面)的该绝缘层,由此在沟槽103a保留绝缘材料。通过该绝缘材料,形成埋入于沟槽103a的绝缘膜103b。通过绝缘膜103b,元件102c成为与形成在元件102c的水平方向的周围的半导体层102e绝缘的状态。

[0143]

如图8的从上方起第2个图所示,以抗蚀图案为掩模,在元件102c中扩散硼、磷等杂顾,由此形成应变传感器102d。另外,也可以在形成应变传感器102d的半导体层102e形成作为产品而实现功能的晶体管(前述的产品电路)。晶体管是在半导体层102e形成的应变传感器以外的电路的一个例子。

[0144]

通过在半导体层102e形成该晶体管,能够在1个半导体层102e设置应变传感器102d以及该晶体管,因而不需要为了该晶体管的形成而设置与半导体层102e不同的半导体层。因此,能够削减半导体层102e的数量,并且不需要追加的贴合的工序,能够削减半导体装置200的材料费和组装工时。

[0145]

如图8的从上方起第3个图所示,使用cvd法等,在半导体层102e的背面(半导体层102e的与绝缘层102b侧相反侧的面)形成绝缘膜104。由此,应变传感器形成层109完成。

[0146]

如图8的从上方起第4个图所示,形成微过孔抗蚀图案,并以微过孔抗蚀图案为掩模来进行蚀刻处理,在绝缘膜104形成微过孔图案105a。之后,清洗微过孔抗蚀图案而将其除去。

[0147]

如图9的从上方起第1个图所示,使用cvd法等,在绝缘膜104的主面104a(绝缘膜104的与半导体层102e侧相反侧的面)形成利用微过孔的材料的层,使得填充微过孔图案

105a。

[0148]

之后,通过使用cmp等除去该层,从而在微过孔图案105a中保留微过孔的材料。通过该材料,形成埋入于微过孔图案105a的微过孔105b。

[0149]

如图9的从上方起第2个图所示,使用cvd法等在绝缘膜104的主面104a形成绝缘层106。

[0150]

如图9的从上方起第3个图所示,形成未图示的内部布线抗蚀图案,并以该内部布线抗蚀图案为掩模来进行蚀刻处理,在绝缘层106形成内部布线图案107a。之后,通过清洗将该内部布线抗蚀图案除去。

[0151]

如图9的从上方起第4个图所示,使用cvd法等,在绝缘层106的表面(绝缘层106的与绝缘膜104侧相反侧的面)形成利用内部布线的材料的层,使得填充内部布线图案107a。

[0152]

之后,通过使用cmp等除去该层,从而在内部布线图案107a保留内部布线的材料。通过该材料,形成埋入于内部布线图案107a的内部布线107b。

[0153]

之后,通过反复执行图8的从上方起第4个图所示的工序到图9的从上方起第4个图所示的工序,从而如图10的从上方起第1个图所示,在应变传感器形成层109的上侧形成多层内部布线层108。在多层内部布线层108形成多个内部布线107b。该工序(内部布线工序)的反复执行次数一般为10次程度,但根据需要也可以是1~20中的任一者。

[0154]

如图10的从上方起第2个图所示,使用反复执行利用聚合物的侧壁的覆盖和各向异性等离子体蚀刻的bosch工艺等,在基材101a的给定的位置形成多个贯通孔108a。贯通孔108a形成为不仅贯通基材101a,还贯通由多个异种材料构成的绝缘层101b、绝缘层102b等层。之后,通过清洗将侧壁的覆盖中使用的聚合物除去。

[0155]

另外,在将贯通电极108b和内部布线107b电连接的情况下,贯通孔108a还进一步形成为贯通半导体层102e、绝缘膜104以及绝缘层106。

[0156]

另外,在bosch工艺中,通过一边将各向异性等离子体蚀刻中使用的气体的种类改变为能够选择性地对要蚀刻的层的材料进行蚀刻的气体一边进行该工艺,从而能够在各个材料不同的多个层形成贯通孔108a。

[0157]

如图10的从上方起第3个图所示,使用cvd法等,在基材101a的背面(基材101a的与主面101a1相反侧的面101a2)形成贯通电极的材料的层,使得向贯通孔108a埋入贯通电极的材料。

[0158]

之后,通过利用cmp等除去形成在基材101a的背面的该层,从而在贯通孔108a保留贯通电极的材料。通过该贯通电极的材料,形成埋入于贯通孔108a的贯通电极108b。

[0159]

另外,也可以在形成贯通电极108b之前,在形成贯通孔108a的壁面(内周面)使用cvd法等来形成绝缘膜。由此,能够防止从贯通电极108b相对于基材101a的漏电。

[0160]

此外,贯通电极108b不需要形成为填充贯通孔108a的全部。例如,也可以通过在贯通孔108a的底部和该底部的周围的侧面呈膜状地形成贯通电极材料,从而设置贯通电极108b。在该情况下,也可以在贯通孔108a的内部空间之中未设置贯通电极材料的部分埋入绝缘性的树脂等。由此,能够削减贯通电极108b的材料的使用量。

[0161]

如图11的从上方起第1个图所示,在贯通电极108b的背面(贯通电极108b的与半导体层102e侧相反侧的面)形成再布线110。再布线110是将贯通电极108b和后述的外部连接电极111电连接的导电性构件。再布线110通过电解镀覆工艺、无电解镀覆工艺等来形成。

[0162]

此外,在基材101a的与主面101a1侧相反侧的面101a2形成绝缘层,使得形成外部连接电极111的给定的位置被开口。绝缘层通过旋涂工艺、狭缝涂敷工艺等来形成。

[0163]

如图11的从上方起第2个图所示,在再布线110的表面之中未被绝缘层覆盖的部分,形成外部连接电极111。外部连接电极111的材料是焊料球、导电性树脂球、柱形凸块等。

[0164]

在使用焊料球、导电性树脂球的情况下,再布线110向外部连接电极111的连接可以是焊接和利用导电性粘接剂的粘接中的任一者。此外,也可以取代焊料球、导电性树脂球等,例如使用丝网印刷法将焊料膏供给到再布线131上,通过对该焊料膏进行回流焊,从而形成外部连接电极111。

[0165]

在使用金(au)、铜(cu)等柱形凸块的情况下,使用金(au)、铜(cu)等细线线材(例如)、引线键合装置等形成外部连接电极111。

[0166]

<基于应变传感器3c的应变测定动作和作用>

[0167]

接下来,参照图12以及图13,对基于应变传感器3c的应变测定动作进行说明。图12以及图13是用于说明在本公开的第1实施方式涉及的半导体装置200和贴合基板201的贴合面产生剥离的机理的图。

[0168]

如图12的从上方起第1个图所示,准备与半导体装置200对置地贴合在半导体装置200的贴合基板201。贴合基板201具备硅基板204、设置在硅基板204的半导体装置200侧的面的铜(cu)电极203、和设置在该面的氧化硅膜(sio2)202。

[0169]

另外,贴合基板201的结构例只要是能够将半导体装置200贴合的基板即可,不限定于图示例。

[0170]

在构成这样贴合的半导体装置200和贴合基板201的多个构件之中,基于热膨胀收缩的内部应变量特别大的构件是厚度较大且线膨胀系数较大的贯通电极5。例如,多层内部布线层2以及应变传感器形成层3各自的厚度为数[μm]以下,相对于此,基材4以及贯通电极5各自的厚度为数十[μm]至数百[μm],非常大。

[0171]

在基材4由刚性较高的硅形成的情况下,硅的线膨胀系数例如是3.9

×

10

‑6,不易在基材4产生应变。相对于此,贯通电极5是金属的导电体,在该导电体例如是铜(cu)的情况下,铜(cu)的线膨胀系数为14.3

×

10

‑6,容易在贯通电极5产生应变。

[0172]

如图12的从上方起第2个图所示,使贴合电极1和铜(cu)电极203对置,并且使绝缘层2a和氧化硅膜(sio2)202对置,这样使它们相互接触。进而,使贴合电极1和铜(cu)电极203金属接合,并且使绝缘层2a和氧化硅膜(sio2)202共价结合。

[0173]

此时,为了使贴合电极1和铜(cu)电极203金属接合,需要施加载荷和高温。所谓高温,例如是350~500℃的较高的温度。另外,在未进行贴合面的活性化处理的情况下,为了金属接合而需要的温度为700~900℃。

[0174]

这样,由于在金属接合中施加较高的温度,因而在半导体装置200以及贴合基板201的内部产生由各结构构件各自的热膨胀导致的内部应变。具体地,在内部应变较大的贯通电极5产生由加热导致的膨胀方向的内部应变l1a。在内部应变较小的基材4产生由加热导致的膨胀方向的内部应变l2a。此外,在贴合基板201产生由加热导致的膨胀方向的内部应变l3a。

[0175]

另外,铜(cu)电极203和贴合电极1以在铜(cu)电极203与贴合电极1的界面产生了内部应变的状态接合,因而在金属接合时未产生应力。关于该应力的详细情况在后面描述。

[0176]

此外,利用加热的贴合时间一般为15~60分钟程度,在该贴合时间内,各结构构件充分地热膨胀。通过贴合而形成层叠型半导体装置210。

[0177]

在完成了利用载荷和加热的金属接合后,将层叠型半导体装置210冷却到成为常温为止。此时,如图13的从上方起第1个图所示,在层叠型半导体装置210的内部产生由冷却导致的热收缩。具体地,在贴合基板201产生由冷却导致的收缩方向的内部应变l3b。在基材4产生由冷却导致的收缩方向的内部应变l2b。由于基材4和贴合基板201各自的热膨胀较小,因而内部应变l3b以及内部应变l2b成为较小的值。

[0178]

在贯通电极5产生由冷却导致的收缩方向的内部应变l1b。内部应变l1b与由加热导致的膨胀方向的内部应变l1a相比,成为较小的值。这是因为,尽管贯通电极5的热膨胀较大,但由于半导体装置200和贴合基板201的贴合,从而绝缘层2a相对于上下方向的位置被固定,位于绝缘层2a的下侧的贯通电极5不能充分地收缩。

[0179]

这样,在贯通电极5不能充分地收缩的情况下,由于在贯通电极5中残留的要收缩的力,从而在半导体装置200中产生要将半导体装置200与贴合基板201的贴合面剥离的朝下的应力f1b。

[0180]

另一方面,在贴合基板201,存在刚性较高的硅基板204的反作用力,产生朝上的应力f2b。

[0181]

要将贴合面剥离的应力f1b以及应力f2b的大小小于贴合面的金属接合和共价结合的力时,在贴合的工序内不产生贴合面的剥离,因而可实现半导体装置200和贴合基板201的导通。因而,通过检查工序的电气检查而被出货到市场中。之后,经过在顾客处的2次安装等工序而被出货到市场中。

[0182]

在市场中,例如由于对具备层叠型半导体装置210的装置的振动、具备层叠型半导体装置210的装置的掉落等,从而如图13的从上方起第2个图所示,在层叠型半导体装置210产生机械性应力f3。此时,在层叠型半导体装置210的贴合面中,机械性应力f3与在贴合的工序内产生的应力f1b以及应力f2b合成,因而产生将机械性应力f3与应力f1b以及应力f2b合成了的应力f1c以及应力f2c。

[0183]

在贴合的工序内产生的应力f1b以及应力f2b由于贴合工艺条件的偏差、材料物性偏差等而变得大于设计时的情况下,该应力f1c以及应力f2c大于金属接合和共价接合的力。由此,在贴合面产生剥离,半导体装置200和贴合基板201的导通丧失,成为市场不良。

[0184]

为了抑制这样的市场不良的发生,可以采取如以下那样的措施。该措施例如是:在贴合的工序内检查在贴合面产生的应力f1b以及应力f2b,检查的结果是估计会成为市场不良的产品作为工序内不良而不进行出货;在贴合工艺内一边进行监测一边反馈到贴合工艺条件中等。通过这样的措施,将应力f1b以及应力f2b降低到标准内对于市场不良的产生的抑制是有效的。

[0185]

通过上述的剥离产生的机理可知,贯通电极5的内部应变对在贴合面产生的应力有较大影响。因此,通过将应变传感器3c设置为与内部应变较大的贯通电极5相邻,从而能够测定贯通电极5的内部应变。于是,能够获得应变传感器3c的测定值(贯通电极5的内部应变量)、以及欲将贴合面剥离的应力(朝下的应力f1b和朝上的应力f2b)等数据。通过从市场不良品获得这些数据,并事先通过数据库进行关联,能够实现内部应力的工序内检查以及监测。

[0186]

另外,应变传感器3c是通过在半导体层3a中扩散硼、磷等杂质而形成的半导体计量器。在向应变传感器3c供给一定电流时,外部应力被施加,应变传感器3c自身发生应变,从而检测到的电压变化,因此能够基于电压的变化量、电阻变化率以及应变率来计算应变。即,应变计算利用了在向计量器施加机械性的应变时其电阻变化的压电电阻效应。

[0187]

<基于应变传感器3c的效果>

[0188]

图14是示出本公开的第1实施方式涉及的半导体装置200的检查流程的图。图15是示出本公开的应变传感器3c的测定值(应变量)和市场不良(在贴合面产生的应力)的关联例的图。

[0189]

如图14所示,在半导体装置200的检查工序中,在自以往实施的步骤s1的外观检查、步骤s2的x射线检查以及步骤s3的电气检查中追加了步骤s4的应变检查工序。

[0190]

在应变检查工序中,通过利用外部设备来测定在层叠型半导体装置210的内部产生的残留应力,从而如图15所示,能够检测可能产生后发性的导通不良等的产品。

[0191]

此外,除上述的市场中的机械性应力以外,在由于顾客处的2次安装工序中的热应力、机械性应力被合成而产生层叠型半导体装置210的贴合面的剥离的情况下,也能够通过进行同样的应变检查工序来事先检测后发性的导通不良。

[0192]

此外,在贯通电极5的内部应变、顾客工序和市场中产生的多个应力(热应力、机械性应力等)被合成而导致的后发性的不良模式中,能够例示如以下那样的不良模式。例如,在多层内部布线层2中的绝缘层2a中产生裂纹,不能进行内部布线2b与微过孔2c之间的绝缘从而漏电的导通不良;在内部布线2b以及微过孔2c产生裂纹,从而丧失电连接的导通不良等。对于这些不良模式,也能够通过进行同样的应变检查工序来事先检测后发性的导通不良。

[0193]

[第2实施方式]

[0194]

接下来,参照图16,对本公开的第2实施方式涉及的半导体装置200的结构例进行说明。图16是将本公开的第2实施方式涉及的半导体装置200的主要部分放大的剖视图。放大位置与被由图1的符号a示出的虚线包围的部位相同。以下,对与第1实施方式相同的部分标注相同的符号,并省略其说明,对不同的部分进行描述。

[0195]

为了提高半导体装置200的内部应变的测定精度,优选将应变传感器3c设置在应变较大的部分。第2实施方式涉及的半导体装置200,具备被设置为与作为应变较大的部分的贯通电极5的侧面相邻的应变传感器3c。该应变传感器3c优选与贯通电极5直接电连接。

[0196]

通过该结构,应变传感器3c不经由绝缘膜3d而与贯通电极5连接,因而能够不受贯通电极5以外的结构构件的应变影响地直接测定贯通电极5的应变。其结果是,能够进一步高精度地测定半导体装置200内部的应变。

[0197]

[第3实施方式]

[0198]

接下来,参照图17,对本公开的第3实施方式涉及的半导体装置200的结构例进行说明。图17是将本公开的第3实施方式涉及的半导体装置200的主要部分放大的剖视图。放大位置与被由图1的符号a示出的虚线包围的部位相同。以下,对与第2实施方式相同的部分标注相同的符号,并省略其说明,对不同的部分进行描述。

[0199]

在第3实施方式涉及的半导体装置200中,应变传感器3c经由微过孔2c以及内部布线2b而与贯通电极5电连接。微过孔2c以及内部布线2b在垂直方向上排列且相互连接。

[0200]

用于将应变传感器3c与贯通电极5电连接的该微过孔2c以及内部布线2b设置在应变传感器3c的上侧。此外,该内部布线2b设置在贯通电极5的上侧。通过该结构,在贯通电极5的垂直方向上产生了由热膨胀导致的应变的情况下,微过孔2c和内部布线2b与贯通电极5一起在垂直方向上发生应变,该应变被传递到应变传感器3c,由此能够通过应变传感器3c来测定贯通电极5的应变。

[0201]

此外,在第3实施方式涉及的半导体装置200中,应变传感器3c不与贯通电极5直接电连接,因而即使在产生了由贯通电极5的垂直方向的热膨胀导致的应变的情况下,应变传感器3c与内部布线2b的接触面积也不易变化,此外内部布线2b与贯通电极5的接触面积也不易变化。因而,即使在贯通电极5在垂直方向上热膨胀了的情况下,在应变传感器3c与贯通电极5之间相互的接触面积也不会变化,并且由于接触面积不变化,从而应变传感器3c与贯通电极5之间的接触电阻也不会变化。由此,能够防止由接触电阻的变化引起的应变传感器3c的测定值的误差增加。

[0202]

此外,应变传感器3c和贯通电极5也可以隔着绝缘膜3d和半导体层3a的一部分而相邻地配置。不过,为了更高精度地测定贯通电极5的应变,优选缩短应变传感器3c与贯通电极5间的距离。因而,优选不包括半导体层3a的一部分而仅隔着绝缘膜3d将应变传感器3c配置为与贯通电极5相邻。

[0203]

[第4实施方式]

[0204]

接下来,参照图18,对本公开的第4实施方式涉及的半导体装置200的结构例进行说明。图18是将本公开的第4实施方式涉及的半导体装置200的主要部分放大的剖视图。放大位置与被由图1的符号a示出的虚线包围的部位相同。以下,对与第3实施方式相同的部分标注相同的符号,并省略其说明,对不同的部分进行描述。

[0205]

在前述的图12等所示的贴合基板201与半导体装置200的贴合面中,若在铜(cu)电极203与贴合电极1之间产生剥离,则可能成为市场不良(导通不良)。为了估计这样的市场不良,例如在图1所示的多个贴合电极1之中,优选测定容易产生与铜(cu)电极203的剥离的贴合电极1对应的贯通电极5的应变。

[0206]

从这样的观点出发,第4实施方式涉及的半导体装置200的应变传感器3c与容易产生与铜(cu)电极203的剥离的贴合电极1所对应的贯通电极5相邻地配置。

[0207]

例如,如图18所示,在沿着贯通电极5的垂直方向延长了的假想区域b中包括贴合电极1的至少一部分的情况下,该贴合电极1被认为是配置在容易由于该贯通电极5的热膨胀收缩而产生剥离的部位的电极。这样,通过将应变传感器3c设置到在多个贴合电极1中也特别容易产生剥离的贴合电极1所对应的贯通电极5的附近,能够容易地估计市场不良。

[0208]

另外,在多个贴合电极1各自的至少一部分被配置在沿着贯通电极5的垂直方向延长了的假想区域b的情况下,能够估计在与多个贴合电极1对应的贴合面产生的剥离,因而能够进一步容易地估计市场不良。

[0209]

如以上说明的那样,本公开的半导体装置200具备:第1基板,具有第1端面和与所述第1端面相反侧的第2端面;多个第1电极,设置在所述第1端面;第2电极,设置在所述第2端面,与贴合在所述第2端面的第2基板的电极电连接;内部布线,设置在所述第1基板的内部,与所述第2电极电连接;多个第3电极,设置在所述第1基板的内部,将所述第1电极和所述内部布线电连接;和应变传感器,设置在所述第1基板的内部,测定在所述第1基板内产生

的应变,所述第3电极的线膨胀系数大于所述第1基板的线膨胀系数。第1基板可以由本实施方式的多层内部布线层2、108、应变传感器形成层3、109以及基材4构成。第2基板可以由本实施方式的贴合基板201构成。第3电极可以由本实施方式的贯通电极5构成。

[0210]

通过该结构,能够测定在加工中的器件产生的应变、残留在加工后的器件中的残留应变。因此,能够在出货前检测出无法通过出货前检查中的电气检查、x射线检查检测出的、被预测在之后的工序中成为不良品的潜在产品。

[0211]

此外,即使在高密度化、小型化进一步发展的半导体装置200中,也能够提前检测出难以通过电气检查、x射线检查检测出的在2次安装工序、市场中产生的后发不良。

[0212]

本公开的半导体装置200的制造方法包括:在基材101a形成绝缘层101b的工序;在该绝缘层101b上形成应变传感器102d的工序;以覆盖所述应变传感器102d的方式形成绝缘层106的工序;在该绝缘层106形成内部布线107b的工序;以覆盖该内部布线107b的方式形成多层内部布线层108的工序;在所述基材101a的与该多层内部布线层108侧相反的一侧形成贯通孔108a的工序;在该贯通孔108a中以与所述应变传感器102d相邻的方式形成贯通电极108b的工序;将外部连接电极111与该贯通电极108b连接的工序,外部连接电极111将由所述应变传感器102d检测到的电压传递到外部设备;以覆盖所述内部布线107b的方式将贴合基板201贴合的工序。

[0213]

产业上的可利用性

[0214]

本公开的一个实施例适用于半导体装置以及半导体装置的制造方法。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。