半导体器件

1.相关申请的交叉引用

2.本技术要求2020年5月18日提交的申请号为10

‑

2020

‑

0059056的韩国专利申请优先权,所述专利申请通过引用整体并入本文。

技术领域

3.本发明的各种实施例涉及半导体器件,更具体地,涉及包括电容器的半导体器件。

背景技术:

4.最近半导体存储器的高度集成化趋向降低了单位单元面积,从而导致低操作电压。这就需要一种具有高电容和低泄漏电流的高k材料。

5.迄今为止,氧化锆(zro2)已被用作用于电容器的电介质层的高k材料,然而,氧化锆在提高电容方面的效果有限。因此,需要新的技术、材料和/或结构来进一步改善高度集成半导体存储器中电容器的特性。

技术实现要素:

6.本发明的实施例涉及一种半导体器件,其包括具有高介电常数、低泄漏电流和高电容的电容器。

7.根据本发明的一个实施例,一种半导体器件包括:第一电极;第二电极;以及位于第一电极和第二电极之间的多层叠层,所述多层叠层包括至少一个反铁电层和至少一个高k电介质层。

8.根据本发明的另一实施例,一种半导体器件包括:第一电极;第二电极;以及位于第一电极和第二电极之间的多层叠层,所述多层叠层包括负电容铁电材料层和至少一个高k电介质层。

9.通过下面的详细描述和附图,这些和其他特征和优点对于本发明所属领域的普通技术人员而言将变得显而易见。

附图说明

10.图1是示出根据本发明的一个实施例的半导体器件的剖视图。

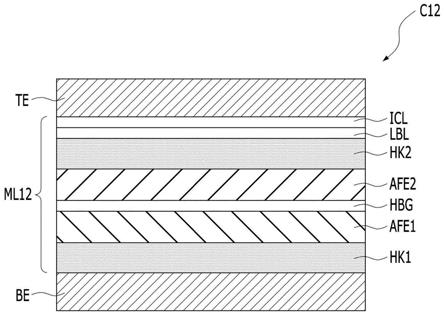

11.图2是示出根据图1的修改示例的电容器的剖视图。

12.图3是示出根据本发明的另一实施例的电容器的剖视图。

13.图4a至图4e是示出根据图3的修改示例的电容器的剖视图。

14.图5是示出根据本发明的另一实施例的电容器的剖视图。

15.图6a至图6e是示出图5的修改示例的剖视图。

16.图7至图15是示出根据本发明的其他实施例的电容器的剖视图。

17.图16a是示出根据本发明的另一实施例的半导体器件的剖视图。

18.图16a至图17c是示出根据本发明的另一实施例的电容器的剖视图。

19.图18是描述沉积富氧化铪的铪锆氧化物层的方法示例的流程图。

20.图19是描述沉积富氧化铪的铪锆氧化物层的方法的另一示例的流程图。

21.图20是示出根据本发明的另一实施例的半导体器件的剖视图。

22.图21至图22b是示出存储单元的剖视图。

23.图23a至图23f是示出存储单元的电容器600的应用的剖视图。

24.图24是示出根据本发明的另一实施例的半导体器件的剖视图。

25.图25至图27是示出根据本发明的其他实施例的电容器的剖视图。

具体实施方式

26.以下可以参考附图更详细地描述本发明的各种实施例。然而,本发明可以以不同的形式体现,并且不应被解释为限于本文所述的实施例。相反,提供这些实施例是为了可以使本发明内容公开得彻底且完善,并使本领域技术人员充分理解本发明的范围。贯穿本公开内容,在本发明的各个图和实施例中的相同附图标记将指代相同的部件。

27.附图不一定是按比例绘制的,在某些情况下,可放大比例以清楚地例示实施例的特征。当第一层被提及在第二层“上”或衬底“上”时,不仅指第一层直接形成在第二层或衬底上的情况,而且还指第一层与第二层或衬底之间存在第三层的情况。

28.可以进一步理解的是,当一个元件被提及“连接到”或“耦接到”另一个元件时,它可以直接在另一个元件上、直接连接到或耦接到另一个元件,或者可以存在一个或更多个介于中间的元件。此外,连接/耦接可以不限于物理连接,可以进一步包括非物理连接,例如,无线连接。

29.此外,还将理解的是,当元件被提及在两个元件“之间”时,它可以是两个元件之间的唯一元件,或者也可以存在一个或更多个介于中间的元件。

30.应当理解的是,附图是所述器件的简化示意图,而且为了避免混淆本发明的特征,并未包括众所周知的细节。

31.还应注意的是,在不偏离本发明的范围的情况下,在一个实施例中存在的特征可以与另一实施例的一个或更多个特征一起使用。

32.氧化铪可以表现出铁电性fe。其中将氧化铪和氧化锆混合在一起的铪锆氧化物(hfzro)通过调整混合物中氧化铪的含量,可以表现出反铁电性afe或铁电性fe。铪锆氧化物(hfzro)在下文中可以简称为

‘

hzo’。

33.表1

[0034][0035]

表1描述了获得反铁电性afe或铁电性fe的hzo的氧化铪含量(x)、氧化锆含量(y)和厚度(t)。

[0036]

参考表1可以看出,无论氧化铪含量(x)和氧化锆含量(y)的比例如何,第一厚度的hzo均可以表现出反铁电性afe。换句话说,当氧化铪含量(x)和氧化锆含量(y)

相同时(x=y),当氧化铪含量(x)大于氧化锆含量(y)时(x>y),以及当氧化锆含量(y)大于氧化铪含量(x)时,hzo可以表现出反铁电性afe。

[0037]

当hzo形成为满足不等式的第二厚度t的层时,在氧化铪含量(x)和氧化锆含量(y)相同时以及在氧化锆含量(y)大于氧化铪含量(x)时,可以表现出反铁电性afe。然而,在氧化铪含量(x)大于氧化锆含量(y)时,hzo可以表现出铁电性fe。

[0038]

当hzo形成为具有满足不等式的第三厚度t的层时,则在氧化锆含量(y)大于氧化铪含量(x)时,hzo可以表现出反铁电性afe。然而,当氧化铪含量(x)和氧化锆含量(y)相同时以及在氧化铪含量(x)大于氧化锆含量(y)时,hzo可以表现出铁电性fe。

[0039]

如上所述,当氧化铪含量和氧化锆含量相同时,或当氧化铪含量大于氧化锆含量时,hzo的反铁电性afe和铁电性fe可以通过调整其厚度来进行选择性地控制。当氧化锆含量大于氧化铪含量时,无论hzo的厚度如何,均可以表现出反铁电性afe。

[0040]

在下文中,可以将其中氧化铪含量和氧化锆含量相同的铪锆氧化物称为

‘

基础(base)铪锆氧化物(基础

‑

hzo,b

‑

hzo)’。可以将其中氧化铪含量大于氧化锆含量的铪锆氧化物称为

‘

富氧化铪的铪锆氧化物(富氧化铪的hzo,hr

‑

hzo)’。可以将其中氧化锆含量大于氧化铪含量的铪锆氧化物称为

‘

富氧化锆的铪锆氧化物(富氧化锆的hzo,zr

‑

hzo)’。可以将具有铁电性的铪锆氧化物称为

‘

铁电性铪锆氧化物(铁电性hzo,fe

‑

hzo)’,可以将具有反铁电性的铪锆氧化物称为

‘

反铁电性铪锆氧化物(反铁电性hzo,afe

‑

hzo)’。

[0041]

反铁电性铪锆氧化物afe

‑

hzo可以具有比基础铪锆氧化物b

‑

hzo和铁电性铪锆氧化物fe

‑

hzo更高的介电常数,并且可以诱发电荷量在发生切换的电压区域内增加的特性,即超高k特性。

[0042]

在下文中,在本发明的实施例中,hf

x

zr

y

o可以指其中氧化铪和氧化锆彼此混合的铪锆氧化物。在hf

x

zr

y

o中,

‘

x’可以指氧化铪含量或铪含量,

‘

y’可以指氧化锆含量或锆含量。富氧化铪的铪锆氧化物hr

‑

hzo也可称为富铪的铪锆氧化物。富氧化锆的铪锆氧化物hr

‑

hzo也可称为富锆的铪锆氧化物。hf

x

zr

y

o也可以用(hfo)

x

(zro)

y

表示,其中hfo代表氧化铪,zro代表氧化锆。

[0043]

基础铪锆氧化物b

‑

hzo可以包括hf

x

zr

y

o(x=y=0.5)。hf

x

zr

y

o(x=y=0.5)可以指氧化铪含量(x)和氧化锆含量(y)相同的材料。hf

x

zr

y

o(x=y=0.5)可以在厚度约为或更小的情况下表现出反铁电性afe。当hf

x

zr

y

o(x=y=0.5)的厚度大于时,其可以表现出铁电性fe。

[0044]

富氧化铪的铪锆氧化物hr

‑

hzo可以包括hf

x

zr

y

o(x>y,0.5<x<0.9)。hf

x

zr

y

o(x>y,0.5<x<0.9)可以指氧化铪含量(x)大于氧化锆含量(y)的材料。当hf

x

zr

y

o(x>y,0.5<x<0.9)小于时,可以表现出反铁电性afe。当hf

x

zr

y

o(x>y,0.5<x<0.9)具有约或更大的厚度时,其可以表现出铁电性fe。

[0045]

富氧化锆的铪锆氧化物(zr

‑

hzo)可以包括hf

x

zr

y

o(x<y,0.5<y<0.7)。hf

x

zr

y

o(x<y,0.5<y<0.7)可以指氧化锆含量(y)大于氧化铪含量(x)的材料。hf

x

zr

y

o(x<y,0.5<y<0.7)不仅可以在厚度为约或更大时表现出反铁电性afe,而且可以在厚度为约或更小时表现出反铁电性afe。hf

x

zr

y

o(x<y,y≥0.7)在即使氧化锆含量(z)显著大于氧化铪含量(x)的情况下,也可以表现出反铁电性afe,即,无论厚度如何,其都可以表现出反铁电性

afe。

[0046]

根据以上描述,通过控制氧化铪含量(或铪含量)、氧化锆含量(或锆含量)和厚度中的至少一个参数,hzo可以表现出铁电性fe或反铁电性afe。

[0047]

图1是示出根据本发明的一个实施例的半导体器件100的剖视图。

[0048]

参考图1,半导体器件100可以包括电容器c11。电容器c11可以包括第一电极be、第二电极te以及在第一电极be和第二电极te之间的多层叠层ml11。多层叠层ml11可以包括至少一个反铁电层afe1和afe2以及至少一个高k电介质层hk1和hk2。多层叠层ml11可以进一步包括至少一个高带隙层hbg。

[0049]

多层叠层ml11可以包括第一高k电介质层hk1、第一反铁电层afe1、高带隙层hbg、第二反铁电层afe2和第二高k电介质层hk2按所述顺序而成的叠层。第一高k电介质层hk1可以形成在第一电极be上方,第一反铁电层afe1可以形成在第一高k电介质层hk1上方。高带隙层hbg可以形成在第一反铁电层afe1上方,第二反铁电层afe2可以形成在高带隙层hbg上方。第二高k电介质层hk2可以形成在第二反铁电层afe2上方,并且第二电极te可以形成在第二高k电介质层hk2上方。多层叠层ml11可以包括至少一个直接接触界面,直接接触界面包括其中至少一个反铁电层afe1和afe2与至少一个高k电介质层hk1和hk2直接接触时的至少一个直接接触界面。例如,第一高k电介质层hk1和第一反铁电层afe1可以直接接触,或者第二反铁电层afe2和第二高k电介质层hk2可以直接接触。在另一个例子中,第一高k电介质层hk1和第一反铁电层afe1可以直接接触,并且第二反铁电层afe2和第二高k电介质层hk2可以直接接触。

[0050]

第一反铁电层afe1可以由铪(hf)、锆(zr)和氧(o)制成或包括铪(hf)、锆(zr)和氧(o)。第一反铁电层afe1可以包括反铁电性铪锆氧化物afe

‑

hzo。作为第一反铁电层afe1,反铁电性铪锆氧化物afe

‑

hzo可以包括基础铪锆氧化物b

‑

hzo、富氧化铪的铪锆氧化物hr

‑

hzo或富氧化锆的铪锆氧化物(zr

‑

hzo)中的至少一种。根据本发明的实施例,第一反铁电层afe1可以包括具有约或更小(至)的厚度的反铁电性铪锆氧化物afe

‑

hzo。例如,第一反铁电层afe1可以包括其中氧化铪含量(x)和氧化锆含量(y)相同的hf

x

zr

y

o(x=y)。在这种情况下,厚度可以是约或更小。根据本发明的另一实施例,第一反铁电层afe1可以包括其中氧化铪含量(x)大于氧化锆含量(y)的hf

x

zr

y

o(x>y)。在这种情况下,厚度可以小于约根据本发明的另一实施例,第一反铁电层afe1可以包括其中氧化锆含量(y)大于氧化铪含量(x)的hf

x

zr

y

o(y>x)。在这种情况下,厚度可以是约或更小。

[0051]

第二反铁电层afe2可以由铪(hf)、锆(zr)和氧(o)制成或包括铪(hf)、锆(zr)和氧(o)。第二反铁电层afe2可以包括反铁电性铪锆氧化物afe

‑

hzo。作为第二反铁电层afe2,反铁电性铪锆氧化物afe

‑

hzo可以包括基础铪锆氧化物b

‑

hzo、富氧化铪的铪锆氧化物hr

‑

hzo或富氧化锆的铪锆氧化物(zr

‑

hzo)。根据本发明的实施例,第二反铁电层afe2可以包括具有约或更小(至)的厚度的反铁电性铪锆氧化物afe

‑

hzo。例如,第二反铁电层afe2可以包括其中氧化铪含量(x)和氧化锆含量(y)相同的hf

x

zr

y

o(x=y)。在这种情况下,厚度可以是约或更小。根据本发明的另一实施例,第二反铁电层afe2可以包括其中氧化铪含量(x)大于氧化锆含量(y)的hf

x

zr

y

o(x>y)。在这种情况下,厚度可以小于约根据本发明的另一实施例,第二反铁电层afe2可以包括其中氧化锆含量(y)大于氧化铪含量

(x)的hf

x

zr

y

o(y>x)。在这种情况下,厚度可以是约或更小。

[0052]

第一和第二反铁电层afe1和afe2可以各自是相同类型材料或同一种材料的反铁电性铪锆氧化物afe

‑

hzo。例如,第一和第二反铁电层afe1和afe2可以各自是约或更小的基础铪锆氧化物b

‑

hzo。另外,第一和第二反铁电层afe1和afe2可以各自是小于约的富氧化铪的铪锆氧化物hr

‑

hzo。

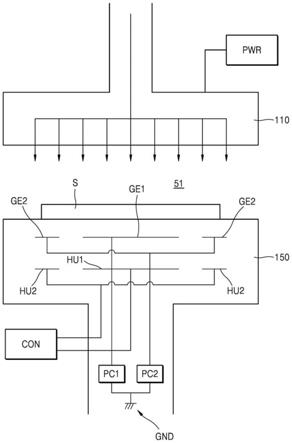

[0053]

根据本发明的另一实施例,第一和第二反铁电层afe1和afe2可以各自为不同材料的反铁电性铪锆氧化物afe

‑

hzo。例如,第一反铁电层afe1可以是约或更小的基础铪锆氧化物b

‑

hzo,而第二反铁电层afe2可以是小于约的富氧化铪的铪锆氧化物hr

‑

hzo。另外,第一反铁电层afe1可以是小于约的富氧化铪的铪锆氧化物hr

‑

hzo,而第二反铁电层afe2可以是约或更小的基础铪锆氧化物b

‑

hzo。

[0054]

根据本发明的另一实施例,第一和第二反铁电层afe1和afe2可以各自包括不同的反铁电性铪锆氧化物,并且可以具有相同的厚度或不同的厚度。

[0055]

根据本发明的另一实施例,第一和第二反铁电层afe1和afe2可以均包括同一种反铁电性铪锆氧化物afe

‑

hzo。在此处,第一反铁电层afe1和第二反铁电层afe2可以具有相同的厚度或不同的厚度。例如,第一和第二反铁电层afe1和afe2可以均为小于约的富氧化铪的铪锆氧化物hr

‑

hzo,第一反铁电层afe1可以是约或更小的基础铪锆氧化物b

‑

hzo,而第二反铁电层afe2可以是小于约的基础铪锆氧化物b

‑

hzo。

[0056]

根据本发明的另一实施例,第一和第二反铁电层afe1和afe2可以均为具有相同氧化铪含量的反铁电性铪锆氧化物。例如,第一反铁电层afe1可以包括第一富氧化铪的铪锆氧化物hr

‑

hzo,而第二反铁电层afe2可以包括第二富氧化铪的铪锆氧化物hr

‑

hzo。在此,第一富氧化铪的铪锆氧化物hr

‑

hzo和第二富氧化铪的铪锆氧化物hr

‑

hzo可以具有相同的氧化铪含量。

[0057]

根据本发明的另一实施例,第一和第二反铁电层afe1和afe2可以各自是具有不同氧化铪含量的反铁电性铪锆氧化物。例如,第一反铁电层afe1可以包括第一富氧化铪的铪锆氧化物hr

‑

hzo,而第二反铁电层afe2可以包括第二富氧化铪的铪锆氧化物hr

‑

hzo。在此,第一富氧化铪的铪锆氧化物hr

‑

hzo和第二富氧化铪的铪锆氧化物hr

‑

hzo可以具有不同的氧化铪含量。第一富氧化铪的铪锆氧化物hr

‑

hzo的氧化铪含量可以大于第二富氧化铪的铪锆氧化物hr

‑

hzo的氧化铪含量。第二富氧化铪的铪锆氧化物hr

‑

hzo的氧化铪含量可以大于第一富氧化铪的铪锆氧化物hr

‑

hzo的氧化铪含量。

[0058]

高带隙层hbg可以用于抑制多层叠层ml11的泄漏电流。高带隙层hbg可以由高能带隙材料制成或包括高能带隙材料。高带隙层hbg可以包括具有比第一和第二反铁电层afe1和afe2的能带隙(以下称其为“带隙”)更大的材料。高带隙层hbg可以由不同于第一和第二反铁电层afe1和afe2的材料制成。高带隙层hbg可以由高k材料制成或包括高k材料,并且可以具有比第一和第二反铁电层afe1和afe2低的介电常数。高带隙层hbg可以具有比氧化硅和氮化硅高的介电常数。高带隙层hbg可以由含铝材料或含铍材料制成或包括含铝材料或含铍材料。高带隙层hbg可以由氧化铝或氧化铍制成或包括氧化铝或氧化铍。高带隙层hbg可以比第一和第二反铁电层afe1和afe2中的每一个都薄。根据本发明的另一实施例,高带

隙层hbg可以由掺杂铝的氧化锆、掺杂铝的氧化铪、掺杂铍的氧化锆或掺杂铍的氧化铪制成,或包括掺杂铝的氧化锆、掺杂铝的氧化铪、掺杂铍的氧化锆或掺杂铍的氧化铪。

[0059]

第一和第二反铁电层afe1和afe2可以具有比第一和第二高k电介质层hk1和hk2高的介电常数。第一高k电介质层hk1可以改善第一反铁电层afe1的结晶度,并且第一高k电介质层hk1可以用于控制在第一反铁电层afe1和第一电极be之间的界面的非完全切换区域。第二高k电介质层hk2可以改善第二反铁电层afe2的结晶度,也可以用于控制在第二反铁电层afe2与第二电极te之间的界面的非完全切换区域。

[0060]

第一高k电介质层hk1可以包括铪和锆中的至少一种。第一高k电介质层hk1可以由氧化铪或氧化锆制成或包括氧化铪或氧化锆。第一高k电介质层hk1可以由单层氧化铪或单层氧化锆制成。第一高k电介质层hk1的底部可以直接接触第一电极be,第一高k电介质层hk1的顶部可以直接接触第一反铁电层afe1。根据本发明的另一实施例,在第一高k电介质层hk1和第一电极be之间可以进一步形成另外的材料。

[0061]

第二高k电介质层hk2可以包括铪和锆中的至少一种。第二高k电介质层hk2可以由氧化铪或氧化锆制成或包括氧化铪或氧化锆。第二高k电介质层hk2可以由单层氧化铪或单层氧化锆制成。第二高k电介质层hk2的底部可以直接接触第二反铁电层afe2,并且第二高k电介质层hk2的顶部可以直接接触第二电极te。根据本发明的另一实施例,在第二高k电介质层hk2和第二电极te之间可以进一步形成另外的材料。

[0062]

第一高k电介质层hk1和第二高k电介质层hk2可以是同一种材料。例如,第一高k电介质层hk1和第二高k电介质层hk2中的每一个可以由单层氧化铪制成。另外,第一高k电介质层hk1和第二高k电介质层hk2可以均为单层氧化锆。

[0063]

第一高k电介质层hk1和第二高k电介质层hk2可以是不同的材料。例如,第一高k电介质层hk1可以由单层氧化铪制成,而第二高k电介质层hk2可以由单层氧化锆制成。同样,第一高k电介质层hk1可以由单层氧化锆制成,而第二高k电介质层hk2可以由单层氧化铪制成。

[0064]

第一高k电介质层hk1或第二高k电介质层hk2可以是反铁电材料。例如,第一高k电介质层hk1可以包括富氧化锆的铪锆氧化物(zr

‑

hzo),而第二高k电介质层hk2可以是氧化铪或氧化锆。根据本发明的另一实施例,第一高k电介质层hk1可以是氧化铪或氧化锆,而第二高k电介质层hk2可以包括富氧化锆的铪锆氧化物(zr

‑

hzo)。富氧化锆的铪锆氧化物(zr

‑

hzo)可以包括hf

x

zr

y

o(x<y),例如hf

0.3

zr

0.7

o。

[0065]

第一和第二高k电介质层hk1和hk2可以比第一和第二反铁电层afe1和afe2厚。第一和第二高k电介质层hk1和hk2可以具有与第一和第二反铁电层afe1和afe2相同的厚度。

[0066]

如上所述,第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第二高k电介质层hk2可以由高k材料制成或包括高k材料,并且高带隙层hbg可以包括具有比第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第二高k电介质层hk2的带隙更高的材料。第一反铁电层afe1和第二反铁电层afe2的介电常数可以比第一高k电介质层hk1和第二高k电介质层hk2高。

[0067]

第一和第二高k电介质层hk1和hk2可以均包括铪或锆,并且第一和第二反铁电层afe1和afe2可以均包括铪和锆。第一高k电介质层hk1和第二高k电介质层hk2可以是氧化铪或氧化锆,第一反铁电层afe1和第二反铁电层afe2可以是反铁电性铪锆氧化物。第一高k电

介质层hk1和第二高k电介质层hk2可以是铁电性氧化铪,第一反铁电层afe1和第二反铁电层afe2可以均为反铁电性铪锆氧化物。

[0068]

根据本发明的一些实施例,多层叠层ml11可以包括hfo2/afe

‑

hzo/al2o3/afe

‑

hzo/hfo2叠层。hfo2/afe

‑

hzo/al2o3/afe

‑

hzo/hfo2叠层可以包括按如下顺序层叠的第一氧化铪层(hfo2)、第一反铁电性铪锆氧化物层afe

‑

hzo、氧化铝层(al2o3)、第二反铁电性铪锆氧化物层afe

‑

hzo和第二氧化铪层(hfo2)。第一氧化铪层(hfo2)可以对应于第一高k电介质层hk1,第二氧化铪层(hfo2)可以对应于第二高k电介质层hk2。氧化铝层(al2o3)可以对应于高带隙层hbg。第一反铁电性铪锆氧化物层afe

‑

hzo可以对应于第一反铁电层afe1,第二反铁电性铪锆氧化物层afe

‑

hzo可以是第二反铁电层afe2。

[0069]

根据本发明的一些实施例,多层叠层ml11可以包括zro2/afe

‑

hzo/al2o3/afe

‑

hzo/zro2叠层。zro2/afe

‑

hzo/al2o3/afe

‑

hzo/zro2叠层可以包括按如下顺序层叠的第一氧化锆层(zro2)、第一反铁电性铪锆氧化物层afe

‑

hzo、氧化铝层(al2o3)、第二反铁电性铪锆氧化物层afe

‑

hzo和第二氧化锆层(zro2)。第一氧化锆层(zro2)可以对应于第一高k电介质层hk1,第二氧化锆层(zro2)可以对应于第二高k电介质层hk2。氧化铝层(al2o3)可以对应于高带隙层hbg。第一反铁电性铪锆氧化物层afe

‑

hzo可以对应于第一反铁电层afe1,第二反铁电性铪锆氧化物层afe

‑

hzo可以对应于第二反铁电层afe2。

[0070]

根据本发明的一些实施例,多层叠层ml11可以包括zro2/afe

‑

hzo/掺杂al的zro2/afe

‑

hzo/zro2叠层、hfo2/afe

‑

hzo/掺杂al的hfo2/afe

‑

hzo/hfo2叠层、zro2/afe

‑

hzo/al2o3/afe

‑

hzo/hfo2叠层或hfo2/afe

‑

hzo/al2o3/afe

‑

hzo/zro2叠层。

[0071]

第一高k电介质层hk1、第一反铁电层afe1、高带隙层hbg、第二反铁电层afe2和第二高k电介质层hk2可以通过原子层沉积(ald)形成。

[0072]

高带隙层hbg可以具有约或更小(至)的厚度,并且第一反铁电层afe1和第二反铁电层afe2可以具有约或更小(至)的厚度。第一高k电介质层hk1和第二高k电介质层hk2可以具有约或更小(至)的厚度。第一和第二高k电介质层hk1和hk2以及第一和第二反铁电层afe1和afe2可以具有相同的厚度或不同的厚度。

[0073]

图2是示出根据图1的修改示例的电容器c12的剖视图。

[0074]

参考图2,电容器c12可以类似于图1的电容器c11。在下文中,可以省略对于同样出现在图1中的构成元件的详细描述。

[0075]

电容器c12可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml12。多层叠层ml12可以包括至少一个反铁电层afe1和afe2以及至少一个高k电介质层hk1和hk2。多层叠层ml12可以进一步包括至少一个高带隙层hbg。多层叠层ml12可以进一步包括泄漏阻挡层lbl和界面控制层icl。

[0076]

多层叠层ml12可以包括按如下顺序层叠的第一高k电介质层hk1、第一反铁电层afe1、高带隙层hbg、第二反铁电层afe2、第二高k电介质层hk2、泄漏阻挡层lbl和界面控制层icl。

[0077]

泄漏阻挡层lbl和界面控制层icl可以位于第二高k电介质层hk2和第二电极te之间。泄漏阻挡层lbl可以位于第二高k电介质层hk2和界面控制层icl之间。界面控制层icl可以位于泄漏阻挡层lbl和第二电极te之间。

[0078]

用于泄漏阻挡层lbl的合适材料可以包括具有高能带隙的高带隙材料。泄漏阻挡层lbl可以包括具有比第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第二高k电介质层hk2的能带隙更大的材料。泄漏阻挡层lbl可以包含高k材料,其介电常数可以低于第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第二高k电介质层hk2。泄漏阻挡层lbl可以具有比氧化硅和氮化硅更高的介电常数。泄漏阻挡层lbl可以由氧化铝或氧化铍制成或包括氧化铝或氧化铍。泄漏阻挡层lbl可以通过原子层沉积(ald)形成。泄漏阻挡层lbl可以比第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第二高k电介质层hk2中的每一个都薄。由于泄漏阻挡层lbl和高带隙层hbg的介电常数相对低于第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第二高k电介质层hk2,因此为了增加电容器c12的电容,泄漏阻挡层lbl和高带隙层hbg可以比第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第二高k电介质层hk2中的每一个都薄。泄漏阻挡层lbl和高带隙层hbg可以均具有约或更小的厚度。泄漏阻挡层lbl和高带隙层hbg可以具有相同的厚度。泄漏阻挡层lbl和高带隙层hbg可以具有不同的厚度。泄漏阻挡层lbl可以比高带隙层hbg要厚。

[0079]

根据本发明的另一实施例,泄漏阻挡层lbl和高带隙层hbg可以由相同类型的材料或同一种材料形成。例如,泄漏阻挡层lbl可以由掺杂铝的氧化锆或掺杂铍的氧化锆制成,或包括掺杂铝的氧化锆或掺杂铍的氧化锆。

[0080]

界面控制层icl可以在形成第二电极te时,用于保护第一高k电介质层hk1、第一反铁电层afe1、高带隙层hbg、第二反铁电层afe2和第二高k电介质层hk2。另外,界面控制层icl可以降低多层叠层ml12的泄漏电流。

[0081]

界面控制层icl可以由在沉积第二电极te时,先于第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第二高k电介质层hk2而还原的材料制成。界面控制层icl可以用作具有大的有效功函数(ewf)和大的导带台阶(conduction band offset,cbo)的泄漏电流阻挡层。另外,界面控制层icl可以不增加多层叠层ml12的等效氧化膜厚度t

ox

。

[0082]

界面控制层icl可以由具有高电负性的材料制成。界面控制层icl可以具有比第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第二高k电介质层hk2更高的鲍林电负性。界面控制层icl可以包括,与第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第二高k电介质层hk2相比具有高鲍林电负性(以下简称为电负性)的材料。当电负性高时,难以被氧化,并且容易被还原。因此,界面控制层icl可代替第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第二高k电介质层hk2而脱氧。界面控制层icl可以防止第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第二高k电介质层hk2损失氧。

[0083]

界面控制层icl可以包括具有高电负性的原子,例如,金属原子、硅原子或锗原子。界面控制层icl可以由钛(ti)、钽(ta)、铝(al)、锡(sn)、钼(mo)、钌(ru)、铱(ir)、铌(nb)、锗(ge)、硅(si)、镍(ni)或其组合制成,或包括钛(ti)、钽(ta)、铝(al)、锡(sn)、钼(mo)、钌(ru)、铱(ir)、铌(nb)、锗(ge)、硅(si)、镍(ni)或其组合。界面控制层icl可以包括钼和氮化钼(mo/mon)的叠层或钨和氮化钨(w/wn)的叠层。界面控制层icl可以包括含有高电负性原子的导电材料,并且因此界面控制层icl可以用作第二电极te的一部分。

[0084]

界面控制层icl可以由氧化钛、氧化钽、氧化铌、氧化铝、氧化硅(sio2)、氧化锡、氧

化锗、二氧化钼、三氧化钼、氧化铱、氧化钌、氧化镍或其组合制成,或包括氧化钛、氧化钽、氧化铌、氧化铝、氧化硅(sio2)、氧化锡、氧化锗、二氧化钼、三氧化钼、氧化铱、氧化钌、氧化镍或其组合。

[0085]

根据本发明的一些实施例,多层叠层ml12可以包括hfo2/afe

‑

hzo/al2o3/afe

‑

hzo/hfo2/al2o3/tio2叠层。hfo2/afe

‑

hzo/al2o3/afe

‑

hzo/hfo2/al2o3/tio2叠层可以包括按如下顺序层叠的第一氧化铪层(hfo2)、第一反铁电性铪锆氧化物层afe

‑

hz o、第一氧化铝层(al2o3)、第二反铁电性铪锆氧化物层afe

‑

hzo、第二氧化铪层(h fo2)、第二氧化铝层(al2o3)和氧化钛层(tio2)。第一氧化铪层(hfo2)可以对应于第一高k电介质层hk1,第二氧化铪层(hfo2)可以对应于第二高k电介质层hk2。氧化铝层(al2o3)可以对应于高带隙层hbg。第一反铁电性铪锆氧化物层afe

‑

hzo可以对应于第一反铁电层afe1,第二反铁电性铪锆氧化物层afe

‑

hzo可以对应于第二反铁电层afe2。第二氧化铝层(al2o3)可以对应于泄漏阻挡层lbl,并且氧化钛层(tio2)可以对应于界面控制层icl。

[0086]

根据本发明的一些实施例,多层叠层ml12可以包括zro2/afe

‑

hzo/al2o3/afe

‑

hzo/zro2/al2o3/tio2叠层。zro2/afe

‑

hzo/al2o3/afe

‑

hzo/zro2/al2o3/tio2叠层可以包括按如下顺序层叠的第一氧化锆层(zro2)、第一反铁电性铪锆氧化物afe

‑

hzo、氧化铝层(al2o3)、第二反铁电性铪锆氧化物afe

‑

hzo、第二氧化锆层(zro2)、第二氧化铝层(al2o3)和氧化钛层(tio2)。第一氧化锆层(zro2)可以对应于第一高k电介质层hk1,第二氧化锆层(zro2)可以对应于第二高k电介质层hk2。氧化铝层(a l2o3)可以对应于高带隙层hbg。第一反铁电性铪锆氧化物层afe

‑

hzo可以对应于第一反铁电层afe1,第二反铁电性铪锆氧化物层afe

‑

hzo可以对应于第二反铁电层af e2。第二氧化铝层(al2o3)可以对应于泄漏阻挡层lbl,并且氧化钛层(tio2)可以对应于界面控制层icl。

[0087]

根据本发明的一些实施例,多层叠层ml12可以包括zro2/afe

‑

hzo/掺杂al的zro2/afe

‑

hzo/zro2/al2o3/tio2叠层、hfo2/afe

‑

hzo/掺杂al的hfo2/afe

‑

hzo/hfo2/al2o3/tio2叠层、zro2/afe

‑

hzo/al2o3/afe

‑

hzo/hfo2/al2o3/tio2叠层或hfo2/afe

‑

hzo/al2o3/afe

‑

hzo/zro2/al2o3/tio2叠层。氧化铝层(al2o3)、掺杂铝的氧化锆层(掺杂al的zro2)和掺杂铝的氧化铪层(掺杂al的hfo2)可以对应于高带隙层hbg。

[0088]

图3是示出根据本发明的另一实施例的电容器c13的剖视图。

[0089]

参考图3,电容器c13可以类似于图1的电容器c11。在下文中,可以省略对于同样出现在图1中的构成元件的详细描述。

[0090]

电容器c13可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml13。多层叠层ml13可以包括至少一个反铁电层afe1和afe2以及至少一个高k电介质层hk1和hk2。多层叠层ml13可以进一步包括至少一个高带隙层hbg。

[0091]

多层叠层ml13可以包括按如下顺序层叠的第一反铁电层afe1、第一高k电介质层hk1、高带隙层hbg、第二高k电介质层hk2和第二反铁电层afe2。

[0092]

第一反铁电层afe1可以直接接触第一电极be和第一高k电介质层hk1。第一反铁电层afe1可以位于第一电极be和第一高k电介质层hk1之间。第二反铁电层afe2可以直接接触第二电极te和第二高k电介质层hk2。第二反铁电层afe2可以位于第二电极te和第二高k电介质层hk2之间。

[0093]

高带隙层hbg可以位于第一高k电介质层hk1和第二高k电介质层hk2之间。高带隙

层hbg可以直接接触第一高k电介质层hk1和第二高k电介质层hk2。返回参考图1,电容器c11的高带隙层hbg可以位于第一反铁电层afe1和第二反铁电层afe2之间。

[0094]

高带隙层hbg可以由具有大的能带隙的高带隙材料制成或包括具有大的能带隙的高带隙材料。高带隙层hbg可以包括具有比第一和第二高k电介质层hk1和hk2更大的能带隙的材料。高带隙层hbg可以由不同于第一和第二高k电介质层hk1和hk2的材料制成。高带隙层hbg可以由高k材料制成或包括高k材料,但可以具有比第一和第二高k电介质层hk1和hk2更小的介电常数。高带隙层hbg可以具有比氧化硅和氮化硅更大的介电常数。高带隙层hbg可以由含铝材料或含铍材料制成或包括含铝材料或含铍材料。高带隙层hbg可以由氧化铝或氧化铍制成或包括氧化铝或氧化铍。高带隙层hbg可以比第一和第二高k电介质层hk1和hk2中的每一个都薄。

[0095]

根据本发明的另一实施例,高带隙层hbg可以不隔离第一高k电介质层hk1和第二高k电介质层hk2的晶粒。例如,第一高k电介质层hk1、高带隙层hbg和第二高k电介质层hk2的晶粒可以呈连续状态而未被间隔开。高带隙层hbg可以具有不使第一高k电介质层hk1的晶粒和第二高k电介质层hk2的晶粒间隔开的薄的厚度。因此,第一高k电介质层hk1的晶粒和第二高k电介质层hk2的晶粒可以在垂直方向上是连续的。

[0096]

当第一高k电介质层hk1和第二高k电介质层hk2包含氧化锆时,高带隙层hbg可以是掺杂铝的氧化锆或掺杂铍的氧化锆。当第一高k电介质层hk1和第二高k电介质层hk2包含氧化铪时,高带隙层hbg可以是掺杂铝的氧化铪或掺杂铍的氧化铪。高带隙层hbg、第一高k电介质层hk1和第二高k电介质层hk2均可以具有四方晶体结构。

[0097]

图4a至4e是示出根据图3的修改示例的电容器的剖视图。

[0098]

参考图4a,电容器c14可以类似于图3的电容器c13。在下文中,可以省略对于同样出现在图3中的构成元件的详细描述。

[0099]

电容器c14可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml14。多层叠层ml14可以包括至少一个反铁电层afe1和afe2以及至少一个高k电介质层hk1和hk2。多层叠层ml14可以进一步包括至少一个高带隙层hbg。多层叠层ml14可以进一步包括泄漏阻挡层lbl和界面控制层icl。

[0100]

多层叠层ml14可以包括按如下顺序层叠的第一反铁电层afe1、第一高k电介质层hk1、高带隙层hbg、第二高k电介质层hk2、第二反铁电层afe2、泄漏阻挡层lbl和界面控制层icl。

[0101]

泄漏阻挡层lbl和界面控制层icl可以位于第二反铁电层afe2和第二电极te之间。泄漏阻挡层lbl可以位于第二反铁电层afe和界面控制层icl之间。界面控制层icl可以位于泄漏阻挡层lbl和第二电极te之间。至于泄漏阻挡层lbl和界面控制层icl的详细描述,可以参考图2及随附的说明。

[0102]

多层叠层ml14的应用实例可以描述如下。

[0103]

参考图4b,多层叠层ml14a可以包括afe

‑

hzo/zro2/al2o3/zro2/afe

‑

hzo/al2o3/tio2叠层。第一和第二反铁电层afe1和afe2可以各自包括反铁电性铪锆氧化物afe

‑

hzo。第一和第二高k电介质层hk1和hk2可以均包括氧化锆(zro2)。高带隙层hbg可以由氧化铝(al2o3)制成或包括氧化铝(al2o3)。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。

[0104]

因此,多层叠层ml14a可以由按如下顺序层叠的反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、氧化铝(al2o3)、氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)制成,或包括按如下顺序层叠的反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、氧化铝(al2o3)、氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)。

[0105]

参考图4c,多层叠层ml14b可以包括afe

‑

hzo/zro2/掺杂al的zro2/zro2/afe

‑

hzo/al2o3/tio2叠层。第一和第二反铁电层afe1和afe2可以均包括反铁电性铪锆氧化物afe

‑

hzo。第一和第二高k电介质层hk1和hk2可以均包括氧化锆(zro2)。高带隙层hbg可以由掺杂铝的氧化锆(掺杂al的zro2)制成,或包括掺杂铝的氧化锆(掺杂al的zro2)。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),并且界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。在zro2/掺杂al的zro2/zro2中,掺杂铝的氧化锆(掺杂al的zro2)可以不分隔氧化锆(zro2)的晶粒。

[0106]

因此,多层叠层ml14b可以由按如下顺序层叠的反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、掺杂铝的氧化锆(掺杂al的zro2)、氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)制成,或包括按如下顺序层叠的反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、掺杂铝的氧化锆(掺杂al的zro2)、氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)。

[0107]

在多层叠层ml14b中,掺杂铝的氧化锆(掺杂al的zro2)可以比氧化锆(zro2)薄。氧化锆(zro2)和掺杂铝的氧化锆(掺杂al的zro2)可以均具有四方晶体结构。zro2/掺杂al的zro2/zro2也可称为嵌入铝的氧化锆(嵌入al的zro2)。

[0108]

掺杂铝的氧化锆(掺杂al的zro2)可以是高带隙层hbg,这与图4b中的高带隙层hbg是氧化铝(al2o3)不同。图4b的氧化铝(al2o3)的厚度可以将下部氧化锆(zro2)的晶粒和上部氧化锆(zro2)的晶粒间隔开。氧化铝(al2o3)可以比掺杂铝的氧化锆(az)厚。下部氧化锆(zro2)的晶粒和上部氧化锆(zro2)的晶粒可以呈连续状态而不被图4c的掺杂铝的氧化锆(掺杂al的zro2)间隔开。下部氧化锆(zro2)的晶粒和上部氧化锆(zro2)的晶粒可以被图4b的氧化铝(al2o3)间隔开。

[0109]

参考图4d,多层叠层ml14c可以包括afe

‑

hzo/hfo2/al2o3/hfo2/afe

‑

hzo/al2o3/tio2叠层。第一和第二反铁电层afe1和afe2可以均包括反铁电性铪锆氧化物afe

‑

hzo。第一和第二高k电介质层hk1和hk2可以均包括氧化铪(hfo2)。高带隙层hbg可以由氧化铝(al2o3)制成或包括氧化铝(al2o3)。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),并且界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。

[0110]

因此,多层叠层ml14c可以由按如下顺序层叠的反铁电性铪锆氧化物afe

‑

hzo、氧化铪(hfo2)、氧化铝(al2o3)、氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)制成,或包括按如下顺序层叠的反铁电性铪锆氧化物afe

‑

hzo、氧化铪(hfo2)、氧化铝(al2o3)、氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)。

[0111]

参考图4e,多层叠层ml14d可以包括afe

‑

hzo/hfo2/掺杂al的hfo2/hfo2/afe

‑

hzo/al2o3/tio2叠层。第一和第二反铁电层afe1和afe2可以均包括反铁电性铪锆氧化物afe

‑

hzo。第一和第二高k电介质层hk1和hk2可以均包括氧化铪(hfo2)。高带隙层hbg可以由掺杂

铝的氧化铪(掺杂al的hfo2)制成或包括掺杂铝的氧化铪(掺杂al的hfo2)。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),并且界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。在hfo2/掺杂al的hfo2/hfo2中,掺杂铝的氧化铪(掺杂al的hfo2)可以不隔离氧化铪(hfo2)的晶粒。

[0112]

因此,多层叠层ml14d可以由按如下顺序层叠的反铁电性铪锆氧化物afe

‑

hzo、氧化铪(hfo2)、掺杂铝的氧化铪(掺杂al的hfo2)、氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)制成,或包括按如下顺序层叠的反铁电性铪锆氧化物afe

‑

hzo、氧化铪(hfo2)、掺杂铝的氧化铪(掺杂al的hfo2)、氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)。

[0113]

图5是示出根据本发明另一实施例的电容器c15的剖视图。

[0114]

参考图5,电容器c15可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml15。多层叠层ml15可以包括至少一个反铁电层afe1和afe2以及至少一个高k电介质层hk1、hk2和hk3。多层叠层ml15可以进一步包括泄漏阻挡层lbl和界面控制层icl。根据本发明的另一实施例,可以省略多层叠层ml15中的泄漏阻挡层lbl和界面控制层icl。

[0115]

多层叠层ml15可以包括按如下顺序层叠的第一高k电介质层hk1、第一反铁电层afe1、第二高k电介质层hk2、高带隙层hbg、第三高k电介质层hk3、第二反铁电层afe2、泄漏阻挡层lbl和界面控制层icl。第一反铁电层afe1可以位于第一高k电介质层hk1和第二高k电介质层hk2之间。第二反铁电层afe2可以位于第三高k电介质层hk3和泄漏阻挡层lbl之间。高带隙层hbg可以位于第二高k电介质层hk2和第三高k电介质层hk3之间。

[0116]

第一高k电介质层hk1、第二高k电介质层hk2和第三高k电介质层hk3可以是同一种材料,也可以是不同材料。

[0117]

第一高k电介质层hk1、第二高k电介质层hk2和第三高k电介质层hk3可以由铪或锆制成或包括铪或锆。第一高k电介质层hk1、第二高k电介质层hk2和第三高k电介质层hk3可以由氧化铪或氧化锆制成或包括氧化铪或氧化锆。第一高k电介质层hk1、第二高k电介质层hk2和第三高k电介质层hk3可以由单层氧化铪或单层氧化锆制成。第一高k电介质层hk1、第二高k电介质层hk2和第三高k电介质层hk3可以具有四方晶体结构。

[0118]

第一高k电介质层hk1、第二高k电介质层hk2和第三高k电介质层hk3可以是不同的材料。例如,第一高k电介质层hk1可以由单层氧化铪制成,第二高k电介质层hk2和第三高k电介质层hk3可以由单层氧化锆制成。另外,第一高k电介质层hk1可以由单层氧化锆制成,第二高k电介质层hk2和第三高k电介质层hk3可以由单层氧化铪制成。另外,第一高k电介质层hk1和第二高k电介质层hk2可以由单层氧化铪制成,第三高k电介质层hk3可以由单层氧化锆制成。第一高k电介质层hk1和第二高k电介质层hk2可以由单层氧化锆制成,第三高k电介质层hk3可以由单层氧化铪制成。

[0119]

第一高k电介质层hk1、第二高k电介质层hk2和第三高k电介质层hk3中的至少一个可以是反铁电材料。例如,第一高k电介质层hk1可以是富氧化锆的铪锆氧化物(zr

‑

hzo),第二高k电介质层hk2和第三高k电介质层hk3可以是氧化铪或氧化锆。另外,第一高k电介质层hk1可以是氧化铪或氧化锆,第二高k电介质层hk2和第三高k电介质层hk3可以是富氧化锆的铪锆氧化物(zr

‑

hzo)。

[0120]

多层叠层ml15可以包括zro2/afe

‑

hzo/zro2/al2o3/zro2/afe

‑

hzo/al2o3/tio2叠层。第一和第二反铁电层afe1和afe2可以均包括反铁电性铪锆氧化物afe

‑

hzo。第一高k电介质层hk1、第二高k电介质层hk2和第三高k电介质层hk3可以包括氧化锆(zro2)。高带隙层hbg可以由氧化铝(al2o3)制成或包括氧化铝(al2o3)。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。

[0121]

因此,多层叠层ml15可以包括按如下顺序层叠的氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、氧化铝(al2o3)、氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)。

[0122]

根据本发明的另一实施例,多层叠层ml15可以包括zro2/afe

‑

hzo/zro2/掺杂al的zro2/zro2/afe

‑

hzo/al2o3/tio2叠层。第一和第二反铁电层afe1和afe2可以均包括反铁电性铪锆氧化物afe

‑

hzo。第一高k电介质层hk1、第二高k电介质层hk2和第三高k电介质层hk3可以包括氧化锆(zro2)。高带隙层hbg可以由掺杂铝的氧化锆(掺杂al的zro2)制成,或包括掺杂铝的氧化锆(掺杂al的zro2)。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),并且界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。因此,多层叠层ml15可以包括按如下顺序层叠的氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、掺杂铝的氧化锆(掺杂al的zro2)、氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)。

[0123]

根据本发明的另一实施例,多层叠层ml15可以包括hfo2/afe

‑

hzo/hfo2/掺杂al的hfo2/hfo2/afe

‑

hzo/al2o3/tio2叠层。第一和第二反铁电层afe1和afe2可以各自包括反铁电性铪锆氧化物afe

‑

hzo。第一高k电介质层hk1、第二高k电介质层hk2和第三高k电介质层hk3可以分别由氧化铪(hfo2)制成或包括氧化铪(hfo2)。高带隙层hbg可以由掺杂铝的氧化铪(掺杂al的hfo2)制成或包括掺杂铝的氧化铪(掺杂al的hfo2)。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),而界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。因此,多层叠层ml15可以由按如下顺序层叠的氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铪(hfo2)、掺杂铝的氧化铪(掺杂al的hfo2)、氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)制成,或包括按如下顺序层叠的氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铪(hfo2)、掺杂铝的氧化铪(掺杂al的hfo2)、氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)。

[0124]

根据本发明的另一实施例,多层叠层ml15可以包括hfo2/afe

‑

hzo/hfo2/al2o3/hfo2/afe

‑

hzo/al2o3/tio2叠层。第一和第二反铁电层afe1和afe2可以各自包括反铁电性铪锆氧化物afe

‑

hzo。第一高k电介质层hk1、第二高k电介质层hk2和第三高k电介质层hk3可以分别由氧化铪(hfo2)制成或包括氧化铪(hfo2)。高带隙层hbg可以由氧化铝(al2o3)制成或包括氧化铝(al2o3)。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),而界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。因此,多层叠层ml15可以由氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铪(hfo2)、氧化铝(al2o3)、氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)制成,或包括氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铪(hfo2)、氧化铝(al2o3)、氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铝(al2o3)和氧化钛(tio2)。

[0125]

图6a至6e是示出图5的修改示例的剖视图。

[0126]

参考图6a,电容器c16可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml16。多层叠层ml16可以包括至少一个反铁电层afe1和afe2以及至少一个高k电介质层hk1、hk2、hk3和hk4。多层叠层ml16可以进一步包括泄漏阻挡层lbl和界面控制层icl。根据本发明的另一实施例,可以省略多层叠层ml16的泄漏阻挡层lbl和界面控制层icl。

[0127]

多层叠层ml16可以包括第一高k电介质层hk1、第一反铁电层afe1、第二高k电介质层hk2、高带隙层hbg、第三高k电介质层hk3、第二反铁电层afe2、第四高k电介质层hk4、泄漏阻挡层lbl和界面控制层icl。第一反铁电层afe1可以位于第一高k电介质层hk1和第二高k电介质层hk2之间。第二反铁电层afe2可以位于第三高k电介质层hk3和第四高k电介质层hk4之间。高带隙层hbg可以位于第二高k电介质层hk2和第三高k电介质层hk3之间。

[0128]

第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3和第四高k电介质层hk4可以是同一种材料,也可以是不同的材料。

[0129]

第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3和第四高k电介质层hk4可以由铪或锆制成或者包括铪或锆。第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3和第四高k电介质层hk4可以由氧化铪或氧化锆制成,或包括氧化铪或氧化锆。第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3和第四高k电介质层hk4可以由单层氧化铪或单层氧化锆制成。

[0130]

第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3和第四高k电介质层hk4中的至少一个可以是反铁电材料。第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3和第四高k电介质层hk4中的至少一个可以是富氧化锆的铪锆氧化物。

[0131]

参考图6b,多层叠层ml16a可以包括zro2/afe

‑

hzo/zro2/al2o3/zro2/afe

‑

hzo/zro2/al2o3/tio2叠层。第一和第二反铁电层afe1和afe2可以均包括反铁电性铪锆氧化物afe

‑

hzo。第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3和第四高k电介质层hk4可以包括氧化锆(zro2)。高带隙层hbg可以由氧化铝(al2o3)制成或包括氧化铝(al2o3)。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。

[0132]

因此,多层叠层ml20可以包括氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、氧化铝(al2o3)、氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、氧化铝(al2o3)和氧化钛(zro2)。

[0133]

参考图6c,多层叠层ml16b可以包括zro2/afe

‑

hzo/zro2/掺杂al的zro2/zro2/afe

‑

hzo/zro2/al2o3/tio2叠层。第一和第二反铁电层afe1和afe2可以均包括反铁电性铪锆氧化物afe

‑

hzo。第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3和第四高k电介质层hk4可以包括氧化锆(zro2)。高带隙层hbg可以由掺杂铝的氧化锆(掺杂al的zro2)制成或包括掺杂铝的氧化锆(掺杂al的zro2)。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。

[0134]

因此,多层叠层ml16b可以包括按如下顺序层叠的氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、掺杂铝的氧化锆(掺杂al的zro2)、氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、氧化铝(al2o3)和氧化钛(tio2)。

[0135]

参考图6d,多层叠层ml16c可以包括hfo2/afe

‑

hzo/zro2/al2o3/zro2/afe

‑

hzo/

hfo2/al2o3/tio2叠层。第一和第二反铁电层afe1和afe2可以均包括反铁电性铪锆氧化物afe

‑

hzo。第二高k电介质层hk2和第三高k电介质层hk3可以包括氧化锆(zro2),而第一高k电介质层hk1和第四高k电介质层hk4可以分别由氧化铪(hfo2)制成或包括氧化铪(hfo2)。高带隙层hbg可以由氧化铝(al2o3)制成或包括氧化铝(al2o3)。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。

[0136]

因此,多层叠层ml16d可以由按如下顺序层叠的氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、氧化铝(al2o3)、氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铪(hfo2)、氧化铝(al2o3)和氧化钛(tio2)制成,或包括按如下顺序层叠的氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、氧化铝(al2o3)、氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铪(hfo2)、氧化铝(al2o3)和氧化钛(tio2)。

[0137]

参考图6e,多层叠层ml16e可以包括hfo2/afe

‑

hzo/zro2/掺杂al的zro2/zro2/afe

‑

hzo/hfo2/al2o3/tio2叠层。第一和第二反铁电层afe1和afe2可以均包括反铁电性铪锆氧化物afe

‑

hzo。第二高k电介质层hk2和第三高k电介质层hk3可以包括氧化锆(zro2),而第一高k电介质层hk1和第四高k电介质层hk4可以分别由氧化铪(hfo2)制成或包括氧化铪(hfo2)。高带隙层hbg可以由掺杂铝的氧化锆(掺杂al的zro2)制成或包括掺杂铝的氧化锆(掺杂al的zro2)。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。

[0138]

因此,多层叠层ml16e可以由按如下顺序层叠的氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、掺杂铝的氧化锆(掺杂al的zro2)、氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铪(hfo2)、氧化铝(al2o3)和氧化钛(tio2)制成,或包括按如下顺序层叠的氧化铪(hfo2)、反铁电性铪锆氧化物afe

‑

hzo、氧化锆(zro2)、掺杂铝的氧化锆(掺杂al的zro2)、氧化锆(zro2)、反铁电性铪锆氧化物afe

‑

hzo、氧化铪(hfo2)、氧化铝(al2o3)和氧化钛(tio2)。

[0139]

图7是示出根据本发明另一实施例的电容器的剖视图。

[0140]

参考图7,电容器c17可以包括第一电极be、第二电极te,以及在第一电极be和第二电极te之间的多层叠层ml17。多层叠层ml17可以包括至少一个反铁电层afe1和afe2以及一个高k电介质层hk。

[0141]

多层叠层ml17可以包括按如下顺序层叠的第一反铁电层afe1、高k电介质层hk和第二反铁电层afe2。高k电介质层hk可以位于第一反铁电层afe1和第二反铁电层afe2之间。高k电介质层hk可以比图1至6e中的高k电介质层hk1、hk2、hk3和hk4厚。高k电介质层hk可以比第一反铁电层afe1和第二反铁电层afe2厚。高k电介质层hk可以具有约至的厚度,第一反铁电层afe1和第二反铁电层afe2可以各自具有约或更小的厚度。

[0142]

高k电介质层hk可以由铪或锆制成或包括铪或锆。高k电介质层hk可以由氧化铪或氧化锆制成,或包括氧化铪或氧化锆。高k电介质层hk可以由单层氧化铪制成。高k电介质层hk可以由单层氧化锆制成。根据本发明的另一实施例,高k电介质层hk可以是反铁电材料。例如,高k电介质层hk可以包括富氧化锆的铪锆氧化物。

[0143]

图8是示出根据本发明另一实施例的电容器的剖视图。

[0144]

参考图8,电容器c18可以类似于图7的电容器c17。在此,可以省略对于同样出现在

图7中的构成元件的详细描述。

[0145]

电容器c18可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml18。多层叠层ml18可以包括至少一个反铁电层afe1和afe2以及一个高k电介质层hk。多层叠层ml18可以进一步包括泄漏阻挡层lbl和界面控制层icl。

[0146]

多层叠层ml18可以包括按如下顺序层叠的第一反铁电层afe1、高k电介质层hk、第二反铁电层afe2、泄漏阻挡层lbl和界面控制层icl。高k电介质层hk可以位于第一反铁电层afe1和第二反铁电层afe2之间。高k电介质层hk可以比第一反铁电层afe1和第二反铁电层afe2厚。高k电介质层hk可以具有约至的厚度。第一反铁电层afe1和第二反铁电层afe2可以各自具有约或更小的厚度。

[0147]

泄漏阻挡层lbl和界面控制层icl可以位于第二反铁电层afe2和第二电极te之间。泄漏阻挡层lbl可以位于第二反铁电层afe2和界面控制层icl之间。界面控制层icl可以位于泄漏阻挡层lbl和第二电极te之间。对于泄漏阻挡层lbl和界面控制层icl的描述,可以参考图2和随附的说明。

[0148]

图9至17c示出了根据本发明的其它实施例的电容器。图9至17c所示的根据本发明的其他实施例的电容器可以具有与根据图1至8的电容器类似的构成元件。在下文中,对于同样出现在图1至8中的构成元件的详细描述,可以参考图1至8和随附的说明。

[0149]

参考图9,电容器c19可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml19。多层叠层ml19可以包括至少一个反铁电层afe1和afe2以及至少一个高k电介质层hk1和hk2。多层叠层ml19可以进一步包括泄漏阻挡层lbl和界面控制层icl。根据本发明的另一实施例,可以省略多层叠层ml19的泄漏阻挡层lbl和界面控制层icl。

[0150]

多层叠层ml19可以包括按如下顺序层叠的第一反铁电层afe1、第一高k电介质层hk1、高带隙层hbg、第二反铁电层afe2、第二高k电介质层hk2、泄漏阻挡层lbl和界面控制层icl。第一反铁电层afe1可以与第一电极be和第一高k电介质层hk1直接接触。第一反铁电层afe1可以位于第一电极be和第一高k电介质层hk1之间。第二反铁电层afe2可以与第二高k电介质层hk2和高带隙层hbg直接接触。第二反铁电层afe2可以位于高带隙层hgb和第二高k电介质层hk2之间。

[0151]

与本发明的上述实施例不同的是,多层叠层ml19的高带隙层hbg可以位于第一高k电介质层hk1和第二反铁电层afe2之间。返回参考图1和图2,高带隙层hbg可以位于第一反铁电层afe1和第二反铁电层afe2之间。返回参考图3,高带隙层hbg可以位于第一高k电介质层hk1和第二高k电介质层hk2之间。

[0152]

多层叠层ml19可以包括:第一叠层,其包括第一反铁电层afe1和在第一反铁电层afe1上方的第一高k电介质层hk1;以及第二叠层,其包括第二反铁电层afe2和在第二反铁电层afe2上方的第二高k电介质层hk2。高带隙层hbg可以位于第一叠层和第二叠层之间。

[0153]

参考图10,电容器c20可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml20。多层叠层ml20可以包括至少一个反铁电层afe1和afe2以及至少一个高k电介质层hk1和hk2。多层叠层ml20可以进一步包括泄漏阻挡层lbl和界面控制层icl。根据本发明的另一实施例,可以省略多层叠层ml20的泄漏阻挡层lbl和界面控制层icl。

[0154]

多层叠层ml20可以包括按如下顺序层叠的第一高k电介质层hk1、第一反铁电层afe1、高带隙层hbg、第二高k电介质层hk2、第二反铁电层afe2、泄漏阻挡层lbl和界面控制层icl。第一反铁电层afe1可以与第一高k电介质层hk1和高带隙层hbg直接接触,并且可以位于第一高k电介质层hk1和高带隙层hbg之间。第二反铁电层afe2可以与第二高k电介质层hk2和泄漏阻挡层lbl直接接触,并且可以位于第二高k电介质层hk2和泄漏阻挡层lbl之间。

[0155]

多层叠层ml20的高带隙层hbg可以位于第一反铁电层afe1和第二高k电介质层hk2之间。

[0156]

多层叠层ml20可以包括:第一叠层,其包括第一高k电介质层hk1和在第一高k电介质层hk1上方的第一反铁电层afe1;以及第二叠层,其包括第二高k电介质层hk2和在第二高k电介质层hk2上方的第二反铁电层afe2。高带隙层hbg可以位于第一叠层和第二叠层之间。

[0157]

参考图11,电容器c21可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml21。多层叠层ml21可以包括至少一个反铁电层afe1、afe2和afe3以及至少一个高k电介质层hk1、hk2和hk3。多层叠层ml21可以进一步包括泄漏阻挡层lbl和界面控制层icl。根据本发明的另一实施例,可以省略多层叠层ml21的泄漏阻挡层lbl和界面控制层icl。

[0158]

多层叠层ml21可以包括按如下顺序层叠的第一高k电介质层hk1、第一反铁电层afe1、第二高k电介质层hk2、高带隙层hbg、第二反铁电层afe2、第三高k电介质层hk3、第三反铁电层afe3、泄漏阻挡层lbl和界面控制层icl。

[0159]

第一反铁电层afe1可以位于第一高k电介质层hk1和第二高k电介质层hk2之间。第二反铁电层afe2可以位于高带隙层hbg和第三高k电介质层hk3之间。第三反铁电层afe3可以位于第三高k电介质层hk3和泄漏阻挡层lbl之间。高带隙层hbg可以位于第二高k电介质层hk2和第二反铁电层afe2之间。

[0160]

第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以由铪(hf)和锆(zr)制成,或包括铪(hf)和锆(zr)。第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以由反铁电性铪锆氧化物制成或包括反铁电性铪锆氧化物。作为第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3,反铁电性铪锆氧化物可以包括基础铪锆氧化物、富氧化铪的铪锆氧化物或富氧化锆的铪锆氧化物。

[0161]

根据本发明的实施例,第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以由厚度为约或更小(至)的反铁电性铪锆氧化物制成,或包括厚度为约或更小(至)的反铁电性铪锆氧化物。例如,第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以含有其中氧化铪含量(x)和氧化锆含量(y)相同的hf

x

zr

y

o(x=y)。在这种情况下,厚度可以是约或更小。根据本发明的另一实施例,第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以由其中氧化铪含量(x)大于氧化锆含量(y)的hf

x

zr

y

o(x>y)制成,或包括氧化铪含量(x)大于氧化锆含量(y)的hf

x

zr

y

o(x>y)。在这种情况下,厚度可以小于约根据本发明的另一实施例,第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以由其中氧化锆含量(y)大于氧化铪含量(x)的hf

x

zr

y

o(y>x)制成,或包括氧化锆含量(y)大于氧化铪含量(x)的hf

x

zr

y

o(y>x)。在这种情况下,厚度可以是约或更小。

[0162]

第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以是相同类型材料或同一种材料的反铁电性铪锆氧化物。

[0163]

根据本发明的另一实施例,第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以是不同材料的反铁电性铪锆氧化物。

[0164]

根据本发明的另一实施例,第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以由相同的反铁电材料制成或包括相同的反铁电材料,并且它们可以具有相同的厚度或不同的厚度。

[0165]

根据本发明的另一实施例,第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以由不同的反铁电材料制成或包括不同的反铁电材料,并且它们可以具有相同的厚度或不同的厚度。

[0166]

根据本发明的另一实施例,第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以是具有相同氧化铪含量的反铁电性铪锆氧化物。

[0167]

根据本发明的另一实施例,第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以是具有不同氧化铪含量的反铁电性铪锆氧化物。

[0168]

参考图12,电容器c22可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml22。多层叠层ml22可以包括至少一个反铁电层afe1、afe2和afe3以及至少一个高k电介质层hk1和hk2。多层叠层ml22可以进一步包括泄漏阻挡层lbl和界面控制层icl。根据本发明的另一实施例,可以省略多层叠层ml22的泄漏阻挡层lbl和界面控制层icl。

[0169]

多层叠层ml22可以包括按如下顺序层叠的第一反铁电层afe1、第一高k电介质层hk1、第二反铁电层afe2、高带隙层hbg、第二高k电介质层hk2、第三反铁电层afe3、泄漏阻挡层lbl和界面控制层icl。

[0170]

第一反铁电层afe1可以位于第一电极be和第一高k电介质层hk1之间。第二反铁电层afe2可以位于第一高k电介质层hk1和高带隙层hbg之间。第三反铁电层afe3可以位于第二高k电介质层hk2和泄漏阻挡层lbl之间。高带隙层hbg可以位于第二反铁电层afe2和第二高k电介质层hk2之间。

[0171]

参考图13,电容器c23可以包括第一电极be、第二电极te和位于第一电极be和第二电极te之间的多层叠层ml23。多层叠层ml23可以包括至少一个反铁电层afe1、afe2和afe3以及至少一个高k电介质层hk1和hk2。多层叠层ml23可以进一步包括泄漏阻挡层lbl和界面控制层icl。根据本发明的另一实施例,可以省略多层叠层ml23的泄漏阻挡层lbl和界面控制层icl。

[0172]

多层叠层ml23可以包括按如下顺序层叠的第一反铁电层afe1、高k电介质层hk1、第二反铁电层afe2、高带隙层hbg、第三反铁电层afe3、第二高k电介质层hk2、泄漏阻挡层lbl和界面控制层icl。

[0173]

第一反铁电层afe1可以位于第一电极be和第一高k电介质层hk1之间。第二反铁电层afe2可以位于第一高k电介质层hk1和高带隙层hbg之间。第三反铁电层afe3可以位于高带隙层hbg和第二高k电介质层hk2之间。高带隙层hbg可以位于第二反铁电层afe2和第三反铁电层afe3之间。

[0174]

参考图14,电容器c24可以包括第一电极be、第二电极te、以及在第一电极be和第

二电极te之间的多层叠层ml24。多层叠层ml24可以包括至少一个反铁电层afe1、afe2、afe3和afe4以及至少一个高k电介质层hk1和hk2。多层叠层ml24可以进一步包括泄漏阻挡层lbl和界面控制层icl。根据本发明的另一实施例,可以省略多层叠层ml24的泄漏阻挡层lbl和界面控制层icl。

[0175]

多层叠层ml24可以包括按如下顺序层叠的第一反铁电层afe1、第一高k电介质层hk1、第二反铁电层afe2、高带隙层hbg、第三反铁电层afe3、第二高k电介质层hk2、第四反铁电层afe4、泄漏阻挡层lbl和界面控制层icl。

[0176]

第一反铁电层afe1可以位于第一电极be和第一高k电介质层hk1之间。第二反铁电层afe2可以位于第一高k电介质层hk1和高带隙层hbg之间。第三反铁电层afe3可以位于高带隙层hbg和第二高k电介质层hk2之间。第四反铁电层afe4可以位于第二高k电介质层hk2和泄漏阻挡层lbl之间。高带隙层hbg可以位于第二反铁电层afe2和第三反铁电层afe3之间。

[0177]

第一反铁电层afe1、第二反铁电层afe2、第三反铁电层afe3和第四反铁电层afe4可以由铪(hf)和锆(zr)制成或包括铪(hf)和锆(zr)。第一反铁电层afe1、第二反铁电层afe2、第三反铁电层afe3和第四反铁电层afe4可以由反铁电性铪锆氧化物制成或包括反铁电性铪锆氧化物。

[0178]

第一反铁电层afe1、第二反铁电层afe2、第三反铁电层afe3、第四反铁电层afe4可以是不同材料的反铁电性铪锆氧化物。

[0179]

根据本发明的另一实施例,第一反铁电层afe1、第二反铁电层afe2、第三反铁电层afe3和第四反铁电层afe4可以包括相同的反铁电材料,并且它们可以具有相同的厚度或不同的厚度。

[0180]

根据本发明的另一实施例,第一反铁电层afe1、第二反铁电层afe2、第三反铁电层afe3和第四反铁电层afe4可以包括不同的反铁电材料,并且它们可以具有相同的厚度或不同的厚度。

[0181]

根据本发明的另一实施例,第一反铁电层afe1、第二反铁电层afe2、第三反铁电层afe3和第四反铁电层afe4可以是具有相同氧化铪含量的反铁电性铪锆氧化物。

[0182]

根据本发明的另一实施例,第一反铁电层afe1、第二反铁电层afe2、第三反铁电层afe3和第四反铁电层afe4可以是具有不同氧化铪含量的反铁电性铪锆氧化物。

[0183]

参考图15,电容器c25可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml25。多层叠层ml25可以包括至少一个反铁电层afe1、afe2和afe3以及至少一个高k电介质层hk1、hk2和hk3。多层叠层ml25可以进一步包括泄漏阻挡层lbl和界面控制层icl。根据本发明的另一实施例,可以省略多层叠层ml25的泄漏阻挡层lbl和界面控制层icl。

[0184]

多层叠层ml25可以包括按如下顺序层叠的第一反铁电层afe1、第一高k电介质层hk1、第二反铁电层afe2、高带隙层hbg、第二高k电介质层hk2、第三反铁电层afe3、第三高k电介质层hk3、泄漏阻挡层lbl和界面控制层icl。

[0185]

第一反铁电层afe1可以位于第一电极be和第一高k电介质层hk1之间。第二反铁电层afe2可以位于第一高k电介质层hk1和高带隙层hbg之间。第三反铁电层afe3可以位于第二高k电介质层hk2和第三高k电介质层hk3之间。高带隙层hbg可以位于第二反铁电层afe2

和第二高k电介质层hk2之间。

[0186]

参考图1至图15,反铁电层afe1、afe2、afe3和afe4可以包括暴露于随后的退火工艺来改善结晶度的材料。反铁电层afe1、afe2、afe3和afe4可以通过退火工艺具有四方晶体结构。四方晶体结构可以具有比其它晶体结构(例如,非晶系或单斜晶系)大的介电常数。

[0187]

参考图1至图10,所有的反铁电层afe1和afe2可以由富氧化铪的铪锆氧化物形成。参考图11至图13和图15,反铁电层afe1、afe2和afe3可以全部由富氧化铪的铪锆氧化物形成。在图14中,反铁电层afe1、afe2、afe3和afe4可以全部由富铪四水合物(hafnium tetrahydrate)的铪锆氧化物形成。

[0188]

图16a示出了根据本发明的另一实施例的半导体器件。

[0189]

参考图16a,半导体器件200可以包括电容器c26。电容器c26可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml26。多层叠层ml26可以包括一个富氧化铪的铪锆氧化物层hr

‑

hzo和至少一个高k电介质层hk1和hk2。

[0190]

多层叠层ml26可以包括按如下顺序层叠的第一高k电介质层hk1、富氧化铪的铪锆氧化物层hr

‑

hzo和第二高k电介质层hk2。富氧化铪的铪锆氧化物层hr

‑

hzo可以位于第一高k电介质层hk1和第二高k电介质层hk2之间。富氧化铪的铪锆氧化物层hr

‑

hzo可以比图1至图15的反铁电层afe1、afe2、afe3和afe4厚。富氧化铪的铪锆氧化物层hr

‑

hzo可以比第一高k电介质层hk1和第二高k电介质层hk2厚。富氧化铪的铪锆氧化物层hr

‑

hzo可以具有约至的厚度,并且其可以表现出铁电性。

[0191]

请参考表1,当富氧化铪的铪锆氧化物层hr

‑

hzo的厚度为约或更大时,富氧化铪的铪锆氧化物层hr

‑

hzo可以表现出铁电性。富铪四水合物的铁电性铪锆氧化物层hr

‑

hzo可以发挥负电容效应。

[0192]

当将常规电介质材料和铁电材料层叠时,可以获得负电容效应,它可以指获得比单独的电介质材料的电容更大的电容的效应。负电容效应可以在反铁电材料和铁电材料中实现,但在铁电材料中可能比反铁电材料更容易实现。因此,为了保证铪锆氧化物的铁电特性,使氧化铪的含量大于氧化锆的含量是有利的。

[0193]

根据本发明的实施例,富氧化铪的铪锆氧化物层hr

‑

hzo可以有利地实现负电容效应,因此,通过富氧化铪的铪锆氧化物层hr

‑

hzo与第一和第二高k电介质层hk1和hk2的联用,可以进一步提高电容器c26的电容。富氧化铪的铪锆氧化物层hr

‑

hzo可称为负电容材料层或负电容铁电材料层。

[0194]

为了获得负电容效应,根据本发明的另一实施例,富氧化铪的铪锆氧化物层hr

‑

hzo可以用基础铪锆氧化物b

‑

hzo代替。再参考表1,其中氧化铪含量和氧化锆含量相同的基础铪锆氧化物在其厚度大于时,可以表现出铁电性。因此,可获得负电容效应。

[0195]

图16b和16c示出了根据本发明的另一实施例的电容器。图16b和16c是图16a中所示的电容器c26的改进。在下文中,可以省略对于同样出现在图16a的构成元件的详细描述。

[0196]

参考图16b,电容器c26a可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml26a。多层叠层ml26a可以包括一个富氧化铪的铪锆氧化物层hr

‑

hzo和一个高k电介质层hk1。

[0197]

多层叠层ml26a可以包括按下述顺序层叠的第一高k电介质层hk1和富氧化铪的铪

锆氧化物层hr

‑

hzo。第一高k电介质层hk1可以直接接触第一电极be,富氧化铪的铪锆氧化物层hr

‑

hzo可以直接接触第二电极te。富氧化铪的铪锆氧化物层hr

‑

hzo可以比第一高k电介质层hk1厚。富氧化铪的铪锆氧化物层hr

‑

hzo可以具有约至的厚度,并且可以表现出铁电性。

[0198]

参考图16c,电容器c26b可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml26b。多层叠层ml26b可以包括一个富氧化铪的铪锆氧化物层hr

‑

hzo和一个高k电介质层hk2。

[0199]

多层叠层ml26b可以包括按下述顺序层叠的富氧化铪的铪锆氧化物层hr

‑

hzo和第二高k电介质层hk2。第二高k电介质层hk2可以直接接触第二电极te,富氧化铪的铪锆氧化物层hr

‑

hzo可以直接接触第一电极be。富氧化铪的铪锆氧化物层hr

‑

hzo可以具有约至的厚度,并且可以表现出铁电性。

[0200]

图17a示出了根据本发明的另一实施例的电容器。图17a中所示的电容器c27可以类似于图16a的电容器c26。在下文中,可以省略对于同样出现在图16a中的构成元件的详细描述。

[0201]

电容器c27可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml27。多层叠层ml27可以包括一个富氧化铪的铪锆氧化物层hr

‑

hzo和至少一个高k电介质层hk1和hk2。多层叠层ml27可以进一步包括泄漏阻挡层lbl和界面控制层icl。

[0202]

多层叠层ml27可以包括第一高k电介质层hk1、富氧化铪的铪锆氧化物层hr

‑

hzo、第二高k电介质层hk2、泄漏阻挡层lbl和界面控制层icl。富氧化铪的铪锆氧化物层hr

‑

hzo可以位于第一高k电介质层hk1和第二高k电介质层hk2之间。可以通过富氧化铪的铪锆氧化物层hr

‑

hzo获得负电容效应。

[0203]

泄漏阻挡层lbl和界面控制层icl可以位于第二高k电介质层hk2和第二电极te之间。泄漏阻挡层lbl可以位于第二高k电介质层hk2和界面控制层icl之间。界面控制层icl可以位于泄漏阻挡层lbl和第二电极te之间。对于泄漏阻挡层lbl和界面控制层icl的描述,可以参考图2和随附的说明。

[0204]

图17b和17c示出了根据本发明的另一实施例的电容器,图17b和17c是图17a中所示的电容器c27的改进。在下文中,可以省略对于同样出现在图17a中的构成元素的详细描述。

[0205]

参考图17b,电容器c27a可以包括第一电极be、第二电极te、以及位于第一电极be和第二电极te之间的多层叠层ml27a。多层叠层ml27a可以包括一个富氧化铪的铪锆氧化物层hr

‑

hzo和一个高k电介质层hk1。多层叠层ml27a可以进一步包括泄漏阻挡层lbl和界面控制层icl。

[0206]

多层叠层ml27a可以以第一高k电介质层hk1、富氧化铪的铪锆氧化物层hr

‑

hzo、泄漏阻挡层lbl和界面控制层icl的顺序层叠而成。富氧化铪的铪锆氧化物层hr

‑

hzo可以位于第一高k电介质层hk1和泄漏阻挡层lbl之间。

[0207]

参考图17c,电容器c27b可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml27b。多层叠层ml27b可以包括一个富氧化铪的铪锆氧化物层hr

‑

hzo和一个高k电介质层hk2。多层叠层ml27b可以进一步包括泄漏阻挡层lbl和界面控制

层icl。

[0208]

多层叠层ml27b可以包括按下述顺序层叠的富氧化铪的铪锆氧化物层hr

‑

hzo和第二高k电介质层hk2、泄漏阻挡层lbl和界面控制层icl。富氧化铪的铪锆氧化物层hr

‑

hzo可以位于第一电极be和第二高k电介质层hk2之间。

[0209]

根据本发明的另一实施例,多层叠层ml26、ml26a、ml26b、ml27、ml27a和ml27b可以通过将多个负电容材料层(例如,富氧化铪的铪锆氧化物层)和多个高k电介质层交替层叠来形成。在这种情况下,负电容材料层可以比高k电介质层厚。

[0210]

图16a至图17c的富氧化铪的铪锆氧化物层hr

‑

hzo的厚度和图1至图15的反铁电层afe1、afe2、afe3和afe4的厚度可以彼此不同。图1至图15的反铁电层afe1、afe2、afe3和afe4的厚度可以是约或更小,而图16a至图17c的富氧化铪的铪锆氧化物层hr

‑

hzo的厚度可以是约至图16a至图17c的富氧化铪的铪锆氧化物层hr

‑

hzo的厚度可以比图1至图15的反铁电层afe1、afe2、afe3和afe4厚。

[0211]

根据本发明的另一实施例,当图1至图15的反铁电层afe1、afe2、afe3和afe4包括富氧化铪的铪锆氧化物层时,可获得负电容效应。

[0212]

参考图1至图17c,多层叠层ml11至ml27b可以具有相同的高度(或厚度)。

[0213]

图18是描述沉积富氧化铪的铪锆氧化物层hr

‑

hzo的方法示例的流程图。

[0214]

富氧化铪的铪锆氧化物层hr

‑

hzo可以通过原子层沉积(ald)来沉积。富氧化铪的铪锆氧化物层hr

‑

hzo的原子层沉积(ald)可以通过在约250℃至380℃的温度下重复多个循环来执行。在此,该循环可以包括用于沉积氧化锆层(zro2)的第一循环z1和用于沉积氧化铪层(hfo2)的第二循环h1。可以通过将第一循环z1重复a次来沉积氧化锆层,并可以通过将第二循环h1重复b次来沉积氧化铪层。在此,a和b可以是不同的自然数。b可以大于a。例如,a可以为1至10,b可以大于10。通过使b大于a,可以使氧化铪层比氧化锆层沉积得要厚,相应地,可以沉积富氧化铪的铪锆氧化物层hr

‑

hzo。

[0215]

第一循环z1可以包括zr源吸附操作(s1)、吹扫操作(s2)、反应气体供给操作(s3)和吹扫未反应气体的操作(s4)。第一循环(z1)可以重复a次。可以在第一循环z1中沉积氧化锆层。

[0216]

第二循环h1可以包括铪(hf)源吸附操作(s11)、吹扫操作(s12)、反应气体供给操作(s13)和吹扫未反应气体的操作(s14)。第二循环h1可以重复b次。可以在第二循环h1中沉积氧化铪层。

[0217]

锆(zr)源可以包括temaz(四(乙基甲基氨基)锆)、tdmaz(四(二甲氨基)锆)等。

[0218]

铪(hf)源可以包括temah(四(乙基甲基氨基)铪)、tdeah(四(二乙氨基)铪)、tdmah(四(二甲氨基)铪)等。

[0219]

反应气体可以包括氧化剂,并且氧化剂可以包括o3、o2、h2o、h2o2、o2等离子体或其组合。当臭氧(o3)被用作氧化剂时,可以优化并供给臭氧的浓度和流速。例如,臭氧的浓度可以为约50g/m3至310g/m3的范围,并且臭氧的流速可以为约100sccm至5000sccm的范围。吹扫操作可以在约1秒至100秒的范围内足够长时间地进行。

[0220]

根据本发明的另一实施例,可以通过使a和b相同,并使铪(hf)源的流速大于锆(zr)源的流速来沉积富氧化铪的铪锆氧化物层hr

‑

hzo。

[0221]

根据本发明的另一实施例,可以通过使a和b相同,并使铪(hf)源的供给时间长于

锆(zr)源的供给时间来沉积富氧化铪的铪锆氧化物层hr

‑

hzo。

[0222]

为了获得反铁电性,可以以小于约的厚度来沉积富氧化铪的铪锆氧化物层hr

‑

hzo。

[0223]

为了获得铁电性,可以将富氧化铪的铪锆氧化物层hr

‑

hzo沉积为约或更大的厚度。

[0224]

在对富氧化铪的铪锆氧化物层hr

‑

hzo进行原子层沉积后,可以使富氧化铪的铪锆氧化物层hr

‑

hzo暴露于后续的退火工艺。通过后续的退火工艺,可以改善富氧化铪的铪锆氧化物层hr

‑

hzo的结晶度,从而提高介电常数。

[0225]

图19是描述沉积富氧化铪的铪锆氧化物层hr

‑

hzo的方法的另一个示例的流程图。

[0226]

富氧化铪的铪锆氧化物层hr

‑

hzo可以通过原子层沉积(ald)来沉积,并且富氧化铪的铪锆氧化物层hr

‑

hzo的原子层沉积(ald)可以在约250℃至380℃下通过重复单元循环hz来执行。在此,单元循环hz可以包括锆(zr)源吸附操作(s21)、吹扫操作(s22)、铪(hf)源吸附操作(s23)、吹扫操作(s24)、反应气体供给操作(s25)、吹扫未反应气体的操作(s26),并且该单元循环hz可以重复c次。

[0227]

锆(zr)源可以包括temaz(四(乙基甲基氨基)锆)、tdmaz(四(二甲氨基)锆)等。

[0228]

铪(hf)源可以包括temah(四(乙基甲基氨基)铪)、tdeah(四(二乙氨基)铪)、tdmah(四(二甲氨基)铪)等。

[0229]

反应气体可以包括氧化剂,并且氧化剂可以包括o3、o2、h2o、h2o2、o2等离子体或其组合。当臭氧(o3)被用作氧化剂时,可以优化并供给臭氧的浓度和流速。例如,臭氧的浓度可以为约50g/m3至310g/m3的范围,并且臭氧的流速可以为约100sccm至5000sccm的范围。任何未反应气体的吹扫操作可以足够长,并且例如可以为大约1秒至100秒的范围。

[0230]

在单元循环hz中,可以通过使铪(hf)源的流速大于锆(zr)源的流速,沉积富氧化铪的铪锆氧化物层hr

‑

hzo。根据本发明的另一实施例,可以通过使铪(hf)源的供应时间长于锆(zr)源的供应时间来沉积富氧化铪的铪锆氧化物层hr

‑

hzo。

[0231]

在执行富氧化铪的铪锆氧化物层hr

‑

hzo的原子层沉积之后,可以使富氧化铪的铪锆氧化物层hr

‑

hzo暴露于随后的退火工艺。通过随后的退火工艺,可以改善富氧化铪的铪锆氧化物层hr

‑

hzo的结晶度。

[0232]

图20是示出根据本发明另一实施例的半导体器件300的剖视图。

[0233]

参考图20,半导体器件300可以包括电容器c28。电容器c28可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml28。多层叠层ml28可以包括至少一个反铁电层afe1和afe2以及至少一个高k电介质层hk1和hk2。多层叠层ml28可以进一步包括泄漏阻挡层lbl和界面控制层icl。根据本发明的另一实施例,可以省略多层叠层ml28的泄漏阻挡层lbl和界面控制层icl。电容器c28可以类似于图2的电容器c12。在下文中,可以省略对于同样出现在图2中的构成元件的详细描述。

[0234]

多层叠层ml28可以进一步包括增强层(booster layer)kbl。增强层kbl可以直接接触第一反铁电层afe1。增强层kbl可以形成在第一反铁电层afe1的下方。增强层kbl可以位于第一高k电介质层hk1和第一反铁电层afe1之间。增强层kbl可以直接接触第一高k电介质层hk1。

[0235]

增强层kbl可以提升第一反铁电层afe1的介电常数。换句话说,增强层kbl可用作

介电常数增强件(可称为k增压件)。增强层kbl可以增大第一反铁电层afe1的介电常数。增强层kbl还可以用作极化增强层,其增强第一反铁电层afe1的极化。增强的极化可以进一步提高第一反铁电层afe1的介电常数。

[0236]

增强层kbl可以由金属制成或包括金属。增强层kbl的金属可以包括二价金属、三价金属或五价金属。二价金属和三价金属可以具有高电子亲和力。

[0237]

增强层kbl可以含有金属。增强层kbl可以包括选自铌、钽和钒中的至少一种。增强层kbl可以由金属氧化物制成或包括金属氧化物。根据本发明的另一实施例,增强层kbl可以是金属氮氧化物。增强层kbl可以包括氧化铌、氮氧化铌、氧化钽、氮氧化钽、氧化钒或氮氧化钒。

[0238]

如上所述,增强层kbl可以含有金属和氧。另外,增强层kbl可以含有金属、氧和氮。为了提升第一反铁电层afe1的介电常数,可以调整增强层kbl的氧含量和氮含量。例如,当增强层kbl中含有金属氧化物时,氧含量可以在约1at%至50at%的范围内调整。当增强层kbl含有金属氮氧化物时,氧含量可以大于氮含量,并且氧和氮的总含量可以为约60at%至70at%的范围。通过控制增强层kbl的氧含量,有利于提升第一反铁电层afe1的介电常数。

[0239]

增强层kbl可以具有约至的厚度。

[0240]

根据本发明的另一实施例,增强层kbl也可以位于第二反铁电层afe2的下方。

[0241]

根据本发明的另一实施例,增强层kbl可以位于第一反铁电层afe1和第二反铁电层afe2中一个反铁电层的下方。

[0242]

参考图1至17c,多层叠层可以包括至少一个增强层kbl。增强层kbl可以位于反铁电层afe1、afe2、afe3和afe4或富铪的铪锆氧化物层hr

‑

hzo的下方。

[0243]

图21至22b是示出存储单元的剖视图。图22a是沿图21中的线a

‑

a’截取的剖视图。图22b是沿图21中的线b

‑

b’截取的剖视图。

[0244]

存储单元400可以包括单元晶体管,所述单元晶体管包括掩埋字线508、位线514和电容器600。电容器600可以包括多层叠层,该多层叠层可以包括上述本发明实施例中的多层叠层ml11至ml28中的一种。

[0245]

可以详细描述存储单元400。

[0246]

隔离层503和有源区504可以形成在衬底501中。可以由隔离层503限定多个有源区504。衬底501可以由适合于半导体加工的材料制成。衬底501可以包括半导体衬底。衬底501可以由含硅的材料形成。衬底501可以包括硅、单晶硅、多晶硅、非晶硅、硅锗、单晶硅锗、多晶硅锗、掺杂碳的硅、它们的组合或其多层。衬底501还可以包括其他半导体材料如锗。衬底501可以包括第iii/v族半导体衬底,例如复合半导体衬底,例如gaas。衬底501可以包括绝缘体上硅(soi)衬底。隔离层503可以通过浅沟槽隔离(sti)工艺形成在隔离沟槽502中。

[0247]

字线沟槽506可以形成在衬底501中。字线沟槽506可以被称为栅极沟槽。可以在字线沟槽506的表面上形成栅极电介质层507。部分填充字线沟槽506的掩埋字线508可以形成在栅极电介质层507上方。掩埋字线508可以称为掩埋栅电极。可以在掩埋字线508上方形成字线覆盖层509。掩埋字线508的上表面可以位于比衬底501的表面低的水平上。掩埋字线508可以是低电阻金属材料。可以通过依次层叠氮化钛和钨来形成掩埋字线508。根据本发明的另一实施例,掩埋字线508可以仅由氮化钛(仅tin)形成。

[0248]

第一和第二杂质区510和511可以形成在衬底501中。第一和第二杂质区510和511

可以通过字线沟槽506彼此间隔开。第一和第二杂质区510和511可以被称为第一和第二源/漏极区。第一和第二杂质区510和511可以包括n型杂质如砷(as)或磷(p)。因此,掩埋字线508和第一和第二杂质区510和511可以成为单元晶体管。掩埋字线508可以改善单元晶体管的短沟道效应。

[0249]

位线接触插塞513可以形成在衬底501上方。位线接触插塞513可以与第一杂质区510耦接。位线接触插塞513可以位于位线接触孔512中。位线接触孔512可以形成在硬掩模层505中。硬掩模层505可以形成在衬底501上方。位线接触孔512可以暴露第一杂质区510。位线接触插塞513的下表面可以低于衬底501的上表面。位线接触插塞513可以由多晶硅或金属材料形成。位线接触插塞513的一部分可以具有小于位线接触孔512的直径的线宽。位线514可以形成在位线接触插塞513上方。位线硬掩模515可以形成在位线514上方。位线514和位线硬掩模515的层叠结构可称为位线结构bl。位线514可以具有在与掩埋字线508交叉的方向上延伸的线形状。位线514的一部分可以与位线接触插塞513耦接。位线514可以由金属材料制成或包括金属材料。位线硬掩模515可以包括电介质材料。

[0250]

位线间隔件516可以形成在位线结构bl的侧壁上。位线间隔件516的底部可以延伸至形成在位线接触插塞513的两侧。位线间隔件516可以包括氧化硅、氮化硅或其组合。根据本发明的另一实施例,位线间隔件516可以包括气隙。例如,它可以是气隙位于氮化硅其间的nan(氮化物

‑

气隙

‑

氮化物)结构。

[0251]

储存节点接触插塞snc可以形成在相邻的位线结构bl之间。储存节点接触插塞snc可以形成在储存节点接触孔518中。储存节点接触插塞snc可以与第二杂质区511耦接。储存节点接触插塞snc可以包括下插塞519和上插塞521。储存节点接触插塞snc可以进一步包括在下插塞519和上插塞521之间的欧姆接触层520。欧姆接触层520可以由金属硅化物制成或包括金属硅化物。上插塞521可以由金属材料制成或包括金属材料,而下插塞519可以包括含硅的材料。

[0252]

从平行于位线结构bl的方向(图21中线c

‑

c’的方向)来看,可以在相邻的储存节点接触插塞snc之间形成插塞隔离层517。插塞隔离层517可以形成在相邻的位线结构bl之间,并且可以与硬掩模层505一起提供储存节点接触孔518。

[0253]

电容器600可以与储存节点接触插塞snc耦接。

[0254]

图23a至23f是示出存储单元的电容器600的应用的剖视图。

[0255]

参考图23a,电容器611可以包括底电极601、顶电极602,以及在底电极601和顶电极602之间的多层叠层603。底电极601可以具有圆筒形状。多层叠层603可以形成在底电极601上方,并且顶电极602可以形成在多层叠层603上方。多层叠层603可以对应于上述本发明实施例中的多层叠层ml11至ml28中的一种。因此,多层叠层603可以包括至少一个反铁电层。

[0256]

在下文中,在图23b至图23f中可以省略对于同样出现在图23a中的构成元件的详细描述。

[0257]

参考图23b,电容器612可以包括圆筒形的底电极601、多层叠层603和顶电极602。电容器612可以进一步包括支撑件600s。支撑件600s可以是支撑底电极601外壁的结构。支撑件600s可以包括氮化硅。

[0258]

参考图23c和图23d,电容器613和614可以包括柱状的底电极601p、多层叠层603和

顶电极602。图23d的电容器614可以进一步包括支撑件600s。

[0259]

参考图23e和图23f,电容器615和616可以包括底电极601l、多层叠层603和顶电极602。图23f的电容器616可以进一步包括支撑件600s。底电极601l可以具有其中融合了柱形状和圆筒形状的混合结构。如上所述,柱形状和圆筒形状的混合结构可以称为柱筒形状(pylinder)或混合形状。

[0260]

如上所述,通过将多层叠层603形成为包括至少一个反铁电层,可以获得具有高介电常数和低泄漏电流的多层叠层603。因此,可以制造具有改善的刷新特性和可靠性的高度集成的dram存储单元。

[0261]

根据本发明上述实施例的电介质层叠层可以应用于dram的外围电路。例如,dram可以包括含存储单元(参见图22a中的400)的存储单元区域和含外围晶体管的外围电路区域。存储单元400的电容器600和外围晶体管中的至少一个可以包括本发明上述实施例的多层叠层ml11至ml28中的一个多层叠层。

[0262]

根据本发明上述实施例的多层叠层ml11至ml28可以应用于金属

‑

绝缘体

‑

金属(mim)电容器。例如,mim电容器可以包括多层叠层,所述多层叠层包括第一金属电极、第二金属电极以及形成在第一金属电极和第二金属电极之间的至少一个反铁电层。

[0263]

根据本发明上述实施例的多层叠层可以应用于嵌入式dram。例如,嵌入式dram可以包括逻辑电路和嵌入式dram,并且嵌入式dram的电容器可以包括含至少一个反铁电层的多层叠层。

[0264]

根据本发明上述实施例的多层叠层可以应用于三维(3d)nand。例如,3d nand可以包括柱形通道层、围绕柱形通道层的字线、以及包括在柱形通道层和字线之间的至少一个反铁电层的多层叠层。

[0265]

图24是示出根据本发明的另一实施例的半导体器件的剖视图。

[0266]

参考图24,半导体器件700可以包括晶体管。半导体器件700可以包括半导体衬底701、栅极电介质层710、栅电极720、源极区740和漏极区750。栅极电介质层710可以形成在半导体衬底701上方,并且栅电极720可以形成在栅极电介质层710上方。源极区740和漏极区750可以形成在半导体衬底701中。

[0267]

栅极电介质层710可以包括根据上述实施例的多层叠层中的一种。栅极电介质层710可以包括至少一个反铁电层和至少一个高k电介质层。根据图24的实施例,栅极电介质层710可以包括按如下顺序层叠的第一高k电介质层hk1、反铁电层afe和第二高k电介质层hk2。反铁电层afe可以位于第一高k电介质层hk1和第二高k电介质层hk2之间。

[0268]

栅电极720可以是包括金属基材料的金属栅电极。例如,栅电极720可以由钨、铝、氮化钨、氮化钛、钛或其组合制成,或包括钨、铝、氮化钨、氮化钛、钛或其组合。

[0269]

源极区740和漏极区750可以包括相同导电类型的杂质。源极区740和漏极区750可以包括n型杂质或p型杂质。n型杂质可以包括磷或砷,而p型杂质可以包括硼或铟。

[0270]

根据本发明的另一实施例,在栅极电介质层710和半导体衬底701之间可以进一步形成薄界面层。在此,薄界面层可以包括氧化硅或氮氧化硅。

[0271]

根据本发明的另一实施例,栅极电介质层710可以应用于finfet的栅极电介质层。

[0272]

根据本发明的另一实施例,栅极电介质层710可以包括富氧化铪的铪锆氧化物,以获得负电容效应。例如,可以用富氧化铪的铪锆氧化物代替反铁电层afe。

[0273]

图25至27是示出根据本发明其他实施例的电容器的剖视图。

[0274]

参考图25,电容器c29可以包括第一电极be、第二电极te、以及在第一电极be和第二电极te之间的多层叠层ml29。多层叠层ml29可以包括至少一个反铁电层afe1、afe2和afe3以及至少一个高k电介质层hk1、hk2、hk3和hk4。多层叠层ml29可以进一步包括泄漏阻挡层lbl和界面控制层icl。

[0275]

多层叠层ml29可以包括按如下顺序层叠的第一高k电介质层hk1、第一反铁电层afe1、第二高k电介质层hk2、第二反铁电层afe2、第三高k电介质层hk3、第三反铁电层afe3、第四高k电介质层hk4、泄漏阻挡层lbl和界面控制层icl。

[0276]

第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3和第四高k电介质层hk4可以是同一种材料,也可以是不同的材料。

[0277]

第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3和第四高k电介质层hk4可以由氧化铪或氧化锆制成,或包括氧化铪或氧化锆。第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3和第四高k电介质层hk4可以由单层氧化铪或单层氧化锆制成。第一高k电介质层hk1和第四高k电介质层hk4可以比第二高k电介质层hk2和第三高k电介质层hk3中的每一个都薄。第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以比第一和第二高k电介质层hk1和hk2中的每一个都薄。

[0278]

第一反铁电层afe1、第二反铁电层afe2和第三反铁电层afe3可以由反铁电性铪锆氧化物afe

‑

hzo制成或包括反铁电性铪锆氧化物afe

‑

hzo。第一高k电介质层hk1和第四高k电介质层hk4可以包括薄的氧化锆,而第二高k电介质层hk2和第三高k电介质层hk3可以包括厚的氧化锆。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),并且界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。

[0279]

参考图26,电容器c30可以包括第一电极be、第二电极te以及位于第一电极be和第二电极te之间的多层叠层ml30。多层叠层ml30可以包括至少一个反铁电层afe1、afe2、afe3和afe4以及至少一个高k电介质层hk1、hk2、hk3、hk4和hk5。多层叠层ml30可以进一步包括泄漏阻挡层lbl和界面控制层icl。

[0280]

多层叠层ml30可以包括按如下顺序层叠的第一高k电介质层hk1、第一反铁电层afe1、第二高k电介质层hk2、第二反铁电层afe2、第三高k电介质层hk3。第三反铁电层afe3、第四高k电介质层hk4、第四反铁电层afe4、第五高k电介质层hk5、泄漏阻挡层lbl和界面控制层icl。

[0281]

第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3、第四高k电介质层hk4和第五高k电介质层hk5可以是同一种材料,或是不同的材料。

[0282]

第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3、第四高k电介质层hk4和第五高k电介质层hk5可以由氧化铪或氧化锆制成,或包括氧化锆或氧化锆。第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3、第四高k电介质层hk4和第五高k电介质层hk5中的每一个可以由单层氧化铪或单层氧化锆制成。第一高k电介质层hk1、第二高k电介质层hk2、第三高k电介质层hk3、第四高k电介质层hk4和第五高k电介质层hk5的厚度可以相同。第一反铁电层afe1、第二反铁电层afe2、第三反铁电层afe3和第四反铁电层afe4可以比第一至第五高k电介质层hk1至hk5中的每一个都薄。

[0283]

第一反铁电层afe1、第二反铁电层afe2、第三反铁电层afe3和第四反铁电层afe4

可以包括反铁电性铪锆氧化物afe

‑

hzo。第一至第五高k电介质层hk1至hk5可以包括薄的氧化锆。泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),并且界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。

[0284]

参考图27,电容器c31可以包括第一电极be、第二电极te以及在第一电极be和第二电极te之间的多层叠层ml31。多层叠层ml31可以包括至少一个反铁电层afe1、afe2、afe3和afe4以及至少一个高k电介质层hk1、hk2、hk3、hk4、hk5和hk6。多层叠层ml31可以进一步包括泄漏阻挡层lbl和界面控制层icl。

[0285]

多层叠层ml31可以包括第一多层叠层ml31a、第二多层叠层ml31b以及位于第一多层叠层ml31a和第二多层叠层ml31b之间的高带隙层hbg。第一多层叠层ml31a可以包括按如下顺序层叠的第一高k电介质层hk1、第一反铁电层afe1、第二高k电介质层hk2、第二反铁电层afe2和第三高k电介质层hk3。第二多层叠层ml31b可以包括按如下顺序层叠的第四高k电介质层hk4、第三反铁电层afe3、第五高k电介质层hk5、第四反铁电层afe4和第六高k电介质层hk6。

[0286]

在第一多层叠层ml31a中,第二高k电介质层hk2可以比第一和第三高k电介质层hk1和hk3中的每一个都厚。第一高k电介质层hk1、第一反铁电层afe1、第二反铁电层afe2和第三高k电介质层hk3可以具有相同的厚度。

[0287]

在第二多层叠层ml31b中,第五高k电介质层hk5可以比第四和第六高k电介质层hk4和hk6厚。第四高k电介质层hk4、第三反铁电层afe3、第四反铁电层afe4和第六高k电介质层hk6可以具有相同的厚度。

[0288]

第一至第六高k电介质层hk1至hk6可以由同一种材料制成,或者可以由不同的材料制成。第一至第六高k电介质层hk1至hk6可以由氧化铪或氧化锆制成,或包括氧化铪或氧化锆。第一至第六高k电介质层hk1至hk6可以由单层氧化铪或单层氧化锆制成。

[0289]

第一反铁电层afe1、第二反铁电层afe2、第三反铁电层afe3和第四反铁电层afe4可以由反铁电性铪锆氧化物afe

‑

hzo制成或包括反铁电性铪锆氧化物afe

‑

hzo。

[0290]

泄漏阻挡层lbl可以由氧化铝(al2o3)制成或包括氧化铝(al2o3),界面控制层icl可以由氧化钛(tio2)制成或包括氧化钛(tio2)。高带隙层hbg可以由氧化铝(al2o3)或掺杂铝的氧化锆(掺杂al的zro2)制成,或包括氧化铝(al2o3)或掺杂铝的氧化锆(掺杂al的zro2)。

[0291]

图23a至图23f的多层叠层603可以包括图25至图27的多层叠层ml29至ml31中的一个多层叠层。

[0292]

根据本发明的实施例,由于电容器的电介质层包括至少一个反铁电层和至少一个高k电介质层,因此可以提高电容器的电容。

[0293]

由于增强层增强了介电常数,所以可以进一步提高电容器的电容。

[0294]

虽然已经就具体的实施例描述了本发明,但对于本领域技术人员来说显而易见的是,在不偏离所附权利要求定义的本发明的精神和范围的情况下,可以做出各种变化和修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。