一种p型电子阻挡层结构及其led外延结构和制备方法

技术领域

1.本发明涉及发光二极管技术领域,具体涉及一种p型电子阻挡层结构及其led外延结构和制备方法。

背景技术:

2.发光二极管(led)是一种常用的发光器件,通过电子与空穴复合释放能量发光,它在照明领域应用广泛。发光二极管可高效地将电能转化为光能,在现代社会具有广泛的用途,如照明、平板显示、医疗器件等。随着led技术不断发展,在其受到越来越广泛的应用的同时,也面临着越来越高的要求,尤其是led的发光效率和抗静电性能。

3.目前,led的发光效率仍然不高,特别是随着芯片尺寸的减小,电流密度越来越大,电子具有较低的有效质量和较高的迁移率,更容易从有源发光层溢出到p型层并与空穴复合,从而降低了发光效率。因此研究人员通常设计电子阻挡层,实现对电子的阻挡。但是电子阻挡层的设计使其与p型gan层的材料界面产生了严重晶格失配和大的应力,使发光层具有较大的畸变,从而影响了led的发光效率和抗静电性能。

4.因此,需对现有技术进一步改善。

技术实现要素:

5.有鉴于此,有必要针对上述的问题,提供一种p型电子阻挡层结构及其led外延结构和制备方法。能够改善电子阻挡层与p型gan层之间晶格失配和应力过大的问题,从而提高led的发光效率和抗静电性能。

6.为实现上述目的,本发明采取以下的技术方案:

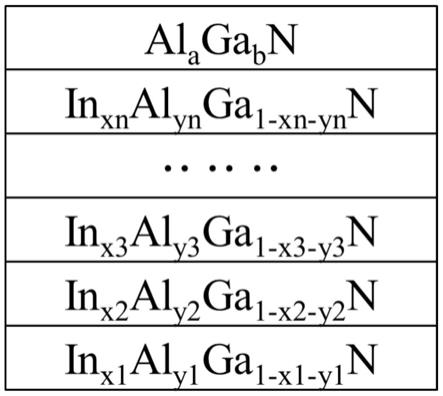

7.第一方面,本发明提供一种p型电子阻挡层结构,所述p型电子阻挡层结构从下至上包括多周期的p型in

xn

al

yn

ga1‑

xn

‑

yn

n层和p型al

a

ga

b

n层,1<n≤6。

8.进一步的,在上述p型电子阻挡层结构中,p型in

xn

al

yn

ga1‑

xn

‑

yn

n层中in组分含量随着周期数n的增加而减少,p型in

xn

al

yn

ga1‑

xn

‑

yn

n层中al组分含量随着周期数n的增加而增加;a>yn。

9.进一步的,在上述p型电子阻挡层结构中,in

xn

al

yn

ga1‑

xn

‑

yn

n层的厚度随着周期数n的增加而增加;p型al

a

ga

b

n层的厚度大于p型in

xn

al

yn

ga1‑

xn

‑

yn

n层的厚度。

10.进一步的,在上述p型电子阻挡层结构中,多周期的p型in

xn

al

yn

ga1‑

xn

‑

yn

n层的总厚度为5~20nm,in组分为0

‑

15%。

11.进一步的,在上述p型电子阻挡层结构中,p型al

a

ga

b

n层的厚度为5~50nm,al组分为0

‑

30%。

12.进一步的,在上述p型电子阻挡层结构中,p型电子阻挡层中掺杂mg,mg掺杂浓度为5e18/cm3~5e19/cm3。

13.第二方面,本发明提供一种led外延结构,所述led外延结构从下至上包括衬底、缓冲层、本征gan层、n型gan层、量子阱发光层、上述的p型电子阻挡层和p型gan层。

14.进一步的,在上述led外延结构中,所述衬底包括但不限于蓝宝石、蓝宝石aln薄膜、gan、硅、碳化硅。

15.进一步的,在上述led外延结构中,所述缓冲层为gan、algan、inalgan、ingan的单层结构或其组合。

16.进一步的,在上述led外延结构中,所述n型gan层掺杂si,si掺杂浓度为1e18/cm3~3e19/cm3。

17.进一步的,在上述led外延结构中,所述量子阱发光层为多周期的gan/ingan超晶格结构,gan/ingan超晶格结构的周期数为3~10。

18.优选的,在上述led外延结构中,gan为势垒层,ingan为势阱层;ingan中in的组分含量为5%~20%。

19.进一步的,在上述led外延结构中,p型gan层掺杂mg或zn,掺杂浓度为5e18/cm3~1e20/cm3。

20.第三方面,本发明提供led外延结构的制备方法,包括以下步骤:

21.步骤s1:制备衬底,在衬底上生长缓冲层;所述缓冲层生长温度为800~1050℃,生长厚度为300~1000nm,生长压力为80~250torr;

22.步骤s2:在缓冲层上生长本征gan层;所述本征gan层生长温度为1050~1200℃,生长厚度为0.5~1μm,生长压力为100~350torr;

23.步骤s3:在本征gan层上生长n型gan层;所述n型gan层生长温度为1000~1200℃,生长厚度为1~4μm,生长压力为100~300torr;

24.步骤s4:在n型gan层上生长量子阱发光层;量子阱发光层的生长温度为700~900℃,生长压力为100~300torr;单一周期内,gan势垒层的生长厚度为1.0~10.0nm,ingan势阱层的生长厚度为1.0~6.0nm;

25.步骤s5:在量子阱发光层上生长p型电子阻挡层;p型电子阻挡层的生长温度为900~950℃,生长压力为100~300torr,生长厚度为25~60nm;

26.步骤s6:在p型电子阻挡层上生长p型gan层;p型gan层的生长温度为850

‑

950℃,生长厚度为70~180nm,生长压力为300~600torr。

27.第四方面,本发明提供上述p型电子阻挡层结构、led外延结构、led外延结构的制备方法在制备发光二极管或半导体器件中的应用。

28.本发明的有益效果为:

29.(一)本发明提供的p型电子阻挡层结构从下至上包括多周期的p型in

xn

al

yn

ga1‑

xn

‑

yn

n层和p型al

a

ga

b

n层,其中1<n≤6。该结构可以调节应力,改善材料界面的晶格失配,减小发光层能带发生的畸变,提高电子和空穴复合效率。

30.(二)本发明提供的led外延结构和制备方法,使得制成的led外延结构具有提高空穴注入、调配应力、调节能带以及改善晶格失配的作用,提高了led发光效率和抗静电性能。

附图说明

31.图1是本发明p型电子阻挡层结构的结构示意图;

32.图2是本发明实施例1的led外延结构的结构示意图;

33.图3是本发明对比例1的led外延结构的结构示意图。

具体实施方式

34.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明实施例,对本发明的技术方案作进一步清楚、完整地描述。需要说明的是,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

35.实施例1

36.一种led外延结构,从下至上包括衬底、缓冲层、本征gan层、n型gan层、量子阱发光层、p型电子阻挡层和p型gan层;其中,p型电子阻挡层结构,从下至上包括周期数为n=2的p型in

xn

al

yn

ga1‑

xn

‑

yn

n层和p型al

a

ga

b

n层;即所述p型电子阻挡层结构从下至上包括p型in

0.1

al

0.1

ga

0.8

n层、p型in

0.05

al

0.15

ga

0.8

n层和p型al

0.2

ga

0.8

n层;p型al

a

ga

b

n层中a=0.2,b=0.8。

37.所述led外延结构的制备方法,包括以下步骤:

38.步骤s1:制备衬底,在衬底上生长缓冲层;所述缓冲层生长温度为950℃,生长厚度为500nm,生长压力为100torr;

39.步骤s2:在缓冲层上生长本征gan层;所述本征gan层生长温度为1100℃,生长厚度为0.8μm,生长压力为250torr;

40.步骤s3:在本征gan层上生长n型gan层;所述n型gan层生长温度为1100℃,生长厚度为2μm,生长压力为200torr;

41.步骤s4:在n型gan层上生长量子阱发光层;量子阱发光层的生长温度为800℃,生长压力为200torr;单一周期内,gan势垒层的生长厚度为5.0nm,ingan势阱层的生长厚度为4.0nm;

42.步骤s5:在量子阱发光层上生长p型电子阻挡层;p型电子阻挡层的生长温度为900℃,生长压力为200torr,其中p型in

xn

al

yn

ga1‑

xn

‑

yn

n层总厚度为10nm,其中p型in

0.1

al

0.1

ga

0.8

n层厚度为4nm,p型in

0.05

al

0.15

ga

0.8

n层厚度为6nm,p型al

0.2

ga

0.8

n层厚度为15nm;

43.步骤s6:在p型电子阻挡层上生长p型gan层;p型gan层的生长温度为900℃,生长厚度为120nm,生长压力为400torr。

44.实施例2

45.一种led外延结构,从下至上包括衬底、缓冲层、本征gan层、n型gan层、量子阱发光层、p型电子阻挡层和p型gan层;其中,p型电子阻挡层结构,从下至上包括周期数为n=4的p型in

xn

al

yn

ga1‑

xn

‑

yn

n层和p型al

a

ga

b

n层;即所述p型电子阻挡层结构从下至上包括p型in

0.1

al

0.1

ga

0.8

n层、p型in

0.08

al

0.12

ga

0.8

n层、p型in

0.06

al

0.14

ga

0.8

n层、p型in

0.04

al

0.16

ga

0.8

n层和p型algan层;p型al

a

ga

b

n层中a=0.2,b=0.8。

46.所述led外延结构的制备方法,包括以下步骤:

47.步骤s1:制备衬底,在衬底上生长缓冲层;所述缓冲层生长温度为950℃,生长厚度为500nm,生长压力为100torr;

48.步骤s2:在缓冲层上生长本征gan层;所述本征gan层生长温度为1100℃,生长厚度为0.8μm,生长压力为250torr;

49.步骤s3:在本征gan层上生长n型gan层;所述n型gan层生长温度为1100℃,生长厚度为2μm,生长压力为200torr;

50.步骤s4:在n型gan层上生长量子阱发光层;量子阱发光层的生长温度为800℃,生长压力为200torr;单一周期内,gan势垒层的生长厚度为5.0nm,ingan势阱层的生长厚度为4.0nm;

51.步骤s5:在量子阱发光层上生长p型电子阻挡层;p型电子阻挡层的生长温度为900℃,生长压力为200torr,其中p型in

0.1

al

0.1

ga

0.8

n层厚度为2nm,p型in

0.08

al

0.12

ga

0.8

n层厚度为3nm,p型in

0.06

al

0.14

ga

0.8

n层厚度为4nm,p型in

0.04

al

0.16

ga

0.8

n层厚度为5nm,p型al

0.2

ga

0.8

n层厚度为20nm;

52.步骤s6:在p型电子阻挡层上生长p型gan层;p型gan层的生长温度为900℃,生长厚度为120nm,生长压力为400torr。

53.实施例3

54.一种led外延结构,从下至上包括衬底、缓冲层、本征gan层、n型gan层、量子阱发光层、p型电子阻挡层和p型gan层;其中,p型电子阻挡层结构,从下至上包括周期数为n=5的p型in

xn

al

yn

ga1‑

xn

‑

yn

n层和p型al

a

ga

b

n层;即所述p型电子阻挡层结构从下至上包括p型in

0.12

al

0.08

ga

0.8

n层、p型in

0.1

al

0.1

ga

0.8

n层、p型in

0.08

al

0.12

ga

0.8

n层、p型in

0.06

al

0.14

ga

0.8

n层、p型in

0.04

al

0.16

ga

0.8

n层和p型algan层;p型al

a

ga

b

n层中a=0.2,b=0.8。

55.所述led外延结构的制备方法,包括以下步骤:

56.步骤s1:制备衬底,在衬底上生长缓冲层;所述缓冲层生长温度为950℃,生长厚度为500nm,生长压力为100torr;

57.步骤s2:在缓冲层上生长本征gan层;所述本征gan层生长温度为1100℃,生长厚度为0.8μm,生长压力为250torr;

58.步骤s3:在本征gan层上生长n型gan层;所述n型gan层生长温度为1100℃,生长厚度为2μm,生长压力为200torr;

59.步骤s4:在n型gan层上生长量子阱发光层;量子阱发光层的生长温度为800℃,生长压力为200torr;单一周期内,gan势垒层的生长厚度为5.0nm,ingan势阱层的生长厚度为4.0nm;

60.步骤s5:在量子阱发光层上生长p型电子阻挡层;p型电子阻挡层的生长温度为900℃,生长压力为200torr,其中p型in

0.12

al

0.08

ga

0.8

n层的厚度为2nm,p型in

0.16

al

0.1

ga

0.8

n层的厚度为3nm,p型in

0.08

al

0.12

ga

0.8

n层的厚度为4nm、p型in

0.06

al

0.14

ga

0.8

n层的厚度为5nm、p型in

0.04

al

0.16

ga

0.8

n层的厚度为6nm,p型al

0.2

ga

0.8

n厚度为25nm;

61.步骤s6:在p型电子阻挡层上生长p型gan层;p型gan层的生长温度为900℃,生长厚度为120nm,生长压力为400torr。

62.对比例1

63.如图3所示,一种led外延结构,从下至上包括衬底、缓冲层、本征gan层、n型gan层、量子阱发光层、p型电子阻挡层和p型gan层;其中,电子阻挡层为p型al

a

ga

b

n层。与实施例1相同,a=0.2,b=0.8。

64.实验数据

65.将上述实施例和对比例制备的不同led结构用维明蓝光led测试机进行测试,每一种结构制备4个平行样品,然后取平行样品的平均值进行统计。测试结果如表1所示。

66.表1

[0067][0068]

通过表1数据对比可以看出,与传统电子阻挡层(对比例1)相比,本发明的电子阻挡层提高了ir良率(ir_yield)及esd良率,因此本发明的电子阻挡层可以有效的调节应力,改善材料界面的晶格失配,从而使晶体质量得到有效提高;此外,本发明的电子阻挡层还可以提高电子和空穴复合效率,使得亮度(lop)也得到有效提升,且随着周期数n的增加,电性也有正向的变化。

[0069]

以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。