技术特征:

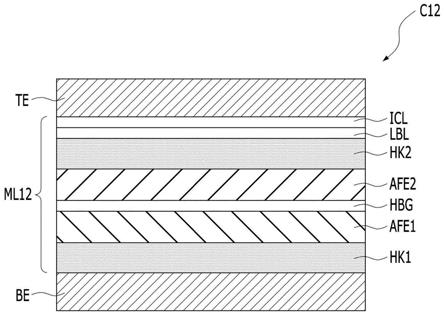

1.一种半导体器件,包括:第一电极;第二电极;和多层叠层,其位于所述第一电极和所述第二电极之间,所述多层叠层包括至少一个反铁电层和至少一个高k电介质层。2.根据权利要求1所述的半导体器件,其中,所述多层叠层包括在所述至少一个反铁电层与所述至少一个高k电介质层之间的至少一个直接接触界面。3.根据权利要求1所述的半导体器件,其中,所述至少一个反铁电层包括反铁电性铪锆氧化物。4.根据权利要求1所述的半导体器件,其中,所述至少一个反铁电层的厚度小于约5.根据权利要求1所述的半导体器件,其中,所述至少一个反铁电层包括其中氧化铪含量和氧化锆含量相同的铪锆氧化物,并且所述铪锆氧化物的厚度小于约6.根据权利要求1所述的半导体器件,其中,所述至少一个反铁电层包括其中氧化铪含量大于氧化锆含量的富氧化铪的铪锆氧化物,并且所述富氧化铪的铪锆氧化物的厚度小于约7.根据权利要求1所述的半导体器件,其中,所述至少一个反铁电层包括其中氧化锆含量大于氧化铪含量的富氧化锆的铪锆氧化物。8.根据权利要求1所述的半导体器件,其中,所述至少一个高k电介质层包括氧化铪或氧化锆。9.根据权利要求1所述的半导体器件,其中,所述多层叠层包括:第一高k电介质层,其在所述第一电极上方;第一反铁电层,其在所述第一高k电介质层上方;高带隙层,其在所述第一反铁电层上方;第二反铁电层,其在所述高带隙层上方;以及第二高k电介质层,其在所述第二反铁电层上方。10.根据权利要求9所述的半导体器件,其中,所述高带隙层的能带隙大于所述第一反铁电层和所述第二反铁电层以及所述第一高k电介质层和所述第二高k电介质层。11.根据权利要求9所述的半导体器件,其中,所述多层叠层进一步包括:泄漏阻挡层,其在所述第二高k电介质层和所述第二电极之间;以及界面控制层,其在所述泄漏阻挡层上方。12.根据权利要求11所述的半导体器件,其中,所述泄漏阻挡层包括具有比所述第一反铁电层和所述第二反铁电层以及所述第一高k电介质层和所述第二高k电介质层低的介电常数和高的能带隙的材料。13.根据权利要求11所述的半导体器件,其中,所述界面控制层包括具有电负性比所述第一反铁电层和所述第二反铁电层以及所述第一高k电介质层和所述第二高k电介质层大的材料。14.根据权利要求1所述的半导体器件,其中,所述多层叠层包括:

第一反铁电层,其在所述第一电极上方;第一高k电介质层,其在所述第一反铁电层上方;高带隙层,其在所述第一高k电介质层上方;第二高k电介质层,其在所述高带隙层上方;第二反铁电层,其在所述第二高k电介质层上方;泄漏阻挡层,其在所述第二反铁电层上方;以及界面控制层,其在所述泄漏阻挡层上方。15.根据权利要求1所述的半导体器件,其中,所述多层叠层包括:第一反铁电层,其在所述第一电极上方;高k电介质层,其在所述第一反铁电层上方;第二反铁电层,其在所述高k电介质层上方;泄漏阻挡层,其在所述第二反铁电层上方;以及界面控制层,其在所述泄漏阻挡层上方,其中所述高k电介质层的厚度比所述第一反铁电层和所述第二反铁电层的厚度大。16.根据权利要求1所述的半导体器件,其中,所述多层叠层包括:第一叠层,其包括第一反铁电层和在所述第一反铁电层上方的第一高k电介质层;第二叠层,其包括第二反铁电层和在所述第二反铁电层上方的第二高k电介质层;以及高带隙层,其在所述第一叠层和所述第二叠层之间。17.根据权利要求1所述的半导体器件,其中,所述多层叠层包括:第一叠层,其包括第一高k电介质层和在所述第一高k电介质层上方的第一反铁电层;第二叠层,其包括第二高k电介质层和在所述第二高k电介质层上方的第二反铁电层;以及高带隙层,其位于所述第一叠层和所述第二叠层之间。18.根据权利要求1所述的半导体器件,其中,所述多层叠层包括:第一叠层,其包括第一高k电介质层、第二高k电介质层以及位于所述第一高k电介质层和所述第二高k电介质层之间的第一反铁电层;第二叠层,其包括第三高k电介质层和在所述第三高k电介质层上方的第二反铁电层;以及高带隙层,其位于所述第一叠层和所述第二叠层之间。19.根据权利要求1所述的半导体器件,其中,所述多层叠层包括:第一叠层,其包括第一高k电介质层、第二高k电介质层以及位于所述第一高k电介质层和所述第二高k电介质层之间的第一反铁电层;第二叠层,其包括第三高k电介质层、第四高k电介质层和位于所述第三高k电介质层和所述第四高k电介质层之间的第二反铁电层;以及高带隙层,其位于所述第一叠层和所述第二叠层之间。20.根据权利要求1所述的半导体器件,其中,所述多层叠层包括:第一叠层,其包括第一高k电介质层、第二高k电介质层以及位于所述第一高k电介质层和所述第二高k电介质层之间的第一反铁电层;第二叠层,其包括第二反铁电层、第三反铁电层和位于所述第二反铁电层和所述第三

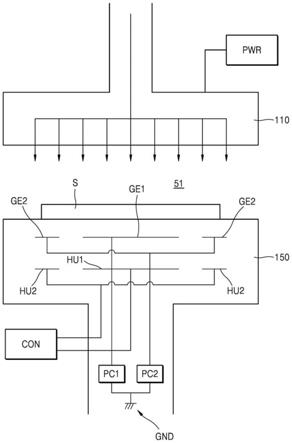

反铁电层之间的第三高k电介质层;以及高带隙层,其位于所述第一叠层和所述第二叠层之间。21.根据权利要求1所述的半导体器件,其中,所述多层叠层包括:第一叠层,其包括第一反铁电层、第二反铁电层以及位于所述第一反铁电层和所述第二反铁电层之间的第一高k电介质层;第二叠层,其包括第二高k电介质层和在所述第二高k电介质层上方的第三反铁电层;以及高带隙层,其位于所述第一叠层和所述第二叠层之间。22.根据权利要求1所述的半导体器件,其中,所述多层叠层包括:第一叠层,其包括第一反铁电层、第二反铁电层以及位于所述第一反铁电层和所述第二反铁电层之间的第一高k电介质层;以及第二叠层,其包括第三反铁电层和在所述第三反铁电层上方的第二高k电介质层;以及高带隙层,其位于所述第一叠层和所述第二叠层之间。23.根据权利要求1所述的半导体器件,其中,所述多层叠层包括:第一叠层,其包括第一反铁电层、第二反铁电层以及位于所述第一反铁电层和所述第二反铁电层之间的第一高k电介质层;以及第二叠层,其包括第三反铁电层、第四反铁电层和位于所述第三反铁电层和所述第四反铁电层之间的第二高k电介质层;以及高带隙层,其位于所述第一叠层和所述第二叠层之间。24.根据权利要求1所述的半导体器件,其中,所述多层叠层包括:第一叠层,其包括第一反铁电层、第二反铁电层以及位于所述第一反铁电层和所述第二反铁电层之间的第一高k电介质层;以及第二叠层,其包括第二高k电介质层、第三高k电介质层和位于所述第二高k电介质层和所述第三高k电介质层之间的第三反铁电层;以及高带隙层,其位于所述第一叠层和所述第二叠层之间。25.根据权利要求1所述的半导体器件,其中,所述多层叠层进一步包括:增强层,其提升所述至少一个反铁电层的介电常数,其中,所述增强层位于所述至少一个反铁电层下方,并且所述增强层和所述至少一个反铁电层直接接触。26.根据权利要求25所述的半导体器件,其中,所述增强层包括氧化铌、氮氧化铌、氧化钽、氮氧化钽、氧化钒或氮氧化钒。27.根据权利要求1所述的半导体器件,进一步包括:半导体衬底;晶体管,其包括形成在所述半导体衬底中的掩埋字线结构以及在所述掩埋字线结构的两侧上的第一源/漏极区和第二源/漏极区;以及位线,其耦接到所述晶体管的所述第一源/漏极区,其中,所述第一电极耦接到所述晶体管的所述第二源/漏极区。28.根据权利要求1所述的半导体器件,其中,所述至少一个反铁电层包括富氧化铪的反铁电性铪锆氧化物层,并且所述高k电介质层包括氧化铪层或氧化锆层。29.一种半导体器件,包括:

第一电极;第二电极;以及多层叠层,其位于所述第一电极和所述第二电极之间,所述多层叠层包括负电容铁电材料层和至少一个高k电介质层。30.根据权利要求29所述的半导体器件,其中,所述多层叠层包括:第一高k电介质层,其在所述第一电极上方;负电容铁电材料层,其在所述第一高k电介质层上方;以及第二高k电介质层,其在所述负电容铁电材料层上方。31.根据权利要求29所述的半导体器件,其中,所述多层叠层包括:高k电介质层,其在所述第一电极上方;以及负电容铁电材料层,其在所述高k电介质层上方。32.根据权利要求29所述的半导体器件,其中,所述多层叠层包括:负电容铁电材料层,其在所述第一电极上方;以及高k电介质层,其在所述负电容铁电材料层上方。33.根据权利要求29所述的半导体器件,其中,所述负电容铁电材料层包括其中氧化铪含量大于氧化锆含量的富氧化铪的铪锆氧化物层。34.根据权利要求29所述的半导体器件,其中,所述负电容铁电材料层比所述高k电介质层厚。35.根据权利要求29所述的半导体器件,其中,所述负电容铁电材料层的厚度为约至36.根据权利要求29所述的半导体器件,其中,所述多层叠层进一步包括:泄漏阻挡层,其与所述负电容材料层或所述高k电介质层相接触;以及界面控制层,其位于所述泄漏阻挡层和所述第二电极之间。

技术总结

本发明的半导体器件包括第一电极、第二电极以及位于第一电极和第二电极之间的多层叠层,所述多层叠层包括至少一个反铁电层和至少一个高k电介质层。一个高k电介质层。一个高k电介质层。

技术研发人员:姜世勋

受保护的技术使用者:爱思开海力士有限公司

技术研发日:2021.05.06

技术公布日:2021/11/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。