1.本公开涉及半导体技术领域,特别涉及一种高可靠性发光二极管芯片及其制造方法。

背景技术:

2.发光二极管(英文:light emitting diode,简称:led)是一种能发光的半导体器件。通过采用不同的半导体材料和结构,led能够覆盖从紫外到红外的全色范围,已经被广泛地应用在显示、装饰、通讯等经济生活中。

3.芯片是led的核心器件,相关技术中,led芯片包括衬底、n型半导体层、有源层、p型半导体层、n型电极、p型电极、绝缘层和焊点;n型半导体层、有源层和p型半导体层依次层叠在衬底的第一表面上;p型半导体层上设有延伸至n型半导体层的凹槽,n型电极设置在凹槽内的n型半导体层上,p型电极设置在p型半导体层上;绝缘层铺设在凹槽内和n型电极上,以及p型半导体层和p型电极上。其中,绝缘层上开始设有延伸至n型电极和延伸至p型电极的导电孔,焊点位于绝缘层表面以及导电孔内,与对应的n型电极或p型电极电连接。通过设置焊点以便于将led芯片通过回流焊接的方式焊接到电路板上。

4.然而,由于绝缘层需要起到保护作用,因此通常设置的较厚,则绝缘层上开设的导电孔的深度也会较深,且现有的导电孔为直孔,侧壁沿竖直方向延伸,后续在制作焊点时,反应物容易堆积在导电孔侧壁的上部分,影响焊点底部的沉积,使得导电孔底部部分区域存在空腔,焊点在导电孔内的填充效果较差。在后续器件使用时,空腔内的空气会快速膨胀,产生风险,不利于器件的稳定可靠使用。

技术实现要素:

5.本公开实施例提供了一种高可靠性发光二极管芯片及其制造方法,可以减少led芯片制造过程中空腔的产生,提高发光二极管芯片的可靠性。所述技术方案如下:

6.一方面,提供了一种高可靠性发光二极管芯片,所述高可靠性发光二极管芯片包括衬底、n型半导体层、有源层、p型半导体层、n型电极、p型电极、绝缘层和焊点;所述n型半导体层、所述有源层和所述p型半导体层依次层叠在所述衬底的第一表面上;所述p型半导体层上设有延伸至所述n型半导体层的凹槽,所述n型电极设置在凹槽内的所述n型半导体层上,所述p型电极设置在所述p型半导体层上;所述绝缘层铺设在所述凹槽内和所述n型电极上,以及所述p型半导体层和所述p型电极上,

7.所述绝缘层上开设有延伸至所述n型电极的第一导电孔和延伸至所述p型电极的第二导电孔,所述焊点包括第一焊点和第二焊点,所述第一焊点位于所述第一导电孔内以及所述绝缘层表面,与对应的所述n型电极电连接,所述第二焊点位于所述第二导电孔内以及所述绝缘层表面,与对应的所述p型电极电连接,所述第一导电孔和所述第二导电孔均为锥形孔,且沿芯片的层叠方向,所述锥形孔的内径逐渐增大。

8.可选地,所述锥形孔的内径的最小值和最大值的比值为1:1.5。

9.可选地,所述第一焊点包括第一基础层和覆盖在所述第一基础层上的第一连接层,所述第一基础层位于所述第一导电孔内,且所述第一基础层的与所述第一连接层连接的一面朝向所述第一连接层凸起,所述第一连接层位于所述绝缘层的表面;

10.所述第二焊点包括第二基础层和覆盖在所述第二基础层上的第二连接层,所述第二基础层位于所述第二导电孔内,且所述第二基础层的与所述第二连接层连接的一面朝向所述第二连接层凸起,所述第二连接层位于所述绝缘层的表面;

11.所述第一连接层与所述第二连接层在所述绝缘层上的正投影不重合。

12.可选地,所述第一基础层和所述第二基础层的结构相同,所述第一基础层为ti/sn/ti层叠结构。

13.可选地,所述第一连接层和所述第二连接础层的结构相同;

14.所述第一连接层为ti/al/ti/al/ni/pt/au/sn/au层叠结构。

15.另一方面,提供了一种高可靠性发光二极管芯片的制造方法,所述制造方法包括:

16.提供一衬底,所述衬底包括相对的第一表面和第二表面;

17.在所述衬底的所述第一表面上依次生长n型半导体层、有源层和p型半导体层;

18.在所述p型半导体层上开设延伸至所述n型半导体层的凹槽;

19.在所述p型半导体层上形成p型电极,在所述凹槽内的所述n型半导体层上形成n型电极;

20.所述凹槽内和所述n型电极上,以及所述p型半导体层和所述p型电极上形成绝缘层;

21.在所述绝缘层上开设延伸至所述n型电极的第一导电孔和延伸至所述p型电极的第二导电孔,所述第一导电孔和所述第二导电孔均为锥形孔,且沿芯片的层叠方向,所述锥形孔的内径逐渐增大;

22.在所述第一导电孔内和所述绝缘层表面形成与所述n型电极电连接的第一焊点,在所述第二导电孔内和所述绝缘层表面形成与所述p型电极电连接的第二焊点。

23.可选地,所述在所述绝缘层上开设延伸至所述n型电极的第一导电孔和延伸至所述p型电极的第二导电孔,包括:

24.采用干法刻蚀的方法在所述绝缘层分别开设延伸至所述n型电极的第一导电孔和延伸至所述p型电极的第二导电孔;

25.其中,在所述第一导电孔和所述第二导电孔的刻蚀初期,增加所述干法刻蚀过程中通入的化学气体的比例,在所述第一导电孔和所述第二导电孔的刻蚀后期,增加所述干法刻蚀过程中通入的物理气体的比例。

26.可选地,所述在所述第一导电孔内和所述绝缘层表面形成与所述n型电极电连接的第一焊点,在所述第二导电孔内和所述绝缘层表面形成与所述p型电极电连接的第二焊点,包括:

27.在所述第一导电孔内形成第一基础层;

28.在所述绝缘层表面形成第一连接层,所述第一连接层覆盖在所述第一基础层上;

29.在所述第二导电孔内形成第二基础层;

30.在所述绝缘层表面形成第二连接层,所述第二连接层覆盖在所述第二基础层上;

31.所述第一连接层与所述第二连接层在所述绝缘层上的正投影不重合。

32.可选地,所述在所述第一导电孔内形成第一基础层,包括:

33.采用真空蒸镀金属薄膜工艺在所述第一导电孔内依次沉积ti金属层、sn金属层和ti金属层,以在所述第一导电孔内形成所述第一基础层;

34.其中,在采用真空蒸镀金属薄膜工艺沉积所述sn金属层,包括:

35.采用第一蒸镀速度并辅以30度倾角的镀锅,生长厚度为a的sn金属层;

36.采用第二蒸镀速度并辅以30度倾角的镀锅,继续生长厚度为b的sn金属层;

37.采用第三蒸镀速度并辅以45度倾角的镀锅,继续生长厚度为c的sn金属层;

38.所述第二蒸镀速度大于所述第一蒸镀速度和所述第二蒸镀速度,a<b,c<b。

39.可选地,所述在所述绝缘层表面形成第一连接层,包括:

40.采用真空蒸镀金属薄膜工艺在所述绝缘层表面依次沉积ti、al、ti、al、ni、pt、au、sn、au层,以在所述绝缘层表面形成所述第一连接层;

41.其中,在沉积完第一层ti层和第二层al层后、在沉积完第三层ti层和第四层al层后、以及在沉积完第五层ni层后,均间隔设定时间,再继续沉积下一层。

42.本公开实施例提供的技术方案带来的有益效果是:

43.通过将绝缘层上开设的第一导电孔和第二导电孔设置为锥形孔,且沿芯片片的层叠方向,锥形孔的内径逐渐增大。则锥形孔的靠近绝缘层的一端的开口更大,靠近n型电极或p型电极的一端的开口更小,这样,在第一导电孔和第二导电孔中形成焊点时,可以从开口大的一端向开口小的一端进行沉积。即使反应物堆积在导电孔侧壁的上部分,也不会影响导电孔底部的沉积效果,从而可以减少导电孔中空腔的产生,提高焊点在导电孔中的填充效果。因此,采用该结构的发光二极管芯片,从而可以减少led芯片制造过程中空腔的产生,提高发光二极管芯片的可靠性。

附图说明

44.为了更清楚地说明本公开实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

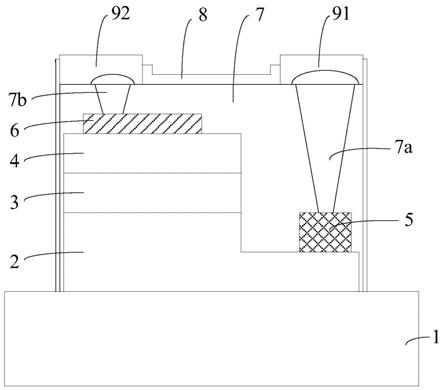

45.图1是本公开实施例提供的一种高可靠性发光二极管芯片的结构示意图;

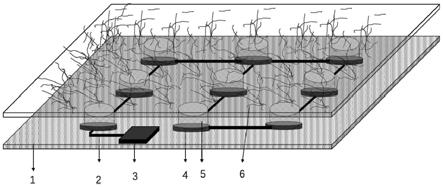

46.图2是本公开实施例提供的一种焊点的分布示意图;

47.图3是本公开实施例提供的一种高可靠性发光二极管芯片的制造方法流程图;

48.图4是本公开实施例提供的另一种高可靠性发光二极管芯片的制造方法流程图。

具体实施方式

49.为使本公开的目的、技术方案和优点更加清楚,下面将结合附图对本公开实施方式作进一步地详细描述。

50.图1是本公开实施例提供的一种高可靠性发光二极管芯片的结构示意图,如图1所示,高可靠性发光二极管芯片100包括衬底1、n型半导体层2、有源层3、p型半导体层4、n型电极5、p型电极6、绝缘层7和焊点9。n型半导体层2、有源层3和p型半导体层4依次层叠在衬底1的第一表面1a上。p型半导体层4上设有延伸至n型半导体层2的凹槽100a。n型电极5设置在

凹槽100a内的n型半导体层上2,p型电极6设置在p型半导体层4上。绝缘层7铺设在凹槽100a内和n型电极5上,以及p型半导体层4和p型电极6上。

51.绝缘层7上开设有延伸至n型电极5的第一导电孔7a和延伸至p型电极6的第二导电孔7b。焊点9包括第一焊点91和第二焊点92,第一焊点91位于第一导电孔7a内以及绝缘层7表面,与对应的n型电极5电连接。第二焊点92位于第二导电孔7b内以及绝缘层8表面,与对应的p型电极6电连接。

52.第一导电孔7a和第二导电孔7b均为锥形孔,且沿芯片的层叠方向,锥形孔的内径d逐渐增大。

53.本公开实施例通过将绝缘层上开设的第一导电孔和第二导电孔设置为锥形孔,且沿芯片的层叠方向,锥形孔的内径逐渐增大。则锥形孔的靠近绝缘层的一端的开口更大,靠近n型电极或p型电极的一端的开口更小,这样,在第一导电孔和第二导电孔中形成焊点时,可以从开口大的一端向开口小的一端进行沉积。即使反应物堆积在导电孔侧壁的上部分,也不会影响导电孔底部的沉积效果,从而可以减少导电孔中空腔的产生,提高焊点在导电孔中的填充效果。因此,采用该结构的发光二极管芯片,从而可以减少led芯片制造过程中空腔的产生,提高发光二极管芯片的可靠性。

54.可选地,锥形孔的内径的最小值和最大值的比值为1:1.5。

55.若锥形孔的内径的最小值和最大值的比值过大,会导致锥形孔在绝缘层表面的面积占比过大,减弱绝缘层对芯片的保护效果;若锥形孔的内径的最小值和最大值的比值过小,又会增大制造难度。

56.可选地,第一焊点91包括第一基础层911和覆盖在第一基础层911上的第一连接层912。第一基础层911位于第一导电孔7a内,且第一基础层911的与第一连接层912连接的一面朝向第一连接层912凸起。第一连接层912位于绝缘层7的表面。

57.第二焊点92包括第二基础层921和覆盖在第二基础层921上的第二连接层922。第二基础层921位于第二导电孔7b内,且第二基础层921的与第二连接层922连接的一面朝向第二连接层922凸起,第二连接层922位于绝缘层7的表面。

58.第一连接层91与第二连接层92在绝缘层7上的正投影不重合。

59.其中,通过在导电孔中生长基础层,可以保证焊点在导电孔的填充效果,从而可以保证后续n型电极和p型电极与电路板的连接效果。然后再在基础层上生长连接层,以便于后续将led芯片焊接至电路板上。且基础层的与连接层连接的一面朝向第二连接层凸起,可以加强基础层与连接层的连接效果。

60.可选地,第一基础层911和第二基础层921的结构相同。第一基础层911为ti/sn/ti层叠结构。

61.其中,ti的粘附性较好,通过在两侧设置ti层,有利于实现基础层与n型电极或p型电极、以及基础层与连接层和绝缘层之间的连接。sn可以作为比较好的填充金属来填充导电孔。

62.示例性地,第一基础层911中的第一层ti层的厚度为20nm,第二层sn层的厚度为4000nm,第三层ti层的厚度为100nm。

63.可选地,第一连接层912和第二连接础层922的结构相同。第一连接层921为ti/al/ti/al/ni/pt/au/sn/au层叠结构。

64.其中,连接层中的ti层与基础层接触,ti的粘附性较好,有利于连接层与基础层之间的连接。al层的柔韧性较好,可以有效缓冲焊接过程中的作用力,防止芯片受损。同时,ti层的密度较高,插入在al层中,有利于对al层定形,防止连接层产生变形。ni层和pt层结构致密,可以有效避免sn层中的sn原子在焊接过程中扩散到芯片的其它部分中,影响芯片的性能,从而可以提高芯片的可靠性。而au的柔韧性较好,可以有效缓解焊接过程中产生的作用力对芯片产生影响。

65.示例性地,第一连接层912中的ti层的厚度均为20nm,al层的厚度均为1000nm。ni层的厚度为500nm,pt层的厚度为200nm,sn层的厚度为5000nm,sn层和pt层之间的au层的厚度为500nm,sn层后的au层的厚度为20nm。

66.在本公开实施例的一种实现方式中,发光二极管芯片可以为氮化镓基的蓝绿光芯片。此时,衬底可以为蓝宝石衬底,n型半导体层可以为n型掺杂的gan层,厚度为4000nm。有源层可以包括多个周期交替生长的ingan阱层和gan垒层,阱层的厚度为3~5nm,垒层的厚度为7~8nm。p型半导体层可以为掺mg的gan层,厚度为5000nm。

67.在本公开实施例的另一种实现方式中,发光二极管芯片可以为铝镓铟磷基的红光芯片。此时,衬底为可以为蓝宝石衬底,n型半导体层为n型掺杂的algainp层,厚度为4000nm。有源层可以包括多个周期交替生长阱层和垒层,且阱层为al

x

ga1‑

x

inp层,垒层为al

y

ga1‑

y

inp层,x<y,阱层的厚度为3~5nm,垒层的厚度为7~8nm。p型半导体层为p型掺杂的gap层,厚度为5000nm。

68.可选地,n型电极5可以为auge层,p型电极6可以为aube层。

69.可选地,绝缘层7包括依次层叠的钝化层和分布式布拉格反射层。

70.其中,钝化层为氧化硅层,厚度为400~600nm,如500nm。氧化硅的硬度较大,可以对芯片进行有效保护。分布式布拉格反射层包括交替层叠的氧化硅层和氧化钛层,氧化硅层和氧化钛层的数量为30个~40个,如36个。反射波长可以按620nm设置。

71.可选地,该高可靠性发光二极管芯片还包括保护层8,保护层8铺设在绝缘层7的除焊点9的设置区域之外的所有区域上。保护层8可以为氧化硅层。厚度为400~600nm,如500nm。通过设置保护层可以避免外延片被空气中的氧气和水蒸气腐蚀。

72.在本公开实施例中,如图1所示,部分保护层8还包覆在第一焊点91和第二焊点92的侧壁上。

73.图2是本公开实施例提供的一种焊点的分布示意图,参见图2,第一焊点91和第二焊点92间隔设置在绝缘层7上。第一焊点91和第二焊点92在绝缘层7上的设置区域大小相同,且第一焊点91和第二焊点92在绝缘层7上的正投影不重合,方便与电路板形成稳定的电连接。

74.本公开实施例提供了一种高可靠性发光二极管芯片的制造方法,适用于制作图1所示的高可靠性发光二极管芯片。图3是本公开实施例提供的一种高可靠性发光二极管芯片的制造方法流程图,参见图3,该制造方法包括:

75.步骤301、提供一衬底。

76.其中,衬底包括相对的第一表面和第二表面。衬底可以为蓝宝石衬底。

77.步骤302、在衬底上依次生长n型半导体层、有源层和p型半导体层。

78.可选地,该步骤302可以包括:

79.采用金属有机化合物化学气相沉淀(英文:metal

‑

organic chemical vapor deposition,简称:mocvd)技术在衬底上依次生长n型半导体层、有源层和p型半导体层。

80.步骤303、在p型半导体层上开设延伸至n型半导体层的凹槽。

81.可选地,该步骤303可以包括:

82.采用光刻技术在p型半导体层上形成图形化光刻胶;

83.采用感应耦合等离子体刻蚀(英文:inductively coupled plasma,简称:icp)技术在p型半导体层上开设延伸至n型半导体层的凹槽;其中,刻蚀深度可以为5um。

84.步骤304、在p型半导体层上形成p型电极,在凹槽内的n型半导体层上形成n型电极。

85.可选地,步骤304包括:

86.采用光刻技术在p型半导体层上形成负性光刻胶;

87.采用蒸发技术在负性光刻胶、p型半导体层上形成电极材料;

88.去除负性光刻胶、以及负性光刻胶上的电极材料,p型半导体层上的电极材料形成p型电极。

89.可选地,p型电极为aube层。

90.可选地,步骤304包括:

91.采用光刻技术在凹槽内的n型半导体层上形成负性光刻胶;

92.采用蒸发技术在负性光刻胶、凹槽内的n型半导体层上形成电极材料;

93.去除负性光刻胶、以及负性光刻胶上的电极材料,凹槽内的n型半导体层上的电极材料形成n型电极。

94.可选地,n型电极为auge层。

95.步骤305、在凹槽内和n型电极上,以及p型半导体层和p型电极上形成绝缘层。

96.在本公开实施例中,绝缘层包括依次层叠的钝化层和分布式布拉格反射层。其中,钝化层为氧化硅层,厚度为400~600nm,如500nm。氧化硅的硬度较大,可以对芯片进行有效保护。分布式布拉格反射层包括交替层叠的氧化硅层和氧化钛层,氧化硅层和氧化钛层的数量为30个~40个,如36个。

97.示例性地,可以采用pecvd(plasma enhanced chemical vapor deposition,等离子体增强化学的气相沉积)法形成钝化层。

98.示例性地,可以采用离子源辅助的蒸镀技术形成dbr层。其中,dbr层包括交替层叠的氧化硅层和氧化钛层。氧化硅层和氧化钛层的周期数可以为32。

99.步骤306、在绝缘层上开设延伸至n型电极的第一导电孔和延伸至p型电极的第二导电孔。

100.其中,第一导电孔和第二导电孔均为锥形孔,且沿芯片的层叠方向,锥形孔的内径逐渐增大。

101.步骤307、在第一导电孔内和绝缘层表面形成与n型电极电连接的第一焊点,在第二导电孔内和绝缘层表面形成与p型电极电连接的第二焊点。

102.本公开实施例通过将绝缘层上开设的第一导电孔和第二导电孔设置为锥形孔,且沿芯片的层叠方向,锥形孔的内径逐渐增大。则锥形孔的靠近绝缘层的一端的开口更大,靠近n型电极或p型电极的一端的开口更小,这样,在第一导电孔和第二导电孔中形成焊点时,

可以从开口大的一端向开口小的一端进行沉积。即使反应物堆积在导电孔侧壁的上部分,也不会影响导电孔底部的沉积效果,从而可以减少导电孔中空腔的产生,提高焊点在导电孔中的填充效果。因此,采用该结构的发光二极管芯片,从而可以减少led芯片制造过程中空腔的产生,提高发光二极管芯片的可靠性。

103.本公开实施例提供了另一种高可靠性发光二极管芯片的制造方法,适用于制作图1所示的高可靠性发光二极管芯片。图4是本公开实施例提供的另一种高可靠性发光二极管芯片的制造方法流程图,参见图4,该制造方法包括:

104.步骤401、提供一衬底。

105.其中,衬底包括相对的第一表面和第二表面。衬底可以为蓝宝石衬底。

106.步骤402、对衬底进行图形化处理。

107.示例性地,图形化处理后的衬底表面具有多个间隔均布的锥形凸起,每个锥形凸起的底部直径均为1.3~1.7um,每个锥形凸起的高度均为0.8~1.2um。

108.在本公开实施中,步骤402可以为可选步骤。

109.步骤403、在衬底上依次生长n型半导体层、有源层和p型半导体层。

110.可选地,该步骤403可以与步骤302相同,在此不再详述。

111.步骤404、在p型半导体层上开设延伸至n型半导体层的凹槽。

112.可选地,该步骤404可以与步骤303相同,在此不再详述。

113.步骤405、在p型半导体层上形成p型电极,在凹槽内的n型半导体层上形成n型电极。

114.可选地,该步骤405可以与步骤304相同,在此不再详述。

115.步骤406、在凹槽内和n型电极上,以及p型半导体层和p型电极上形成绝缘层。

116.可选地,该步骤406可以与步骤305相同,在此不再详述。

117.步骤407、在绝缘层上开设延伸至n型电极的第一导电孔和延伸至p型电极的第二导电孔。

118.可选地,步骤407可以包括:

119.采用干法刻蚀技术在方法在绝缘层分别开设延伸至n型电极的第一导电孔和延伸至p型电极的第二导电孔;

120.其中,在第一导电孔和第二导电孔的刻蚀初期,增加干法刻蚀过程中通入的化学气体的比例,在第一导电孔和第二导电孔的刻蚀后期,增加干法刻蚀过程中通入的物理气体的比例。

121.通过上述生长方式,可以使得导电孔的上端和下端形成良好的转角,从而有利于提高后续焊点的填充效果,进一步减少空腔的产生。

122.可选地,物理气体可以包括ar气体,化学气体可以包括cl2气体。

123.例如,假设正常情况下,干法刻蚀第一导电孔和第二导电孔,需要通入的物理气体与化学气体的比例为1:1。

124.则在第一导电孔和第二导电孔的刻蚀初期,控制通入的物理气体与化学气体的流量比为1:3;

125.在第一导电孔和第二导电孔的刻蚀中期,控制通入的物理气体与化学气体的流量比为1:1;

126.在第一导电孔和第二导电孔的刻蚀初期,控制通入的物理气体与化学气体的流量比为1.5:1。

127.示例性地,若干法刻蚀第一导电孔和第二导电孔的总时间均为t,则刻蚀初期可以为0~1/3t时间段,刻蚀后期可以为2/3t~t时间段。

128.步骤408、在第一导电孔内和绝缘层表面形成与n型电极电连接的第一焊点,在第二导电孔内和绝缘层表面形成与p型电极电连接的第二焊点。

129.示例性地,步骤408可以包括:

130.第一步、在绝缘层表面形成设定图形的光刻胶;

131.第二步、在第一导电孔内形成第一基础层。

132.可选地,第二步可以包括:

133.采用真空蒸镀金属薄膜工艺在第一导电孔内依次沉积ti、sn、ti三个金属层,以在第一导电孔内形成第一基础层;

134.其中,在采用真空蒸镀金属薄膜工艺沉积sn金属层,包括:

135.1)采用第一蒸镀速度并辅以30度倾角的镀锅,生长厚度为a的sn金属层;

136.2)采用第二蒸镀速度并辅以30度倾角的镀锅,继续生长厚度为b的sn金属层;

137.3)采用第三蒸镀速度并辅以45度倾角的镀锅,继续生长厚度为c的sn金属层。

138.示例性地,第三蒸镀速度大于第一蒸镀速度和第二蒸镀速度,a<b,c<b。

139.示例性地,第三蒸镀速度为1~1.5nm/s,第一蒸镀速度和第二蒸镀速度相等,均为0.2nm/s。

140.示例性地,a=c=0.5um,b=3um。

141.第三步、在第一导电孔周围没有光刻胶覆盖的绝缘层上形成第一连接层。

142.可选地,第三步可以包括:

143.采用真空蒸镀金属薄膜工艺,在第一导电孔周围没有光刻胶覆盖的绝缘层表面,依次沉积ti、al、ti、al、ni、pt、au、sn、au层,以在绝缘层表面形成第一连接层;

144.其中,在沉积完第一层ti层和第二层al层后、在沉积完第三层ti层和第四层al层后、以及在沉积完第五层ni层后,均间隔设定时间,再继续沉积下一层。

145.示例性地,设定时间可以设置为例如30分钟,以避免光刻胶受到过高温度影响而碳化。即在沉积完ti/al层叠结构后,间隔30分钟,继续沉积ti/al层叠结构,然后间隔30分钟,继续沉积ni层,然后间隔30分钟,继续沉积pt/au/sn/au层。

146.第四步、在第二导电孔内形成第二基础层。

147.第四步的具体步骤与第二步相同,在此不再详述。

148.第五步、在绝缘层表面形成第二连接层,第二连接层覆盖在第二基础层上。

149.第五步的具体步骤与第三步相同,在此不再详述。

150.其中,第一连接层与第二连接层在绝缘层上的正投影不重合。

151.第六步,去除光刻胶。

152.示例性地,光刻胶可以采用光刻技术形成,光刻胶厚度可以增加到15μm,并且可以采用紫外固化的手段,保持光刻胶形貌的稳定。

153.步骤409、在绝缘层的除焊点的设置区域之外的所有区域上形成钝化层。

154.示例性地,可以采用pecvd技术形成钝化层。其中,钝化层为氧化硅层,厚度为

500nm。

155.可选地,可以采用光刻技术在钝化层上形成图形化光刻胶,然后干法刻蚀未被光刻胶覆盖的钝化层,接着去除光刻胶。

156.步骤410、减薄衬底。

157.在本公开实施例中,减薄后的衬底的最终厚度约为60~120um,例如80um。在保证支撑强度的情况下,减少光线在衬底内的损失。

158.可选地,该制造方法还可以包括:

159.对衬底进行隐形切割划裂。

160.实际应用中,切割可以先利用隐形切割技术进行划裂,再劈开即可,有利于提高亮度。隐形切割时,可以从芯片的背面射入激光光子,激光波长可以为1024nm。

161.本公开实施例通过将绝缘层上开设的第一导电孔和第二导电孔设置为锥形孔,且沿芯片的层叠方向,锥形孔的内径逐渐增大。则锥形孔的靠近绝缘层的一端的开口更大,靠近n型电极或p型电极的一端的开口更小,这样,在第一导电孔和第二导电孔中形成焊点时,可以从开口大的一端向开口小的一端进行沉积。即使反应物堆积在导电孔侧壁的上部分,也不会影响导电孔底部的沉积效果,从而可以减少导电孔中空腔的产生,提高焊点在导电孔中的填充效果。因此,采用该结构的发光二极管芯片,从而可以减少led芯片制造过程中空腔的产生,提高发光二极管芯片的可靠性。

162.以上所述仅为本公开的可选实施例,并不用以限制本公开,凡在本公开的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。