一种hemt与阵列led单片集成芯片及其制备方法

技术领域

1.本发明涉及半导体制造技术领域,尤其涉及一种hemt与阵列led单片集成芯片及其制备方法。

背景技术:

2.近年来,固态照明(ssl)和可见光通信(vlc)的发展受到了人们的广泛关注。相比于传统的射频无线通信,可见光通信没有电磁干扰和许可证限制,频谱资源丰富。用于照明和通信两用的白光光源,通常是基于蓝光发光二极管结合黄色荧光粉的led,由于黄色荧光粉缓慢的响应速度,使得传统的白光led的带宽仅为几mhz,这限制了其在可见光通信系统中的数据通信能力。

3.algan/gan hemt(algan/gan高电子迁移率晶体管)器件具有高击穿和低导通电阻的特性,利用其高频和输出电流容量,可以作为固态照明、显示器和可见光通信等许多应用中的led驱动晶体管,通过共享一个通用的材料平台,将led和hemt单片集成在同一衬底上,可以大大地降低由于引线键合引起的寄生电阻和电容,从而提高了驱动电路的功率效率,并利用片上集成algan/gan hemt驱动器,可以充分发挥led芯片的高寿命优势,提高led系统的可靠性。

4.基于传统si基cmos(互补金属氧化物半导体)驱动的led阵列系统十分复杂,以及集成芯片具有较低的光输出功率,限制其应用场景。为了进一步提高led芯片的性能,从而扩大其应用场景,研制hemt与阵列led单片集成芯片有重要意义。

技术实现要素:

5.为了克服现有技术的不足,本发明的目的之一在于提供一种hemt与阵列led单片集成芯片,其通过将电流控制的led芯片转变为电压控制,简化驱动电路,并通过led区中各led单元采用阵列串联的方法,进一步地提升了集成芯片的驱动电压和光输出功率,可将集成的hemt与阵列led应用于更多对照明需求高的场景。

6.本发明的目的之二在于提供一种hemt与阵列led单片集成芯片的制备方法,其流程简单,成品率高,适用于工业化生产,具有很好的应用前景。

7.本发明的目的之一采用如下技术方案实现:

8.一种hemt与阵列led单片集成芯片,包括hemt区域及led区域,所述hemt区域包括从下到上依次排列分布的高阻衬底、gan缓冲层、gan沟道层、algan势垒层及hemt电极层,所述hemt电极层包括源电极、漏电极及栅电极;所述led区域包括至少两个阵列设置的led单元及第一金属连接桥,所述led单元包括高阻衬底、gan缓冲层、gan沟道层、algan势垒层、i

‑

gan层、n型gan层、n电极、ingan/gan多量子阱层、algan电子阻挡层、p型gan层、p电极及保护层,所述第一金属连接桥的两端分别用于连接相邻的led单元的n电极与p电极,以实现各led单元的串联;所述hemt区域的源电极通过第二金属连接桥与串联设置的首个led单元的p电极相连,以实现hemt区域与led区域的电学导通。

9.进一步地,各所述led单元的排布方式为线性排布。

10.进一步地,所述源电极与所述algan势垒层为欧姆接触,所述源电极为ti、al、ni、au中的一种或者两种以上;所述漏电极与所述algan势垒层为欧姆接触,所述漏电极为ti、al、ni、au中的一种或者两种以上;所述栅电极与所述algan势垒层为肖特基接触,所述栅电极为ni、au中的一种或者两种。

11.进一步地,所述n电极的表面与所述n型gan层为欧姆接触,所述n电极为cr、ti、al、au、ag、pt中的一种或者两种以上;所述p电极的表面与所述p型gan层为欧姆接触,所述p电极为cr、ti、al、au、ag、pt中的一种或者两种以上。

12.进一步地,所述n电极的厚度为1μm

‑

5μm;所述p电极的厚度为1μm

‑

5μm。

13.进一步地,所述高阻衬底为高阻硅衬底,所述高阻硅衬底的厚度为500μm

‑

1000μm;所述保护层为sio2钝化层,所述sio2钝化层的厚度为300nm

‑

500nm。

14.进一步地,所述第一金属连接桥、第二金属连接桥均为au。

15.进一步地,所述hemt区域与所述led区域的面积比为1:2。

16.本发明的目的之二采用如下技术方案实现:

17.一种hemt与阵列led单片集成芯片的制备方法,包括如下步骤:

18.s1:取外延高阻衬底,在外延高阻衬底上依次生长gan缓冲层、gan沟道层、algan势垒层、i

‑

gan层、n型gan层、ingan/gan多量子阱层、algan电子阻挡层和p型gan层,得到hemt

‑

led集成外延片;

19.s2:在上述hemt

‑

led集成外延片上通过选区刻蚀方法,分为hemt区域和led区域;

20.s3:在hemt区域上制备源电极、漏电极和栅电极;

21.s4:在led区域上通过刻蚀方法,形成n型gan层台阶,并在n型gan层台阶处制备n电极,在p型gan层的顶部制备p电极,得到第一led单元;重复上述第一led单元的制备步骤,得到至少一个阵列设置的第二led单元;

22.s5:通过上述步骤s3、s4,得到hemt

‑

led集成外延器件,在hemt

‑

led集成外延器件的表面沉积保护层;

23.s6:制备第一金属连接桥,使第一金属连接桥穿设于第一led单元的n电极上方的保护层和相邻的第二led单元的p电极上方的保护层,将第一led单元的n电极和相邻的第二led单元的p电极相连,实现阵列设置的led单元的串联;

24.s7:制备第二金属连接桥,使第二金属连接桥穿设于hemt区域的源电极上方的保护层和第一led单元的p电极上方的保护层,将源电极与第一led单元的p电极互联,实现hemt区域与led区域的电学导通;

25.s8:引出hemt区域的漏电极和栅电极,得到hemt与阵列led单片集成芯片。

26.进一步地,在步骤s1中,利用mocvd设备在外延高阻衬底上生长各外延层;在步骤s3中,具体制备步骤为:在hemt区域上通过光刻并沉积金属层,然后在n2气氛和温度为850℃下退火30s,制备具有欧姆接触的源电极和漏电极,最后通过光刻并沉积金属层,制备具有肖特基接触的栅电极。

27.相比现有技术,本发明的有益效果在于:

28.本发明的hemt与阵列led单片集成芯片通过将电流控制的led芯片转变为电压控制,简化驱动电路,并通过led区中各led单元采用阵列串联的方法,进一步地提升了集成芯

片的驱动电压和光输出功率,通过led单元串联阵列的方法,降低了芯片的结电容,进而降低rc时间常数,可用于制备适用于可见光通信的高带宽、高光输出功率的hemt与阵列led集成芯片,可将集成的hemt与阵列led应用于更多对照明需求高的场景。

29.其中,一方面,通过芯片阵列排布的方式,可以有效提升led的驱动电压、电功率以及光输出功率,可应用于对亮度需求高的场景;另一方面,利用具有高电子迁移率和低导通电阻的algan/gan hemt器件作为led的驱动器可以实现电压控制,简化调制电路的复杂程度,串联阵列可降低led芯片的结电容,从而降低rc时间常数,提高器件带宽,可广泛应用于智能显示和可见光通信系统中。

30.本发明的hemt与阵列led单片集成芯片的制备方法,流程简单,成品率高,适用于工业化生产,具有很好的应用前景。

附图说明

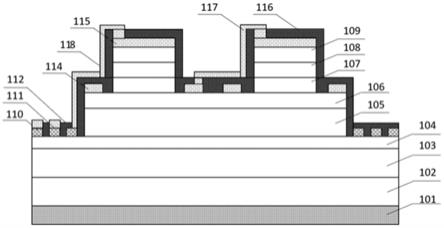

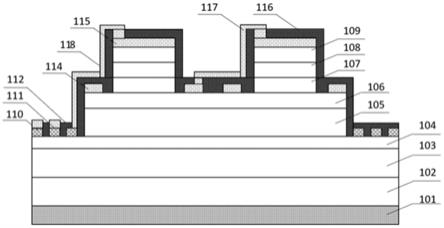

31.图1为本发明的hemt与阵列led单片集成芯片的结构图;

32.图2为图1所示的hemt与阵列led单片集成芯片的俯视结构图;

33.图3为本发明的hemt与led集成芯片外延的结构图;

34.图4为在图3的hemt与led集成芯片外延结构上得到hemt区域的源电极、漏电极、栅电极的结构图;

35.图5为在图4的结构上得到led区域的p电极、n电极的结构图。

36.图中:101、高阻衬底;102、gan缓冲层;103、gan沟道层;104、algan势垒层;105、i

‑

gan层;106、n型gan层;107、ingan/gan多量子阱层;108、algan电子阻挡层;109、p型gan层;110、源电极;111、漏电极;112、栅电极;114、n电极;115、p电极;116、保护层;117、第一金属连接桥;118、第二金属连接桥。

具体实施方式

37.下面,结合具体实施方式,对本发明做进一步描述,需要说明的是,在不相冲突的前提下,以下描述的各实施例之间或各技术特征之间可以任意组合形成新的实施例。

38.请参阅图1和图2,图1为本发明的一较佳实施例的hemt与阵列led单片集成芯片的结构图,图2为图1的hemt与阵列led单片集成芯片的俯视结构图,具体的,该hemt与阵列led单片集成芯片包括hemt区域及led区域,hemt区域在外,led区域在内,以形成hemt区域围绕led区域设置。在其中一实施例中,所述hemt区域与所述led区域的面积比为1:2。

39.所述hemt区域包括从下到上依次排列分布的高阻衬底101、gan缓冲层102、gan沟道层103、algan势垒层104及hemt电极层,所述hemt电极层包括源电极110、漏电极111及栅电极112;所述led区域包括至少两个阵列设置的led单元及第一金属连接桥117,所述led单元包括高阻衬底101、gan缓冲层102、gan沟道层103、algan势垒层104、i

‑

gan层105、n型gan层106、n电极114、ingan/gan多量子阱层107、algan电子阻挡层108、p型gan层109、p电极115及保护层116。

40.所述第一金属连接桥117的两端分别用于连接相邻的led单元的n电极114与p电极115,以实现各led单元的串联,即若led单元的数量为2个,第一led单元的n电极114与第二led单元的p电极115通过第一金属连接桥117相连;若led单元的数量为3个,第一led单元的

n电极114与第二led单元的p电极115通过第一金属连接桥117相连,第二led单元的n电极114与第三led单元的p电极115通过第一金属连接桥117相连,以此类推,形成阵列led单元的串联。

41.所述hemt区域的源电极110通过第二金属连接桥118与串联设置的首个led单元的p电极115相连,以实现hemt区域与led区域的电学导通,实现hemt与led的集成,即hemt区域的源电极110与第一led单元(首个led单元)的p电极115通过第二金属连接桥118相连,第一led单元的n电极114与第二led单元的p电极115通过第一金属连接桥117相连。

42.在其中一实施例中,由于led单元的单元个数为2个以上,且各led单元为阵列分布,因此各led单元的排布方式为但不限于线性排布,还可以为其他多种任意的排布方式,以有利于各led单元的发光及散热。

43.在本实施例中,所述源电极110与所述algan势垒层104为欧姆接触,所述源电极110为ti、al、ni、au中的一种或者两种以上;所述漏电极111与所述algan势垒层104为欧姆接触,所述漏电极111为ti、al、ni、au中的一种或者两种以上;所述栅电极112与所述algan势垒层104为肖特基接触,所述栅电极112为ni、au中的一种或者两种。在另一实施例中,源电极110的厚度为1μm;漏电极111的厚度为1μm;栅电极112的厚度为1μm;优选地,源电极110为ti、al、ni、au所形成的合金,漏电极111为ti、al、ni、au所形成的合金,栅电极112为ni、au所形成的合金。

44.led单元的p电极115位于led区域的顶部,所述p电极115的表面与所述p型gan层109为欧姆接触,所述p电极115为cr、ti、al、au、ag、pt中的一种或者两种以上。优选地,p电极115的厚度为1μm

‑

5μm。更优选地,p电极115的厚度为3μm。

45.led单元的n电极114位于led区域的台阶处,所述n电极114的表面与所述n型gan层106为欧姆接触,所述n电极114为cr、ti、al、au、ag、pt中的一种或者两种以上;优选地,n电极114的厚度为1μm

‑

5μm。更优选地,n电极114的厚度为3μm。

46.所述高阻衬底101为但不限于高阻硅衬底,所述高阻硅衬底的厚度为500μm

‑

1000μm;所述保护层116为sio2钝化层,所述sio2钝化层的厚度为300nm

‑

500nm。优选地,所述高阻硅衬底的厚度为500μm

‑

600μm。更优选地,高阻硅衬底的厚度为500μm,sio2钝化层的厚度为300nm。

47.在其中一实施例中,所述第一金属连接桥117、第二金属连接桥118均为但不限于au。

48.上述hemt与阵列led单片集成芯片通过将电流控制的led芯片转变为电压控制,简化驱动电路,并通过led区中各led单元采用阵列串联的方法,进一步地提升了集成芯片的驱动电压和光输出功率,通过led单元串联阵列的方法,降低了芯片的结电容,进而降低rc时间常数,可用于制备适用于可见光通信的高带宽、高光输出功率的hemt与阵列led集成芯片,可将集成的hemt与阵列led应用于更多对照明需求高的场景。

49.本发明还提供一种hemt与阵列led单片集成芯片的制备方法,包括如下步骤:

50.s1:取外延高阻衬底101,利用mocvd设备在外延高阻衬底101上依次生长gan缓冲层102、gan沟道层103、algan势垒层104、i

‑

gan层105、n型gan层106、ingan/gan多量子阱层107、algan电子阻挡层108和p型gan层109,得到hemt

‑

led集成外延片,即在外延高阻衬底101上依次生长hemt全结构与led全结构,如图3所示。

51.s2:在上述hemt

‑

led集成外延片上通过选区刻蚀方法(即光刻和icp刻蚀结合),分为hemt区域和led区域;

52.s3:在hemt区域上制备源电极110、漏电极111和栅电极112,如图4所示;

53.s4:在led区域上通过刻蚀方法(即光刻和icp刻蚀结合),形成n型gan层106台阶(如图2所示的台阶),并在n型gan层106台阶处制备n电极114,在p型gan层109的顶部制备p电极115,得到第一led单元;重复上述第一led单元的制备步骤,得到至少一个阵列设置的第二led单元,如图5所示;

54.s5:通过上述步骤s3、s4,得到hemt

‑

led集成外延器件,在hemt

‑

led集成外延器件的表面利用pecvd沉积保护层116;

55.s6:通过光刻和湿法腐蚀的结合方法制备第一金属连接桥117,使第一金属连接桥117穿设于第一led单元的n电极114上方的保护层116和相邻的第二led单元的p电极115上方的保护层116,将第一led单元的n电极114和相邻的第二led单元的p电极115相连,实现阵列设置的led单元的串联;

56.s7:通过光刻和湿法腐蚀的结合方法制备第二金属连接桥118,使第二金属连接桥118穿设于hemt区域的源电极110上方的保护层116和第一led单元的p电极115上方的保护层116,将源电极110与第一led单元的p电极115互联,实现hemt区域与led区域的电学导通;

57.s8:最后,通过光刻和湿法腐蚀的结合,引出hemt区域的漏电极111和栅电极112,得到hemt与阵列led单片集成芯片,如图1所示。

58.在其中一实施例中,在步骤s1中,利用mocvd设备在外延高阻衬底101上生长各外延层;在步骤s3中,具体制备步骤为:在hemt区域上通过光刻并沉积金属层,然后在n2气氛和温度为850℃下退火30s,制备具有欧姆接触的源电极110和漏电极111,最后通过光刻并沉积金属层,制备具有肖特基接触的栅电极112。

59.上述制备方法,流程简单,成品率高,适用于工业化生产,具有很好的应用前景。

60.以下通过具体的实施例对其进一步地说明,但本发明的实施不限于此。

61.实施例1

62.一种hemt与阵列led单片集成芯片,包括如下制备步骤:

63.s1:取厚度为500μm的外延高阻硅衬底,利用mocvd设备在外延高阻衬底101上依次生长gan缓冲层102、gan沟道层103、algan势垒层104、i

‑

gan层105、n型gan层106、ingan/gan多量子阱层107、algan电子阻挡层108和p型gan层109,得到hemt

‑

led集成外延片;

64.s2:在上述hemt

‑

led集成外延片上通过光刻和icp刻蚀进行选取刻蚀,分为hemt区域和led区域;所述hemt区域与所述led区域的面积比为1:2;

65.s3:在hemt区域通过光刻并依次沉积ti、al、ni、au多金属层,然后在n2气氛和850℃下退火30s,制备具有欧姆接触的源电极110、漏电极111,源电极110的厚度为1μm,漏电极111的厚度为1μm;再在hemt区域通过光刻并依次沉积ni、au多金属层,制备具有肖特基接触的栅电极112,栅电极112的厚度为1μm;

66.s4:在led区域上通过光刻和icp刻蚀,形成n型gan层106台阶,并在该n型gan层106台阶处通过光刻和沉积ti、cr、au合金,制备厚度为3μm的n电极114,在p型gan层109的顶部通过光刻和沉积ti、cr、au合金,制备厚度为3μm的p电极115,得到第一led单元;然后采用制备第一led单元的方法得到第二led单元,第一led单元和第二led单元的排布方式为线性排

布;

67.s5:通过上述步骤s3、s4,得到hemt

‑

led集成外延器件,在hemt

‑

led集成外延器件的表面利用pecvd沉积300nm厚的sio2钝化层;

68.s6:通过光刻和湿法腐蚀的结合方法制备第一金属连接桥117,使第一金属连接桥117穿设于第一led单元的n电极114上方的保护层116和相邻的第二led单元的p电极115上方的sio2钝化层,将第一led单元的n电极114和相邻的第二led单元的p电极115相连,实现阵列设置的led单元的串联;其中,第一金属连接桥117为au;

69.s7:通过光刻和湿法腐蚀的结合方法制备第二金属连接桥118,使第二金属连接桥118穿设于hemt区域的源电极110上方的保护层116和第一led单元的p电极115上方的sio2钝化层,将源电极110与第一led单元的p电极115互联,实现hemt区域与led区域的电学导通;其中,第二金属连接桥118为au;

70.s8:最后,通过光刻和湿法腐蚀的结合,引出hemt区域的漏电极111和栅电极112,得到hemt与阵列led单片集成芯片。

71.实施例2

72.一种hemt与阵列led单片集成芯片,包括如下制备步骤:

73.s1:取厚度为500μm的外延高阻硅衬底,利用mocvd设备在外延高阻衬底101上依次生长gan缓冲层102、gan沟道层103、algan势垒层104、i

‑

gan层105、n型gan层106、ingan/gan多量子阱层107、algan电子阻挡层108和p型gan层109,得到hemt

‑

led集成外延片;

74.s2:在上述hemt

‑

led集成外延片上通过光刻和icp刻蚀进行选取刻蚀,分为hemt区域和led区域;所述hemt区域与所述led区域的面积比为1:2;

75.s3:在hemt区域通过光刻并依次沉积ti、al、ni、au多金属层,然后在n2气氛和850℃下退火30s,制备具有欧姆接触的源电极110、漏电极111,源电极110的厚度为1μm,漏电极111的厚度为1μm;再在hemt区域通过光刻并依次沉积ni、au多金属层,制备具有肖特基接触的栅电极112,栅电极112的厚度为1μm;

76.s4:在led区域上通过光刻和icp刻蚀,形成n型gan层106台阶,并在该n型gan层106台阶处通过光刻和沉积ti、cr、au合金,制备厚度为3μm的n电极114,在p型gan层109的顶部通过光刻和沉积ti、cr、au合金,制备厚度为3μm的p电极115,得到第一led单元;然后采用制备第一led单元的方法得到第二led单元;接着,采用制备第一led单元的方法得到第三led单元;第一led单元、第二led单元、第三led单元的排布方式为线性排布;

77.s5:通过上述步骤s3、s4,得到hemt

‑

led集成外延器件,在hemt

‑

led集成外延器件的表面利用pecvd沉积300nm厚的sio2钝化层;

78.s6:通过光刻和湿法腐蚀的结合方法制备第一金属连接桥117,使第一金属连接桥117穿设于第一led单元的n电极114上方的保护层116和相邻的第二led单元的p电极115上方的sio2钝化层,将第一led单元的n电极114和相邻的第二led单元的p电极115相连;采用第一金属连接桥117的制备方法将第二led单元的n电极114和相邻的第三led单元的p电极115相连,实现阵列设置的led单元的串联;其中,第一金属连接桥117为au;

79.s7:通过光刻和湿法腐蚀的结合方法制备第二金属连接桥118,使第二金属连接桥118穿设于hemt区域的源电极110上方的保护层116和第一led单元的p电极115上方的sio2钝化层,将源电极110与第一led单元的p电极115互联,实现hemt区域与led区域的电学导

通;其中,第二金属连接桥118为au;

80.s8:最后,通过光刻和湿法腐蚀的结合,引出hemt区域的漏电极111和栅电极112,得到hemt与阵列led单片集成芯片。

81.实施例3

82.一种hemt与阵列led单片集成芯片,包括如下制备步骤:

83.s1:取厚度为500μm的外延高阻硅衬底,利用mocvd设备在外延高阻衬底101上依次生长gan缓冲层102、gan沟道层103、algan势垒层104、i

‑

gan层105、n型gan层106、ingan/gan多量子阱层107、algan电子阻挡层108和p型gan层109,得到hemt

‑

led集成外延片;

84.s2:在上述hemt

‑

led集成外延片上通过光刻和icp刻蚀进行选取刻蚀,分为hemt区域和led区域;所述hemt区域与所述led区域的面积比为1:2;

85.s3:在hemt区域通过光刻并依次沉积ti、al、ni、au多金属层,然后在n2气氛和850℃下退火30s,制备具有欧姆接触的源电极110、漏电极111,源电极110的厚度为1μm,漏电极111的厚度为1μm;再在hemt区域通过光刻并依次沉积ni、au多金属层,制备具有肖特基接触的栅电极112,栅电极112的厚度为1μm;

86.s4:在led区域上通过光刻和icp刻蚀,形成第一个n型gan层106台阶,并在该n型gan层106台阶处通过光刻和沉积ti、cr、au合金,制备第一个厚度为3μm的n电极114,在p型gan层109的顶部通过光刻和沉积ti、cr、au合金,制备第一个厚度为3μm的p电极115,得到第一led单元;然后采用制备第一led单元的方法得到第二led单元;接着,采用制备第一led单元的方法得到第三led单元;最后,采用制备第一led单元的方法得到第四led单元;第一led单元、第二led单元、第三led单元、第四led单元的排布方式为线性排布;

87.s5:通过上述步骤s3、s4,得到hemt

‑

led集成外延器件,在hemt

‑

led集成外延器件的表面利用pecvd沉积300nm厚的sio2钝化层;

88.s6:通过光刻和湿法腐蚀的结合方法制备第一金属连接桥117,使第一金属连接桥117穿设于第一led单元的n电极114上方的保护层116和相邻的第二led单元的p电极115上方的sio2钝化层,将第一led单元的n电极114和相邻的第二led单元的p电极115相连;采用第一金属连接桥117的制备方法将第二led单元的n电极114和相邻的第三led单元的p电极115相连;采用第一金属连接桥117的制备方法将第三led单元的n电极114和相邻的第四led单元的p电极115相连;实现阵列设置的led单元的串联;其中,第一金属连接桥117为au;

89.s7:通过光刻和湿法腐蚀的结合方法制备第二金属连接桥118,使第二金属连接桥118穿设于hemt区域的源电极110上方的保护层116和第一led单元的p电极115上方的sio2钝化层,将源电极110与第一led单元的p电极115互联,实现hemt区域与led区域的电学导通;其中,第二金属连接桥118为au;

90.s8:最后,通过光刻和湿法腐蚀的结合,引出hemt区域的漏电极111和栅电极112,得到hemt与阵列led单片集成芯片。

91.上述实施方式仅为本发明的优选实施方式,不能以此来限定本发明保护的范围,本领域的技术人员在本发明的基础上所做的任何非实质性的变化及替换均属于本发明所要求保护的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。