显示装置

1.本技术是申请日为2018年03月07日、申请号为201810186982.6、发明名称为“显示装置”的发明专利申请的分案申请。

2.关联申请的相互引用

3.本技术基于2017年3月7日提出的日本专利申请第2017-043028号主张优先权,在此引用其全部内容。

技术领域

4.本发明涉及显示装置。

背景技术:

5.液晶显示装置或有机电致发光显示装置等的显示装置具有排列像素的显示区域和将显示区域包围的周边区域,在周边区域中,配置用来驱动像素的周边电路。

6.近年来,研究了各种用来使显示装置窄边框化的技术。为了实现显示装置的窄边框化,需要使周边电路的布局高效率化、使周边区域的面积变小。

技术实现要素:

7.根据本发明一方式的显示装置,具备:基板,在角部具有圆弧的外形;形成在上述基板的显示区域,且在第一方向隔开间隔而排列的多条信号线、在与上述第一方向交叉的第二方向隔开间隔而排列的多条扫描线、及多个像素;以及扫描线驱动器,设置在上述显示区域的外侧,上述多个像素沿着上述圆弧的外形被设置为台阶状,上述扫描线驱动器具有:沿着上述圆弧的外形而配置的第一移位寄存器单元及第二移位寄存器单元;与上述第一移位寄存器单元连接的多个第一电路;与上述第二移位寄存器单元连接的多个第二电路,上述多个第一电路在上述第一方向排列,上述多个第一电路中的各个第一电路与上述多条扫描线中的对应的一条扫描线连接,上述多个第二电路在上述第二方向排列,上述多个第二电路中的各个第二电路与上述多条扫描线中的对应的一条扫描线连接,连接上述第一移位寄存器单元与上述多个第一电路的第一布线的长度比连接上述第二移位寄存器单元与上述多个第二电路的第二布线的长度小。

8.根据本发明一方式的显示装置,具备:多个像素,位于显示区域;多条信号线,在上述显示区域中在第一方向排列;多条扫描线,在上述显示区域中在与上述第一方向交叉的第二方向排列;以及扫描线驱动器,位于上述显示区域的外侧的周边区域,上述显示区域包含角部,上述多个像素在上述角部中被配置为台阶状,上述扫描线驱动器包含:第一移位寄存器单元、与上述第一移位寄存器单元连接的第一缓冲单元、上述第一移位寄存器单元的前段或后段的第二移位寄存器单元、与上述第二移位寄存器单元连接的第二缓冲单元,上述第一移位寄存器单元以及上述第二移位寄存器单元沿着上述台阶状的上述多个像素而配置,上述第一缓冲单元以及上述第二缓冲单元沿着上述台阶状的上述多个像素而配置,上述多条扫描线中的四条扫描线与上述第一缓冲单元连接,上述多条扫描线中的其他的四

条扫描线与上述第二缓冲单元连接,上述第一缓冲单元包含在上述第一方向排列的四个缓冲电路,上述第二缓冲单元包含在上述第二方向排列的四个缓冲电路。

9.大体上根据一技术方案,显示装置具备:显示区域,包含多个像素;上述显示区域的周围的周边区域;多条扫描线,在上述显示区域中沿第一方向延伸;多条信号线,在上述显示区域中在与上述第一方向交叉的第二方向上延伸;第一驱动器,被配置在上述周边区域中,被连接在上述多条扫描线上;以及第二驱动器,被配置在上述周边区域,并连接在上述多条信号线上。上述显示区域具有圆弧状的角部。上述第一驱动器包括向对应的上述扫描线供给电压的第一缓冲单元及第二缓冲单元、控制上述第一缓冲单元的第一移位寄存器单元、和控制上述第二缓冲单元的第二移位寄存器单元。在上述角部中,上述第一缓冲单元及上述第一移位寄存器单元的延伸方向相互一致。上述第二缓冲单元及上述第二移位寄存器单元的延伸方向相互不同。

10.根据这样的结构,能够得到能够实现窄边框化的显示装置。

附图说明

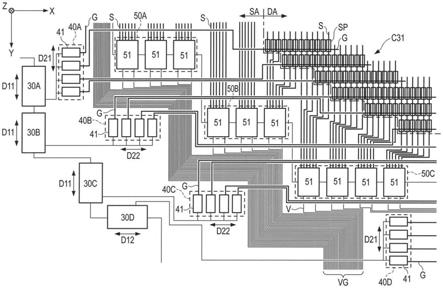

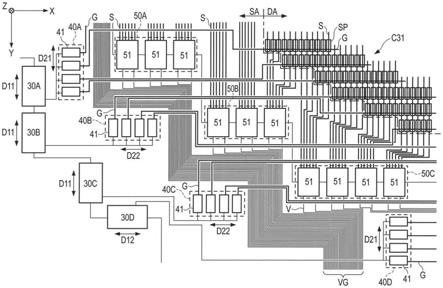

11.图1是概略地表示有关一实施方式的显示装置的结构例的平面图。

12.图2是概略地表示关于接触检测功能的显示装置的结构例的平面图。

13.图3是表示沿着图2的iii-iii线的显示面板的概略性的截面的图。

14.图4是概略地表示显示区域的角部的附近的周边电路的结构例的平面图。

15.图5是表示应用到扫描线驱动器中的等价电路的具体例的图。

16.图6是表示扫描线的驱动例的时间图。

17.图7是表示显示区域的角部的附近的周边电路的具体的结构例的平面图。

18.图8是表示缓冲单元的布局的一例的图。

19.图9是表示沿着图8的ix-ix线的缓冲电路的截面的一例的图。

20.图10是表示移位寄存器单元的详细的电路的一例的图。

21.图11是表示图10中的电路的动作的一例的时间图。

具体实施方式

22.以下,参照附图对一实施方式进行说明。另外,本公开不过是一例,关于本领域技术人员保持着发明的主旨而适当变更所能容易地想到的形态,当然包含在本发明的范围中。此外,附图为了使说明变得更明确,有与实际的形态相比关于各部的宽度、厚度、形状等示意地表示的情况,但不过是一例,并不限定本发明的解释。此外,在本说明书和个图中,有针对与关于已示出的图中上述要素发挥相同或类似的功能的构成要素赋予相同的标号而省略重复的详细的说明的情况。

23.在本实施方式中,作为显示装置的一例,例示了具备接触检测功能的液晶显示装置。该液晶显示装置例如可以用在智能电话、平板电脑终端、便携电话终端、笔记本型的个人计算机、车载设备、游戏设备等的各种装置中。在本实施方式中公开的主要的结构,对于有机电致发光显示装置等的自发光型的显示装置、具有电泳元件等的电子纸张型的显示装置、应用了mems(micro electro mechanical system、微机电系统)的显示装置、或者应用了电致变色的显示装置等也能够适用。此外,在本实施方式中公开的关于图像显示的结构

对于不具备接触检测功能的显示装置也能够适用。

24.图1是概略地表示有关本实施方式的显示装置dsp的结构例的平面图。在图中,第一方向x及第二方向y是相互交叉的方向,第三方向z是与第一方向x及第二方向y交叉的方向。在一例中,第一方向x、第二方向y及第三方向z相互正交,但也可以以90度以外的角度交叉。在本说明书中,将朝向表示第三方向z的箭头的前端的方向称作上方(或简单称作上),将从箭头的前端朝向相反的方向称作下方(或简单称作下)。

25.显示装置dsp具备显示面板pnl、布线基板f和控制器ct。显示面板pnl具备第一基板sub1、第二基板sub2、和配置在第一基板sub1及第二基板sub2之间的液晶层lc(详细参照图3)。进而,显示面板pnl具备显示图像的显示区域da、和将显示区域da包围的框边状的周边区域sa。

26.显示面板pnl具有第一端部e1、相对于显示区域da位于第一端部e1的相反侧的第二端部e2、第三端部e3、和相对于显示区域da位于第三端部e3的相反侧的第四端部e4。在图1的例子中,各端部e1、e2与第一方向x平行,各端部e3、e4与第二方向y平行。在各端部e2、e3、e4中,第一基板sub1及第二基板sub2的边缘对齐。第一端部e1相当于第一基板sub1的边缘。第一端部e1的侧的第二基板sub2的边缘位于比第一基板sub1的边缘更靠显示区域da侧。即,显示面板pnl在第一端部e1及显示区域da之间具有第一基板sub1不与第二基板sub2对置的非对置区域na(或端子区域)。

27.第一基板sub1具备各端部e1、e3之间的角部c11、各端部e1、e4之间的角部c12、各端部e2、e3之间的角部c13、和各端部e2、e4之间的角部c14。第二基板sub2具有角部c11的附近的角部c21、角部c12的附近的角部c22、角部c13的附近的角部c23和角部c14的附近的角部c24。显示区域da具有角部c11的附近的角部c31、角部c12的附近的角部c32、角部c13的附近的角部c33和角部c14的附近的角部c34。

28.在图1的例子中,第一基板sub1的各角部c11~c14、第二基板sub2的各角部c21~c24、显示区域da的各角部c31~c34都是圆弧状。作为一例,第一基板sub1的各角部c11~c14和第二基板sub2的各角部c23、c24具有第一曲率半径,第二基板sub2的各角部c21、c22具有第二曲率半径,显示区域da的各角部c31~c34具有第三曲率半径。第一至第三曲率半径相互不同,例如可以设为第一曲率半径>第三曲率半径>第二曲率半径。但是,各角部c11~c14、c21~c24、c31~c34的关系并不限于这里例示的关系。此外,也可以各角部c11~c14、c21~c24、c31~c34的至少一个不是圆弧状而是垂直的。

29.显示面板pnl在显示区域da中具备多个扫描线g和多个信号线s。各扫描线g分别在第一方向x上延伸,在第二方向y上隔开间隔排列。各信号线s分别在第二方向y上延伸,在第一方向x上隔开间隔排列。

30.显示区域da具有沿着第一方向x及第二方向y排列的多个像素px。像素px包括分别显示不同颜色的副像素sp。作为一例,像素px包括红色的副像素spr、绿色的副像素spg和蓝色的副像素spb。像素px的结构并不限于此,例如也可以还包括显示白色的副像素等,也可以包括与相同的颜色对应的多个副像素。在本公开中,有将副像素简单称作像素的情况。

31.各副像素sp具备开关元件sw、像素电极pe和共通电极ce。共通电极ce例如遍及多个副像素sp形成。开关元件sw与扫描线g、信号线s及像素电极pe电连接。

32.显示面板pnl在周边区域sa中具备连接着各扫描线g的扫描线驱动器gd1、gd2(第

一驱动器)、和连接着各信号线s的信号线驱动器sd(第二驱动器)。扫描线驱动器gd1被配置在显示区域da与第三端部e3之间,扫描线驱动器gd2被配置在显示区域da与第四端部e4之间。信号线驱动器sd被配置在显示区域da与非对置区域na之间。也可以将扫描线驱动器gd1、gd2的一方省略。

33.在图1的例子中,在角部c31、c33的附近,扫描线驱动器gd1与角部c31、c33同样以圆弧状弯曲。即,扫描线驱动器gd1包括与第二方向y平行地延伸的部分(第二方向y上的中腹部分)、和在与第一方向x及第二方向y交叉的方向上延伸的部分(第二方向y上的两端部分)。

34.此外,在角部c32、c34的附近,扫描线驱动器gd2与角部c32、c34同样以圆弧状弯曲。即,扫描线驱动器gd2包括与第二方向y平行地延伸的部分(第二方向y上的中腹部分)、和在与第一方向x及第二方向y交叉的方向上延伸的部分(第二方向y上的两端部分)。

35.此外,在角部c31、c32的附近,信号线驱动器sd与角部c31、c32同样以圆弧状弯曲。即,信号线驱动器sd具有与第一方向x平行地延伸的部分(第一方向x上的中腹部分)、和在与第一方向x及第二方向y交叉的方向上延伸的部分(第一方向x上的两端部分)。

36.角部c31的附近的信号线驱动器sd的端部位于扫描线驱动器gd1与显示区域da之间。角部c32的附近的信号线驱动器sd的端部位于扫描线驱动器gd2与显示区域da之间。

37.扫描线驱动器gd1、gd2对各扫描线g供给扫描信号。信号线驱动器sd对各信号线s供给影像信号。如果对与某个开关元件sw对应的扫描线g供给扫描信号,并且对连接在该开关元件sw上的信号线s供给影像信号,则通过扫描信号而开关元件sw成为导通状态,与影像信号对应的电压被施加在像素电极pe上。此时,通过像素电极pe与共通电极ce之间产生的电场,液晶层lc的液晶分子的取向从没有被施加电压的初始取向状态变化。通过这样的动作,在显示区域da中显示图像。

38.在非对置区域na中沿着第一端部e1设有连接端子t,在该连接端子t上连接着布线基板f。在图1的例子中,在布线基板f上安装着控制器ct。控制器ct具备控制扫描线驱动器gd1、gd2及信号线驱动器sd的显示驱动器r1、和接触检测用的检测驱动器r2。显示驱动器r1及检测驱动器r2的安装方式并不限于此,例如也可以安装在第一基板sub1上。此外,显示驱动器r1及检测驱动器r2也可以被安装到不同的部件上。

39.图2是概略地表示关于接触检测功能的结构例的显示装置dsp的平面图。显示装置dsp具备多个检测电极rx。各检测电极rx在显示区域da上在第一方向x上延伸,在第二方向y上排列。进而,在图2的例子中,多个共通电极ce被配置在显示区域da中。各共通电极ce在第二方向y上延伸,在第一方向x上排列。

40.各共通电极ce除了作为用于图像显示的电极的功能以外,还具有用来对接近于各检测电极rx与显示区域da的物体进行检测的作为驱动电极的功能。在本实施方式中,设想在第一基板sub1上配置各共通电极ce、在第二基板sub2上配置各检测电极rx的结构。但是,设置与共通电极ce分体的驱动电极的结构也能够适用于显示装置dsp。此外,检测电极rx及共通电极ce(或驱动电极)的配置方式能够是各种变形。例如,也可以在第二基板sub2上设置共通电极ce(或驱动电极),也可以在配置在显示面板pnl的显示面上的透明的基材上设置与检测电极rx及共通电极ce分体的驱动电极。

41.在图2的例子中,各检测电极rx与配置在周边区域sa中的焊盘p经由连接孔h电连

接。焊盘p经由配置在周边区域sa中的导线l1与连接端子t电连接。例如如图示那样,从第二端部e2起第奇数个检测电极rx与配置在第三端部e3与显示区域da之间的焊盘p连接,从第二端部e2起第偶数个检测电极rx与配置在第四端部e4与显示区域da之间的焊盘p连接。

42.图3是表示沿着图2的iii-iii线的显示面板pnl的概略性的截面的图。第一基板sub1具备玻璃基板或树脂基板等的第一基材10、第一绝缘层11、第二绝缘层12、第一取向膜13和上述的共通电极ce及像素电极pe。第一基板sub1也具备上述扫描线g、信号线s、开关元件sw等,但在图3中省略了图示。

43.焊盘p及导线l1被配置在第一基材10之上。也可以在焊盘p及导线l1与第一基材10之间夹装绝缘层。第一绝缘层11将焊盘p及导线l1覆盖。各共通电极ce被配置在第一绝缘层11之上。第二绝缘层12将各共通电极ce及第一绝缘层11覆盖。各像素电极pe被配置在第二绝缘层12之上,经由第二绝缘层12与共通电极ce对置。第一取向膜13将各像素电极pe及第一绝缘层12覆盖。

44.第二基板sub2具备玻璃基板或树脂基板等的第二基材20、滤色器层21和第二取向膜22。滤色器层21被配置在第二基材20之下。滤色器层21包括与上述副像素spr、spg、spb对应的颜色的滤色器。第二取向膜22将滤色器层21覆盖。另外,滤色器层21也可以配置在第一基板sub1上。

45.第一基板sub1及第二基板sub2经由密封件sl被贴合。在由第一取向膜13、第二取向膜22及密封件sl包围的空间中封入有液晶层lc。

46.检测电极rx被配置在第二基材20之上。上述连接孔h将第二基材20、滤色器层21、第二取向膜22、密封件sl、第一取向膜13、第二绝缘层12、第一绝缘层11贯通。连接孔h也可以还将焊盘p贯通。连接孔h例如如图示那样是朝向焊盘p前端细的锥状,但并不限于该例。在连接孔h的内部配置有导电性的连接部件c。经由该连接部件c将检测电极rx与焊盘p电连接。

47.像素电极pe及共通电极ce例如可以由ito(indium tin oxide)等的透明导电材料形成。检测电极rx、焊盘p及导线l1可以由ito等的透明导电材料或金属材料形成。在将检测电极rx用金属材料形成的情况下,例如可以使用将单层或多层构造的金属细线配置为网状或波形的电极图案。

48.另外,图3所示的截面构造不过是一例,除此以外在显示面板pnl中也能够应用各种结构。例如,共通电极ce也可以被配置在像素电极pe与液晶层lc之间,也可以被配置在与像素电极pe同层中,也可以配置在第二基板sub2中。此外,也可以在连接孔h的位置不配置第一取向膜13、滤色器层21或第二取向膜22。

49.在以上的结构中,在检测电极rx与共通电极ce之间形成第一电容。此外,如果用户的手指等的物体接近于显示区域da,则在该物体与检测电极rx之间形成第二电容。检测驱动器r2将用于物体检测的驱动信号向共通电极ce供给。此时,经由第一电容从检测电极rx向检测驱动器r2输出检测信号。该检测信号对应于第二电容的有无及第二电容的大小而变化。因而,基于该检测信号,检测驱动器r2能够检测接近于显示区域da的物体的有无及显示区域da中的物体的位置。

50.这里所述的检测方式例如被称作互电容方式。但是,物体的检测方式并不限于互电容方式,也可以是自电容方式。在自电容方式中,向检测电极rx供给驱动信号,并从检测

电极rx读出检测信号,基于该检测信号能够检测接近于显示区域da的物体的有无及显示区域da中的物体的位置。

51.接着,对配置在周边区域sa中的周边电路(扫描线驱动器gd1、gd2,信号线驱动器sd等)的结构进行说明。

52.图4是概略地表示角部c11、c21、c31的附近的周边电路的结构例的平面图。扫描线驱动器gd1具备多个移位寄存器单元30、和相对于各移位寄存器单元30各连接1个并且连接着至少1个扫描线g的多个缓冲单元40。各移位寄存器单元30构成对用于向各扫描线g依次供给扫描信号的时机进行控制的移位寄存器。缓冲单元40包括至少1个缓冲电路41。缓冲电路41在移位寄存器单元30的控制下,对扫描线g供给扫描信号(扫描电压)。

53.第一基板sub1在周边区域中具备包括多个视频线v的视频线群vg。视频线群vg沿着信号线驱动器sd配置。视频线群vg沿着显示区域da的角部c31弯曲。构成视频线群vg的各视频线v经由上述连接端子t及布线基板f与显示驱动器r1电连接。在图4的例子中,在视频线群vg与显示区域da之间配置有信号线驱动器sd。进而,在信号线驱动器sd位于扫描线驱动器gd1与显示区域da之间的区域中,视频线群vg延伸到扫描线驱动器gd1与信号线驱动器sd之间。

54.信号线驱动器sd具备多个选择器单元50。各选择器单元50包括至少1个选择器电路51(选择器开关)。在选择器电路51上,连接着n条视频线v和比n大的m条(m>n)的信号线s。在一例中,是n=2且m=6。选择器电路51将与视频线v连接的信号线s以时间划分来切换。由此,能够用比配置在显示区域da中的信号线s少的数量的视频线v向各信号线s供给影像信号。

55.将上述检测电极rx与连接端子t连接的导线l1被沿着第一基板sub1的边缘部配置。即,扫描线驱动器gd1、信号线驱动器sd及视频线群vg位于导线l1与显示区域da之间。导线l1在角部c11的附近与角部c11同样地以圆弧状弯曲。在图4的例子中,导线l1与第一基板sub1的边缘部之间的距离遍及整体是一定的,但也可以部分地不同。例如,在角部c11的附近,导线l1与第一基板sub1的边缘部之间的距离也可以随着朝向第一端部e1而增大。

56.扫描线驱动器gd1及信号线驱动器sd在显示区域da的角部c31的附近沿着角部c31弯曲。因而,角部c31的附近的信号线驱动器sd的一部分位于比距第一端部e1最近的显示区域da的外缘eda1更靠第二端部e2侧(图中的上侧)。此外,角部c31的附近的扫描线驱动器gd1的一部分位于比距第三端部e3最近的显示区域da的外缘eda2更靠第四端部e4侧(图中的右侧)。

57.各选择器单元50中包含的选择器电路51的数量,越是距信号线驱动器sd的端部较近的选择器单元50所包含的选择器电路51的数量则越少。由此,各选择器单元50的第一方向x上的宽度,越是距信号线驱动器sd的端部较近的选择器单元50的第一方向x上的宽度则越小。

58.在图4的例子中,视频线群vg包括在第一方向x上延伸的部分和在第二方向y上延伸的部分交替地反复的台阶状的区域,对于该区域的1个段配置有各1个选择器单元50。但是,也可以对1个段配置多个选择器单元50。此外,也可以是视频线群vg的至少一部分在与第一方向x及第二方向y交叉的方向上延伸。

59.这里,作为一例,着眼于各移位寄存器单元30及各缓冲单元40中的、移位寄存器单

元30a、30b、30c及与它们连接的缓冲单元40a、40b、40c。移位寄存器单元30a与移位寄存器单元30b相邻,移位寄存器单元30b与移位寄存器单元30c相邻。此外,缓冲单元40a与缓冲单元40b相邻,缓冲单元40b与缓冲单元40c相邻。

60.将移位寄存器单元30a与移位寄存器单元30b的第一方向x上的间隔定义为dx11,将移位寄存器单元30b与移位寄存器单元30c的第一方向x上的间隔定义为dx12,将移位寄存器单元30a与移位寄存器单元30b的第二方向y上的间隔定义为dy11,将移位寄存器单元30b与移位寄存器单元30c的第二方向y上的间隔定义为dy12。在此情况下,在图4的例子中,间隔dx11与间隔dx12相互不同。具体而言,是dx11<dx12,为了各移位寄存器单元30a、30b在第一方向x上不错开,间隔dx11是零。进而,在图4的例子中,间隔dy11与间隔dy12相互不同。具体而言,是dy11<dy12。作为其他的例子,各移位寄存器单元30a、30b、30c也可以配置为dx11>dx12,也可以配置为dy11≥dy12。

61.与间隔dx11、dx12同样,在图4的例子中,缓冲单元40a及缓冲单元40b的第一方向x上的间隔与缓冲单元40b及缓冲单元40c的第一方向x上的间隔相互不同。此外,与间隔dy11、dy12同样,缓冲单元40a及缓冲单元40b的第二方向y上的间隔与缓冲单元40b及缓冲单元40c的第二方向y上的间隔相互不同。

62.进而,作为一例,着眼于各选择器单元50中的选择器单元50a、50b、50c。选择器单元50a与选择器单元50b相邻,选择器单元50b与选择器单元50c相邻。各选择器单元50a、50b、50c在第一方向x及第二方向y上相互错开。

63.将选择器单元50a与选择器单元50b的第一方向x上的间隔定义为dx21,将选择器单元50b与选择器单元50c的第一方向x上的间隔定义为dx22,将选择器单元50a与选择器单元50b的第二方向y上的间隔定义为dy21,将选择器单元50b与选择器单元50c的第二方向y上的间隔定义为dy22。在此情况下,在图4的例子中,间隔dx21与间隔dx22相互不同。具体而言,是dx21<dx22。此外,在图4的例子中,间隔dy21与间隔dy22大致一致。作为其他的例子,各选择器单元50a、50b、50c也可以配置为dx21≥dx22,也可以配置为间隔dy21与间隔dy22相互不同。

64.这样,通过将各移位寄存器单元30及各缓冲单元40的各方向x、y上的间隔在角部c31的附近调整,能够实现沿着角部c31以圆弧状弯曲的扫描线驱动器gd1。同样,通过将各选择器单元50的各方向x、y上的间隔在角部c31的附近调整,能够实现沿着角部c31以圆弧状弯曲的信号线驱动器sd。

65.另外,在以上的说明中,相邻的2个单元的第一方向x上的间隔(dx11、dx12、dx21、dx22等)相当于这些单元各自的第一方向x上的中心间的距离。此外,相邻的2个单元的第二方向y上的间隔(dy11、dy12、dy21、dy22等)相当于这些单元各自的第二方向y上的中心间的距离。

66.移位寄存器单元30如后述那样由多个元件构成,各移位寄存器单元30内的各元件的配置大致相同。此外,缓冲单元40具有多个缓冲电路41,在缓冲单元40内,各缓冲电路41在任意的方向上排列。

67.在图4中,移位寄存器单元30被用在第二方向y上长的纵长的矩形来表示。这表示构成移位寄存器单元30的多个元件在第二方向y上排列。此外,缓冲单元40在图中上侧被用纵长的矩形来表示,在图中下侧被用在第一方向x上长的横长的矩形来表示。这是纵长的矩

形表示缓冲电路41在第二方向y上排列,横长的矩形表示缓冲电路41在第一方向x上排列。

68.在显示区域da的角部c31的附近,周边区域sa从图中上侧朝向下侧而第一方向x的宽度变宽。并且,随着周边区域sa的宽度,缓冲单元40从纵长的矩形变化为横长的矩形。即,在缓冲单元40a中,周边区域sa的第一方向x的宽度没有变宽到能够将缓冲电路41在第一方向x上排列,而在缓冲单元40b中,周边区域sa的第一方向x的宽度变宽到能够将缓冲电路41在第一方向x上排列的程度。

69.但是,在形成缓冲单元40b、40c的区域中,周边区域sa的第一方向x的宽度变宽,但由于需要与选择器单元50a、50b在第一方向x上排列形成,所以需要考虑上述相邻的2个单元的第一方向x上的间隔和第二方向y上的间隔、及可配置的视频线v的数量等。

70.进而,在图中下侧,周边区域sa的第一方向x的宽度变宽,相对于此,第二方向y的宽度变窄,被限制为一定的宽度。因而,考虑形成选择器单元50的区域来决定移位寄存器单元30和缓冲单元40的位置关系。

71.图1所示的显示区域da的角部c33的附近的扫描线驱动器gd1的结构与角部c31的附近的扫描线驱动器gd1的结构是同样。此外,显示区域da的角部c32的附近的扫描线驱动器gd2、信号线驱动器sd、视频线群vg及导线l1的结构与角部c31的附近的这些结构是同样的。进而,显示区域da的角部c34的附近的扫描线驱动器gd2的结构与角部c33的附近的扫描线驱动器gd1的结构是同样的。角部c31~c34的附近的周边区域sa的结构并不限定于这里例示的结构,可以考虑配置的电路及布线的布局来适当变更。

72.图5是表示能够应用到扫描线驱动器gd1中的等价电路的具体例的图。这里,着眼于各移位寄存器单元30及各缓冲单元40中的、移位寄存器单元30a、缓冲单元40a、移位寄存器单元30b以及缓冲单元40b。

73.移位寄存器单元30a具备逻辑电路31a、32a、33a、时钟供给开关34a和定电压供给开关35a。缓冲单元40a包括4个缓冲电路41。在各缓冲电路41上,分别连接着扫描线ga1~ga4。各缓冲电路41具备栅极脉冲供给开关42a和栅极低电压供给开关43a。另外,缓冲单元40a中包含的缓冲电路41的数量并不限定于4个。

74.时钟供给开关34a及栅极脉冲供给开关42a由n型的tft(thin film transistor)和p型的tft构成。定电压供给开关35a及栅极低电压供给开关43a由n型的tft构成。

75.移位寄存器单元30b具备逻辑电路31b、32b、33b、时钟供给开关34b和定电压供给开关35b。缓冲单元40b的结构与缓冲单元40a是同样的,所以省略电路结构的图示。在图5的例子中,在缓冲单元40b上分别连接着扫描线gb1~gb4。时钟供给开关34b由n型的tft和p型的tft构成。定电压供给开关35b由p型的tft构成。

76.在逻辑电路31a上,连接着包括开关61a、62a的扫描方向设定开关60a。在逻辑电路31b上,连接着包括开关61b、62b的扫描方向设定开关60b。这些扫描方向设定开关60a、60b决定将各移位寄存器单元30扫描的方向。具体而言,以移位寄存器单元30a的前段的移位寄存器单元30、移位寄存器单元30a、移位寄存器单元30b、移位寄存器单元30b的后段的移位寄存器单元30

…

的顺序,将各移位寄存器单元30扫描。开关61a、62a、61b、62b都由n型的tft和p型的tft构成。

77.在逻辑电路31a中,被输入来自扫描方向设定开关60a的信号ina和信号backa。逻辑电路31a向逻辑电路32a、时钟供给开关34a的p型的tft及定电压供给开关35a输出将各信

号ina、backa的逻辑和反转后的信号。逻辑电路32a将来自逻辑电路31a的信号反转并向时钟供给开关34a的n型的tft输出。对应于来自逻辑电路31a的信号,时钟供给开关34a及定电压供给开关35a的某一方被导通。在时钟供给开关34a被导通的期间中,时钟供给开关34a输出时钟ckv。另一方面,在定电压供给开关35a被导通的期间中,定电压供给开关35a输出一定的低电压vgl。这些时钟ckv及低电压vgl被作为输出信号out1向缓冲单元40a输出,并且被作为上述信号backa向逻辑电路31a输出。进而,输出信号out1被逻辑电路33a反转,作为输出信号xout1被向缓冲单元40a输出。

78.在缓冲单元40a中,输出信号out1被输入到各栅极脉冲供给开关42a的n型的tft中。输出信号xout1被输入到各栅极脉冲供给开关42a的p型的tft和各栅极低电压供给开关43a中。如果输出信号out1是l电平(低电压)、输出信号xout1是h电平(高电压),则各栅极脉冲供给开关42a被断开,并且各栅极低电压供给开关43a被导通。在此情况下,从各栅极低电压供给开关43a向各扫描线ga1~ga4输出低电压vgl。低电压vgl是将上述开关元件sw断开的电压。

79.另一方面,如果输出信号out1是h电平,输出信号xout1是l电平,则各栅极脉冲供给开关42a被导通,并且各栅极低电压供给开关43a被断开。在此情况下,从各栅极脉冲供给开关42a向各扫描线ga1~ga4分别输出启动信号enb1~enb4。

80.输出信号xout1经由扫描方向设定开关60b作为信号inb被向移位寄存器单元30b的逻辑电路31b输出。在逻辑电路31b中也被输入信号backb。逻辑电路31b向逻辑电路32b、时钟供给开关34b的n型的tft及定电压供给开关35b输出相当于将各信号inb、backb反转后的信号的逻辑和的信号。逻辑电路32b将来自逻辑电路31b的信号反转并向时钟供给开关34b的p型的tft输出。对应于来自逻辑电路31b的信号,时钟供给开关34b及定电压供给开关35b的某一方被导通。在时钟供给开关34b被导通的期间中,时钟供给开关34b输出时钟ckv。另一方面,在定电压供给开关35b被导通的期间中,定电压供给开关35b输出一定的高电压vgh。这些时钟ckv及高电压vgh作为输出信号xout2被向缓冲单元40b输出,并且作为上述的信号backb被向逻辑电路31b输出。进而,输出信号xout2被逻辑电路33b反转,作为输出信号out2被向缓冲单元40b输出。输出信号out2也被向与下段的移位寄存器单元30对应的扫描方向设定开关输出。通过输出信号out2、xout2进行的缓冲单元40b的驱动与通过输出信号out1、xout1进行的缓冲单元40a的驱动是同样的。

81.另外,时钟ckv及启动信号enb1~enb4等例如被从上述显示驱动器r1供给。

82.使用图6的时间图,对图5的电路结构的各扫描线ga1~ga4的驱动例进行说明。如果信号ina从l电平成为h电平,则从逻辑电路31a输出的信号成为l电平,时钟供给开关34a被导通,并且定电压供给开关35a被断开。此时,如果被供给h电平的时钟ckv,则输出信号out1、xout1分别成为h电平和l电平,所以各栅极脉冲供给开关42a被导通,各栅极低电压供给开关43a被断开。由此,在各扫描线ga1~ga4中被供给启动信号enb1~enb4。启动信号enb1~enb4是时钟ckv将作为h电平或l电平的期间分成4份那样的4相时钟。即,如图6所示,在时钟ckv是h电平的期间中,启动信号enb1~enb4依次切换为h电平。由此,在各扫描线ga1~ga4中依次被供给脉冲状的扫描信号。

83.然后,如果时钟ckv成为l电平,则信号inb成为h电平,从逻辑电路31b输出的信号成为h电平。因而,时钟供给开关34b被导通,并且定电压供给开关35b被断开,输出信号

out2、xout2分别成为h电平和l电平。在该状态下,启动信号enb1~enb4依次切换为h电平,在各扫描线gb1~gb4中依次被供给脉冲状的扫描信号。

84.通过将移位寄存器单元30a及缓冲单元40a的结构和移位寄存器单元30b及缓冲单元40b的结构交替地应用到扫描线驱动器gd1的各移位寄存器单元30及各缓冲单元40中,能够对各扫描线g依次供给扫描信号。另外,对于扫描线驱动器gd2也能够应用同样的结构。

85.接着,使用图7的平面图,对显示区域da的角部c31的附近的周边电路的具体的结构例进行说明。这里例示的结构也能够对显示区域da的角部c32的附近的周边电路应用。进而,移位寄存器单元30及缓冲单元40的结构也能够对显示区域da的其他的角部c32、c33、c34的附近的周边电路应用。

86.图7所示的周边电路包括各移位寄存器单元30a、30b、30c、30d、各缓冲单元40a、40b、40c、40d、各选择器单元50a、50b、50c和视频线群vg。移位寄存器单元30d与移位寄存器单元30c相邻。缓冲单元40d连接在移位寄存器单元30d上。

87.各缓冲单元40a、40b、40c、40d都包括4个缓冲电路41。对于各缓冲电路41的各自连接着1条扫描线g。选择器单元50a及选择器单元50b分别包括3个选择器电路51,选择器单元50c包括4个选择器电路51。对于选择器电路51的各自,连接着2条视频线v和6条信号线s。在各选择器单元50a、50b、50c中,选择器电路51在第一方向x上排列。各扫描线g及各信号线s也延伸到显示区域da中。显示区域da的各副像素sp在角部c31的附近以台阶状排列,通过调整构成各段的副像素sp的数量,能够实现图4等所示那样的圆弧状的角部c31。

88.在图7的例子中,各移位寄存器单元30a、30b、30c的延伸方向d11与移位寄存器单元30d的延伸方向d12相互不同。这里,移位寄存器单元30的延伸方向例如相当于移位寄存器单元30的较长方向。移位寄存器单元30的延伸方向也可以是移位寄存器单元30中包含的tft等的元件的排列方向。

89.此外,在图7的例子中,各缓冲单元40a、40d的延伸方向d21与各缓冲单元40b、40c的延伸方向d22相互不同。这里,缓冲单元40的延伸方向例如相当于缓冲单元40的较长方向。缓冲单元40的延伸方向也可以是缓冲单元40中包含的缓冲电路41的排列方向。

90.作为一例,延伸方向d11、d21与第二方向y平行,延伸方向d12、d22与第一方向x平行。在此情况下,移位寄存器单元30a的延伸方向与缓冲单元40a的延伸方向相互一致。另一方面,移位寄存器单元30b的延伸方向与缓冲单元40b的延伸方向、移位寄存器单元30c的延伸方向与缓冲单元40c的延伸方向、移位寄存器单元30d的延伸方向与缓冲单元40d的延伸方向分别相互不同。延伸方向d11、d12、d21、d22也可以是与第一方向x或第二方向y交叉的方向。

91.这样,通过将一对移位寄存器单元30及缓冲单元40的各自的延伸方向适当地调整为相互一致的方向或相互不同的方向,能够有效利用周边区域sa的空间。结果,能够减小周边区域sa的面积,所以能够实现显示装置dsp的窄边框化。

92.在图7的例子中,各缓冲单元40a、40b、40c被配置在视频线群vg的外侧(显示区域da的相反侧),缓冲单元40d被配置在视频线群vg与显示区域da之间。通过这样调整缓冲单元40的配置位置,能够更有效地利用周边区域sa的空间。

93.接着,使用图8的布局图说明缓冲单元40的延伸方向。图8是图5中记载的缓冲单元40a具有的缓冲电路41的详细图,是构成缓冲电路41的要素的布局图。图9是沿着图8的ix-

ix线的缓冲电路41的剖视图。这里例示的结构对于显示区域da的其他角部c32、c33、c34的附近的周边电路也能够应用。另外,在图9中,详细地表示了从图3所示的剖视图的第一基材10到第一绝缘层11形成的缓冲电路41的结构。

94.在图8中,栅极脉冲供给开关42a的n型的tft(以后称作第一n型晶体管)、栅极脉冲供给开关42a的p型的tft(以后称作第一p型晶体管)和栅极低电压供给开关43a(以后称作第二n型晶体管)共用半导体层451而相邻配置。

95.标号421是第一n型晶体管的栅极,连接在布线471上,被供给图5所示的输出信号out1。在图中,为了容易理解布线,也一起标注了信号名。标号443是兼作为第一n型晶体管的漏极和第一p型晶体管的源极的区域。区域443连接在布线473上,被供给图5所示的启动信号enb1。标号425是兼作为第一n型晶体管的源极和第二n型晶体管的源极的区域。如果输出信号out1成为h电平,则第一n型晶体管成为导通状态,从第一n型晶体管的源极425向布线463输出启动信号enb1。

96.标号441是第一p型晶体管的栅极,连接在布线475上,被供给图5所示的输出信号xout1。标号445是第一p型晶体管的漏极。如果输出信号xout1成为l电平,则第一p型晶体管成为导通状态,从第一p型晶体管的漏极445向布线465输出启动信号enb1。

97.另外,输出信号xout1是将输出信号out1反转后的信号,所以第一n型晶体管和第一p型晶体管同时成为导通状态,输出启动信号enb1。

98.标号431是第二n型晶体管的栅极,连接在布线477上,被供给图5所示的输出信号xout1。标号433是第二n型晶体管的漏极。如果输出信号xout1成为h电平,则第二n型晶体管成为导通状态,经由布线479供给的低电压vgl被从第二n型晶体管的源极425向布线463输出。

99.如图9中示出了沿着图8的ix-ix线的剖视图,在玻璃基板或树脂基板等的第一基材10之上,形成有半导体层451。在半导体层451中,通过杂质的投入等,形成第一p型晶体管的漏极445、兼作为第一n型晶体管的漏极和第一p型晶体管的源极的区域443、兼作为第一n型晶体管的源极和第二n型晶体管的源极的区域425、第二n型晶体管的漏极433。另外,在半导体层451与第一基材10之间形成有基底层111。

100.在半导体层451之上形成有绝缘膜113,在绝缘膜113之上形成有第一p型晶体管的栅极441、第一n型晶体管的栅极421、第二n型晶体管的栅极431。在各栅极421、431、441之上形成有绝缘膜115,在绝缘膜115之上,形成有供给低电压vgl的布线(电源线)479、供给启动信号enb1的布线473、连接在兼作为第一和第二n型晶体管的源极的区域425上的布线463、和连接在p型晶体管的漏极445上的布线465。

101.缓冲电路41的输出经由布线463连接在布线465上,布线465连接在扫描线ga1上。

102.在绝缘膜115上形成有多个贯通孔461。经由各贯通孔461,第一p型晶体管的漏极445与布线463被电连接,布线473与兼作为第一n型晶体管的漏极和第一p型晶体管的源极的区域443被电连接,兼作为第一和第二n型晶体管的源极的区域425与布线463被电连接,第二n型晶体管的漏极433与供给低电压vgl的布线479被电连接。

103.作为图8中的信号的流动,来自位于图中左方的移位寄存器单元30的输出信号out1、xout1被输入到缓冲电路41中,来自缓冲电路41的信号被输入到位于图中右方的扫描线g中。因而,信号的流动沿着第一方向x。此外,将缓冲电路41的形状赋予特征的是半导体

层451的形状。半导体层451以由栅极脉冲供给开关42a和栅极低电压供给开关43a共用的方式、在平面观察时形成为矩形,图中沿着第一方向x的边比沿着第二方向y的边长。

104.进而,第二n型晶体管的漏极433、兼作为第一n型晶体管的源极和第二n型晶体管的源极的区域425、兼作为第一n型晶体管的漏极和第一p型晶体管的源极的区域443、和第一p型晶体管的漏极445以沿着矩形的半导体层451的长边在第一方向x上排列的方式配置。

105.在图5所示的缓冲单元40中,排列配置有多个图8所示的缓冲电路41。在图8所示的缓冲电路41的结构中,在将多个缓冲电路41以相邻的方式排列的情况下,相邻的2个缓冲电路41以各自的半导体层451的长边对置的方式被排列。因而,在图8中,由于沿着第二方向y形成多个缓冲电路41,所以缓冲单元40的延伸方向为第二方向y。

106.如上述那样,在显示区域da的角部c31、c32、c33、c34的附近,按照周边区域sa的宽度,缓冲单元40具有在第二方向y上较长的矩形和在第一方向x上较长的矩形的2个延伸方向。在第二方向y上以较长的矩形表示的缓冲单元40沿着第二方向y形成有多个缓冲电路41并在第二方向y上延伸。在第一方向x上以较长的矩形表示的缓冲单元40沿着第一方向x形成有多个缓冲电路41并在第一方向x上延伸。

107.接着,图10中表示了移位寄存器单元30a、30b的详细的电路图。另外,图10是电路图,但表示各晶体管的电路记号的配置/位置关系表示形成各晶体管的第一基材10上的配置/位置关系。

108.在图10中,p型的晶体管311、313和n型的晶体管315、317形成了图5的逻辑电路(nor)31a。信号ina输入到p型的晶体管311的栅极和n型的晶体管315的栅极中。p型的晶体管313和n型的晶体管315的输出被连接在节点n1上。节点n1被连接在p型的晶体管341的栅极和n型的晶体管351(定电压供给开关35a)的栅极上。另外,在图10中,图5的逻辑电路(逆变器)32a和时钟供给开关(传输门)34a的n型的晶体管被省略。因而,时钟供给开关34a由p型的晶体管341构成。

109.如果节点n1是l电平,则p型的晶体管341成为导通状态,时钟ckv被作为输出信号out1及信号backa输出。如果节点n1是h电平,则n型的晶体管351成为导通状态,低电压vgl被作为输出信号out1及信号backa输出。如果信号backa是l电平,则p型的晶体管313成为导通状态,如果信号backa是h电平,则n型的晶体管317成为导通状态。如果p型的晶体管313和311成为导通状态,则在节点n1被供给高电压vgh。相对于此,如果n型的晶体管317成为导通状态,则在节点n1被供给低电压vgl。

110.由n型的晶体管331和p型的晶体管333构成了图5的逻辑电路(逆变器)33a。从逻辑电路33a输出的信号被反转,被作为输出信号xout1输出。输出信号xout1经由构成开关61b的n型的晶体管611和p型的晶体管613,作为信号inb被向移位寄存器单元30b的逻辑电路(nor)31b输出。另外,在扫描方向控制线621是h电平且扫描方向控制线623是l电平的情况下,信号从移位寄存器单元30a朝向30b移动。在扫描方向控制线621是l电平且扫描方向控制线623是h电平的情况下,信号从移位寄存器单元30b朝向30a移动。

111.逻辑电路31b由n型的晶体管321、323和p型的晶体管325、327构成。信号inb输入到n型的晶体管321的栅极和p型的晶体管325的栅极中。n型的晶体管323和p型的晶体管325的输出连接在节点n2上。节点n2连接在p型的晶体管343(定电压供给开关35b)的栅极和n型的晶体管353的栅极上。另外,在图10中,图5的逻辑电路(逆变器)32b和时钟供给开关(传输

门)34b的p型的晶体管被省略。因而,时钟供给开关34b由n型的晶体管353构成。

112.如果节点n2是h电平,则n型的晶体管353成为导通状态,时钟ckv被作为输出信号xout2及信号backb输出。如果节点n2是l电平,则p型的晶体管343成为导通状态,高电压vgh被作为输出信号xout2及信号backb输出。如果信号backb是h电平,则n型的晶体管323成为导通状态,如果信号backb是l电平,则p型的晶体管327成为导通状态。如果n型的晶体管323和321成为导通状态,则在节点n2被供给低电压vgl。相对于此,如果p型的晶体管327成为导通状态,则在节点n2被供给高电压vgh。

113.由n型的晶体管337和p型的晶体管335构成了图5的逻辑电路(逆变器)33b。由逻辑电路33b将信号反转,作为输出信号out2输出。

114.接着,使用图11的时间图,说明图10所示的电路的动作。在时刻t1,来自移位寄存器单元30a的前段的信号ina从l电平变化为h电平。信号ina是l电平,n型的晶体管315成为导通状态,节点n1成为l电平。节点n1成为l电平,从而p型的晶体管341成为导通状态,但在从时刻t1到t2的期间中,由于时钟ckv是l电平,所以输出信号out1及信号backa是l电平。

115.接着,如果成为时刻t2,则时钟ckv从l电平变化为h电平,在从时刻t2到t3的期间中,输出信号out1及信号backa成为h电平。信号backa是h电平,n型的晶体管351成为导通状态,所以节点n1成为l电平,p型的晶体管341的导通状态被维持。此外,在从时刻t2到t3的期间中,被逆变器33a反转的信号xout1是l电平,被输入到移位寄存器单元30a中的信号inb是l电平。

116.如果成为时刻t3,则时钟ckv从l电平变化为h电平,信号backa成为l电平,所以n型的晶体管317成为断开状态,p型的晶体管313成为导通状态。在时刻t3,由于信号ina是l电平,所以p型的晶体管311成为导通状态。因此,通过高电压vgh,节点n1成为h电平,在时刻t3以后,节点n1以h电平被维持。

117.如上述那样,在图10中,表示各晶体管的电路记号的配置/位置关系表示第一基材10上的配置/位置关系。在图10中,构成移位寄存器单元30的主要的晶体管形成在供给高电压vgh的布线481和供给低电压vgl的布线483所夹着的区域中。即,构成移位寄存器单元30的逻辑电路31a、33a、31b、33b、时钟供给开关34a、34b、定电压供给开关35a、35b沿着布线481和483所延伸的第二方向y形成。因而,在图10中,各移位寄存器单元30a和30b的延伸方向成为布线481和483延伸的第二方向y。

118.另外,对于高电压vgh及低电压vgl而言,只要低电压vgl是比高电压vgh低电压就可以。高电压vgh及低电压vgl是逻辑电路31a、33a、31b、33b、时钟供给开关34a、34b、定电压供给开关35a、35b的电源电压,也是能够控制各元件的导通和断开的电压。

119.如上述那样,在显示区域da的角部c31、c32、c33、c34的附近,按照周边区域sa的宽度,移位寄存器单元30具有在第二方向上较长的矩形和在第一方向上较长的矩形的2个延伸方向。在第二方向y上以较长的矩形表示的移位寄存器单元30,其供给高电压vgh及低电压vgl的各布线沿着第二方向y形成,在第二方向y上延伸。在第一方向x上以较长的矩形表示的移位寄存器单元30,其供给高电压vgh及低电压vgl的各布线沿着第一方向x形成,在第一方向x上延伸。

120.这样,通过具有多个缓冲单元40及移位寄存器单元30的延伸方向,能够调整缓冲单元40及移位寄存器单元30的配置位置,能够有效利用周边区域sa的空间。

121.此外,如使用图4说明那样,通过使相邻的移位寄存器单元30的间隔、相邻的缓冲单元40的间隔、还有相邻的选择器单元50的间隔不为一定,至少在一部分中不同,能够调整扫描线驱动器gd1、gd2及信号线驱动器sd的整体的形状。由此,即使如在本实施方式中例示那样角部c31~c34是圆弧状等情况下,显示区域da是非矩形状,也能够实现最优的形状的扫描线驱动器gd1、gd2及信号线驱动器sd,减小周边区域sa的面积。

122.此外,如使用图5及图6说明那样,如果是用1个移位寄存器单元30控制多个缓冲单元40的结构,则能够减少扫描线驱动器gd1、gd2中包含的移位寄存器单元30的数量。由此,能够进一步减小周边区域sa的面积。

123.另外,对于如在本实施方式中例示的多个移位寄存器单元30、多个缓冲单元40、多个选择器单元50、多个扫描线g、多个信号线s那样相同或类似的多个要素,可以适当地附加“第一”、“第二”、“第三”、

…“

第n”那样的语言而相互识别。

124.在本发明的思想范畴中,如果是本领域技术人员所能够想到各种变形例,关于这些变形例也应理解为属于本发明的范围。例如,本领域技术人员对上述各实施方式适当进行了构成要素的追加、删除或设计变更后的形态、或者进行了工序的追加、省略或条件变更的形态,也只要具备本发明的主旨,就包含在本发明的范围中。

125.此外,应理解为,关于在各实施方式中叙述的技术方案所带来的其他的作用效果,通过本说明书的记载能够明了的内容或者本领域技术人员能够适当地想到的内容,当然是本发明所带来的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。