1.本发明涉及一种灵敏放大器,具体涉及一种适用于静态随机存储器(static random access memory,sram)中数据读出模块灵敏放大器(sense amplifier,sa),特别涉及用于补偿和消除输入失调电压(offset voltage)的影响、提高灵敏度的灵敏放大器,属于集成电路设计技术领域。

背景技术:

2.目前被业内广泛使用的锁存器型差分灵敏放大器,不仅结构简单,而且正反馈结构使位线间的压差被快速放大。

3.其电路基于全差分放大器进行设计,输入输出节点共用,且输出电位能低至零电平,高至供电电压。核心结构为交叉耦合的反相器,起到数据锁存的作用;供电用的电流源由单级nmos管实现;通过增加一组共栅pmos管,可以将内部节点置位至供电电位。由于差分结构的原因,不可避免的引入输入失调电压,而且工艺节点越小,电路失调越严重。

4.降低灵敏放大器的失调电压是新型灵敏放大器的重要设计指标。目前常用的手段有以下几种:第一种方法利用热载流子注入(hot carrier injection)校准手段,通过调节某个晶体管的阈值电压,使相邻的差分对管匹配;但是芯片测试成本较高、不稳定性因素偏多,而且电路可能出现电学特性退化的现象。第二种方法利用内建自测(built

‑

in self

‑

test,bist)原理,内置多组相同尺寸的灵敏放大器,分别对各组进行测试,测试完成后仅有其中一组工作,缺点是外围控制电路较为复杂。第三种方法利用衬底电压偏置调制效应的原理,通过调节衬底电平值来减小阈值电压的失配,但该方法提高了灵敏放大器电路对衬底偏置电压的精度要求,使电路的实现难度提高。

5.中国电子科技集团公司第五十八研究所在2018年申请的专利(申请号:cn201822236118.0)的技术方案中,通过引入锁存器型灵敏放大器,作为输入失调自调整控制电路;根据失调信息产生对应的调整控制信号,实现灵敏放大过程中两个内部节点放电速度的平衡,来降低失调电压。虽然降低了失调电压,提高了灵敏度;但是引入的失调自调整控制电路检测失调的时间较长,实际上并没有在数据读出速度上做出大幅的改善,而且灵敏放大电路电源到地之间mos管级数太多,输出电压余量较小。

技术实现要素:

6.本发明要解决技术问题是:克服上述技术的缺点,提供一种基于线性电流反馈原理进行失调补偿的电压型灵敏放大器。

7.为了解决上述技术问题,本发明提出的技术方案是:一种灵敏放大器,包括:失调检测电路和灵敏放大电路;所述灵敏放大电路将sram存储阵列的位线上的压差信号放大并进行输出;所述失调检测电路的输入端连接第一预充电压、第一使能电压、输入信号控制电压;所述失调检测电路的失调检测输入端和失调检测输出端与所述灵敏放大电路相连;所述灵敏放大电路的输入端连接第二预充电压、第二使能电压、位线输入控制电压。

8.上述方案进一步的改进在于:所述失调检测电路包括:第一至第七pmos管、第一至第三nmos管;所述第一pmos管和第二pmos管的源极均连接电源,栅极均与所述第三pmos管的栅极连接;所述第一pmos管的漏极连接所述第三pmos管的源极,所述第二pmos管的漏极连接所述第三pmos管的漏极;所述第三pmos的栅极连接所述第一预充电压;所述第一pmos管和第二pmos管的漏极构成所述失调检测输出端;所述第四pmos管的源极与所述第五pmos管的漏极构成所述失调检测输入端;所述第四pmos管与第五pmos管的栅极均连接所述输入信号控制电压;所述第四pmos管的漏极连接所述第一pmos管的漏极;所述第五pmos管的源极连接所述第三pmos管的漏极;所述第六pmos管和第七pmos管的源极均连接所述电源;所述第六pmos管的栅极连接所述第七pmos管的漏极,所述第七pmos管的栅极连接所述第六pmos管的漏极;所述第四pmos管的漏极还与所述第六pmos管的漏极连接;所述第五pmos管的源极还连接所述第七pmos管的漏极;所述第一nmos管的栅极连接所述第五pmos管的漏极,漏极连接所述第六pmos管的漏极;所述第二nmos管的栅极连接所述第四pmos管的源极,漏极连接所述第七pmos管的漏极;所述第一nmos管与第二nmos管的源极均与所述第三nmos管的漏极连接;所述第一nmos管的漏极与第二nmos管的漏极之间串联有由两个二极管反向并联构成限幅器;所述第三nmos管的栅极连接所述第一使能电压,源极接地。

9.上述方案进一步的改进在于:所述灵敏放大电路包括:第一至第九pmos管、第一至第五nmos管;所述第一pmos管和第二pmos管的源极均连接电源,栅极均与所述第三pmos管的栅极连接;所述第一pmos管的漏极连接所述第三pmos管的源极,所述第二pmos管的漏极连接所述第三pmos管的漏极;所述第三pmos管的栅极连接所述第二预充电压;所述第一pmos管的漏极连接所述第四pmos管的漏极,所述第四pmos管的栅极连接所述位线输入控制电压,源极连接第一选择器的第一支路,所述第四pmos管的源极还通过第一缓冲器连接所述第一选择器的第二支路;所述第二pmos管的漏极连接所述第五pmos管的源极,所述第五pmos管的栅极连接所述位线输入控制电压,漏极连接第二选择器的第一支路,所述第五pmos管的漏极还通过第二缓冲器连接所述第二选择器的第二支路;所述第一选择器和第二选择器的输出端分别连接所述sram存储阵列的位线;所述第六pmos管和第七pmos管的源极均连接所述电源;所述第六pmos管的栅极连接所述第七pmos管的漏极,所述第七pmos管的栅极连接所述第六pmos管的漏极;所述第四pmos管的漏极还与所述第六pmos管的漏极连接;所述第五pmos管的源极还连接所述第七pmos管的漏极;所述第八pmos管的栅级和源极均连接所述第六pmos管的漏极,漏极接地;所述第九pmos管的栅级和源极均连接所述第七pmos管的漏极,漏极接地;所述第八pmos管的栅级与第九pmos管的栅级之间串联有由两个二极管反向并联构成限幅器;所述第六pmos管与第七pmos管的漏极作为输出,通过所述失调检测输入端与所述失调检测电路连接;所述第一nmos管与所述第二nmos管的漏极相连后连接所述第八pmos管的栅极,所述第三nmos管与所述第四nmos管的漏极相连后连接所述第pmos管的栅极,所述第一nmos管、第二nmos管、第三nmos管与第四nmos管的源极均连接所述第五nmos管的漏极;所述第一nmos管与第四nmos管的栅极作为输入,通过所述失调检测输出端连接所述失调检测电路;所述第二nmos管的栅极连接所述第四pmos管的源极,所述第三nnmos管的栅极连接所述第五pmos管的漏极;所述第五nmos管的源极接地,栅极连接所述第二使能电压。

10.本发明提供的灵敏放大器,在原来两条电流支路的基础上额外增加了两条失调补偿支路,灵敏放大电路内部节点的压差经失调检测电路进行放大后,将放大后的信号传输至补偿支路的栅端,从而减少或消除输入失调电压。本发明的灵敏放大器相对于补偿前的结构灵敏度更高;灵敏度指的是灵敏放大器在保证功能的情况下,能检测并放大的位线最小压差。由于输入失调电压的存在,灵敏放大器只有在压差大于输入失调电压后才能进行信号放大,否则会导致功能错误;通过补偿或消除输入失调电压,可以提高电路的灵敏度。本发明的灵敏放大器可提高sram中数据的读出速度;本领域熟知的静态随机存储器的数据读出时间,一般指的是从地址信号输入开始,到数据信号输出所经历的总延时。所以决定数据读出速度的延时主要包括字线选通前后两部分。选通前主要由译码电路决定,由于该部分的结构相对固定,所以优化空间有限。本发明通过提高灵敏放大器的灵敏度,可减少字线选通后数据经灵敏放大器放大输出的延时,从而可减少sram的读出时间;同时,在灵敏放大器中引入额外的下拉支路和锁存支路,使压差放大过程更快。本发明将补偿结构直接引入灵敏放大电路中,并不改变灵敏放大器的基本结构,与本领域中的存储结构兼容性较好。

附图说明

11.下面结合附图对本发明作进一步说明。

12.图1是本发明一个优选的实施例结构示意图。

13.图2图1中的失调检测电路结构示意图。

14.图3图1中的灵敏放大电路结构示意图。

具体实施方式实施例

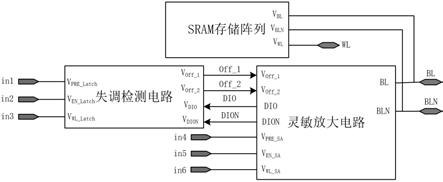

15.本实施例的灵敏放大器,如图1所示,包括:失调检测电路和灵敏放大电路;灵敏放大电路将sram存储阵列的位线v

bl

、v

bln

上的压差信号放大并进行输出;灵敏放大电路的bl、bln为双向的差分位线信号,既可以将来自于sram存储阵列的v

bl

、v

bln

位线上的压差进行放大,也可以将放大后的全摆幅信号进行输出。灵敏放大电路的输入端连接外部信号的in4、in5、in6,为灵敏放大电路提电预充电压v

pre_sa

、使能电压v

en_sa

、位线输入控制电压v

wl_sa

;失调检测电路的输入端连接外部信号的in1、in2、in3,为失调检测电路提供预充电压v

pre_latch

、使能电压v

en_latch

、输入信号控制电压v

wl_latch

;失调检测电路通过v

dio

、v

dion

端口接收灵敏放大电路的失调压差,也即灵敏放大电路内部节点dio和dion的信号,失调检测电路通过v

off_1

、v

off_2

输出检测放大后的位线信号,送至灵敏放大电路的失调补偿支路的控制端。

16.如图2所示,失调检测电路包括:第一至第七pmos管(图2中p1至p7)、第一至第三nmos管(图2中n1至n3);第一pmos管p1和第二pmos管p2的源极均连接电源,栅极均与第三pmos管p3的栅极连接;第一pmos管p1的漏极连接第三pmos管p3的源极,第二pmos管p2的漏极连接第三pmos管p3的漏极;第三pmos的栅极连接预充电压v

pre_latch

;第一pmos管p1和第二pmos管p2的漏极构成失调检测输出端,分别输出v

off_2

、v

off_1

;第四pmos管p4的源极与第五pmos管p5的漏极构成失调检测输入端v

dio

、v

dion

;第四pmos管p4与第五pmos管p5的栅极均连

接输入信号控制电压v

wl_latch

;第四pmos管p4的漏极连接第一pmos管p1的漏极;第五pmos管p5的源极连接第三pmos管p3的漏极;第六pmos管p6和第七pmos管p7的源极均连接电源;第六pmos管p6的栅极连接第七pmos管p7的漏极,第七pmos管p7的栅极连接第六pmos管p6的漏极;第四pmos管p4的漏极还与第六pmos管p6的漏极连接;第五pmos管p5的源极还连接第七pmos管p7的漏极;第一nmos管的栅极连接第五pmos管p5的漏极,漏极连接第六pmos管p6的漏极;第二nmos管的栅极连接第四pmos管p4的源极,漏极连接第七pmos管p7的漏极;第一nmos管与第二nmos管的源极均与第三nmos管的漏极连接;第一nmos管的漏极与第二nmos管的漏极之间串联有由两个二极管反向并联构成限幅器;第三nmos管的栅极连接使能电压v

en_latch

,源极接地。

17.失调检测电路的供电用的电流源由单级nmos管实现;通过增加一组共栅pmos管,可以将内部节点置位至供电电位;v

off_2

、v

off_1

两节点分别连接到pmos管的源漏端,用于预充电阶段平衡两节点的电位;差分对负载由交叉耦合的pmos管构成,且在v

off_2

、v

off_1

两节点间增加一级背靠背反相器型锁存器,用于加快输出节点高低电平的拉低和推高,且不增加电源和地之间的晶体管级数。

18.该失调检测电路分为预充和失调补偿两个工作阶段,其原理如下:在检测失调前需要对电路内部v

off_1

、v

off_2

节点进行预充,v

pre_latch

设置为低电平、v

wl_latch

为高电平、v

en_latch

设为低电平时,电源通过pmos开关将v

off_1

、v

off_2

节点拉高;然后v

pre_latch

设置为高电平、v

wl_latch

设置为低电平、v

en_latch

设为高电平,来自灵敏放大电路中dio、dion节点的信号v

dio

、v

dion

经过传输管传输到v

off_2

、v

off_1

。若灵敏放大器存在失调,经过交叉相连的锁存负载结构,v

off_2

、v

off_1

节点中电压较低的一端经电路下端的电流源被拉至地,另一端经锁存结构中的pmos被抬高至电源。v

off_2

、v

off_1

用于微调灵敏放大电路。为了提升失调检测的速度,在差分对管的驱动和负载之间的节点上,新引入一级锁存结构,在不降低输出电压余量的情况下,快速扩大两节点的压差。

19.如图3,灵敏放大电路包括:第一至第九pmos管(图3中p1至p9)、第一至第五nmos管(图3中n1至n5);第一pmos管p1和第二pmos管p2的源极均连接电源,栅极均与第三pmos管p3的栅极连接;第一pmos管p1的漏极连接第三pmos管p3的源极,第二pmos管p2的漏极连接第三pmos管p3的漏极;第三pmos管p3的栅极连接预充电压v

pre_sa

。

20.第一pmos管p1的漏极连接第四pmos管p4的漏极,第四pmos管p4的栅极连接位线输入控制电压v

wl_sa

,源极连接第一选择器u1的a0支路,第四pmos管p4的源极还通过第一缓冲器u3连接第一选择器u1的a1支路;第二pmos管p2的漏极连接第五pmos管p5的源极,第五pmos管p5的栅极连接位线输入控制电压v

wl_sa

,漏极连接第二选择器u2的a0支路,第五pmos管p5的漏极还通过第二缓冲器u4连接第二选择器u2的a1支路;第一选择器u1和第二选择器u2的即为bl于bln。第一选择器u1和第二选择器u2由信号v

tri_col

控制。

21.第六pmos管p6和第七pmos管p7的源极均连接电源;第六pmos管p6的栅极连接第七pmos管p7的漏极,第七pmos管p7的栅极连接第六pmos管p6的漏极。

22.第四pmos管p4的漏极还与第六pmos管p6的漏极连接;第五pmos管p5的源极还连接第七pmos管p7的漏极;第八pmos管p8的栅级和源极均连接第六pmos管p6的漏极,漏极接地;第九pmos管的栅级和源极均连接第七pmos管p7的漏极,漏极接地;第八pmos管p8的栅级与第九pmos管的栅级之间串联有由两个二极管反向并联构成限幅器;第六pmos管p6与第七

pmos管p7的漏极输出dio和dion的信号。

23.第一nmos管n1与第二nmos管n2的漏极相连而后连接第八pmos管p8的栅极,第三nmos管n3与第四nmos管n4的漏极相连而后连接第九pmos管p9的栅极,第一nmos管n1、第二nmos管n2、第三nmos管n3与第四nmos管n4的源极均连接第五nmos管n5的漏极;第一nmos管n1与第四nmos管n4的栅极作为输入分别连接v

off_1

、v

off_2

;第二nmos管n2的栅极连接第四pmos管p4的源极,第三nnmos管n3的栅极连接第五pmos管p5的漏极;第五nmos管n5的源极接地,栅极连接使能电压v

en_sa

。

24.该灵敏放大电路基本结构为双端输入,双端输出的全差分放大器:供电用的电流源由单级nmos管实现;每端输入由两部分组成,一部分来源于存储阵列信号,另一部分来源于失调检测电路中的补偿信号v

off_1

、v

off_2

,用来补偿输入失调电压;负载为交叉耦合的pmos管,结合dio节点的背靠背的反相器、二极管接法的pmos管,可对dio上的微小压差迅速反应,拉至低电平或者高电平。

25.工作过程包含预充电和放大两个工作阶段,其原理如下所述:在检测来自位线上的压差信号前,需要对电路内部dio、dion节点进行预充电,v

pre_sa

设置为低电平、v

wl_sa

为高电平、v

tri_col

为低电平、v

en_sa

为低电平时,电源通过pmos开关将dio、dion节点拉高;然后v

pre_sa

设置为高电平、v

wl_sa

设置为低电平、v

tri_col

保持为低电平、v

en_sa

设为高电平,来自位线上的bl、bln信号经过一级多路选择器和pmos开关传输到dio、dion。若灵敏放大器存在失调,即dio、dion节点上存在初始压差,v

off_2

或v

off_1

置为高电平,为锁存结构提供一条额外的电流支路,用于微调灵敏放大电路的失调。当dio和dion上存在一定的压差时,电压较低的一端被拉至地,另一端则被拉低至电源电位。通过在dio、dion节点位置增加一级并联的锁存结构,加快放大压差的同时,又不影响原灵敏放大器的输出电压余量;同样在这两个节点处增加两个二极管接法的pmos管,另一端接地,当dio或dion节点上的电压降至pmos的阈值时,pmos作为开关能将节点电压迅速拉低至零电位。

26.在位线和灵敏放大器输入输出节点之间增加一级选择器(mux),位线上的数据传入灵敏放大器时,选择a0端的支路;灵敏放大后的数据在读出时选择带有缓冲器(buffer)的支路a1:v

bl’或v

bln’中的一端被拉低至缓冲器中晶体管的阈值时,配合sa加快其降为干净的零电位,且起到隔离位线上寄生电容影响的作用。

27.此外,上述对各元件和方法的定义并不仅限于实施例中提到的各种具体结构、形状或方式,本领域普通技术人员可对其进行简单地更改或替换,例如:(1)失调检测电路不限于交叉耦合的锁存结构,也可采用本技术领域所熟知的电流镜型、strong arm型电压灵敏放大器结构。

28.(2)除上述原理陈述时的时序外,只要v

wl_sa

和v

en_sa

(v

wl_latch

和v

en_latch

)在v

pre_sa

(v

pre_latch

)信号预充结束后使能,本发明中的电路均能正常工作。

29.(3)本技术领域所熟知,失调检测电路和灵敏放大电路中的传输管电路,均可用传输门代替。

30.(4)灵敏放大电路中,除缓冲器外,也可采用本技术领域所熟知的其他隔离结构,一方面用于隔离位线电容,另一方面用于加快灵敏放大器对dio、dion节点中高低电平的放大。

31.本发明不局限于上述实施例。凡采用等同替换形成的技术方案,均落在本发明要

求的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。