1.本发明涉及计算存储一体化,特别是涉及一种存内计算单元、模块和系统。

背景技术:

2.计算存储一体化是近年来出现的新型计算技术,其目标为在内存中完成数据计算,避免或减少数据在内存和cpu之间的搬运,提高计算效率。尤其是随着人工智能(artificial intelligence,ai)的发展,数据量和计算量快速增加,传统的冯诺依曼计算机结构正受到越来越多的挑战。以卷积神经网络(convolution neural network,cnn)为例,每次乘运算之后,需要先将乘积存储起来,取出到cpu内相加,周而复始。数据在内存和cpu之间的不断存取占用大量能耗,效率很低。

3.为了进一步提高计算效率,人们提出了存内计算的思路,即在存储模块内部完成数据的计算,而无需再将数据搬运至cpu内进行运算。但是,现有的存内计算结构需要将各存储单元输出的饱和电流汇入同一个输出线路后,再将其转换为数字信号,以求得乘积和。由于不同存储单元输出的饱和电流不可能完全保持一致,必然存在一定的误差,因此在电流汇集的过程中,会存在累积误差不断增大的风险。当汇集的饱和电流个数越多,累积误差也越大。

技术实现要素:

4.基于此,有必要针对上述问题,提供一种存内计算单元、模块和系统。

5.一种存内计算单元,包括:存储阵列,包含多个呈n行n列排布的存储单元,位于第i行第j列的所述存储单元记为s

i,j

;位于同一列的所述存储单元中存储的数据值相同;所述存储阵列用于存储n比特的第一数据;其中,n大于等于1,i大于等于1且小于等于n,j大于等于1且小于等于n;n条字线,所述字线用于输入n比特的第二数据;位于同一行所述存储单元的控制端经由同一条所述字线依次串接;m个位线组,第k组位线记为位线组blk,m等于2n

‑

1,k大于等于1且小于等于m;其中,当k大于等于1且小于等于n时,第k组位线具有k条位线,k条位线分别连接至和存储单元s

1,k

及存储单元s

k,1

位于同一直线上的各存储单元的输出端;当k大于n且小于等于m时,第k组位线具有2n

‑

k条位线,2n

‑

k条位线分别连接至和存储单元s

k

‑

n 1,n

及存储单元s

n,k

‑

n 1

位于同一直线上的各存储单元的输出端。

6.上述存内计算单元,上述存内计算单元将第二数据通过字线直接作用于存储单元的控制端,将第一数据按照一定规则存储于阵列排布的存储单元,可以在一个时钟周期内完成n bit与n bit的二进制乘法运算。无需将存储数据搬运至cpu内进行运算,可以在存储模块中直接完成运算,减少了数据搬运,在运算量大的情况下,可以大幅提升运算速度,降低功耗。并且,每个存储单元的输出端均单独连接至一条独立的位线,与传统的技术方案相比,无需再将不同的存储单元输出的电流汇合到一根位线上,解决了电流汇合所导致的误差累积的问题。

7.在其中一个实施例中,所述存储单元包括非易失性存储器。

8.在其中一个实施例中,所述非易失性存储器包括nor闪存单元。

9.在其中一个实施例中,所述存储单元的控制端包括非易失性存储器的栅极;所述存储单元的输出端包括非易失性存储器的漏极。

10.在其中一个实施例中,所述第一数据为二进制数据,所述非易失性存储器用于存储比特值0或1;所述第二数据为二进制数据,当所述字线上的电压大于等于预设电压,则所述字线上的比特值为1;当所述字线上的电压小于预设电压,则所述字线上的比特值为0。

11.在其中一个实施例中,所述存内计算单元还包括m

‑

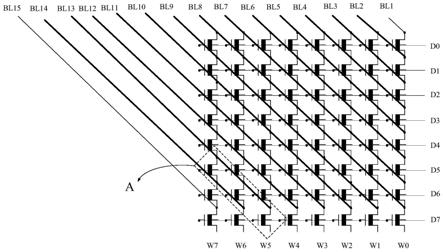

2个比特编码器,所述m

‑

2个比特编码器与第2个至第m

‑

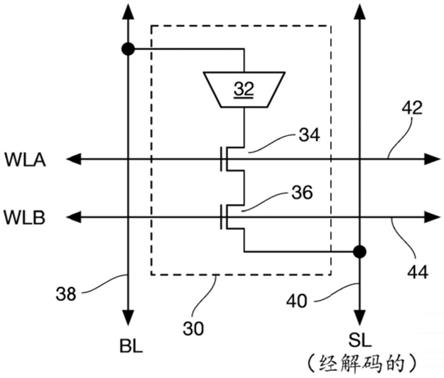

1个位线组一一对应连接,所述比特编码器用于将所述位线组的输出信号进行编码,以得到数字信号。

12.上述存内计算单元,将各个位线组连接到对应的比特编码器,把位线组中各位线上的电流电压信号进行编码,无需再采用模数转换模块对位线中的电流信号进行转换,不仅在时间上节省了模数转换的时间,也在面积上节省了模数转换模块的面积。虽然增加了位线的数量和比特编码器,但是从存内计算单元整体来看,面积还是得到了缩减,计算速度也得到了提升。

13.在其中一个实施例中,所述非易失性存储器包括:基底,所述基底包括衬底、衬底介质层及全耗尽沟道层;其中,所述基底内形成有阱区;所述衬底介质层位于所述衬底上,且覆盖所述阱区;所述全耗尽沟道层层位于所述衬底介质层上;栅极结构,位于所述全耗尽沟道层的上表面;源极,位于所述全耗尽沟道层的上表面,且位于所述栅极结构的一侧;漏极,位于所述全耗尽沟道层的上表面,且位于所述栅极结构远离所述源极的一侧;其中,所述源极和所述漏极通过外延工艺形成于所述全耗尽沟道层的上表面。

14.上述存内计算单元中,每个非易失性存储器采用具有全耗尽沟道层和和衬底介质层的半导体结构,可以减少漏电,使得存内计算单元可以应用于边缘计算的ai装置。此外,源极和漏极采用外延式工艺形成,可以提高饱和电流,加快读取速度,提升计算效能。

15.在其中一个实施例中,所述栅极结构包括:栅极叠层结构,位于所述全耗尽沟道层的上表面;所述栅极叠层结构包括由下至上依次叠置的隧穿介质层、浮栅、控制介质层和控制栅;栅极侧墙,位于所述栅极叠层结构相对的两侧。

16.一种存内计算模块,包括一个或多个上述实施例中所述的存内计算单元。

17.一种存内计算系统,包括一个或多个上述实施例中所述的存内计算模块。

18.上述存内计算模块和存内计算系统,无需借助于cpu进行数据运算,可以在存储阵列中直接完成数据运算,减少了数据搬移所消耗的时间和能耗,提高了运算效率;同时,采用比特编码器代替传统的模数转换模块或感应放大器,完全采用数字电路,节省了模拟信号转换为数字信号所消耗的时间,提高了数字信号的获取速度,也避免了模数转换过程中电流合并带来的误差累积的问题,同时还减小了整体结构的体积。

附图说明

19.图1为本技术一实施例中存内计算单元的结构示意图。

20.图2为图1的虚线框a中部分存内计算单元的结构放大示意图。

21.图3为两个8bit的二进制数据相乘的计算过程示意图。

22.图4为本技术另一实施例中存内计算单元的结构示意图。

23.图5为本技术一实施例中将存内计算单元的各位线组上的数字信号进行求和的示意图。

24.图6为本技术一实施例中非易失性存储器的截面结构示意图。

25.图7为本技术一实施例中输入数据矩阵与filter进行点积运算的示意图。

26.图8为图7所示运算过程的矩阵展开示意图。

27.图9为本技术一实施例中存内计算系统的计算过程示意图。

28.附图标号说明:1、基底;11、衬底;12、衬底介质层;13、全耗尽沟道层;21、隧穿介质层;22、浮栅;23、控制介质层;24、控制栅;25、栅极侧墙;3、源极;4、漏极。

具体实施方式

29.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的较佳的实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容的理解更加透彻全面。

30.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

31.在描述位置关系时,除非另有规定,否则当一元件例如层、膜或基板被指为在另一膜层“上”时,其能直接在其他膜层上或亦可存在中间膜层。进一步说,当层被指为在另一层“下”时,其可直接在下方,亦可存在一或多个中间层。亦可以理解的是,当层被指为在两层“之间”时,其可为两层之间的唯一层,或亦可存在一或多个中间层。

32.在使用本文中描述的“包括”、“具有”、和“包含”的情况下,除非使用了明确的限定用语,例如“仅”、“由

……

组成”等,否则还可以添加另一部件。除非相反地提及,否则单数形式的术语可以包括复数形式,并不能理解为其数量为一个。

33.随着计算机的发展,计算机的计算能力得到不断提升,但是也逐渐遇到了瓶颈。较为明显的是在人工智能(artificial intelligence,ai)领域,计算量急剧增加,依靠传统的冯诺依曼结构已经很难再进一步,提高计算速度。因此,很多科学界和公司开始了针对传统计算机结构的改进。其中一种思路是模仿人脑,将计算功能和存储功能都在存储单元内完成,而无需将存储单元内的数据搬运至cpu内进行计算,然后再将计算结果搬运至存储单元。

34.如图1所示,本技术的一个实施例提供了一种存内计算单元,包括:存储阵列,包含多个呈n行n列排布的存储单元,位于第i行第j列的所述存储单元记为s

i,j

;位于同一列的所述存储单元中存储的数据值相同;所述存储阵列用于存储n比特的第一数据;其中,n大于等于1,i大于等于1且小于等于n,j大于等于1且小于等于n;n条字线,所述字线用于输入n比特的第二数据;位于同一行所述存储单元的控制端经由同一条所述字线依次串接;m个位线组,m等于2n

‑

1,第k组位线记为位线bl

k

,k大于等于1且小于等于m;其中,当k大于等于1且小于等于n时,第k组位线具有k条位线,k条位线分别连接至和存储单元s

1,k

及存储单元s

k,1

位于同一直线上的各存储单元的输出端;当k大于n且小于等于m时,第k组位线具有2n

‑

k条位

线,2n

‑

k条位线分别连接至和存储单元s

k

‑

n 1,n

及存储单元s

n,k

‑

n 1

位于同一直线上的各存储单元的输出端。

35.作为示例,对于存储阵列中行的排列,可以按照从上到下的方向,将存储阵列最上面的一行作为第一行,最下面的一行作为第n行。对于存储阵列中列的排列,可以按照从右到左的方向,将存储阵列最右侧的一列作为第一列,最左侧的一列作为第n列。在其他实施例中,排和列还可以按照其他定义方式进行设置,本技术对此不做强制性的限制。其中,n可以是任意正整数,例如3、5、8或10,在本实施例中,以n为8进行示例说明。

36.在图1中,n为8,存储阵列右上角的存储单元记为存储单元s

1,1

,左下角的存储单元为存储单元s

8,8

。存储阵列中每一列的存储单元存储有相同的比特值,作为示例,第一列存储单元中均存储有数据w0,第二列存储单元中均存储有数据w1,

……

,第8列存储单元中均存储有数据w7。因此,存储阵列中存储的第一数据为w=[w7,w6,w5,w4,w3,w2,w1,w0]。每条字线输入一个bit的数值,作为示例,第一行存储单元的控制端均与第一字线相连接,第一字线携带的输入数据为d0,第二行存储单元的控制端均与第二字线相连接,第二字线携带的输入数据为d1,

……

,第八行存储单元的控制端均与第八字线相连接,第八字线携带的输入数据为d7。8条字线向存储阵列输入的第二数据为d=[d7,d6,d5,d4,d3,d2,d1,d0]。

[0037]

作为示例,当字线上的电压大于等于预设电压,则字线上的比特值为1;当字线上的电压小于预设电压,则字线上的比特值为0。例如,当第一字线上的电压大于等于预设电压时,d0为1;当第一字线上的电压小于预设电压时,d0为0。预设电压可以是存储单元的阈值电压。

[0038]

位线的连接关系分为两部分进行描述,第一部分,当k大于等于1且小于等于8时,与存储单元s

1,k

及存储单元s

k,1

位于同一直线上的各存储单元的输出端与位线组bl

k

中的k条位线一一对应连接。例如,当k等于1时,位线组bl1仅有一条位线,与存储单元s

1,1

的输出端相连接;当k等于2时,位线组bl2有两条位线,分别与存储单元s

2,1

和存储单元s

1,2

的输出端相连接;当k等于3时,位线组bl3有三条位线,分别与存储单元s

3,1

、存储单元s

2,2

及存储单元s

1,3

的输出端相连接。第二部分,当k大于8且小于等于15时,与存储单元s

k

‑

8 1,8

及存储单元s

8,k

‑

8 1

位于同一直线上的各存储单元的输出端与位线组bl

k

中的2n

‑

k条位线一一对应连接。例如,当k等于15时,位线组bl

15

仅有一条位线,与存储单元s

8,8

的输出端相连接;当k等于14时,位线组bl

14

有两条位线,分别与存储单元s

7,8

和存储单元s

8,7

的输出端相连接;当k等于13时,位线组bl

13

有三条位线,分别与存储单元s

6,8

、存储单元s

7,7

及存储单元s

8,6

的输出端相连接。位线组bl

13与

存储单元s

6,8

、存储单元s

7,7

及存储单元s

8,6

的输出端相连接的结构放大示意图如图2所示。

[0039]

上述存内计算单元可以用于完成两个8bit数据的二进制乘法运算。其中,输入数据为第二数据d=[d7,d6,d5,d4,d3,d2,d1,d0],存储数据为第一数据w=[w7,w6,w5,w4,w3,w2,w1,w0]。数据d和数据w二进制乘法计算过程如图3所示。两个8bit的数据进行二进制乘法,最终得到一个15bit的乘积p=[p

14

,p

13

,p

12

,p

11

,p

10

,p9,p8,p7,p6,p5,p4,p3,p2,p1,p0]。乘积p中的各位数据对应于图1中的15个位线组[bl

15

,bl

14

,bl

13

,bl

12

,bl

11

,bl

10

,bl9,bl8,bl7,bl6,bl5,bl4,bl3,bl2,bl1]。在本实施例中,d与w的最大值为255,p的最大值为65025。

[0040]

其中,单个存储单元的计算逻辑如下:

[0041]

当一存储单元中存储有数据1,且与该存储单元的栅极相连的字线上的数据也是

1,则该存储单元被导通,产生一个饱和电流。该饱和电流代表乘积结果为1,即1

×

1=1。

[0042]

当一存储单元中存储有数据0,且与该存储单元的栅极相连的字线上的数据是1,则该存储单元未被导通,无法产生饱和电流。则乘积结果为0,即0

×

1=0。

[0043]

当一存储单元中存储有数据1,且与该存储单元的栅极相连的字线上的数据是0,则该存储单元未被导通,无法产生饱和电流。则乘积结果为0,即1

×

0=0。

[0044]

基于上述运算逻辑,当采用上述存内计算单元对二进制数据w和二进制数据d进行二进制乘法运算时,每个位线组中具有饱和电流的位线的条数,即为该位线组可以输出的数字信号的值。

[0045]

上述存内计算单元,上述存内计算单元将第二数据通过字线直接作用于存储单元的控制端,将第一数据按照一定规则存储于阵列排布的存储单元,可以在一个时钟周期内完成n bit与n bit的二进制乘法运算。无需将存储数据搬运至cpu内进行运算,可以在存储模块中直接完成运算,减少了数据搬运,在运算量大的情况下,可以大幅提升运算速度,降低功耗。并且,每个存储单元的输出端均单独连接至一条独立的位线,与传统的技术方案相比,无需再将不同的存储单元输出的电流汇合到一根位线上,解决了电流汇合所导致的误差累积的问题。

[0046]

在一个实施例中,存储单元可以是非易失性存储器,非易失性存储器可以在不连接外部电源的情况下保存数据。作为示例,存储单元的控制端可以是非易失性存储器的栅极,存储单元的输出端可以是非易失性存储器的漏极。可选地,阵列中的存储单元还可以是电荷储存存储单元,例如浮动栅单元或介电电荷捕捉单元,具有耦接到对应位线的漏极,以及耦接到地的源极。在其他实施例中可以使用其他类型的存储单元,包括但不限于许多类型的可编程电阻性存储单元,例如基于相变化存储单元、基于磁阻的存储单元、基于金属氧化物的存储单元或其它单元。

[0047]

在一个实施例中,存储单元可以是nor闪存单元。例如体硅工艺的浮栅nor闪存单元,全耗尽绝缘体上硅(full

‑

depletion silicon on insulator,fdsoi)工艺的浮栅nor闪存单元。其中,nor闪存单元的栅极与字线连接,漏极与位线连接,源极和背极可以接地。

[0048]

在一个实施例中,存内计算单元还包括m

‑

2个比特编码器,所述m

‑

2个比特编码器与第2个至第m

‑

1个位线组一一对应连接,所述比特编码器用于将所述位线组的输出信号进行编码,以得到数字信号。

[0049]

作为示例,如图4所示,存内计算单元包括13个比特编码器,分别与位线组bl2至位线组bl

14

一一对应连接。当一存储单元导通后,通过与之相连的位线输出饱和电流,与此同时,该位线上的电压从低电平变为高电平。在本实施例中,位线组bl2有两条位线,连接于2to2比特编码器和两个存储单元之间。位线组bl2最多可向比特编码器发送2个高电平信号,2to2比特编码器可将两个高电平信号编码为bcd码10。位线组bl3有三条位线,连接于3to2比特编码器和三个存储单元之间。位线组bl3最多可向比特编码器发送3个高电平信号,3to2比特编码器可将三个高电平信号编码为bcd码11。位线组bl4最多可向比特编码器发送4个高电平信号,4to3比特编码器可将四个高电平信号编码为bcd码100。综上可知,比特编码器可以将与其相连的位线中传达的高电平信号编码为bcd码。对于位线组bl1和位线组bl

15

,由于各自仅有一条位线,所能传达的数字信号为0(低电平)或1(高电平),无需使用比特编码器进行编码。

[0050]

上述实施例通过比特编码器将各个位线组中的位线信号转化为数字信号,无需再将多个饱和电流输入同一位线,解决了电流汇合所导致的误差累积的问题。并且,本实施例中巧妙地利用比特编码器将每个位线组中的位线信号编码为数字信号,全部采用数字电路和组合逻辑电路,可以在一个周期内完成n bit的二进制乘法运算,与传统的方案相比,无需使用占用面积较大的模数转换电路或感应放大电路,在提高计算速度的同时,减小了存内计算单元的面积。

[0051]

比特编码器输出数字信号后,对各数字信号进行移位相加,即可得到最终的乘积和,如图5所示。作为示例,可以使用加法器对各数字信号进行加法运算。

[0052]

在一个实施例中,如图6所示,非易失性存储器包括:基底,所述基底包括衬底、衬底介质层及全耗尽沟道层;其中,所述基底内形成有阱区;所述衬底介质层位于所述衬底上,且覆盖所述阱区;所述全耗尽沟道层层位于所述衬底介质层上;栅极结构,位于所述全耗尽沟道层的上表面;源极,位于所述全耗尽沟道层的上表面,且位于所述栅极结构的一侧;漏极,位于所述全耗尽沟道层的上表面,且位于所述栅极结构远离所述源极的一侧;其中,所述源极和所述漏极通过外延工艺形成于所述全耗尽沟道层的上表面。

[0053]

通过在衬底11和全耗尽沟道层13之间设置衬底介质层12,可以使得源极3和漏极4之间的电子通道仅限于全耗尽沟道层13内,避免了源极3和漏极4之间通过阱区进行电子转移,从而大幅降低了漏电流。全耗尽沟道层13与衬底介质层12相结合,在半导体结构导通的情况下,将饱和电流的通道限制在全耗尽沟道层13中,极大地提高了半导体结构的一致性,降低了不同半导体结构之间的变异性。此外,源极3和漏极4可以通过外延工艺形成于全耗尽沟道层13的上表面,以得到外延式源极和外延式漏极,可以在晶体管导通时极大地提高沟道中的饱和电流,提高晶体管的开关速度。

[0054]

在一个实施例中,请继续参考图6,栅极结构包括:栅极叠层结构,位于全耗尽沟道层13的上表面;栅极叠层结构包括由下至上依次叠置的隧穿介质层21、浮栅22、控制介质层23和控制栅24;栅极侧墙25,位于栅极叠层结构相对的两侧。作为示例,图6中所示非易失性存储器可以是fdsoi工艺下的浮栅nor闪存单元。

[0055]

在一个实施例中,本技术还公开了一种存内计算模块,该存内计算模块包括一个或多个上述实施例中的存内计算单元。

[0056]

每个存内计算单元都可以完成一个n bit

×

n bit的二进制运算,因此,每个存内计算模块可以同时完成一个或多个n bit

×

n bit的二进制运算。上述存内计算模块可以作为卷积神经网络计算中用于产生特征图(feature map)的过滤器(filter),即预先在存内计算模块中写入存储值,作为filter中各个元素的值。以影像识别的cnn架构为例,在第一层的特征图(feature map)计算中,输入数据矩阵(input)中的每个数据可以代表影像的黑白像素,每个像素的值具有l个bit,l可以是任意正整数,例如5、8、12或16。在本实施中,l为8,输入数据矩阵为5

×

5的矩阵。filter也是5

×

5的矩阵,filter中每个元素也为8bit的二进制数。

[0057]

filter与输入数据矩阵进行点积运算的示意图如图7所示。其中,w

ij

是filter的值,d

ij

为输入值,i=0,1,2,3,4,j=0,1,2,3,4,5。根据前述内容可以知晓,对于每个d

ij

*w

ij

的计算,均需要一个存内计算单元来执行计算。例如,d

00

*w

00

、d

01

*w

01

、d

02

*w

02

、d

03

*w

03

、d

04

*w

04

均为8bit

×

8bit的数据相乘,其中,

[0058]

d

00

=[d

00

[0],d

00

[1],d

00

[2],d

00

[3],d

00

[4],d

00

[5],d

00

[6],d

00

[7]]

[0059]

w

00

=[w

00

[0],w

00

[1],w

00

[2],w

00

[3],w

00

[4],w

00

[5],w

00

[6],w

00

[7]]

[0060]

对于d

00

*w

00

,可以先将w

00

写入第一存储阵列,将d

00

通过输入线路输入第一存储阵列,在一个时钟周期内即可完成d

00

*w

00

的数据计算。总共需要进行25次8bit

×

8bit的数据计算,即d

00

*w

00

、d

01

*w

01

、d

02

*w

02

、d

03

*w

03

、

……

d

43

*w

43

、d

44

*w

44

,因此,可以布置25个存内计算单元同时运算,每个存内计算单元完成一个8bit

×

8bit的数据计算,即可在一个时钟周期内完成一次点积运算。

[0061]

为了便于理解,可将图7中的式子以向量和矩阵的形式展开,如图8所示。其中,左侧的列矩阵代表从字线上向存内计算单元输入的数据d

00

至d

44

,该列矩阵具有200行,1列。其中,每8行代表一个8bit的输入数据。例如,d

00

[0]至d

00

[7]代表数据d

00

。

[0062]

图8右侧的数据矩阵可以代表存储阵列w

00

至w

44

,该数据矩阵具有200行,8列。其中,每8行代表一个8bit的存储数据。8bit的二进制数据w

00

至w

44

从上到下依次排布。作为示例,前8行代表存储数据w

00

。具体地,前8行中,每一列元素的数值相同,例如,前8行中的第一列元素均为w

00

[7],第二列元素均为w

00

[6],

……

,第七列元素均为w

00

[0]。

[0063]

存内计算模块具有25个存内计算单元,可以在一个时钟周期内完成一次点积运算。

[0064]

本技术的一个实施例还公开了一种存内计算系统,包括一个或多个上述实施例中所述的存内计算模块。

[0065]

如果以一个存内计算模块作为一个filter,那么上述存内计算系统包括一个或多个filter。对于cnn网络架构而言,每一层的feature map计算过程中,可能存在多个filter。以k个filter为例,上述存内计算系统包括k个存内计算模块。

[0066]

作为示例,每个filter为n

×

n的矩形数据阵列。每个数据为l bit的二进制数据,总共有k个filter。则完成cnn网络架构中一层feature map的计算过程示意图如图9所示。

[0067]

以n为5、k为32、l为8为例进行说明,在一个时钟周期内,图9的结构可以执行5

×5×

32=800个8比特数据的乘法,以及几乎等量的加法,因此,本实施例中的存内计算系统一个时钟周期的算力是1600operations(ops)。由于信号经过nor单元、比特编码器与加法器时耗费的时间都极短,所以上述存内计算系统结构可以达到ghz的等级。也就是说,在此面积大约为51200(即:800

×

64)个nor单元的大小的芯片上,就可以提供1.6tops(tera operations)的算力,属于非常先进的结构。

[0068]

上述存内计算单元完全由数字电路实现,与传统的存内计算方案相比,虽然在位线布局上,需要为每个存储单元布置独立的位线,并连接到编码器上,会在一定程度上增加存储阵列的面积,但是,从整体存内计算单元的角度来看,省去了面积较大的模数信号转换模块或者感应放大器,同时也省去了模数转换的时间。因此,本技术中的存内计算单元减小了面积,提升了速度,也降低了功耗。由上述存内计算单元组成的存内计算模块或存内计算系统,无需频繁地数据搬运,并且在数据处理速度上也大幅度提升,功耗大幅降低,可以在边缘装置上实现边缘计算。

[0069]

以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0070]

以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。