1.本发明涉及半导体技术领域,更具体地,涉及一种半导体结构及其形成方法。

背景技术:

2.基板(例如扇出基板fosub)设计主要是要减少扇出层和基板的层数。在一种情况下,会例如因为串行器解串器(serdes)等的电性需求,在扇出重布线层(rdl)设计时,需要厚度较厚的rdl。具体的是需要rdl的较厚金属层(metal layer),这是因为薄金属层会造成讯号损耗。若是不增加金属层的厚度,则可以需要增加金属层的宽度,但是这样则会增加rdl的层数。另一方面,目前形成细线路结构的制程都是使用的薄膜光阻,再叠加光阻和电镀的偏差,则细线路厚度只能控制在2

‑

3微米,rdl无法满足设计需求的6

‑

7微米的较厚厚度。若要增加rdl的厚度则必须扩宽细线路的线宽和线距,也就是说,若是使用可以达到厚度的光阻则线路无法满足设计的细线路。

技术实现要素:

3.针对相关技术中的上述问题,本发明提出一种半导体结构及其形成方法。

4.根据本发明的实施例的一个方面,提供了一种半导体结构,包括:第一线路层;第二线路层,位于第一线路层上方,第二线路层包括第一导电线路和覆盖在第一导电线路上的第一介电层,其中,第一导电线路延伸至第一介电层内并且第一导电线路的顶面位于第一介电层的顶面下方。

5.在一些实施例中,第一导电线路的深宽比大于1。

6.在一些实施例中,第一导电线路的线宽小于5微米,并且第一导电线路之间的间隔小于5微米。

7.在一些实施例中,在从第一线路层到第一介电层的顶面的方向上,第一导电线路的至少在第一介电层内的部分的宽度逐渐缩小。

8.在一些实施例中,半导体结构还包括串行器解串器,位于第二线路层上方并与第二线路层电连接。

9.在一些实施例中,第二线路层还包括穿过第一介电层的第二导电线路。

10.在一些实施例中,第二线路层还包括位于第一介电层下方的第二介电层和内埋于第二介电层的另外有第一导电线路,其中,另外的第一导电线路的顶面位于第二介电层的顶面下方。

11.在一些实施例中,第二线路层还包括连接通孔,连接通孔连接在第一导电线路上,并且在从第一线路层到第一介电层的顶面的方向上,连接通孔的宽度逐渐增大。

12.根据本发明的实施例的另一个方面,还提供了一种形成半导体结构的方法,包括:在载体上提供第一介电层;在第一介电层中形成第一线路沟槽,第一线路沟槽的底面高于第一介电层的底面;在第一线路沟槽内填充导电材料以形成位于第一介电层中的第一线路。

13.在一些实施例中,形成第一线路沟槽包括:利用灰阶光掩模在第一介电层中形成第一线路沟槽和第二线路沟槽,第二线路沟槽的深度大于第一线路沟槽的深度。

14.在一些实施例中,第二线路沟槽穿过第一介电层。

15.在一些实施例中,形成半导体结构的方法还包括:当用导电材料填充第一线路沟槽时,掩盖第二线路沟槽。

16.在一些实施例中,形成半导体结构的方法还包括:形成位于线路层上方并与线路层电连接的串行器解串器。

17.在一些实施例中,形成半导体结构的方法还包括:将第一介电层附接至基板并去除载体;在第一介电层的与基板相对的表面上形成到达第一线路的连接通孔开孔;在连接通孔开孔内填充导电材料以形成连接通孔。

18.在一些实施例中,第一线路的线宽小于5微米,并且第一线路之间的间隔小于5微米。

19.在一些实施例中,形成半导体结构的方法还包括:形成位于线路层上方并与线路层电连接的串行器解串器。

20.在一些实施例中,形成半导体结构的方法还包括:在第一介电层上方形成第二介电层,在第二介电层中形成另外的第一线路沟槽,另外的第一线路沟槽的底面高于第二介电层的底面;在第二线路沟槽内填充导电材料以形成位于第二介电层中的另外的第一线路。

21.在一些实施例中,第一线路沟槽的深宽比大于1。

22.在一些实施例中,第一线路的线宽小于5微米,并且第一线路之间的间隔小于5微米。

23.在一些实施例中,在从载体到第一介电层的顶面的方向上,第一线路沟槽的宽度逐渐增加。

附图说明

24.当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各个方面。应当注意,根据工业中的标准实践,各个部件并非按比例绘制。事实上,为了清楚讨论,各个部件的尺寸可以任意增大或减小。

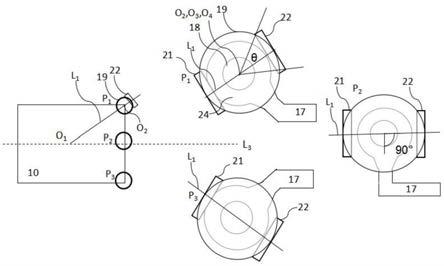

25.图1是根据本发明实施例的半导体结构的示意图。

26.图2a至图2g是根据本发明实施例的形成半导体结构的方法的各个阶段的示意图。

具体实施例

27.下列公开提供了许多用于实现所提供主题的不同特征的不同实施例或实例。下面将描述元件和布置的特定实例以简化本发明。当然这些仅仅是实例并不旨在限定本发明。例如,在以下描述中,在第二部件上方或上形成第一部件可以包括第一部件和第二部件直接接触的实施例,也可以包括在第一部件和第二部件之间形成额外的部件使得第一部件和第二部件可以不直接接触的实施例。而且,本发明在各个实例中可重复参考数字和/或字母。这种重复仅是为了简明和清楚,其自身并不表示所论述的各个实施例和/或配置之间的关系。

28.图1是根据本发明实施例的半导体结构的示意图。如图1所示,半导体结构可以包括第一线路层110和位于第一线路层110上方的第二线路层120。其中,第二线路层120包括第一导电线路125和覆盖在第一导电线路125的第一介电层121。第一导电线路125延伸至第一介电层121内并且第一导电线路125的顶面位于第一介电层121的顶面下方。并且,第一导电线路125的顶面与第一介电层121的顶面之间具有一距离。在一些实施例中,第一线路层10可以是基板。在一些实施例中,第二线路层120可以是重布线(rdl)层。

29.在一些实施例中,可以利用灰阶光罩在第一介电层121中开设用于容纳第一导电线路125的沟槽,再由金属材料通过例如电镀制程填满沟槽。通过利用灰阶光罩会使得介电层曝光不到底的特性,可制造出内埋于第一介电层121的第一导电线路125,如此一来就可以透过第一介电层121的厚度来增加第二线路层120(例如rdl层)整体的厚度,这样会形成具有较厚厚度且线宽线距满足细线路要求的细线路而不牺牲电特性。提高了制程良率,制程良率可以达到大于99.5%。另一方面,因为内埋第一导电线路125的设计,与现行技术相比可以减少第二线路层120的层数,使得本发明的半导体结构厚度更薄。

30.在一些实施例中,第一导电线路125的深宽比大于1。第一导电线路125的线宽小于5微米,并且第一导电线路125之间的间隔(即,线距)小于5微米。在一些实施例中,第一导电线路125的线宽小于2微米,并且第一导电线路125之间的间隔小于2微米。也就是说,第一导电线路125的线宽线距可以满足细线路要求。

31.在一些实施例中,半导体结构还可以包括串行器解串器(serdes)(未示出),serdes位于第二线路层120上方并与第二线路层120电连接。本发明透过内埋rdl可以达成serdes电性设计需求,例如需要厚度较厚的rdl。

32.继续参考图1所示,在从第一线路层110到第一介电层121的顶面的方向上,第一导电线路125的至少在第一介电层121内的部分的宽度逐渐缩小。第二线路层120中还可以包括第二导电线路126,第二导电线路126穿过第一介电层121。此外,第二线路层120还可以包括连接通孔129,连接通孔129连接在第一导电线路125上。连接通孔129连通到第一介电层121的顶面。在从第一线路层110到第一介电层121的顶面的方向上,连接通孔129的宽度逐渐增大。也就是说,连接通孔129的轮廓与第一导电线路125的轮廓相反。

33.第二线路层120还可以包括位于第一介电层121下方的第二介电层122和内埋于第二介电层122的另外的第一导电线路125,与第一导电线路125类似的,另外的第一导电线路125的顶面位于第二介电层122的顶面下方,并且另外的第一导电线路125的顶面与第二介电层122的顶面之间具有一距离。在一些实施例中,内埋的第一导电线路125与下一层内的另外的第一导电线路125之间的距离可以在2微米至3微米的范围内。

34.在示处的实施例中,第二介电层122下方还设置有第三介电层123和位于第三介电层123中的另外的第一导电线路125和第二导电线路126。第三介电层123中的另外的第一导电线路125和第二导电线路126可以与第二介电层122中的另外的第一导电线路125和第二导电线路126类似,在此不再重复说明。第二线路层120可以通过粘着层190与第一线路层110附接。

35.根据本发明的实施例还提供了一种形成半导体结构的方法。图2a至图2g是根据本发明实施例的形成半导体结构的方法的各个阶段的示意图。

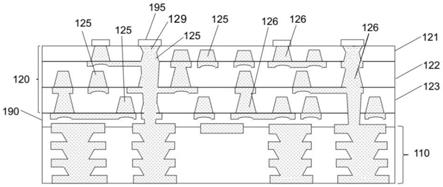

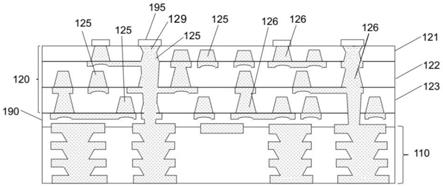

36.首先,如图2a所示,提供载体201,并在载体201上提供第一介电层121。然后,利用

灰阶光罩在第一介电层121中形成第一线路沟槽221。利用灰阶光罩形成的第一线路沟槽221未穿透第一介电层121,因此第一线路沟槽221的底面高于第一介电层121的底面。在此步骤中,还可以同时形成第二线路沟槽222,第二线路沟槽222的深度大于第一线路沟槽221的深度。第二线路沟槽222可以穿过第一介电层121。

37.然后,如图2b所示,利用掩模230遮盖第二线路沟槽222,并用导电材料填充第一线路沟槽221以形成第一导电线路125(也可称为第一线路)。如图2c所示,去除掩模230而暴露出第二线路沟槽222,并在第二线路沟槽222中填充导电材料以形成第二导电线路126(也可称为第二线路)。在形成第一导电线路125和第二导电线路126之后,由于第一介电层上方的线路厚度不足而在第一导电线路125和第二导电线路126的顶面上产生凹坑。在一些实施例中,凹坑的深度可以在1微米至3微米的范围内。

38.如上,通过利用灰阶光罩会使得第一介电层121曝光不到底,因此可制造出内埋于第一介电层121的第一导电线路125,如此一来就可以透过第一介电层121的厚度来增加第二线路层120(例如rdl层)整体的厚度,这样会形成具有较厚厚度且线宽线距满足细线路要求的细线路而不牺牲电特性。因为内埋第一导电线路125的设计,与现行技术相比可以减少第二线路层120的层数,又可以使得本发明的半导体结构厚度更薄。

39.如图2d所示,在第一介电层121上方形成第二介电层122,利用灰阶光罩在第二介电层122中形成另外的第一线路沟槽221,另外的第一线路沟槽221的底面高于第二介电层122的底面,即,另外的第一线路沟槽221未穿过第二介电层122。另外,还在第二介电层122中形成穿过第二介电层122的另外的第二线路沟槽222。并且,在另外的第一导电线路125沟槽和第二线路沟槽222内填充导电材料以形成位于第二介电层122中的另外的第一导电线路125和第二导电线路126。

40.如图2e所示,可以在第二介电层122上方形成第三介电层123。并且与图2d类似的,在第三介电层123中形成另外的第一导电线路125和第二导电线路126。第一介电层121、第二介电层122和第三介电层123及其中的第一导电线路125和第二导电线路126共同称为第二线路层120。在其他实施例中,第二线路层120也可以包括任何适当数量的层。

41.如图2f所示,例如通过粘着层190将第二线路层120与第一线路层110附接,并去除载体201。然后,如图2g所示,在第一介电层121的与第一线路层110相对的表面上形成到达第一导电线路125的连接通孔开孔。在连接通孔开孔内填充导电材料以形成连接通孔129。如上,连接通孔与第一导电线路125的轮廓相反。

42.随后,在连接通孔和穿过第一介电层121的第二导电线路126形成ubm(凸块下金属)195而得到图1所示的半导体结构。在一些未示出的实施例中,还可以形成位于第二线路层120上方并与第二线路层120中的线路电连接的serdes。

43.上述内容概括了几个实施例的特征使得本领域技术人员可更好地理解本公开的各个方面。本领域技术人员应该理解,可以很容易地使用本发明作为基础来设计或更改其他的处理和结构以用于达到与本发明所介绍实施例相同的目的和/或实现相同优点。本领域技术人员也应该意识到,这些等效结构并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,可以进行多种变化、替换以及改变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。