1.本发明涉及半导体发光元件及半导体发光元件的制造方法。

背景技术:

2.半导体发光元件具有在基板上层叠的n型半导体层、活性层及p型半导体层,在n型半导体层上设有n侧电极,在p型半导体层上设有p侧电极。在使用gan、algan等氮化物半导体的发光元件中,有时使用由ti和al的层叠体构成的n侧电极(例如,参照专利文献1)。

3.[在先技术文献]

[0004]

[专利文献]

[0005]

专利文献1:日本特开2019

‑

192908号公报

技术实现要素:

[0006]

[发明要解决的课题]

[0007]

通过采用在n侧电极中不使用au的构造,能够提高n侧电极的紫外光反射率。但是,在使用al形成n侧电极的情况下,由于n侧电极中不含有用于保护电极的au,因此随着通电使用,al的腐蚀进展,导致紫外光反射率的降低。

[0008]

本公开鉴于这样的课题而完成,其目的在于提供一种抑制因半导体发光元件的通电使用而导致的光输出的降低的技术。

[0009]

[用于解决技术课题的技术方案]

[0010]

本发明的一种方案的半导体发光元件包括:由n型algan系半导体材料构成的n型半导体层;设于n型半导体层的第1上表面,由algan系半导体材料构成的活性层;设于活性层上的p型半导体层;与p型半导体层的上表面接触设置的p侧接触电极;在p侧接触电极上设于比p侧接触电极的形成区域窄的区域内的p侧电流扩散层;设于p侧电流扩散层上的p侧焊盘电极;与n型半导体层的第2上表面接触设置的n侧接触电极;在n侧接触电极上遍及比n侧接触电极的形成区域大的区域而设置,包含tin层的n侧电流扩散层;以及设于n侧电流扩散层上的n侧焊盘电极。

[0011]

根据本方案,通过在p侧接触电极上、在比p侧接触电极窄的区域内设置p侧电流扩散层,能够使p侧接触电极在p型半导体层的上表面所占的面积最大化,能够使发光层中有助于发光的发光面积最大化。另外,通过在n侧接触电极上遍及比n侧接触电极的形成区域大的区域而设置包含tin层的n侧电流扩散层,能够抑制因通电使用而导致的n侧接触电极的腐蚀。由此,抑制作为反射电极发挥功能的n侧接触电极的反射率降低,能够抑制因通电使用而导致的光输出的降低。

[0012]

p侧电流扩散层及n侧电流扩散层也可以分别具有依次层叠tin层、金属层及tin层的层叠构造。

[0013]

n侧电流扩散层也可以包含设于n侧接触电极上的第1电流扩散层和设于第1电流扩散层上的第2电流扩散层。第1电流扩散层及第2电流扩散层也可以分别具有依次层叠tin

层、金属层及tin层的层叠构造。

[0014]

第1电流扩散层也可以遍及比n侧接触电极的形成区域大的区域而设置。

[0015]

第2电流扩散层也可以遍及比第1电流扩散层的形成区域大的区域而设置。

[0016]

层叠构造的金属层的厚度也可以大于层叠构造的tin层的厚度。

[0017]

本发明的另一方案是半导体发光元件的制造方法。该方法包括:在由n型algan系半导体材料构成的n型半导体层上形成由algan系半导体材料构成的活性层的工序;在活性层上形成p型半导体层的工序;部分地除去p型半导体层及活性层,以使n型半导体层的局部区域的上表面露出的工序;形成与p型半导体层的上表面接触的p侧接触电极的工序;在p侧接触电极上、在比p侧接触电极的形成区域窄的区域内形成p侧电流扩散层的工序;形成与n型半导体层的露出的上表面接触的n侧接触电极的工序;在n侧接触电极上、遍及比n侧接触电极的形成区域大的区域而形成包含tin层的n侧电流扩散层的工序;在p侧电流扩散层上形成p侧焊盘电极的工序;以及在n侧电流扩散层上形成n侧焊盘电极的工序。

[0018]

根据本方案,通过在p侧接触电极上、在比p侧接触电极窄的区域内设置p侧电流扩散层,能够使p侧接触电极在p型半导体层的上表面所占的面积最大化,能够使发光层中有助于发光的发光面积最大化。另外,通过在n侧接触电极上、遍及比n侧接触电极的形成区域大的区域而设置包含tin层的n侧电流扩散层,能够抑制因通电使用而导致的n侧接触电极的腐蚀。由此,抑制作为反射电极发挥功能的n侧接触电极的反射率降低,能够抑制因通电使用而导致的光输出的降低。

[0019]

也可以还包括对n侧接触电极进行退火的工序。n侧电流扩散层也可以在n侧接触电极的退火后形成。

[0020]

[发明效果]

[0021]

根据本发明,能够抑制因半导体发光元件的通电使用而导致的光输出的降低。

附图说明

[0022]

图1是概略地表示第1实施方式的半导体发光元件的构成的剖视图。

[0023]

图2是概略地表示半导体发光元件的制造工序的图。

[0024]

图3是概略地表示半导体发光元件的制造工序的图。

[0025]

图4是概略地表示半导体发光元件的制造工序的图。

[0026]

图5是概略地表示半导体发光元件的制造工序的图。

[0027]

图6是概略地表示半导体发光元件的制造工序的图。

[0028]

图7是概略地表示半导体发光元件的制造工序的图。

[0029]

图8是概略地表示半导体发光元件的制造工序的图。

[0030]

图9是概略地表示半导体发光元件的制造工序的图。

[0031]

图10是概略地表示半导体发光元件的制造工序的图。

[0032]

图11是概略地表示半导体发光元件的制造工序的图。

[0033]

图12是概略地表示半导体发光元件的制造工序的图。

[0034]

图13是概略地表示半导体发光元件的制造工序的图。

[0035]

图14是概略地表示第2实施方式的半导体发光元件的构成的剖视图。

[0036]

图15是概略地表示半导体发光元件的制造工序的图。

[0037]

图16是概略地表示半导体发光元件的制造工序的图。

[0038]

图17是概略地表示半导体发光元件的制造工序的图。

[0039]

图18是概略地表示半导体发光元件的制造工序的图。

[0040]

图19是概略地表示半导体发光元件的制造工序的图。

[0041]

图20是概略地表示半导体发光元件的制造工序的图。

[0042]

图21是概略地表示半导体发光元件的制造工序的图。

具体实施方式

[0043]

以下,参照附图对用于实施本发明的方式进行详细说明。此外,在说明中对相同的要素标注相同的附图标记,适当省略重复的说明。另外,为了帮助说明的理解,各附图中的各构成要素的尺寸比,不一定与实际的发光元件的尺寸比一致。

[0044]

本实施方式的半导体发光元件是构成为发出中心波长λ为约360nm以下的“深紫外光”的、所谓duv

‑

led(deep ultraviolet

‑

light emitting diode:深紫外发光二极管)芯片。为输出这样波长的深紫外光,使用带隙为约3.4ev以上的氮化铝镓(algan)系半导体材料。在本实施方式中,特别表示发出中心波长λ为约240nm~320nm的深紫外光的情况。

[0045]

在本说明书中,“algan系半导体材料”是指至少含有氮化铝(aln)及氮化镓(gan)的半导体材料,包括含有氮化铟(inn)等其它材料的半导体材料。因此,本说明书所指的“algan系半导体材料”例如可以以in1‑

x

‑

y

al

x

ga

y

n(0<x y≦1、0<x<1、0<y<1)的组分表示,包括algan或inalgan。本发明书的“algan系半导体材料”例如aln及gan的各自的摩尔分数为1%以上,优选为5%以上、10%以上或20%以上。

[0046]

另外,为了区分不含有aln的材料,有时称为“gan系半导体材料”。“gan系半导体材料”中包括gan、ingan。同样,为了区分不含有gan的材料,有时称为“aln系半导体材料”。“aln系半导体材料”中包括aln、inaln。

[0047]

(第1实施方式)

[0048]

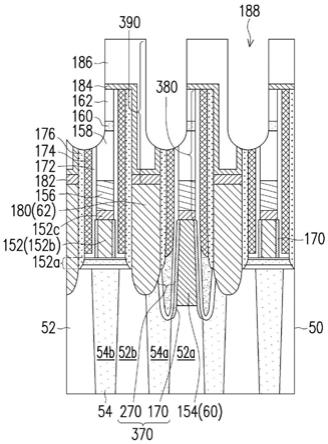

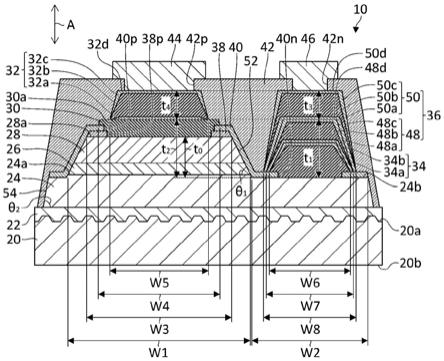

图1是概略地表示第1实施方式的半导体发光元件10的构成的剖视图。半导体发光元件10包括:基板20、基底层22、n型半导体层24、活性层26、p型半导体层28、p侧接触电极30、p侧电流扩散层32、n侧接触电极34、n侧电流扩散层36、第1保护层38、第2保护层40、第3保护层42、p侧焊盘电极44、n侧焊盘电极46。

[0049]

在图1中,有时将箭头a所示的方向称为“上下方向”或“厚度方向”。另外,从基板20观察,有时将远离基板20的方向称为上侧,将朝向基板20的方向称为下侧。

[0050]

基板20具有第1主表面20a和第1主表面20a的相反侧的第2主表面20b。第1主表面20a是用于使从基底层22到p型半导体层28的各层成长的结晶成长面。基板20由对半导体发光元件10发出的深紫外光具有透光性的材料构成,例如由蓝宝石(al2o3)构成。在第1主表面20a形成有深度及间距为亚微米(1μm以下)的微细的凹凸图案。这样的基板20也被称为图案化蓝宝石基板(pss;patterned sapphire substrate)。第2主表面20b是用于将活性层26发出的深紫外光取出到外部的光取出面。基板20可以由aln构成,也可以由algan构成。基板20也可以是第1主表面20a由未图案化的平坦面构成的常规的基板。

[0051]

基底层22设于基板20的第1主表面20a上。基底层22是用于形成n型半导体层24的基础层(模板层)。基底层22例如由未掺杂的aln构成,具体而言由高温生长的aln(ht

‑

aln;

high temperature aln:高温氮化铝)构成。基底层22也可以包含aln层和形成于aln层上的未掺杂的algan层。在基板20为aln基板或algan基板的情况下,基底层22也可以仅由未掺杂的algan层构成。基底层22包含未掺杂的aln层及algan层的至少一者。

[0052]

n型半导体层24设于基底层22上。n型半导体层24由n型的algan系半导体材料构成。例如,掺杂si作为n型的杂质。n型半导体层24以使活性层26发出的深紫外光透过的方式选择组分比,例如构成为aln的摩尔分数为25%以上,优选为40%以上或50%以上。n型半导体层24具有大于活性层26发出的深紫外光的波长的带隙,例如构成为带隙为4.3ev以上。n型半导体层24优选构成为aln的摩尔分数为80%以下,即带隙为5.5ev以下,更优选构成为aln的摩尔分数为70%以下(即带隙为5.2ev以下)。n型半导体层24具有1μm~3μm程度的厚度,例如具有2μm程度的厚度。

[0053]

n型半导体层24被构成为作为杂质的si的浓度为1

×

10

18

/cm3以上且5

×

10

19

/cm3以下。n型半导体层24优选被构成为si的浓度为5

×

10

18

/cm3以上且3

×

10

19

/cm3以下,更优选被构成为7

×

10

18

/cm3以上且2

×

10

19

/cm3以下。在一实施例中,n型半导体层24的si浓度为1

×

10

19

/cm3前后,具体而言为8

×

10

18

/cm3以上且1.5

×

10

19

/cm3以下的范围。

[0054]

n型半导体层24具有第1上表面24a和第2上表面24b。第1上表面24a是形成有活性层26的部分。第2上表面24b是未形成活性层26而形成有n侧接触电极34的部分。第1上表面24a及第2上表面24b彼此高度不同,从基板20到第1上表面24a的高度大于从基板20到第2上表面24b的高度。在此,将第1上表面24a所在的区域定义为“第1区域w1”,将第2上表面24b所在的区域定义为“第2区域w2”。

[0055]

活性层26设于n型半导体层24的第1上表面24a上。活性层26由algan系半导体材料构成,被夹在n型半导体层24与p型半导体层28之间而形成双异质结构造。为输出波长355nm以下的深紫外光,活性层26构成为带隙为3.4ev以上,例如,以能够输出波长320nm以下的深紫外光的方式选择aln组分比。

[0056]

活性层26例如具有单层或多层的量子阱构造,以由未掺杂的algan系半导体材料构成的势垒层和由未掺杂的algan系半导体材料构成的阱层的层叠体构成。活性层26例如包含与n型半导体层24直接接触的第1势垒层和设于第1势垒层上的第1阱层。在第1势垒层与第1阱层之间,也可以追加设置阱层及势垒层的一个以上的对。势垒层及阱层分别具有1nm~20nm程度的厚度,例如具有2nm~10nm程度的厚度。

[0057]

活性层26也可以还包含与p型半导体层28直接接触的电子阻挡层。电子阻挡层由未掺杂的algan系半导体材料构成,例如构成为aln的摩尔分数为40%以上,优选为50%以上。电子阻挡层也可以构成为aln的摩尔分数为80%以上,也可以由不包含gan的aln系半导体材料构成。电子阻挡层具有1nm~10nm程度的厚度,例如具有2nm~5nm程度的厚度。

[0058]

p型半导体层28设于活性层26上。p型半导体层28由p型的algan系半导体材料或p型的gan系半导体材料构成,例如,由掺杂镁(mg)作为p型的杂质的algan或gan构成。p型半导体层28例如具有300nm~1400nm程度的厚度。例如,也可以构成为从n型半导体层24的第2上表面24b到p型半导体层28的上表面28a的高度t0为400nm以上且1500nm以下。

[0059]

p型半导体层28也可以由多层构成。p型半导体层28例如也可以具有p型包覆层和p型接触层。p型包覆层是与p型接触层相比aln比率高的p型algan层,以与活性层26直接接触的方式设置。p型接触层是与p型包覆层相比aln比率低的p型algan层或p型gan层。p型接触

层设于p型包覆层上,以与p侧接触电极30直接接触的方式设置。

[0060]

p型包覆层以使活性层26发出的深紫外光透过的方式选择组分比。p型包覆层例如构成为aln的摩尔分数为25%以上,优选为40%以上或50%以上。p型包覆层的aln比率,例如与n型半导体层24的aln比率为相同程度,或大于n型半导体层24的aln比率。p型包覆层的aln比率也可以为70%以上或80%以上。p型包覆层具有10nm~100nm程度的厚度,例如具有15nm~70nm程度的厚度。

[0061]

为了得到与p侧接触电极30良好的欧姆接触,p型接触层构成为aln比率为20%以下,优选构成为aln比率为10%以下、5%以下或0%。即,p型接触层也可以由不含有aln的p型gan系半导体材料构成。p型接触层具有300nm~1500nm程度的厚度,例如具有500nm~1000nm程度的厚度。

[0062]

p侧接触电极30设于p型半导体层28上,与p型半导体层28的上表面28a接触。p侧接触电极30由能够与p型半导体层28欧姆接触的材料构成,例如由氧化锡(sno2)、氧化锌(zno)、铟锡氧化物(ito)等透明导电性氧化物(tco)构成。p侧接触电极30的厚度为20nm~500nm程度,优选为50nm以上,更优选为100nm以上。

[0063]

p侧接触电极30以封闭第1保护层38的第1p侧接触开口38p及第2保护层40的第2p侧接触开口40p的方式设置。p侧接触电极30以重叠在第1保护层38及第2保护层40上的方式设置。因此,形成有p侧接触电极30的第4区域w4比第1p侧接触开口38p及第2p侧接触开口40p各自的开口区域大。在沿厚度方向观察半导体发光元件10时的俯视观察中,第4区域w4的内侧包含第1p侧接触开口38p及第2p侧接触开口40p各自的开口区域的整体。另外,形成有p侧接触电极30的第4区域w4比p型半导体层28的上表面28a所在的第3区域w3窄。在沿厚度方向观察半导体发光元件10时的俯视观察中,第3区域w3的内侧包含第4区域w4的整体。形成有p侧接触电极30的第4区域w4的面积,例如为p型半导体层28的上表面28a所在的第3区域w3的80%以上或90%以上。

[0064]

p侧电流扩散层32设于p侧接触电极30上。形成有p侧电流扩散层32的第5区域比p侧接触电极30所在的第4区域窄。在沿厚度方向观察半导体发光元件10时的俯视观察中,第4区域w4的内侧包含第5区域w5的整体。形成有p侧电流扩散层32的第5区域w5的面积,例如为p侧接触电极30所在的第4区域w4的80%以上或90%以上。为使从p侧焊盘电极44注入的电流在横向(水平方向)上扩散,p侧电流扩散层32优选具有一定程度的厚度。p侧电流扩散层32的厚度为300nm以上且1500nm以下,例如为500nm~1000nm程度。

[0065]

p侧电流扩散层32具有依次层叠第1tin层32a、金属层32b及第2tin层32c的层叠构造。第1tin层32a及第2tin层32c由具有导电性的氮化钛(tin)构成。具有导电性的tin的导电率为1

×

10

‑5ω

·

m以下,例如为4

×

10

‑7ω

·

m程度。第1tin层32a及第2tin层32c各自的厚度为10nm以上,例如为50nm~200nm程度。

[0066]

p侧电流扩散层32的金属层32b由单一金属层或多个金属层构成。金属层32b由钛(ti)、铬(cr)、镍(ni)、铝(al)、铂(pt)、钯(pd)或铑(rh)等金属材料构成。金属层32b也可以具有层叠材料不同的多个金属层的构造。金属层32b可以具有层叠由第1金属材料构成的第1金属层和由第2金属材料构成的第2金属层的构造,也可以具有交错地重叠多个第1金属层和多个第2金属层的构造。金属层32b也可以还具有由第3金属材料构成的第3金属层。金属层32b的厚度大于第1tin层32a及第2tin层32c各自的厚度。金属层32b的厚度为100nm以上,

例如为300nm~800nm程度。

[0067]

n侧接触电极34设于n型半导体层24的第2上表面24b上,与n型半导体层24接触。n侧接触电极34以封闭第2保护层40的n侧接触开口40n的方式设置。n侧接触电极34以重叠在第2保护层40上的方式设置。形成有n侧接触电极34的第6区域w6比n侧接触开口40n的开口区域大。在沿厚度方向观察半导体发光元件10时的俯视观察中,第4区域w4的内侧包含n侧接触开口40n的开口区域的整体。

[0068]

n侧接触电极34具有金属层34a和tin层34b。金属层34a由能够与n型半导体层24欧姆接触,且对活性层26发出的深紫外光的反射率高的材料构成。金属层34a例如包含与n型半导体层24直接接触的ti层和与ti层直接接触的铝(al)层。ti层的厚度为1nm~10nm程度,优选为5nm以下,更优选为1nm~2nm。通过使ti的厚度减小,能够提高从n型半导体层24观察时的n侧接触电极34的紫外光反射率。al层的厚度优选为200nm以上,例如为300nm~1000nm程度。通过使al层的厚度增大,能够提高n侧接触电极34的紫外光反射率。金属层34a也可以还具有设于al层上的ti层。

[0069]

tin层34b设于金属层34b上,由导电性的tin构成。具有导电性的tin的导电率为1

×

10

‑5ω

·

m以下,例如为4

×

10

‑7ω

·

m程度。tin层34b的厚度为10nm以上,例如为50nm~200nm程度。

[0070]

n侧电流扩散层36设于n侧接触电极34上。n侧电流扩散层36遍及比n侧接触电极34所在的第6区域w6大的第8区域w8而设置。在沿厚度方向观察半导体发光元件10时的俯视观察中,第8区域w8的内侧包含第6区域w6的整体。因此,n侧电流扩散层36覆盖n侧接触电极34的上表面及侧面的整体,防止n侧接触电极34的上表面或侧面露出。

[0071]

n侧电流扩散层36包含第1电流扩散层48和第2电流扩散层50。第1电流扩散层48设于n侧接触电极34上。第1电流扩散层48遍及比形成有n侧接触电极34的第6区域w6大的第7区域w7而设置。在沿厚度方向观察半导体发光元件10时的俯视观察中,第7区域w7的内侧包含第6区域w6的整体。因此,第1电流扩散层48覆盖n侧接触电极34的上表面及侧面的整体,防止n侧接触电极34的上表面或侧面露出。第1电流扩散层48以与第2保护层40接触的方式设置,但与n型半导体层24不接触。第1电流扩散层48的厚度为100nm以上且1000nm以下,例如为200nm~800nm程度。

[0072]

第2电流扩散层50设于第1电流扩散层48上。第2电流扩散层50遍及比形成有第1电流扩散层48的第7区域w7宽的第8区域w8而设置。在沿厚度方向观察半导体发光元件10时的俯视观察中,第8区域w8的内侧包含第7区域w7的整体。因此,第2电流扩散层50覆盖第1电流扩散层48的上表面及侧面的整体,防止第1电流扩散层48的上表面或侧面露出。第2电流扩散层50以与第2保护层40接触的方式设置,但与n型半导体层24不接触。第2电流扩散层50的厚度为300nm以上且1500nm以下,例如为500nm~1000nm程度。

[0073]

第1电流扩散层48具有依次层叠第1tin层48a、金属层48b及第2tin层48c的层叠构造。第1tin层48a及第2tin层48c由具有导电性的tin构成。具有导电性的tin的导电率为1

×

10

‑5ω

·

m以下,例如为4

×

10

‑7ω

·

m程度。第1tin层48a及第2tin层48c各自的厚度为10nm以上,例如为50nm~200nm程度。

[0074]

第1电流扩散层48所包含的金属层48b由单一金属层或多个金属层构成。金属层48b由钛(ti)、铬(cr)、镍(ni)、铝(al)、铂(pt)、钯(pd)或铑(rh)等金属材料构成。金属层

48b也可以具有层叠材料不同的多个金属层的构造。金属层48b可以具有层叠由第1金属材料构成的第1金属层和由第2金属材料构成的第2金属层的构造,也可以具有交错地重叠多个第1金属层和多个第2金属层的构造。金属层48b也可以还具有由第3金属材料构成的第3金属层。金属层48b的厚度大于第1tin层48a及第2tin层48c各自的厚度。金属层48b的厚度为100nm以上,例如为200nm~800nm程度。

[0075]

第1电流扩散层48以与p侧接触电极30的高度一致的方式形成。即,第1电流扩散层48的上表面48d的高度位置与p侧接触电极30的上表面30a的高度位置实质上一致。具体而言,构成为第1电流扩散层48的上表面48d的高度位置与p侧接触电极30的上表面30a的高度位置的差为100nm以下,优选为50nm以下。高度位置的基准没有特别限定,例如在以n型半导体层24的第2上表面24b为基准的情况下,从第2上表面24b到第1电流扩散层48的上表面48d的厚度t1与从第2上表面24b到p侧接触电极30的上表面30a的厚度t2的差为100nm以下或50nm以下。第1电流扩散层48的上表面48d的高度位置可以比p侧接触电极30的上表面30a的高度位置高,也可以比p侧接触电极30的上表面30a的高度位置低,也可以完全一致。

[0076]

第2电流扩散层50具有依次层叠第1tin层50a、金属层50b及第2tin层50c的层叠构造。第2电流扩散层50与p侧电流扩散层32同样地构成,构成为第2电流扩散层50的厚度t3与p侧电流扩散层32的厚度t4相同。其结果,第2电流扩散层50的上表面50d的高度位置与p侧电流扩散层32的上表面32d的高度位置实质上一致。具体而言,构成为第2电流扩散层50的上表面50d的高度位置与p侧电流扩散层32的上表面32d的高度位置的差为100nm以下,优选为50nm以下。第2电流扩散层50的上表面50d的高度位置可以比p侧电流扩散层32的上表面32d的高度位置高,也可以比p侧电流扩散层32的上表面32d的高度位置低,也可以完全一致。

[0077]

第1保护层38设于p型半导体层28上。第1保护层38在与第1p侧接触开口38p不同的部位覆盖p型半导体层28的上表面28a。第1保护层38由氧化硅(sio2)、氮氧化硅(sion)等电介质材料构成。第1保护层38的厚度为50nm以上,例如为100nm以上且500nm以下。

[0078]

第2保护层40设于n型半导体层24的第2上表面24b上、第1保护层38上、半导体发光元件10的第1台面52上。第2保护层40由氧化铝(al2o3)等电介质材料构成。第2保护层40的厚度可以设为5nm以上且50nm以下,例如可以设为10nm~30nm程度。

[0079]

第2保护层40在与n侧接触开口40n不同的部位覆盖n型半导体层24的第2上表面24b。第2保护层40在与第2p侧接触开口40p不同的部位覆盖第1保护层38。第2p侧接触开口40p的开口区域比第1p侧接触开口38p的开口区域大。在沿厚度方向观察半导体发光元件10时的俯视观察中,第2p侧接触开口40p的开口区域的内侧包含第1p侧接触开口38p的开口区域的整体。

[0080]

第2保护层40覆盖第1台面52。第1台面52是在第1区域w1的内侧以第1角度θ1倾斜的侧面,包含n型半导体层24的第1侧面、活性层26的侧面、p型半导体层28的侧面、第1保护层38的侧面。第1台面52的倾斜的第1角度θ1为15度以上且50度以下,例如为20度以上且40度以下。第1角度θ1使用活性层26的折射率n,优选为θ1<{π/2 sin

‑1(1/n)}/2。通过将第1角度θ1设定为这样的值,紫外光在基板20的第2主表面20b全反射,能够防止紫外光不向基板20的外部射出。

[0081]

第3保护层42以覆盖半导体发光元件10的整体的方式设置。第3保护层42由氧化硅

(sio2)、氮氧化硅(sion)、氮化硅(sin)、氮化铝(aln)或氧氮化铝(alon)等电介质材料构成。第3保护层42的厚度为100nm以上,例如为500nm~2000nm程度。

[0082]

第3保护层42设于p侧接触电极30上、p侧电流扩散层32上、n侧电流扩散层36上、第2保护层40上、半导体发光元件10的第2台面54上。第3保护层42在与p侧焊盘开口42p不同的部位覆盖p侧电流扩散层32,在与n侧焊盘开口42n不同的部位覆盖n侧电流扩散层36。第2台面54是在第1区域w1及第2区域w2的外侧以大于第1角度的第2角度θ2倾斜的侧面,包含n型半导体层24的第2侧面。第2台面54的倾斜的第2角度θ2为55度以上且小于70度,例如为60度~65度程度。

[0083]

p侧焊盘电极44及n侧焊盘电极46是在将半导体发光元件10安装于封装基板等时进行键合接合的部分。p侧焊盘电极44设于p侧电流扩散层32上,与p侧电流扩散层32接触并与p侧接触电极30电连接。p侧焊盘电极44以封闭p侧焊盘开口42p的方式设置,重叠在第3保护层42上。n侧焊盘电极46设于n侧电流扩散层36上,与n侧电流扩散层36接触并与n侧接触电极34电连接。n侧焊盘电极46以封闭n侧焊盘开口42n的方式设置,重叠在第3保护层42上。

[0084]

从耐腐蚀性的观点出发,p侧焊盘电极44及n侧焊盘电极46构成为含有au,例如由ni/au、ti/au或ti/pt/au的层叠构造构成。p侧焊盘电极44及n侧焊盘电极46也可以还包含由键合接合用的金属接合材料构成的金属层,例如可以还包含金锡(ausn)层,也可以还包含sn层与au层的层叠构造。

[0085]

接着,说明半导体发光元件10的制造方法。图2~图13是概略地表示半导体发光元件10的制造工序的图。在图2中,首先在基板20的第1主表面20a上依次形成基底层22、n型半导体层24、活性层26、p型半导体层28、第1保护层38。活性层26形成于n型半导体层24的第1上表面24a。

[0086]

基板20例如是图案化的蓝宝石基板。基底层22例如包含ht

‑

aln层和掺杂的algan层。n型半导体层24、活性层26及p型半导体层28是由algan系半导体材料、aln系半导体材料或gan系半导体材料构成的半导体层,可以使用有机金属化合物气相外延(movpe;metal organic vapor phase epitaxy)法、分子束外延(mbe;molecular beam epitaxy)法等已知的外延成长法形成。第1保护层38由sio2或sion构成,可以使用化合物气相外延法(cvd)等已知的技术形成。

[0087]

接着,如图2所示,在第1保护层38上形成第1掩模61。第1掩模61是用于形成图1的第1台面52的蚀刻掩模。第1掩模61可以使用已知的光刻技术形成。第1掩模61设于与图1的第1区域w1对应的部位。第1掩模61的侧面倾斜。第1掩模61的侧面的倾斜角以在后续的蚀刻工序中形成以第1角度θ1倾斜的第1台面52的方式设定。

[0088]

接着,如图3所示,从第1掩模61上蚀刻第1保护层38、p型半导体层28及活性层26,使与第1掩模61不重叠的区域的n型半导体层24露出。该蚀刻工序的蚀刻深度d相当于活性层26、p型半导体层28及第1保护层38的厚度合计,例如为400nm以上且1500nm以下。通过该蚀刻工序,形成以第1角度θ1倾斜的第1台面52,并且形成n型半导体层24的第2上表面24b。

[0089]

在图3的蚀刻工序中,可以使用使用了氯系的蚀刻气体的反应性离子蚀刻,并可以使用电感耦合型等离子体(icp;inductively coupled plasma)蚀刻。例如,作为蚀刻气体可以使用含有氯(cl2)、三氯化硼(bcl3)、四氯化硅(sicl4)等氯的反应性气体。此外,也可以将反应性气体与惰性气体组合进行干式蚀刻,也可以在氯系气体中混合氩(ar)等稀有气

体。在形成第1台面52及第2上表面24b后,除去第1掩模61。

[0090]

接着,如图4所示,形成第2保护层40。第2保护层40覆盖n型半导体层24的第2上表面24b,覆盖第1保护层38,并且覆盖n型半导体层24的第1侧面、活性层26的侧面及p型半导体层28的侧面(即,第1台面52)。第2保护层40例如由al2o3构成,可以通过以三甲基铝(tma)和o2等离子体或o3为原料的原子层沉积(ald)法形成。

[0091]

接着,如图5所示,在第2保护层40上形成第2掩模62,除去位于未设置第2掩模62的第1开口71及第2开口72的第2保护层40。第2掩模62可以使用已知的光刻技术形成。第2保护层40可以使用氯系气体或氯系气体与稀有气体的混合气体进行干式蚀刻。通过该蚀刻工序,形成第2p侧接触开口40p及n侧接触开口40n。在第2p侧接触开口40p中,第1保护层38露出。在n侧接触开口40n中,n型半导体层24的第2上表面24b露出。在形成第2p侧接触开口40p及n侧接触开口40n后,除去第2掩模62。

[0092]

接着,如图6所示,在第2保护层40上形成第3掩模63,在未设置第3掩模63的第3开口73上形成n侧接触电极34。第3掩模63可以使用已知的光刻技术形成。第3开口73位于应形成n侧接触电极34的第6区域w6。第3开口73的开口区域比n侧接触开口40n的开口区域大。在第3开口73上,首先形成金属层34a。金属层34a具有依次层叠的ti层、al层及ti层。接着,在金属层34a上形成tin层34b。金属层34a的各层及tin层34b可以通过溅射法、eb蒸镀法形成。

[0093]

接着,除去第3掩模63,对n侧接触电极34实施退火处理。n侧接触电极34的退火处理在低于al的熔点(约660℃)的温度下执行,例如在500℃以上且650℃以下,优选在550℃以上且625℃以下的温度下执行。通过退火处理,能够使n侧接触电极34的接触电阻为1

×

10

‑2ω

·

cm2以下。另外,通过使退火温度低于al的熔点,能够提高退火后的n侧接触电极34的平坦性,使紫外光反射率为80%以上或90%以上。

[0094]

接着,如图7所示,在n侧接触电极34及第2保护层40上形成第4掩模64,除去位于未设置第4掩模64的第4开口74的第1保护层38。第4掩模64可以使用已知的光刻技术形成。第4开口74的开口区域比第2p侧接触开口40p的开口区域窄。第1保护层38可以使用氢氟酸(hf)与氟化铵(nh4f)的混合液即缓冲氢氟酸(bhf)除去。通过在第4开口74上除去第1保护层38,形成第1p侧接触开口38p。在第1p侧接触开口38p中,p型半导体层28的上表面28a露出。通过对第1保护层38进行湿式蚀刻,与对第1保护层38进行干式蚀刻的情况相比,能够减少对露出的p型半导体层28的上表面28a的损伤。在形成第1p侧接触开口38p后,除去第4掩模64。

[0095]

接着,如图8所示,在n侧接触电极34及第2保护层40上形成第5掩模65,在未设置第5掩模65的第5开口75上形成p侧接触电极30。第5开口75位于图1的第4区域w4。第5开口75的开口区域比第1p侧接触开口38p的开口区域及第2p侧接触开口40p的开口区域大。p侧接触电极30与p型半导体层28的上表面28a接触,以封闭第1p侧接触开口38p及第2p侧接触开口40p的方式设置。p侧接触电极30例如由ito构成,可以通过溅射法形成。

[0096]

接着,除去第5掩模65,对p侧接触电极30实施退火处理。通过退火处理能够使p侧接触电极30的接触电阻为1

×

10

‑2ω

·

cm2以下。

[0097]

接着,如图9所示,在p侧接触电极30及第2保护层40上形成第6掩模66,在未设置第6掩模66的第6开口76上形成第1电流扩散层48。第6掩模66可以使用已知的光刻技术形成。第6开口76位于应形成第1电流扩散层48的第7区域w7。第6开口76比形成有n侧接触电极34的第6区域w6大。第1电流扩散层48形成于退火处理后的n侧接触电极34上。在第6开口76上,

首先形成第1tin层48a,在第1tin层48a上形成金属层48b,在金属层48b上形成第2tin层48c。第1tin层48a、金属层48b及第2tin层48c可以通过溅射法、eb蒸镀法形成。第1电流扩散层48的上表面48d的高度位置与p侧接触电极30的上表面30a的高度位置对应。p侧接触电极30的上表面30a的高度位置与第1电流扩散层48的上表面48d的高度位置的差为100nm以下或50nm以下。在形成第1电流扩散层48后,除去第6掩模66。

[0098]

接着,如图10所示,在p侧接触电极30、第2保护层40及第1电流扩散层48上形成第7掩模67。在未设置第7掩模67的第7开口77上形成p侧电流扩散层32,在未设置第7掩模67的第8开口78上形成第2电流扩散层50。第7开口77位于图1的第5区域w5。第7开口77的开口区域比形成有p侧接触电极30的第4区域w4窄。第8开口78位于图1的第8区域w8。第8开口78的开口区域比形成第1电流扩散层48的第7区域w7大。

[0099]

p侧电流扩散层32在第7开口77上形成于p侧接触电极30上。第2电流扩散层50在第8开口78上形成于第1电流扩散层48上。p侧电流扩散层32及第2电流扩散层50可以同时形成。首先,形成第1tin层32a、50a,接着形成金属层32b、50b,接着形成第2tin层32c、50c。第1tin层32a、50a,金属层32b、50b及第2tin层32c、50c可以由溅射法、eb蒸镀法形成。通过同时形成p侧电流扩散层32和第2电流扩散层50,能够使p侧电流扩散层32与第2电流扩散层50的厚度相同,能够使p侧电流扩散层32的上表面32d的高度位置与第2电流扩散层50的上表面50d的高度位置一致。在形成p侧电流扩散层32及第2电流扩散层50后,除去第7掩模67。

[0100]

此外,p侧电流扩散层32及第2电流扩散层50也可以不是同时形成,而是分别形成。例如,也可以在使用用于形成p侧电流扩散层32的掩模来形成p侧电流扩散层32后,使用用于形成第2电流扩散层50的掩模来形成第2电流扩散层50。p侧电流扩散层32和第2电流扩散层50的形成顺序没有特别限定,也可以在形成第2电流扩散层50后,形成p侧电流扩散层32。例如,也可以在连续形成第1电流扩散层48和第2电流扩散层50后,形成p侧电流扩散层32。

[0101]

接着,如图11所示,以覆盖p侧接触电极30、p侧电流扩散层32、第2保护层40及n侧电流扩散层36的方式形成第8掩模68。第8掩模68遍及图1的第1区域w1及第2区域w2而设置。第8掩模68的侧面倾斜,以能够形成以第2角度θ2倾斜的第2台面54的方式设定第8掩模68的侧面的倾斜角。第8掩模68可以使用已知的光刻技术形成。接着,从第8掩模68上蚀刻第2保护层40及n型半导体层24,使与第8掩模68不重叠的区域的基底层22露出。通过该蚀刻工序,形成以第2角度θ2倾斜的第2台面54。第2保护层40及n型半导体层24可以使用氯系气体或氯系气体与稀有气体的混合气体进行干式蚀刻。在形成第2台面54后,除去第8掩模68。

[0102]

接着,如图12所示,以覆盖n型半导体层24的第2侧面(第2台面54)、p侧接触电极30、p侧电流扩散层32、第2保护层40及n侧电流扩散层36的方式形成第3保护层42。第3保护层42遍及第1区域w1及第2区域w2的二者而形成,以覆盖元件构造的上表面的整体的方式形成。第3保护层42例如由sio2或sion构成,可以使用化合物气相外延法(cvd)等已知的技术形成。

[0103]

接着,如图13所示,在第3保护层42上形成第9掩模69,除去位于未设置第9掩模69的第9开口79、第10开口80及第11开口81的第3保护层42。第3保护层42可以使用cf系的蚀刻气体进行干式蚀刻,例如,可以使用六氟乙烷(c2f6)。通过该蚀刻工序,在第9开口79上形成p侧电流扩散层32露出的p侧焊盘开口42p,在第10开口80上形成n侧电流扩散层36露出的n侧焊盘开口42n。另外,在第11开口81中,基底层22露出。第11开口81位于从1块基板形成多

个半导体发光元件10的情况下的元件分离区域。在执行部分地除去第3保护层42的蚀刻工序后,除去第9掩模69。

[0104]

在图13所示的干式蚀刻工序中,p侧电流扩散层32及n侧电流扩散层36作为蚀刻停止层发挥功能。更具体而言,p侧电流扩散层32的第2tin层32c及第1电流扩散层48的第2tin层48c作为蚀刻停止层发挥功能。tin与用于除去第3保护层42的氟系的蚀刻气体的反应性低,不易产生由蚀刻导致的副产物。因此,能够防止对p侧接触电极30及n侧接触电极34的损伤。另外,在执行干式蚀刻之后,也能够维持p侧电流扩散层32及n侧电流扩散层36的露出面的高品质。

[0105]

接着,在p侧焊盘开口42p上、在p侧电流扩散层32上形成p侧焊盘电极44,在n侧焊盘开口42n上、在n侧电流扩散层36上形成n侧焊盘电极46。p侧焊盘电极44及n侧焊盘电极46例如可以通过将ni层或ti层沉积在p侧电流扩散层32及n侧电流扩散层36上,并在其上沉积au层而形成。也可以在au层上进一步设置其他金属层,例如也可以形成sn层、ausn层、sn/au的层叠构造。

[0106]

p侧焊盘电极44及n侧焊盘电极46可以同时形成,也可以分别形成。例如,也可以在使用用于形成p侧焊盘电极44的掩模来形成p侧焊盘电极44后,使用用于形成n侧焊盘电极46的掩模来形成n侧焊盘电极46。p侧焊盘电极44和n侧焊盘电极46的形成顺序没有特别限定,也可以在形成n侧焊盘电极46后形成p侧焊盘电极44。

[0107]

通过以上工序,形成图1所示的半导体发光元件10。

[0108]

根据本实施方式,通过设置p侧电流扩散层32,能够使从p侧焊盘电极44注入的电流在横向(水平方向)上扩散,能够扩大活性层26的发光面积。由此,能够提高半导体发光元件10的光输出。

[0109]

根据本实施方式,通过使形成有p侧电流扩散层32的第5区域w5比形成有p侧接触电极30的第4区域w4窄,能够进一步增大p侧接触电极30在p型半导体层28的上表面28a中所占的面积的最大值。假设,在使形成有p侧电流扩散层32的第5区域w5比形成有p侧接触电极30的第4区域w4大的情况下,由于第5区域w5变得比p型半导体层28的上表面28a所在的第3区域w3窄,且第4区域w4变得比第5区域w5窄,因此第4区域w4能够取得的最大面积减少。另一方面,根据本实施方式,能够使p侧接触电极30在p型半导体层28的上表面28a中所占的面积尽可能地增大,能够扩大活性层26的发光面积。由此,能够提高半导体发光元件10的光输出。

[0110]

根据本实施方式,通过使形成有n侧电流扩散层36的第8区域w8比形成有n侧接触电极34的第6区域w6大,能够由n侧电流扩散层36覆盖n侧接触电极34的整体。另外,由于n侧电流扩散层36由第1电流扩散层48及第2电流扩散层50构成,因此能够进一步提高覆盖并密封n侧接触电极34的功能。由此,能够防止n侧接触电极34中包含的al层在通电使用时因氧化等而腐蚀。其结果,能够抑制n侧接触电极34的紫外光反射率的降低,能够长期维持作为反射电极的功能,能够抑制伴随通电使用的光输出的降低。即,能够实现可长期维持高的光输出的半导体发光元件10。

[0111]

根据本实施方式,作为p侧电流扩散层32及n侧电流扩散层36,通过使用依次层叠tin层、金属层及tin层的层叠构造,能够实现高导电性并且防止金属的迁移。例如,具体而言,通过使用tin层能够防止金属的迁移,并且通过在tin层与tin层之间放入金属层能够提

高导电率。

[0112]

根据本实施方式,通过设置第1电流扩散层48,能够使p侧接触电极30的上表面30a的高度位置与第1电流扩散层48的上表面48d的高度位置一致。特别是,在本实施方式中,由于从n型半导体层24的第2上表面24b到p型半导体层28的上表面28a的厚度t0较大、为400nm~1500nm程度,因此在未设置用于高度调整的第1电流扩散层48的情况下,p侧焊盘电极44与n侧焊盘电极46的高度大幅偏离。在p侧焊盘电极44与n侧焊盘电极46的高度的偏离大的情况下,在将半导体发光元件键合接合于安装基板等时,有可能施加不均匀的力而对半导体发光元件产生损伤。特别是,在p侧焊盘电极44与n侧焊盘电极46的高度的偏离为200nm以上或500nm以上的情况下,安装时的不良率有增加的倾向。另一方面,根据本实施方式,通过使p侧接触电极30的上表面30a的高度位置与第1电流扩散层48的上表面48d的高度位置的差为100nm以下,能够使p侧焊盘电极44与n侧焊盘电极46的高度的偏离为100nm以下,能够降低安装时的不良率。

[0113]

根据本实施方式,通过使p侧电流扩散层32和第2电流扩散层50的构造、厚度实质上相同,在半导体发光元件10的安装时能够使对p侧接触电极30和第1电流扩散层48施加的力均匀化,能够降低安装时的不良率。

[0114]

根据本实施方式,通过在p侧电流扩散层32及n侧电流扩散层36中使用tin层,能够提高与由电介质材料构成的第3保护层42的密合性。由此,能够防止第3保护层42从p侧接触电极30、n侧接触电极34剥离而导致的密封功能的降低。由此,能够实现长期内光输出不易降低的半导体发光元件10。

[0115]

根据本实施方式,通过以在n侧接触电极34的金属层34a上设置tin层34b的状态进行退火处理,能够防止退火处理时的金属层34a的氧化。由此,能够防止n侧接触电极34的紫外光反射率的降低、n侧接触电极34的上表面的平坦性的降低。

[0116]

根据本实施方式,通过在n侧接触电极34的退火处理后形成第1电流扩散层48及第2电流扩散层50,能够防止因退火处理而导致第1电流扩散层48及第2电流扩散层50的劣化。同样,通过在p侧接触电极30的退火处理后形成p侧电流扩散层32,能够防止由退火处理导致的p侧电流扩散层32的劣化。

[0117]

[第2实施方式]

[0118]

图14是概略地表示第2实施方式的半导体发光元件110的构成的剖视图。图14的半导体发光元件110的p侧接触电极130、p侧电流扩散层132、n侧电流扩散层136、第1保护层138及第2保护层140的构成与上述实施方式不同。以下,对于本实施方式,以与上述第1实施方式的不同为中心进行说明,适当省略重复的说明。

[0119]

半导体发光元件110包括:基板20、基底层22、n型半导体层24、活性层26、p型半导体层28、p侧接触电极130、p侧电流扩散层132、n侧接触电极34、n侧电流扩散层136、第1保护层138、第2保护层140、第3保护层42、p侧焊盘电极44、n侧焊盘电极46。

[0120]

p侧接触电极130设于p型半导体层28的上表面28a,且设于p型半导体层28与第1保护层138之间。p侧接触电极130在设于第1保护层138的下侧的点上与上述实施方式的p侧接触电极30不同。p侧接触电极130具有金属层130b和tin层130c。金属层130b由rh等铂族金属,或ni/au的层叠构造构成。tin层130c由导电性的tin构成,以覆盖金属层130b的上表面及侧面的方式设置。p侧接触电极130的上表面130a的高度位置与第1电流扩散层48的上表

面48d的高度位置一致。p侧接触电极130的上表面130a的高度位置与第1电流扩散层48的上表面48d的高度位置的差为100nm以下,优选为50nm以下。

[0121]

p侧电流扩散层132设于p侧接触电极130的上表面130a。p侧电流扩散层132以封闭设于第1保护层138的第1p侧接触开口138p及设于第2保护层140的n侧接触开口140p的方式设置。p侧电流扩散层132以重叠在第1保护层138及第2保护层140上的方式设置。p侧电流扩散层132具有依次层叠第1tin层132a、金属层132b及第2tin层132c的层叠构造。

[0122]

n侧电流扩散层136遍及比形成有n侧接触电极34的第6区域w6大的第7区域w7而设置。n侧电流扩散层136包含第1电流扩散层48和第2电流扩散层150。第1电流扩散层48与上述实施方式同样地构成。第2电流扩散层150与上述实施方式不同,设于比形成有第1电流扩散层48的第7区域w7窄的第9区域w9。在沿厚度方向观察半导体发光元件110时的俯视观察中,第7区域w7的内侧包含第9区域w9的整体。在图示的示例中,设有第2电流扩散层150的第9区域w9比设有n侧接触电极34的第6区域w6窄。此外,设有第2电流扩散层150的第9区域w9也可以与第6区域w6一致,也可以比第6区域w6大。

[0123]

第2电流扩散层150具有依次层叠第1tin层150a、金属层150b及第2tin层150c的层叠构造。第2电流扩散层150与p侧电流扩散层132同样地构成,构成为第2电流扩散层150的厚度t3与p侧电流扩散层132的厚度t4相同。其结果,第2电流扩散层150的上表面150d的高度位置与p侧电流扩散层132的上表面132d的高度位置实质上一致。具体而言,构成为第2电流扩散层150的上表面150d的高度位置与p侧电流扩散层132的上表面132d的高度位置的差为100nm以下,优选为50nm以下。

[0124]

接着,说明半导体发光元件110的制造方法。从图15起是概略地表示半导体发光元件110的制造工序的图。在图15中,首先在基板20的第1主表面20a上形成基底层22、n型半导体层24、活性层26及p型半导体层28。这些层的形成方法与图2的工序相同。

[0125]

接着,在p型半导体层28的上表面28a上形成p侧接触电极130。p侧接触电极130形成于图14的第4区域w4。首先,在除第4区域w4之外的p型半导体层28的上表面28a上形成掩模。接着,在第4区域w4形成金属层130b,在金属层130b上形成tin层130c。p侧接触电极130可以通过溅射法、eb蒸镀法形成。由此,形成p侧接触电极130。也可以在形成p侧接触电极130后除去掩模,并对p侧接触电极130实施退火处理。

[0126]

接着,如图16所示,在p型半导体层28及p侧接触电极130上形成第1保护层138。第1保护层138由sio2或sion构成,可以使用cvd法等已知的技术形成。

[0127]

接着,如图17所示,形成第1台面52。第1台面52与图3的工序同样地形成。

[0128]

接着,如图18所示,以覆盖n型半导体层24的第2上表面24b及第1保护层138的方式形成第2保护层140。第2保护层140可以与图4的工序同样地形成。接着,部分地除去第2保护膜140,形成第2p侧接触开口140p及n侧接触开口140n。第2p侧接触开口140p及n侧接触开口140n可以与图5的工序同样地形成。

[0129]

接着,如图19所示,在n侧接触开口140n形成n侧接触电极34,在n侧接触电极34上形成第1电流扩散层48。n侧接触电极34可以与图6的工序同样地形成。第1电流扩散层48可以与图9的工序同样地形成。

[0130]

接着,如图20所示,在第1保护层138形成第1p侧接触开口138p,并使p侧接触电极130的上表面130a露出。第1p侧接触开口138p可以与图7的工序同样地形成。

[0131]

接着,如图21所示,在p侧接触电极130上形成p侧电流扩散层132,在第1电流扩散层48上形成第2电流扩散层150。形成有p侧电流扩散层132的第5区域w5比形成有p侧接触电极130第4区域w4窄。另外,形成有第2电流扩散层150的第9区域w9比形成有第1电流扩散层48的第7区域w7窄。p侧电流扩散层132及第2电流扩散层150可以同时形成,可以与图10的工序同样地形成。

[0132]

接着,与图11~图13的工序同样地形成第2台面54,形成第3保护层42,在第3保护层42形成n侧焊盘开口42n及p侧焊盘开口42p,形成p侧焊盘电极44及n侧焊盘电极46。通过以上工序,形成图14所示的半导体发光元件110。

[0133]

在本实施方式的半导体发光元件110中,也能够起到与上述实施方式相同的效果。另外,根据本实施方式,通过p侧接触电极130具有tin层130c,能够提高p侧接触电极130相对于第1保护层138的密合性。

[0134]

以上,基于实施方式说明了本发明。本领域技术人员应当理解,本发明不限定于上述实施方式,可以进行各种设计变更,可以有各种变形例,并且这样的变形例也包含在本发明的范围内。

[0135]

在其他实施方式中,也可以适当替换上述实施方式的半导体发光元件10、110的构成。例如,图1的半导体发光元件10也可以具备图14所示的n侧电流扩散层136来替代图1所示的n侧电流扩散层36。同样,图14的半导体发光元件110也可以具备图1所示的n侧电流扩散层36来替代图14所示的n侧电流扩散层136。

[0136]

在一实施方式中,第1电流扩散层48及第2电流扩散层50、150的至少一者,遍及比形成有n侧接触电极34的第6区域w6大的区域而设置。例如,如图14所示,相对于第1电流扩散层48设于比第6区域w6大的区域,第2电流扩散层50、150设于与第6区域w6一致的区域或设于比第6区域w6窄的区域。此外,也可以是,相对于第1电流扩散层48设于与第6区域w6一致的区域或比第6区域w6窄的区域,第2电流扩散层50、150设于比第6区域w6大的区域。在这些情况下,形成有第1电流扩散层48的第7区域w7可以与形成有第2电流扩散层50、150的第8区域w8或第9区域w9一致,也可以比第8区域w8或第9区域w9窄,也可以比第8区域w8或第9区域w9大。

[0137]

在上述实施方式中,表示了n侧电流扩散层36、136包含第1电流扩散层48及第2电流扩散层50、150的情况。在其他实施方式中,n侧电流扩散层36、136也可以仅由1个电流扩散层构成。即,n侧电流扩散层36、136也可以只具备1个第1tin层、金属层及第2tin层的层叠构造。此外,n侧电流扩散层36、136也可以具备3个以上的第1tin层、金属层及第2tin层的层叠构造。另外,p侧电流扩散层32、132也可以具备2个以上的第1tin层、金属层及第2tin层的层叠构造。

[0138]

[附图标记说明]

[0139]

10

…

半导体发光元件,24

…

n型半导体层,24a

…

第1上表面,24b

…

第2上表面

…

,26

…

活性层,28

…

p型半导体层,28a

…

上表面,30

…

p侧接触电极,30a

…

上表面,30p

…

p侧接触电极,32

…

p侧电流扩散层,32a

…

第1tin层,32b

…

金属层,32c

…

第2tin层,32d

…

上表面,34

…

n侧接触电极,34a

…

金属层,34b

…

tin层,36

…

n侧电流扩散层,44

…

p侧焊盘电极,46

…

n侧焊盘电极,48

…

第1电流扩散层,48a

…

第1tin层,48b

…

金属层,48c

…

第2tin层,48d

…

上表面,50

…

第2电流扩散层,50a

…

第1tin层,50b

…

金属层,50c

…

第2tin层,50d

…

上表面。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。