1.本说明书中公开的发明涉及一种线性电源电路及源极跟随器电路。

背景技术:

2.诸如ldo(低压差)型的线性电源电路被用作各种装置的电源。

3.与上文所述相关的已知技术的一例可见于例如下面确定的专利文献1。

4.源极跟随器电路例如被用作阻抗转换电路。

5.与上文所述相关的已知技术的一例可见于例如下面确定的专利文献2。

6.现有技术文献

7.专利文献

8.专利文献1:日本特开第2003

‑

84843号公报

9.专利文献2:日本特开第2008

‑

258849号公报

技术实现要素:

10.发明所解决的技术问题

11.线性电源电路能够快速响应为佳,以便即使在负载突然变化的情况下也能保持输出电压的变化较小。此外,线性电源电路即使在未设有输出电容器或输出电容器的电容较低的情况下也能够实现输出电压的稳定性为佳。

12.包括nmos晶体管的源极跟随器电路在所述输入电压下降时呈现出nmos晶体管的源极电压的较大的下降量(即,输入电压与nmos晶体管的源极电压之间的较大的差)。

13.解决问题的技术方案

14.根据本说明书中公开的第一方面,提供一种线性电源电路,包括:输出晶体管,其设置在被施加输入电压的输入端与被施加输出电压的输出端之间;以及驱动器,其被配置为根据基于所述输出电压的电压与基准电压之间的差来驱动所述输出晶体管。所述驱动器包括:差分放大器,其被配置为输出与所述基于所述输出电压的电压和所述基准电压之间的差相应的电压;第一电容器,其一端被施加所述差分放大器的输出,另一端被施加地电位;转换器,其被配置为将基于所述差分放大器的输出的电压转换为电流并输出所述电流;以及电流放大器,其被配置为对所述转换器的输出进行电流放大。所述差分放大器及所述转换器的电源电压是取决于所述输出电压的电压。所述线性电源电路还包括:源极跟随器电路或发射极跟随器电路,其包括第一端子连接到所述输入端并且第二端子连接到所述输出端的第一晶体管;第二晶体管,其与所述输出晶体管串联连接,并且与所述第一晶体管一起构成电流镜电路;以及第二电容器,其连接到所述电流放大器或所述第一晶体管的控制端子(第一配置)。

15.根据本说明书中公开的第二方面,提供一种线性电源电路,包括:输出晶体管,其设置在被施加输入电压的输入端与被施加输出电压的输出端之间;以及驱动器,其被配置为根据基于所述输出电压的电压与基准电压之间的差来驱动所述输出晶体管。所述驱动器

包括:差分放大器,其被配置为输出与所述基于所述输出电压的电压与所述基准电压之间的差相应的电压;第一电容器,其一端被施加所述差分放大器的输出,另一端被施加基于所述输出电压的电压;转换器,其被配置为将基于所述差分放大器的输出的电压转换为电流并输出所述电流;以及电流放大器,其被配置为对所述转换器的输出进行电流放大。所述差分放大器的电源电压是第一恒定电压并且所述电流放大器的电源电压是第二恒定电压,或者所述差分放大器的电源电压以及所述电流放大器的电源电压是所述输入电压。所述线性电源电路还包括:源极跟随器电路或发射极跟随器电路,其包括第一端子连接到所述输入端并且第二端子连接到所述输出端的第一晶体管;第二晶体管,其与所述输出晶体管串联连接,并且与所述第一晶体管一起构成电流镜电路;以及第二电容器,其连接到所述电流放大器或所述第一晶体管的控制端子(第二配置)。

16.在上述第一配置或第二配置的线性电源电路中,所述第二电容器可以连接到所述第一晶体管的控制端子(第三配置)。

17.在上述第三配置的线性电源电路中,所述线性电源电路可以包括所述源极跟随器电路。所述线性电源电路还可以包括设置在所述第一晶体管与第二晶体管之间的电荷泵电路。所述电荷泵电路可以包括所述第二电容器,并且可以被配置为对所述第二电容器充电高于所述输入电压的电压,并将所述第二电容器的充电电压施加于所述第一晶体管的控制端子(第四配置)。

18.在上述第四配置的线性电源电路中,所述电荷泵电路可以被配置为基于时钟信号进行动作,该时钟信号的时钟频率取决于从所述输出端流向负载的拉电流(soure current)(第五配置)。

19.在上述第四配置的线性电源电路中,所述电荷泵电路可以被配置为基于时钟信号进行动作,该时钟信号的时钟频率取决于从所述输出端流向负载的拉电流和从所述负载流向所述输出端的灌电流(sink current)的标量和(第六配置)。

20.在上述第四配置至第六配置中任一配置的线性电源电路中,所述线性电源电路可以被配置为在所述电荷泵电路动作的第一模式与所述电荷泵电路不动作且所述第一晶体管的控制端子和所述第二晶体管的控制端子处于等电位的第二模式之间可切换(第七配置)。

21.根据本说明书中公开的第三方面,提供一种线性电源电路包括:输出晶体管,其设置在被施加输入电压的输入端与被施加输出电压的输出端之间;以及驱动器,其被配置为根据基于所述输出电压的电压与基准电压之间的差来驱动所述输出晶体管。所述驱动器包括:差分放大器,其被配置为输出与所述基于所述输出电压的电压与所述基准电压之间的差相应的电压;第一电容器,其一端被施加所述差分放大器的输出,并且另一端被施加地电位;转换器,其被配置为将基于所述差分放大器的输出的电压转换为电流并输出所述电流;以及电流放大器,其被配置为对所述转换器的输出进行电流放大。所述差分放大器及所述转换器的电源电压是取决于所述输出电压的电压。所述输出晶体管是pmosfet。所述线性电源电路还包括:第二电容器,其设置在所述输出晶体管的栅极与漏极之间(第八配置)。

22.根据本说明书中公开的第四方面,提供一种线性电源电路,包括:输出晶体管,其设置在被施加输入电压的输入端与被施加输出电压的输出端之间;以及驱动器,其被配置为根据基于所述输出电压的电压与基准电压之间的差来驱动所述输出晶体管。所述驱动器

包括:差分放大器,其被配置为输出与所述基于所述输出电压的电压与所述基准电压之间的差相应的电压;第一电容器,其一端被施加所述差分放大器的输出,并且另一端被施加基于所述输出电压的电压;转换器,其被配置为将基于所述差分放大器的输出的电压转换为电流并输出所述电流;以及电流放大器,其被配置为对所述转换器的输出进行电流放大。所述差分放大器的电源电压是第一恒定电压并且所述电流放大器的电源电压是第二恒定电压,或者所述差分放大器的电源电压以及所述电流放大器的电源电压是所述输入电压。所述输出晶体管是pmosfet。所述线性电源电路还包括:第二电容器,其设置在所述输出晶体管的栅极与漏极之间(第九配置)。

23.上述第八配置或第九配置的线性电源电路还可以包括:整流器,其设置在所述输出晶体管的栅极与漏极之间。所述整流器可以被配置为:阻止趋于从所述输出晶体管的栅极流向漏极的电流,并且使趋于从所述输出晶体管的漏极流向栅极的电流通过(第十配置)。

24.在上述第十配置的线性电源电路中,所述整流器可以是缓冲放大器(第十一配置)。

25.在上述第一配置至第十一配置中任一配置的线性电源电路中,可以没有电容器连接到所述输出端(第十二配置)。

26.在上述第一配置至第十一配置中任一配置的线性电源电路中,电容小于100nf的电容器可以连接到所述输出端(第十三配置)。

27.根据本说明书中公开的另一方面,提供一种半导体集成电路器件,包括:多个外部引脚;以及作为内部电源的上述第一配置至第十三配置中任一配置的线性电源电路。所述输入端连接到所述多个外部引脚的一个或多个,并且所述输出端不连接到所述多个外部引脚中的任何一个(第十四配置)。

28.根据本说明书中公开的另一方面,提供一种源极跟随器电路,包括:输入端,其被施加输入电压;输出端;电荷泵电路,其配置为被输入所述输入电压或低于所述输入电压的电压;以及nmosfet,其漏极连接到所述输入端,源极连接到所述输出端,并且栅极被输入所述电荷泵电路的输出电压(第十五配置)。

29.在上述第十五配置的源极跟随器电路中,所述电荷泵电路可以被配置为:当施加于所述输出端的所述源极跟随器电路的输出电压低于预定值时动作,并且当施加于所述输出端的所述源极跟随器电路的输出电压高于所述预定值时不动作(第十六配置)。

30.在上述第十六配置的源极跟随器电路中,所述电荷泵电路可以被配置为基于从时钟信号生成电路输出的时钟信号进行动作。所述时钟信号生成电路可以被配置为:当施加于所述输出端的所述源极跟随器电路的输出电压低于所述预定值时输出所述时钟信号,并且当施加于所述输出端的所述源极跟随器电路的输出电压高于所述预定值时不输出所述时钟信号(第十七配置)。

31.在上述第十五配置的源极跟随器电路中,所述电荷泵电路可以被配置为基于时钟信号进行动作,该时钟信号的时钟频率取决于从所述输出端流向负载的拉电流(第十八配置)。

32.在上述第十五配置的源极跟随器电路中,所述电荷泵电路可以被配置为基于时钟信号进行动作,该时钟信号的时钟频率取决于从所述输出端流向负载的拉电流和从所述负

载流向所述输出端的灌电流的标量和(第十九配置)。

33.根据本说明书中公开的另一方面,提供一种电源电路,包括:上述第十五配置至第十九配置中任一配置的源极跟随器电路(第二十配置)。

34.根据本说明书中公开的另一方面,提供一种车辆,包括:上述第一配置至第九配置中任一配置的线性电源电路,或上述第十配置的半导体集成电路器件,或上述第十二配置的电源电路(第二十一配置)。

35.发明的效果

36.根据本说明书中公开的发明的一方面,可以提供一种线性电源电路,其能够快速响应并且即使在没有输出电容器或输出电容器的电容较低的情况下也能够实现输出电压的稳定性。

37.根据本说明书中公开的发明的另一方面,可以提供一种源极跟随器电路,其能够在输入电压下降时减少nmos晶体管的源极电压的下降量(输入电压与nmos晶体管的源极电压之间的差)。

附图说明

38.图1是示出本发明人开发的线性电源电路的配置的图。

39.图2是示出图1所示的线性电源电路的输出特性的时序图。

40.图3是示出图1所示的线性电源电路、输出电容器及负载的传递函数的增益特性的图。

41.图4是示出图1所示的线性电源电路、输出电容器及负载的传递函数的增益特性的图。

42.图5是示出根据第一实施方式的线性电源电路的配置的图。

43.图6是示出电流放大器的一配置例的图。

44.图7a是示出根据第一实施方式的变形例的图。

45.图7b是示出根据第一实施方式的另一变形例的图。

46.图7c是示出根据第一实施方式的又一变形例的图。

47.图8a是示出根据第二实施方式的线性电源电路的配置的图。

48.图8b是示出电流放大器的另一配置例的图。

49.图9a是示出图1所示的线性电源电路的输入输出特性的图。

50.图9b是示出线性电源电路的理想的输入输出特性的图。

51.图10是示出根据第三实施方式及第四实施方式的线性电源电路的配置的图。

52.图11是示出根据第三实施方式中使用的时钟信号生成电路的一配置例的图。

53.图12是示出第四实施方式中使用的时钟信号生成电路的一配置例的图。

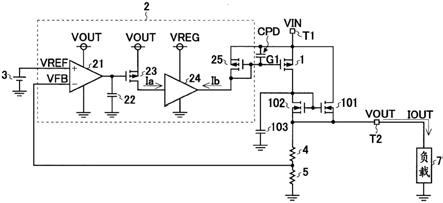

54.图13是示出根据第五实施方式的线性电源电路的配置的图。

55.图14是示出根据第六实施方式的线性电源电路的配置的图。

56.图15a是示出根据第七实施方式的线性电源电路的配置的图。

57.图15b是示出根据第七实施方式的线性电源电路的具体例的图。

58.图16是示出根据第八实施方式的线性电源电路的配置的图。

59.图17是示出根据第九实施方式的线性电源电路的配置的图。

60.图18是半导体集成电路器件的外观图。

61.图19是车辆的外观图。

具体实施方式

62.<1.快速响应的线性电源电路>

63.图1是示出作为能够快速响应的线性电源电路由本发明人开发的线性电源电路的配置的图。图1所示的线性电源电路包括输入端t1、输出端t2、输出晶体管1、驱动器2、基准电压生成器3、以及电阻器4和5。

64.输出电容器6和负载7外部连接到图1所示的线性电源电路。具体地,输出电容器6和负载7彼此并联地外部连接到输出端t2。图1所示的线性电源电路对输入电压vin进行降压以生成输出电压vout,并将输出电压vout供给至负载7。

65.输出晶体管1设置在被施加输入电压vin的输入端tl和被施加输出电压vout的输出端t2之间。

66.驱动器2驱动输出晶体管1。具体地,驱动器2将栅极信号gl供给至输出晶体管1的栅极,由此驱动输出晶体管1。输出晶体管1的导通率(反过来说,导通电阻值)由栅极信号g1控制。在图1所示的配置中,用作输出晶体管1的是pmosfet(p沟道mosfet)。从而,栅极信号g1越低,输出晶体管1的导通率越高,因此输出电压vout越高。反过来说,栅极信号g1越高,输出晶体管1的导通率越低,因此输出电压vout越低。作为输出晶体管1,代替pmosfet地,可以使用pnp双极晶体管。

67.基准电压生成器3生成基准电压vref。电阻器4和5生成反馈电压vfb,该反馈电压vfb是输出电压vout的分压。

68.驱动器2的非反相输入端( )被施加基准电压vref,驱动器2的反相输入端(

‑

)被施加反馈电压vfb。驱动器2基于反馈电压vfb与基准电压vref之间的差值δv(=vref

‑

vfb)来驱动输出晶体管1。差δv增大时,驱动器2增加栅极信号g1,差δv减小时,驱动器2减少栅极信号g1。

69.驱动器2包括差分放大器21、电容器22、pmosfet23、电流放大器24、以及pmosfet25。

70.差分放大器21输出与反馈电压vfb与基准电压vref之间的差相应的电压。差分放大器21的电源电压是输出电压vout。即,差分放大器21由输出电压vout与地电位之间的电压驱动。作为差分放大器21的电源电压,代替输出电压vout,可以使用取决于输出电压vout的低于输出电压vout的电压。

71.差分放大器21的耐受电压低于电流放大器24的耐受电压。差分放大器21的增益低于电流放大器24的增益。这有助于保持差分放大器21小型紧凑。

72.电容器22的一端被施加差分放大器21的输出,电容器22的另一端被施加地电位。

73.pmosfet 23的源极被施加输出电压vout,pmosfet 23的栅极被施加基于差分放大器21的输出的电压(即,差分放大器21与电容器22之间的连接节点处的电压)。pmosfet 23将基于差分放大器21的输出的电压转换为电流并从其漏极输出电流。差分放大器21与电容器22之间的连接节点在高频带用作负接地,这有助于实现驱动器2中的快速响应。

74.电流放大器24对从pmosfet 23的漏极输出的电流ia进行电流放大。电流放大器24

的电源电压是恒定电压vreg。即,电流放大器24由恒定电压vreg与地电位之间的电压驱动。

75.pmosfet 25与输出晶体管1一起构成电流镜电路。pmosfet 25将从电流放大器24输出的电流ib转换为电压并将该电压供给至输出晶体管1的栅极。

76.图2是示出图1所示的线性电源电路输出特性的时序图。图2是当假设输出电压vout的设定值等于vs且输出电容器6具有预定值,负载7从第一状态切换到第二状态后又返回到第一状态时得到的时序图。第一状态是输出电流iout的理论值等于i1的轻载状态,第二状态是输出电流iout的理论值等于i2(>i1)的重载状态。

77.图1所示的线性电源电路能够快速响应,这有助于减少过冲os。

78.图3是示出图1所示的线性电源电路、输出电容器6及负载7的传递函数的增益特性的图。第一极点频率fpl表示由于输出电容器6和负载7而出现的极点第一极点的频率。第二极点频率fp2表示由于形成在输出晶体管1的源极与栅极之间的寄生电容cpd而出现的第二极点的频率。

79.对于图3所示的传递函数,零交叉频率fzc较低,在增益为负的区域出现第二极点频率fp2。这使得相位补偿变得容易。

80.相比之下,若去除输出电容器6,为增益的调整作出贡献的第一极点频率fpl消失;因此零交叉频率fzc移至高区。结果,图1所示的线性电源电路、输出电容器6及负载7的传递函数的增益特性如图4所示。在图4中,图3所示的增益特性用粗虚线表示,以作比较。

81.对于图4所示的增益特性,由于零交叉频率fzc移至高区,在增益为正的区域中出现多个极点。这使得相位补偿变得困难。

82.<2.第一实施方式>

83.图5是示出本发明人为了解决图1所示的线性电源电路的问题而开发的第一实施方式的线性电源电路的图。在图5中,对与图1中相对应的部分用相同的附图标记标识,并且不再重复详细描述。

84.图5所示的线性电源电路与图1所示的线性电源电路的不同之处在于,包括nmosfet 101、102以及电容器103。代替nmosfet 101、102,可以使用npn双极晶体管。虽然对nmosfet101的耐受电压不作特殊限制,但nmosfet 101可以给定10v以上的耐受电压,以便可以应对例如超过5v的输入电压vin。

85.在图5所示的线性电源电路中,如同图1所示的线性电源电路,差分放大器21与电容器22之间的连接节点在高频带用作负接地。这有助于实现驱动器2中的快速响应。

86.差分放大器21和pmosfet 23的耐受电压低于电流放大器24的耐受电压。差分放大器21的增益低于电流放大器24的增益。这有助于保持差分放大器21和pmosfet 23小型紧凑。

87.pmosfet 23的耐受电压低于电流放大器24的耐受电压。这有助于保持pmosfet 23小型紧凑。

88.图6是示出电流放大器24的一配置例的图。图6所示的配置例的电流放大器24包括灌电流型电流镜电路cm_1、cm_2、...cm_n以及拉电流型电流镜电路cm_3、...cm_n

‑

1(其中cm_n

‑

1未示于图6中)。在一端处的灌电流型电流镜电路cm_1和产生恒定电流i1的电流源cs1与另一端处的灌电流型电流镜电路cm_n之间,从电流放大器24的输入向输出,灌电流型电流镜电路和拉电流型电流镜电路交替排列。为了使在每个电流镜电路中出现的极点尽可

能远离低频带,优选每个电流镜电路被给定的镜像比(输出侧晶体管的尺寸与输入侧晶体管的尺寸的比例)为5以下,更优选地,为3以下。然而,应注意的是,每个电流镜电路的镜像比越小,电流放大器24的电路面积越大。因此,每个电流镜电路的镜像比可以考虑改善的频率特性与小型紧凑性两者之间的权衡而定。

89.返回至图5,对nmosfet 101、102及电容器103进行描述。nmosfet 101的漏极连接到输入端t1。nmosfet 101的源极连接到输出端t2。因此,nmosfet 101形成源极跟随器电路。nmosfet 102的漏极、nmosfet 101、102的各自的栅极、以及电容器103的一端连接到输出晶体管1的漏极。nmosfet 102的源极连接到输出端t2。电容器103的另一端被施加地电位。

90.在图5所示的线性电源电路中,由于形成源极跟随器电路的nmosfet 101处于末级,因而输出阻抗较低。电容器103连接到nmosfet 101的栅极,并且通过由nmosfet 101和102构成的电流镜电路驱动nmosfet101。因此,可以在保持驱动器2中的快速响应性能的同时,产生与图3中的第一极点频率fp1的频率相当的频率的第一极点。

91.图5所示的线性电源电路能够快速响应,尽管没有外部连接的输出电容器6(见图1),也能够实现输出电压vout的稳定性。

92.此外,在图5所示的线性电源电路中,与负载7的阻抗相比,可以使nmosfet 102的跨导的倒数(1/gm)足够高,这使得可以给予电容器103小到其可以内置于半导体集成电路器件中的电容(例如,小于20pf)。

93.此外,在图5所示的线性电源电路中,nmosfet 101的跨导的倒数(1/gm)和nmosfet 102的跨导的倒数(1/gm)与负载7的阻抗成比例,如同图1所示的线性电源电路,这有助于维持零交叉频率根据负载7的阻抗上升的特性。通常,考虑瞬态负载(电功率消耗呈矩形波的负载),当线性电源电路的输出增加时,输出电压呈现相应大的下降量。然而,在高零交叉频率下,实现对瞬态负载的快速响应,这有助于减少瞬态负载的输出电压的下降量。对于图5所示的线性电源电路,如上所述,负载越重,零交叉频率越高。从而,对于图5所示的线性电源电路,与一般的线性电源电路相比,可以以较小的输出电压的下降量来应对负载的瞬时增加。在线性电源电路中,提高零交叉频率需要更高的电路电流。然而,当瞬态负载较轻时,即使零交叉频率较低,输出电压的下降量也较小。因此,不需要通过消耗额外的电路电流来保持高零交叉频率。对于图5所示的线性电源电路,如上所述,轻负载使零交叉频率低。因此,对于图5所示的线性电源电路,与一般的线性电源电路相比,可以抑制无负载时的消耗电流(暗电流)。

94.电容器103可以连接到除nmosfet 101、102的栅极外的任何地方;例如,如图7a至图7c所示,可以取而代之地连接到电流放大器24内的灌电流型电流镜电路。将电容器103连接到nmosfet 101的栅极,产生最佳的快速响应性能。另一方面,电容器103连接得越靠近pmosfet 23(见图5),可以使电容器103的电容越小。

95.<3.第二实施方式>

96.图8a是示出根据第二实施方式的线性电源电路的配置的图。在图8a中,对与图5中相对应的部分用相同的附图标记标识,并且不再重复详细描述。

97.在该实施方式中,驱动器2包括差分放大器21’、电容器22’、nmosfet 23’、电流放大器24、以及pmosfet 25。

98.差分放大器21’输出与反馈电压vfb与基准电压vref之间的差相应的电压。差分放大器21’的电源电压是第一恒定电压vreg1。即,差分放大器21’由第一恒定电压vreg1与地电位之间的电压驱动。

99.差分放大器21’及nmosfet 23’的耐受电压低于电流放大器24的耐受电压。差分放大器21’的增益低于电流放大器24的增益。这有助于保持差分放大器21’及nmosfet 23’小型紧凑。

100.电容器22’的一端被施加差分放大器21’的输出,电容器22’的另一端被施加输出电压vout。代替输出电压vout,可以将取决于输出电压vout的电压施加于电容器22的另一端。

101.nmosfet 23’的源极被施加地电位,nmosfet 23’的栅极被施加基于差分放大器21’的输出的电压(即,差分放大器21’与电容器22’之间的连接节点处的电压)。nmosfet 23’将基于差分放大器21’的输出的电压转换为电流并从其漏极输出该电流。差分放大器21’与电容器22’之间的连接节点在高频带用作正(vout)接地,这有助于实现驱动器2中的快速响应。

102.电流放大器24对从nmosfet 23’的漏极输出的电流ia进行电流放大。电流放大器24的电源电压是第二恒定电压vreg2。即,电流放大器24由从第二恒定电压vreg2与地电位之间的电压驱动。第一恒定电压vreg1和第二恒定电压vreg2可以具有相等的值,或者可以具有不同的值。在该配置例中,电流ia从电流放大器24流向nmosfet 23’,因此可以将电流放大器24提供为例如如图8b所示的电路配置。

103.图8a所示的根据该实施方式的线性电源电路提供与图5所示的第一实施方式中的线性电源电路类似的有益效果。此外,根据图8a所示的该实施方式的线性电源电路确保差分放大器21’即使在输出电压vout的设定值较低的情况下也动作。在将低电压用作输入电压vin的情况下,代替第一恒定电压vreg1,可以将输入电压vin用作差分放大器21’的电源电压;代替第二恒定电压vreg2,可以将输入电压vin用作电流放大器24的电源电压。

104.<4.第三实施方式>

105.对于图5和8所示的线性电源电路,当如图9a所示输入电压vin降至接近输出电压vout的值时,输出电压vout降至比输入电压vin低nmosfet 101的阈值电压vth。然而,ldo电源电路中期望的理想的输入输出特性如图9b所示,当输入电压vin降至接近输出电压vout的值时,输出电压vout几乎不会降至低于输入电压vin。

106.根据第三实施方式的线性电源电路是提供接近如图9b所示理想的特性的输入输出特性的电源电路。图10是示出根据第三实施方式的线性电源电路的配置的图。在图10中,与图5中相对应的部分用相同的附图标记标识,并且不再重复详细描述。

107.图10所示的线性电源电路与图5所示的线性电源电路的不同之处在于,包括电荷泵电路104和时钟信号生成电路105。在图10所示的线性电源电路中,输入端t1、输出端t2、nmosfet101以及电荷泵电路104构成源极跟随器电路。

108.电荷泵电路104设置在nmosfet 102与101之间。电荷泵电路104包括开关s1至s4以及电容器cc。开关s1和s2由时钟信号ck接通和断开。开关s3和s4由反向时钟信号接通和断开。由于电荷泵电路104基于时钟信号ck和反向时钟信号动作,作为nmosfet 101的源

极电压和nmosfet 102的栅源电压之和的电压被施加于nmosfet 101的栅极。

109.如上所述,在图10所示的线性电源电路中,电荷泵电路104驱动nmosfet 101。从而,在图10所示的线性电源电路中,可以使nmosfet 101的栅极电压高于输入电压vin。因此,可以减小输入电压vin下降时的输出电压vout的下降量(输入电压vin与输出电压vout之间的差)。

110.如上所述,电荷泵电路104驱动nmosfet 101。从而,由输入端t1、输出端t2、nmosfet 101以及电荷泵电路104构成的源极跟随器电路可以使nmosfet 101的栅极电压高于输入电压vin。因此,该源极跟随器电路可以减小输入电压vin下降时的晶体管q3的源极电压的下降量(输入电压vin与晶体管q3的源极电压之间的差)。对于图10所示的线性电源电路,由于其包括上述源极跟随器电路,因而可以减小输入电压vin下降时的输出电压vout的下降量(输入电压vin与输出电压vout之间的差)。

111.电荷泵电路104可以线性近似于rc电路,因此由于电荷泵电路104所出现的极点的频率会随时钟信号ck的频率而变化。从而,通过适当地设置时钟信号ck的频率,可以在图10所示的线性电源电路中实现类似于图5所示的线性电源电路的快速响应特性。

112.从图5所示的线性电源电路到图10所示的线性电源电路的变更同样适用于图9a所示的线性电源电路。

113.下面对时钟信号生成电路105进行描述。图11是示出时钟信号生成电路105的一配置例的图。图11所示的配置例的时钟信号生成电路105包括电容器105a、基准电压源105b、比较器105c以及放电晶体管105d。

114.电容器105a由取决于从电流放大器24输出的电流ib的充电电流充电。电流ib取决于输出电流iout,因此电容器105a的充电速度取决于输出电流iout。比较器105c将电容器105a的充电电压与从基准电压源105b输出的基准电压的比较结果作为时钟信号ck输出。当时钟信号ck变为高电平时,放电晶体管105d导通,电容器105a被放电。在图11所示的配置例的时钟信号生成电路105中,还生成作为时钟信号ck的反转信号的反向时钟信号

115.在图11所示的配置例的时钟信号生成电路105中,输出电流iout越高,时钟信号ck的时钟频率越高。因此,可以在无负载情况下(当负载7的阻抗可以被视为无限高时)抑制电荷泵电路104的功耗,而在响应负载时实现电荷泵电路104中的快速动作。

116.代替图11所示的配置例的时钟信号生成电路105,也可以使用如下(1)至(4)所述的时钟信号生成电路:

117.(1)时钟信号生成电路,其将输出电压vout与基准电压进行比较,当输出电压vout低于基准电压时,生成时钟信号ck和向时钟信号

118.(2)时钟信号生成电路,其将从输入电压vin减去输出电压vout所得的值与基准电压进行比较,当从输入电压vin减去输出电压vout所得的值小于基准电压时,生成时钟信号ck和反向时钟信号

119.(3)时钟信号生成电路,其将输出电压vout与输入电压vin之比与基准电压进行比较,当输出电压vout与输入电压vin之比大于基准电压时,生成时钟信号ck和反向时钟信号

120.(4)时钟信号生成电路,其在接收到指示生成时钟信号的信号(例如,在车辆启动

时从车载微型计算机发出的信号)时,生成时钟信号ck和反向时钟信号

121.当时钟信号生成电路不生成时钟信号ck和反向时钟信号时,开关s1和s3可以例如通过高电平信号接通。这可以通过设置例如在时钟信号生成电路不生成时钟信号ck和反向时钟信号时输出高电平信号的电压源、向开关s1供给高电平信号和时钟信号ck的or(逻辑和)的or(或)门、向开关s3供给高电平信号和反向时钟信号的or的or(或)门、以及附加开关来实现。附加开关设置在nmosfet 102的源极和开关s2的一端的连接节点与地电位之间。附加开关在待后述的第一模式下接通,并且在待后述的第二模式下断开。由此,可以在电荷泵电路动作的第一模式和电荷泵电路不动作且nmosfet 101和nmosfet 102的栅极处于等电位的第二模式之间切换。第二模式产生没有开关纹波的输出电压vout。

122.<5.第四实施方式>

123.图11所示的配置例的时钟信号生成电路105,即第三实施方式中使用的时钟信号生成电路,以输出电流iout是经由输出端t2流向负载7的拉电流为前提。从而,若外部的漏电流或输出电流iout经由输出端t2流入,则图11所示的配置例的时钟信号生成电路105不动作,并且输出电压vout上升。

124.根据第四实施方式的线性电源电路是无论输出电流iout是拉电流还是灌电流使时钟信号生成电路105和电荷泵电路104都能够动作并且防止输出电压vout上升的电源电路。图12示出在根据第四实施方式的线性电源电路中使用的时钟信号生成电路105的一配置例。根据第四实施方式的线性电源电路的整体配置与根据第三实施方式的线性电源电路的整体配置类似,并且如图10所示。

125.与图11所示的配置例的时钟信号生成电路105相比,图12所示的配置例的时钟信号生成电路105还额外包括电流镜电路105e。电流镜电路105e从电流ia’生成电流i2。电流ia’是电流ia的镜像电流(见图10)。即,根据第四实施方式的线性电源电路包括从电流ia生成电流ia’的电流镜电路(未示出)。

126.在图12中,电流i1是取决于作为拉电流的输出电流iout的电流。在图12中,电流i2是取决于作为灌电流的输出电流iout的电流。电容器105a由取决于电流i1和i2的标量和的充电电流,即取决于作为拉电流的输出电流iout和作为灌电流的输出电流iout的标量和的充电电流充电。因此,图12所示的配置例的时钟信号生成电路105与输出电流iout是拉电流还是灌电流无关地动作。

127.作为拉电流的输出电流iout和作为灌电流的输出电流iout不会同时出现,因此作为拉电流的输出电流iout和作为灌电流的输出电流iout的标量和的瞬时值是作为拉电流的输出电流iout或作为灌电流的输出电流iout。

128.<6.第五实施方式>

129.如同根据第三、第四实施方式的线性电源电路,根据第五实施方式的线性电源电路是呈现出接近如图9b所示的理想的特性的输入输出特性的电源电路。图13是示出根据第五实施方式的线性电源电路的配置的图。在图13中,对与图1中相对应的部分用相同的附图标记标识,并且不再重复详细描述。

130.图13所示的线性电源电路与图5所示的线性电源电路的不同之处在于,包括电容器106,而不是nmosfet 101、102以及电容器103。

131.电容器106设置在作为pmosfet的输出晶体管1的栅极与漏极之间。即,电容器106的一端连接到输出晶体管1的栅极,电容器106的另一端连接到输出晶体管1的漏极。

132.就图13所示的线性电源电路而言,不同于图5和图8a所示的线性电源电路,由于省略了nmosfet 101、102,因而即使在输入电压vin下降至接近输出电压vout的值时,输出电压vout也不会下降至比输入电压vin低nmosfet 101的阈值电压vth。

133.此外,当负载7急剧变化时,即,当图13所示的线性电源电路在高频动作时,电容器106短路。因此,当输出电压vout(输出晶体管1的漏极电压)相对于负载7急剧下降时,输出晶体管1的栅源电压变得高于输出晶体管1的阈值电压,并且,无论驱动器2的输出如何,输出晶体管1导通。因此,图13所示的线性电源电路能够快速响应。

134.此外,图13所示的线性电源电路提供类似于图5和图8a所示的线性电源电路的频率特性。即,对于图13所示的线性电源电路,容易进行相位补偿。

135.此外,不同于图10所示的线性电源电路,图13所示的线性电源电路不包括电荷泵电路,因此原则上不会产生来自电荷泵电路的开关噪声。

136.<7.第六实施方式>

137.如同根据第三至第五实施方式的线性电源电路,根据第六实施方式的线性电源电路是提供接近如图9b所示的理想的特性的输入输出特性的电源电路。图14是示出根据第六实施方式的线性电源电路的配置的图。在图14中,对与图8a中相对应的部分用相同的附图标记标识,并且不再重复详细描述。

138.图14所示的线性电源电路与图8a所示的线性电源电路的不同之处在于,包括电容器106,而不是nmosfet 101、102以及电容器103。

139.电容器106设置在作为pmosfet的输出晶体管1的栅极与漏极之间。即,电容器106的一端连接到输出晶体管1的栅极,电容器106的另一端连接到输出晶体管1的漏极。

140.图14所示的根据本实施方式的线性电源电路提供类似于图13所示的根据第五实施方式的线性电源电路的优点。此外,图14所示的线性电源电路确保即使在输出电压vout的设定值较低的情况下差分放大器21’也动作。在将低电压用作输入电压vin的情况下,代替第一恒定电压vreg1,可以将输入电压vin用作差分放大器21’的电源电压,并且,代替第二恒定电压vreg2,可以将输入电压vin用作电流放大器24的电源电压。

141.<8.第七实施方式>

142.图15a是示出根据第七实施方式的线性电源电路的配置的图。在图15a中,对与图13中相对应的部分用相同的附图标记标识,并且不再重复详细描述。

143.图15a所示的线性电源电路与图13所示的线性电源电路的不同之处在于,包括缓冲放大器107。

144.缓冲放大器107的输入端连接到电容器106,缓冲放大器107的输出端连接到输出晶体管1的栅极。

145.缓冲放大器107使趋于从输出晶体管1的漏极流向栅极的电流通过。因此,图15a所示的根据该实施方式的线性电源电路提供类似于图13所示的根据第五实施方式的线性电源电路的有益效果。

146.缓冲放大器107阻止趋于从输出晶体管1的栅极流向漏极的电流。因此,对于根据图15a所示的该实施方式的线性电源电路,当输入电压vin发生变动时,可以防止输入电压

vin的变动经由pmosfet 25和电容器106影响输出电压vout。

147.图15b是示出根据第七实施方式的线性电源电路的具体例的图。在图15b所示的线性电源电路中,nmosfet 107a和恒定电流源107b构成缓冲放大器107。nmosfet 107a的栅极被施加预定的偏置电压vbias。即,nmosfet 107a栅极接地。

148.即使在随输入电压vin发生变动而nmosfet 107a的漏极电压发生变动时,nmosfet 107a的漏极电流也不会发生变动。另一方面,当随输出电压vout发生变动而nmosfet 107a的源极电压发生变动时,nmosfet 107a的栅源电压发生变动,因此nmosfet 107a的漏极电流发生变动。

149.缓冲放大器107是整流器的一示例,该整流器设置在输出晶体管1的栅极与漏极之间,用来阻止趋于从输出晶体管1的栅极流向漏极的电流,而使趋于从输出晶体管1的漏极流向栅极的电流通过。从而,可以使用除缓冲放大器107外的任何整流器来代替缓冲放大器107。然而应注意的是,这样的整流器需要具有不会有损于线性电源电路的快速响应的程度的快速响应性。

150.<9.第八实施方式>

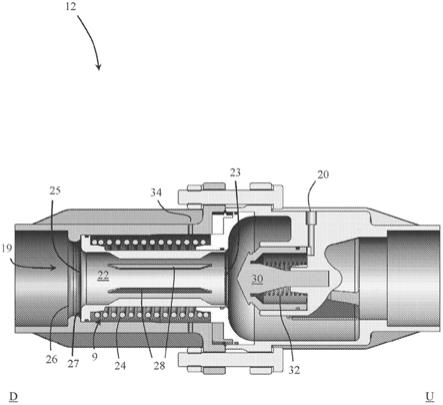

151.图16是示出根据第八实施方式的线性电源电路的配置的图。图16所示的线性电源电路包括输入端tm1、输出端tm2、晶体管q1至q3、电荷泵电路cp1、基准电压生成器ref1、差分放大器amp1、电容器c1、电阻器r1和r2、比较器cmp1、以及时钟信号生成电路clk1。电荷泵电路cp1包括开关sw1至sw4以及电容器c2。输入端tm1、输出端tm2、晶体管q3以及电荷泵电路cp1构成源极跟随器电路。

152.图16所示的线性电源电路具有与其外部连接的输出电容器c3和负载ldl。具体地,输出电容器c3和负载ld1彼此并联地外部连接到输出端tm2。图16所示的线性电源电路对输入电压vin进行降压以生成输出电压vout,并将输出电压vout供给至负载ld7。

153.晶体管q3设置在被施加输入电压vin的输入端tm1与被施加输出电压vout的输出端tm2之间。晶体管q3是nmosfet。从而,从电荷泵电路cp1供给至基准电压生成器3的栅极的栅极信号g3越低,晶体管q1的导通率越高,因此输出电压vout越高。反过来说,栅极信号g3越高,晶体管q1的导通率越低,因此输出电压vout越低。

154.基准电压生成器ref1生成基准电压vref。电阻器r1和r2生成反馈电压vfb,该反馈电压vfb是输出电压vout的分压。

155.差分放大器amp1的反相输入端(

‑

)被施加基准电压vref,差分放大器amp1的非反相输入端( )被施加反馈电压vfb。差分放大器amp1将输入电压vin用作其电源电压。差分放大器amp1基于基准电压vref与反馈电压vfb之间的差δv(=vfb

‑

vref)来驱动晶体管q1。即,差分放大器amp1的输出端连接到晶体管q1的栅极。

156.晶体管q1是pmosfet。晶体管q1的源极连接到输入端tm1。晶体管q1的漏极连接到作为nmosfet的晶体管q2的漏极和栅极、电容器c1的一端、以及开关sw1的一端。晶体管q2的源极连接到地电位、电容器c1的另一端、以及开关sw2的一端。

157.开关swl的另一端连接到电容器c2的一端以及开关sw3的一端。开关sw3的另一端用作电荷泵电路cp1的输出端。开关sw2的另一端连接到电容器c2的另一端以及开关sw4的一端。开关sw4的另一端连接到输出端tm2。

158.电荷泵电路cp1中的开关sw1和sw2由时钟信号ck接通和断开。开关sw3和sw4由反

向时钟信号接通和断开。由于电荷泵电路cp1基于时钟信号ck和反向时钟信号动作,作为nmosfet的晶体管q3的源极电压和电容器c2的充电电压(即,具有与电容器c1的充电电压相同值的电压)之和的电压被施加于晶体管q3的栅极。

159.如上所述,电荷泵电路cp1驱动晶体管q3。因此,由输入端tm1、输出端tm2、晶体管q3以及电荷泵电路cp1构成的源极跟随器电路可以使作为nmosfet的晶体管q3的栅极电压高于输入电压vin。因此,上述源极跟随器电路可以减小输入电压vin下降时的晶体管q3的源极电压的下降量(即,输入电压vin与晶体管q3的源极电压之间的差)。由于设有上述源极跟随器电路,图16所示的线性电源电路可以减小输入电压vin下降时的输出电压vout的下降量(输入电压vin与输出电压vout之间的差)。

160.下面对比较器cmp1和时钟信号生成电路clk1进行描述。比较器cmp1的非反相输入端( )被施加基准电压vref,比较器cmp1的反相输入端(

‑

)被施加反馈电压vfb。比较器cmp1将输入电压vin用作其电源电压。比较器cmp1将基准电压vref与反馈电压vfb进行比较,并在反馈电压vfb低于基准电压vref时输出高电平输出信号,而反馈电压vfb高于基准电压vref时输出低电平输出信号。

161.这里,反馈电压vfb低于基准电压vref的情况等同于输出电压vout低于预定值(基准电压vref乘以电阻器r1和r2的分压比的倒数所得的值)的情况。当反馈电压vfb与基准电压vref相等时,比较器cmp1的输出信号可处于高电平和低电平中的任一个。

162.比较器cmpl的输出信号作为使能信号被供给至时钟信号生成电路clkl。

163.当比较器cmpl的输出信号处于高电平时,时钟信号生成电路clkl处于使能状态,输出时钟信号ck和反向时钟信号时钟信号ck和反向时钟信号被供给至电荷泵电路cp1。由此,使得电荷泵电路cp1能够动作。

164.另一方面,当比较器cmp1的输出信号处于低电平时,时钟信号生成电路clk1处于禁用状态,不输出时钟信号ck和反向时钟信号因此,电荷泵电路cp1也不动作。即,当反馈电压vfb高于基准电压vref时,可以保持时钟信号生成电路clk1和电荷泵电路cp1不动作。因此,可以在无负载情况下(即,当负载ld1的阻抗可以被视为无限高时)抑制时钟信号生成电路clk1和电荷泵电路cp1的功耗。

165.<10.第九实施方式>

166.图17是示出根据第九实施方式的线性电源电路的配置的图。图17所示的线性电源电路与图16所示的线性电源电路的不同之处在于,晶体管q1和q2被省略,基准电压vreg被施加于差分放大器amp1的非反相输入端( ),并且反馈电压vfb被施加于差分放大器amp1的反相输入端(

‑

),而其他与图16所示的线性电源电路相同。

167.图17所示的线性电源电路提供类似于图16所示的线性电源电路的有益效果。

168.<11.用途>

169.图18是半导体集成电路器件的外观图。图18所示的半导体集成电路器件具有外部引脚p1至p14,并且内置有内部电源8。内部电源8可以是根据前述第一至第四实施方式中任一实施方式的线性电源电路。内部电源8向图18所示的半导体集成电路器件内的至少一些电路供给内部电源电压vreg(即,线性电源电路的输出电压vout)。

170.内部电源8的输入端t1连接到外部引脚p1。在所讨论的示例的变型例中,内部电源

8的输入端t1可以连接到多个外部引脚。

171.另一方面,内部电源8的输出端t2不连接到外部引脚p1至p14中的任何一个。用作内部电源8的线性电源电路是不需要外接电容器的电源电路,因此不需要将内部电源8的输出端t2连接到外部引脚。由此,消除了为内部电源8的输出部分提供保护电路的需要。因此,将根据前述第一至第七实施例中任一实施方式的线性电源电路用作内部电源8大大有助于半导体集成电路器件的尺寸减小和成本降低。

172.图19是车辆x的外观图。该配置例的车辆x搭载有通过接受从电池(未示出)供给的电压而动作的各种电子设备x11至x18。为方便起见,图19可能未示出在实际所设置于的位置处的电子设备x11至x18。

173.电子设备x11是发动机控制单元,其执行关于发动机的控制(喷射控制、电子节气门控制、怠速控制、氧传感器加热器控制、自动巡航控制等)。

174.电子设备x12是控制hid(高强度放电灯)和drl(日间行车灯)的点亮和熄灭的灯控制单元。

175.电子设备x13执行关于变速器的控制的变速器控制单元。

176.电子设备x14是执行关于车辆x的运动的控制(abs[防抱死制动系统]控制、eps(电动助力转向)控制、电子悬架控制等)的行为控制单元。

[0177]

电子设备x15是驱动和控制门锁、防盗报警器等的安全控制单元。

[0178]

电子设备x16包括在工厂发运阶段作为标准或制造商装配的设备并入车辆x中的电子设备,例如雨刷、电动侧视镜、电动窗、阻尼器(减震器)、电动天窗、以及电动座椅。

[0179]

电子设备x17包括作为用户装配设备可选地安装在车辆x上的电子设备,例如a/v(视听)设备、汽车导航系统以及etc(电子收费控制系统)等。

[0180]

电子设备x18包括设有高耐压电机的电子设备,例如车载鼓风机、油泵、水泵、电池冷却风扇等。

[0181]

前文中描述的任意线性电源电路和半导体集成电路器件可以内置于电子设备x11至x18中的任一个。

[0182]

<12.其他>

[0183]

本说明书中公开的实施方式应被视为在每个方面都是说明性的而非限制性的,本发明的技术范围不由上面给出的实施方式的描述定义,而是由所附权利要求书的范围定义,并且应被理解为包含任何在与权利要求书等同的精神和范围内的变更。

[0184]

例如,虽然上述第一至第七实施方式涉及线性电源电路不包括输出电容器的配置,但线性电源电路可以包括(并入)电容小于100nf的输出电容器(连接到输出端t2的电容器)。

[0185]

附图标记说明

[0186]1ꢀꢀ

输出晶体管

[0187]2ꢀꢀ

驱动器

[0188]8ꢀꢀ

内部电源

[0189]

21、21

’ꢀꢀ

差分放大器

[0190]

22、22

’ꢀꢀ

电容器

[0191]

23

ꢀꢀ

pmosfet(转换器的一例)

[0192]

23

’ꢀ

nmosfet(转换器的另一例)

[0193]

24

ꢀꢀ

电流放大器

[0194]

101、102

ꢀꢀ

nmosfet

[0195]

103、106

ꢀꢀ

电容器

[0196]

104、cp1

ꢀꢀ

电荷泵电路

[0197]

105、clk1

ꢀꢀ

时钟信号生成电路

[0198]

t1、tm1

ꢀꢀ

输入端

[0199]

t2、tm2

ꢀꢀ

输出端

[0200]

p1至p14

ꢀꢀ

外部引脚

[0201]

q1

ꢀꢀ

晶体管

[0202]

x

ꢀꢀ

车辆。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。