摄像装置

1.本技术是申请日为2016/02/16、申请号为201610086746.8、发明名称为“摄像装置”的中国专利申请的分案申请

技术领域

2.本发明涉及摄像装置。本发明特别涉及具有包括支承在半导体基板上的光电转换膜的光电转换元件的摄像装置。

背景技术:

3.作为mos(metal oxide semiconductor:金属氧化物半导体)型的摄像装置而提出了层叠型的摄像装置。在层叠型的摄像装置中,在半导体基板的最表面上层叠光电转换膜,将在光电转换膜中通过光电转换产生的电荷向电荷储存区域(称作“浮动扩散区”)储存。摄像装置在半导体基板内使用ccd(charge coupled device:电荷耦合器件)电路或cmos(complementary mos:互补金属氧化物半导体)电路将其储存的电荷读出。例如日本特开2009-164604号公报公开了这样的摄像装置。日本特开2012-151771号公报公开了具有包含有机材料的光电转换层的固体摄像元件。日本特开2010-067827号公报提出了在配置于光电转换层的上方的滤色器上设置隔壁的方案。该隔壁设在相互邻接的不同颜色的两个滤色器(从r滤色器、g滤色器及b滤色器中选择的两个)之间。

技术实现要素:

4.根据本发明的并非限定性的某个例示性的实施方式,提供以下技术方案。

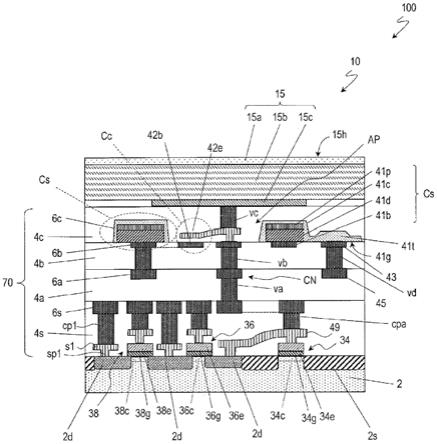

5.本发明的摄像装置,具备:半导体基板,设有电路元件;光电转换元件,被半导体基板支承,对入射光进行光电转换,具有形成在受光面侧的第1电极、遮光性的第2电极以及配置在第1电极与第2电极之间的光电转换膜;多层配线构造,设在半导体基板与光电转换元件的第2电极之间,包括将第2电极与设于半导体基板的电路元件电连接的连接部;以及电容元件,形成在多层配线构造内。电容元件具有下部电极、上部电极以及配置在上部电极与下部电极之间的电介质膜。下部电极及上部电极的至少一方具有连接部所贯通的开口或切缝,开口或切缝从半导体基板的法线方向来看时与第2电极重叠。

附图说明

6.图1是表示有关本发明的实施方式1的摄像装置的例示性的电路结构的图。

7.图2是表示图1所示的单位像素单元10的例示性的电路结构的图。

8.图3是摄像装置100具有的单位像素单元10的示意性的剖面图。

9.图4是表示单位像素单元10中的各元件的布局的一例的示意性的平面图。

10.图5是用来说明从半导体基板2的法线方向观察时的、光电转换元件15的第2电极15c及第1电容元件cs的上部电极41c的配置例的平面图。

11.图6是本发明的实施方式2的单位像素单元10a的示意性的剖面图。

12.图7是用来说明从半导体基板2的法线方向观察时的、屏蔽电极15sd、光电转换元件15的第2电极15c及第1电容元件cs的上部电极41c的配置例的平面图。

13.图8是用来说明第1模式下的晶体管的动作的一例的时序图。

14.图9是表示单位像素单元的另一例示性的电路结构的图。

具体实施方式

15.在摄像装置的领域中,有降低噪声的要求。

16.在详细说明本发明的实施方式之前,说明本发明的一技术方案的概要。本发明的一技术方案的概要如下。

17.[项目1]

[0018]

一种摄像装置,具备:半导体基板;光电转换元件,包括第1电极、第2电极及上述第1电极与上述第2电极之间的光电转换膜,被上述半导体基板支承,通过对入射光进行光电转换而生成信号;多层配线构造,包括设在上述半导体基板与上述光电转换元件的上述第2电极之间的上部配线层及下部配线层;信号检测电路,设在上述半导体基板及上述多层配线构造内,包括信号检测晶体管及第1电容元件,检测上述信号;上述信号检测晶体管包括栅极、以及设在上述半导体基板上的源极区域及漏极区域;上述第1电容元件包括第1下部电极、第1上部电极、以及配置在上述第1上部电极与上述第1下部电极之间的电介质膜;上述上部配线层配置在上述光电转换元件的上述第2电极与上述信号检测晶体管的上述栅极之间;上述上部配线层包含上述第1上部电极。

[0019]

根据项目1的结构,由于能够将具有比较大的电容值的第1电容元件比较容易地形成在单位像素单元内,所以能够进一步减小ktc噪声等的噪声。

[0020]

[项目2]

[0021]

如项目1所述的摄像装置,上述下部配线层配置在上述上部配线层与上述信号检测晶体管的上述栅极之间;上述下部配线层包含上述第1下部电极。

[0022]

根据项目2的结构,能够将第1电容元件形成在多层配线构造内。

[0023]

[项目3]

[0024]

如项目1或2所述的摄像装置,上述信号检测电路还包括包含第2下部电极及第2上部电极的第2电容元件;上述第2电容元件的电容比上述第1电容元件的电容小;上述第2下部电极及第2上部电极中的一方与上述第1下部电极及上述第1上部电极中的一方连接。

[0025]

根据项目3的结构,与第1电容元件同样,能够比较容易地将第2电容元件配置到半导体基板与光电转换元件之间。

[0026]

[项目4]

[0027]

如项目3所述的摄像装置,上述第2下部电极及第2上部电极中的另一方与上述光电转换元件的上述第2电极连接。

[0028]

根据项目4的结构,能够经由第2电容元件将第1电容元件电连接到光电转换元件的第2电极上。

[0029]

[项目5]

[0030]

如项目1~4中任一项所述的摄像装置,还具备使上述信号检测电路的输出负反馈的反馈电路;上述反馈电路包括输出线;上述信号检测电路还包括包含源极及漏极的复位

晶体管;上述复位晶体管的上述源极及上述漏极中的一方与上述光电转换元件的上述第2电极连接;上述复位晶体管的上述源极及上述漏极中的另一方与上述输出线连接。

[0031]

根据项目5的结构,能够使用反馈电路执行ktc噪声的消除。

[0032]

[项目6]

[0033]

如项目1~5中任一项所述的摄像装置,上述多层配线构造还包括将上述光电转换元件的上述第2电极与上述信号检测晶体管的上述栅极连接的连接部;当从上述半导体基板的法线方向观察时,上述第1上部电极及上述第1下部电极中的一方将上述连接部包围。

[0034]

根据项目6的结构,能够抑制噪声向电荷储存节点的混入。

[0035]

[项目7]

[0036]

如项目1~6中任一项所述的摄像装置,上述多层配线构造还包括向上述第1上部电极施加基准电压的信号线;上述第1上部电极具有与上述光电转换元件的上述第2电极对置的第1面及上述第1面相反侧的第2面;上述第1上部电极在上述第2面中与上述信号线连接。

[0037]

根据项目7的结构,能够将光电转换元件的第2电极与第1电容元件的第1上部电极之间的距离缩小。此外,能够在第1上部电极的下表面中建立供给一定的电压的电路与第1上部电极之间的电连接。

[0038]

[项目8]

[0039]

如项目1~7中任一项所述的摄像装置,上述第1上部电极将上述电介质膜的表面中的与上述第1下部电极对置的表面以外的表面覆盖。

[0040]

根据项目8的结构,能够抑制第1电容元件中的泄漏电流的发生。

[0041]

[项目9]

[0042]

如项目1~8中任一项所述的摄像装置,上述光电转换元件的上述第2电极及上述第1上部电极由同一材料构成。

[0043]

[项目10]

[0044]

如项目1~9中任一项所述的摄像装置,还具备与上述光电转换元件的上述第2电极隔开间隔地配置的屏蔽电极;当从上述半导体基板的法线方向观察时,上述屏蔽电极将上述光电转换元件的上述第2电极包围。

[0045]

[项目11]

[0046]

如项目10所述的摄像装置,当从上述半导体基板的法线方向观察时,在上述光电转换元件的上述第2电极与上述屏蔽电极之间配置有上述第1上部电极。

[0047]

以下,参照附图详细地说明本发明的实施方式。另外,以下说明的实施方式都表示包含性或具体的例子。在以下的实施方式中表示的数值、形状、材料、构成要素、构成要素的配置及连接形态、步骤、步骤的顺序等是一例,不是限定本发明的意思。在本说明书中说明的各种形态只要不发生矛盾就能够相互组合。此外,以下的实施方式的构成要素中的在表示最上位概念的独立权利要求中没有记载的构成要素,设为任意的构成要素进行说明。在以下的说明中,有将实质上具有相同功能的构成要素用共同的标号表示而省略说明的情况。

[0048]

(实施方式1)

[0049]

图1表示有关本发明的实施方式1的摄像装置的例示性的电路结构的概略。图1所

示的摄像装置100具备多个单位像素单元10和外围电路。通过将多个单位像素单元10在半导体基板上二维地排列而形成感光区域(像素区域)。

[0050]

在图示的例子中,多个单位像素单元10在行方向及列方向上排列。在本说明书中,所谓行方向及列方向,是指行及列分别延伸的方向。这里,纸面上的垂直方向是列方向,水平方向是行方向。多个单位像素单元10也可以一维地排列。换言之,摄像装置100可以是线性传感器。

[0051]

单位像素单元10中的每一个连接在电源配线22上。对于各单位像素单元10,经由电源配线22供给规定的电源电压。如在后面详细说明那样,单位像素单元10中的每一个,包括对入射光进行光电转换的光电转换部、和检测由光电转换部生成的信号的信号检测电路。如图示那样,摄像装置100具有用来向全部的光电转换部施加相同的一定电压的储存控制线17。

[0052]

摄像装置100的外围电路包括垂直扫描电路(也称作“行扫描电路”)16、多个负荷电路19、多个纵列信号处理电路20(也称作“行信号储存电路”)、多个反转放大器24和水平信号读出电路(也称作“列扫描电路”)21。负荷电路19、纵列信号处理电路20及反转放大器24按照二维排列的单位像素单元10的每个列配置。

[0053]

垂直扫描电路16连接在寻址信号线30及复位信号线26上。垂直扫描电路16通过对寻址信号线30施加规定的电压,以行单位选择配置在各行中的多个单位像素单元10。通过将多个单位像素单元10以行单位进行选择,执行所选择的单位像素单元10的信号电压的读出和后述的像素电极的复位。

[0054]

在图示的例子中,垂直扫描电路16也连接在反馈控制线28及灵敏度调整线32上。如后述那样,通过垂直扫描电路16向反馈控制线28施加规定的电压,能够形成使单位像素单元10的输出负反馈的反馈电路。此外,垂直扫描电路16能够经由灵敏度调整线32向多个单位像素单元10供给规定的电压。

[0055]

配置在各列中的单位像素单元10经由与各列对应的垂直信号线18电连接在纵列信号处理电路20上。在垂直信号线18上电连接着负荷电路19。纵列信号处理电路20进行以相关双采样为代表的噪音抑制信号处理及模拟-数字转换(ad转换)等。在与单位像素单元10的各列对应设置的纵列信号处理电路20上,电连接着水平信号读出电路21。水平信号读出电路21从多个纵列信号处理电路20将信号向水平共用信号线23依次读出。

[0056]

在图1所例示的结构中,反转放大器24对应于各列设置。反转放大器24的负侧的输入端子连接在对应的垂直信号线18上。对于反转放大器24的正侧的输入端子,供给规定的电压(例如1v或1v左右的正电压)vref。此外,反转放大器24的输出端子经由对应于各列设置的反馈线25连接在与该反转放大器24的负侧的输入端子连接的多个单位像素单元10上。反转放大器24构成使来自单位像素单元10的输出负反馈的反馈电路的一部分。也可以将反转放大器24称作反馈放大器。反转放大器24的动作后述。

[0057]

图2表示图1所示的单位像素单元10的例示性的电路结构。单位像素单元10包括光电转换部pc和信号检测电路sc。

[0058]

光电转换部pc包括具有第1电极15a、光电转换膜15b及第2电极(像素电极)15c的光电转换元件15。光电转换元件15的第1电极15a连接在储存控制线17上,光电转换元件15的第2电极15c连接在电荷储存节点(也称作“浮动扩散节点”)44上。通过经由储存控制线17

控制第1电极15a的电位,能够将通过光电转换产生的空穴-电子对中的空穴及电子中的某一方用第2电极15c收集。在作为信号电荷而使用空穴的情况下,只要使第1电极15a的电位比第2电极15c高就可以。以下,例示作为信号电荷使用空穴的情况。例如将10v左右的电压经由储存控制线17向第1电极15a施加。由此,信号电荷向电荷储存节点44储存。当然,作为信号电荷也可以使用电子。

[0059]

信号检测电路sc包括将由光电转换元件15生成的信号放大的信号检测晶体管34和第1电容元件cs。在图示的例子中,信号检测电路sc还包括复位晶体管(第1复位晶体管)36、具有比第1电容元件cs小的电容值的第2电容元件cc和寻址晶体管40。这样,在本发明中,单位像素单元10中的每一个在像素内具有1个以上的电容元件。如后面详细说明的那样,如果第1电容元件cs具有比较大的电容值,则能够有效地降低ktc噪声,所以是有益的。

[0060]

信号检测晶体管34的栅极连接在电荷储存节点44上。换言之,信号检测晶体管34的栅极具有与第2电极15c的电连接。信号检测晶体管34的源极及漏极的一方(如果是n沟道mos则是漏极)连接在电源配线(源极跟随电源)22上,另一方连接在垂直信号线18上。由信号检测晶体管34和负荷电路19(在图2中没有图示,参照图1)形成源极跟随电路。

[0061]

单位像素单元10包括寻址晶体管(行选择晶体管)40。寻址晶体管40的漏极或源极连接在信号检测晶体管34的源极及漏极中的没有与电源配线22连接的一侧。寻址晶体管40的栅极连接在寻址信号线30上。

[0062]

与储存在电荷储存节点44中的信号电荷的量对应的电压被施加至信号检测晶体管34的栅极。信号检测晶体管34将该电压放大。由信号检测晶体管34放大的电压作为信号电压被寻址晶体管40有选择地读出。

[0063]

在图2所例示的结构中,第1电容元件cs的电极中的一方连接在灵敏度调整线32上。灵敏度调整线32的电位例如被设定为0v。典型地,灵敏度调整线32的电位在摄像装置100动作时被固定。灵敏度调整线32能够用于电荷储存节点44的电位的控制。第1电容元件cs的电极中的另一方连接在第2电容元件cc的电极中的一方上。以下,有时将包括第1电容元件cs与第2电容元件cc的连接点的节点称作复位漏极节点46。

[0064]

第2电容元件cc的电极中的另一方连接在电荷储存节点44上。即,第2电容元件cc的电极中的没有连接在复位漏极节点46上的电极,具有与光电转换元件15的第2电极15c的电连接。另外,在该例中,与第2电容元件cc并联地连接着复位晶体管36。即,复位晶体管36的源极及漏极中的一方连接在电荷储存节点44上,具有与光电转换元件15的第2电极15c的电连接。复位晶体管36的源极及漏极中的另一方连接在复位漏极节点46上。

[0065]

在图2所例示的结构中,单位像素单元10还包括源极及漏极的一方连接在复位漏极节点46上、另一方连接在反馈线25上的第2复位晶体管38。第2复位晶体管38的栅极连接在反馈控制线28上。如在后面详细说明的那样,通过控制反馈控制线28的电压,能够形成使信号检测电路sc的输出负反馈的反馈电路fc。在图示的结构中,复位晶体管36的源极及漏极中的连接在复位漏极节点46上的一侧与作为反馈电路fc的输出线的反馈线25,经由第2复位晶体管38而连接。

[0066]

上述的信号检测晶体管34、第1复位晶体管36、寻址晶体管40及第2复位晶体管38中的每一个晶体管,既可以是n沟道mos,也可以是p沟道mos。也不需要将它们的全部统一为n沟道mos或p沟道mos的某个。以下,说明信号检测晶体管34、第1复位晶体管36、寻址晶体管

40及第2复位晶体管38是n沟道mos的例子。

[0067]

(单位像素单元10的设备构造)

[0068]

接着,参照图3至图5说明单位像素单元10的设备构造的一例。

[0069]

图3示意地表示摄像装置100具有的单位像素单元10中的1个截面。图4示意地表示单位像素单元10的各元件的布局的一例。图3相当于图4所示的iii-iii线剖面图。

[0070]

如图3所示,摄像装置100具有半导体基板2、光电转换元件15、和配置在半导体基板2及光电转换元件15之间的多层配线构造70。图3表示以垂直于半导体基板2的主面的面切断时的单位像素单元10的截面的一例。

[0071]

作为半导体基板2,例如可以使用硅基板。半导体基板2并不限定于其整体是半导体的基板。半导体基板2也可以是在形成感光区域的一侧的表面上设有半导体层的绝缘性基板等。以下,说明作为半导体基板2而使用p型硅(si)基板的例子。

[0072]

半导体基板2(这里是p型硅基板)具有杂质区域2d(这里是n型区域)。在图3及图4所例示的结构中,第2复位晶体管38包括两个杂质区域2d、形成在半导体基板2上的栅极绝缘膜38g和形成在栅极绝缘膜38g上的栅极电极38e。在作为源极或漏极的两个杂质区域2d之间形成沟道区域38c。第2复位晶体管38中的两个杂质区域2d的一方经由多晶硅插塞sp1、配线层s1及接触插塞cp1连接在未图示的反馈线25(参照图2)上。

[0073]

与第2复位晶体管38同样,第1复位晶体管36包括两个杂质区域2d、形成在半导体基板2上的栅极绝缘膜36g和形成在栅极绝缘膜36g上的栅极电极36e。在作为源极或漏极的两个杂质区域2d之间,形成沟道区域36c。在图示的例子中,第1复位晶体管36及第2复位晶体管38共用杂质区域2d中的1个。

[0074]

信号检测晶体管34也同样,包括两个杂质区域2d、形成在半导体基板2上的栅极绝缘膜34g和形成在栅极绝缘膜34g上的栅极电极34e。另外,信号检测晶体管34的两个杂质区域2d在图3中分别位于纸面的近侧及里侧,在图3中,没有表示信号检测晶体管34的两个杂质区域2d。在图3中表示信号检测晶体管34的栅极绝缘膜34g、栅极电极34e及形成在两个杂质区域2d之间的沟道区域34c。在图3中未图示的、形成在半导体基板2上的这两个杂质区域2d,分别作为信号检测晶体管34的源极区域及漏极区域发挥功能(图4所示的源极区域2ds及漏极区域2dd)。

[0075]

寻址晶体管40也可以具有与信号检测晶体管34大致同样的结构。在这里说明的例子中,寻址晶体管40及信号检测晶体管34共用杂质区域2d中的1个(参照图4)。

[0076]

半导体基板2具有用于元件间的电分离的元件分离区域2s。在图4所示的例子中,第1复位晶体管36及第2复位晶体管38的组、以及信号检测晶体管34及寻址晶体管40的组通过元件分离区域2s而分离。单位像素单元10中的每一个通过元件分离区域2s而相互分离。元件分离区域2s例如可以通过在规定的注入条件下进行受主(acceptor)的离子注入来形成。

[0077]

参照图3。单位像素单元10具有支承在半导体基板2上的光电转换元件15。如已经说明那样,光电转换元件15具有第1电极15a、光电转换膜15b和第2电极15c。光电转换元件15典型地具有在第1电极15a及第2电极15c之间夹着光电转换膜15b的构造。在图示的例子中,在多层配线构造70上层叠着光电转换元件15的第2电极15c。即,在本发明的实施方式中,光电转换部pc没有形成在半导体基板2内,而设在半导体基板2的上方。另外,本说明书

中的“上方”的用语为了表示部件间的相对的配置而使用,不是限定本发明的摄像装置的姿态的意思。关于本说明书中的“上部”及“下部”的用语也是同样的。

[0078]

第2电极15c在多个单位像素单元10之间被电分离。典型地,相互邻接的第2电极15c通过例如由二氧化硅形成的绝缘层电分离。第2电极15c收集在光电转换膜15b中通过光电转换产生的电荷。第2电极15c可以由铝、铜等的金属、金属氮化物或通过掺杂杂质而被赋予了导电性的多晶硅等形成。

[0079]

光电转换膜15b由有机材料或非晶硅等的无机材料形成。光电转换膜15b也可以包括由有机材料构成的层和由无机材料构成的层。

[0080]

第1电极15a隔着光电转换膜15b与第2电极15c对置。在该例中,第1电极15a设于在光电转换元件15中来自被摄体的光入射的受光面15h侧。第1电极15a既可以直接形成在光电转换膜15b上,也可以在第1电极15a与光电转换膜15b之间配设其他层。第1电极15a由ito等的透明的导电性材料形成。

[0081]

光电转换膜15b及第1电极15a典型地跨越多个像素而形成。但是,光电转换膜15b及第1电极15a的至少一方也可以与第2电极15c同样,在多个单位像素单元10之间电分离。

[0082]

如图3所示,在光电转换元件15与半导体基板2之间设有多层配线构造70。多层配线构造70包括用来将光电转换元件15的第2电极15c与形成在半导体基板2上的信号检测晶体管34的栅极电极34e电连接的连接部cn。连接部cn可以是电荷储存节点44的一部分。以下,参照图3更详细地说明多层配线构造70的结构。

[0083]

多层配线构造70典型地包括1个以上的绝缘层及1个以上的配线层。在图3所例示的结构中,多层配线构造70具有将信号检测晶体管34及复位晶体管36、38覆盖而形成的绝缘层4s、形成在绝缘层4s上的绝缘层4a、形成在绝缘层4a上的绝缘层4b、和形成在绝缘层4b上的绝缘层4c。绝缘层4s、绝缘层4a、绝缘层4b及绝缘层4c例如由二氧化硅形成。

[0084]

在图3所例示的结构中,多层配线构造70包括配线层s1、配线层6s、配线层6a、配线层6b及配线层6c。多层配线构造70中包含的绝缘层及配线层的层数并不限定于图3所例示的层数,可以任意地设定。

[0085]

配线层s1形成在绝缘层4s内。在该例中,配线层s1由多晶硅形成。配线层s1在其一部分中包含将信号检测晶体管34的栅极电极34e与复位晶体管36的漏极(杂质区域2d中的1个)电连接的多晶硅配线49。

[0086]

配线层6s被埋入在绝缘层4s的上表面中。配线层6a及配线层6b分别被埋入在绝缘层4a的上表面及绝缘层4b的上表面中。配线层6c配置在绝缘层4c内。另外,本说明书中的“上表面”,是指所关注的层具有的两个主面中的、距光电转换元件15比半导体基板2近的主面。此外,“下表面”是指所关注的层具有的两个主面中的、距半导体基板2比光电转换元件15近的方的主面(与“上表面”相反侧的主面)。本说明书中的“上表面”及“下表面”的用语被用于将多层配线构造70中包含的各层的主面加以区别,不以限定本发明的摄像装置的姿态的意图来使用。

[0087]

在图示的例子中,多层配线构造70还包括接触插塞cpa、通孔va及通孔vb。接触插塞cpa形成在绝缘层4s内。接触插塞cpa将配线层s1(这里是多晶硅层)与配线层6s电连接。通孔va及通孔vb分别形成在绝缘层4a内及绝缘层4b内。通孔va将配线层6s与配线层6a电连接,通孔vb将配线层6a与配线层6b电连接。接触插塞cpa、配线层6s、6a及6b以及通孔va及vb

例如由金属形成。在图3所例示的结构中,接触插塞cpa、配线层6s的至少一部分、通孔va、配线层6a的至少一部分、通孔vb、配线层6b的至少一部分以及后述的通孔vc及第2电容元件cc的上部电极42e是上述连接部cn的一部分。

[0088]

如图示那样,在本发明的实施方式中,第1电容元件cs形成在多层配线构造70内。即,具有信号检测晶体管34及第1电容元件cs的本发明的实施方式的信号检测电路sc形成在半导体基板2及多层配线构造70内。以下,参照附图更详细地说明第1电容元件cs的结构的典型例。

[0089]

第1电容元件cs具有下部电极41b、上部电极41c及配置在下部电极41b与上部电极41c之间的电介质膜41d。在图3所例示的结构中,第1电容元件cs的上部电极41c是位于光电转换元件15的第2电极15c与信号检测晶体管34的栅极电极34e之间的配线层6c的至少一部分。此外,第1电容元件cs的下部电极41b是位于配线层6c与信号检测晶体管34的栅极电极34e之间的配线层6b的至少一部分。

[0090]

通过将第1电容元件cs配置到设在半导体基板2与光电转换元件15之间的多层配线构造70内,能够形成具有更大的电容值的第1电容元件cs。特别是,如果将第1电容元件cs配置到光电转换元件15与信号检测晶体管34的栅极电极34e之间,则能够抑制包括信号检测晶体管34的栅极电极34e的配线层与第1电容元件cs的上部电极41c及下部电极41b之间的干涉,确保更大的电极面积。这样,通过将第1电容元件cs配置到多层配线构造70内,第1电容元件cs的电极形状的设计的自由度提高。另外,从半导体基板2的法线方向观察时的上部电极41c的形状不需要与下部电极41b的形状一致。当从半导体基板2的法线方向观察时,只要上部电极41c包含与下部电极41b的至少一部分对置的部分就可以。

[0091]

在该例中,上部电极41c在其中央具有开口部ap。如图示那样,将光电转换元件15的第2电极15c与信号检测晶体管34的栅极电极34e连接的连接部cn贯穿设在上部电极41c上的开口部ap。

[0092]

在图3所例示的结构中,在开口部ap内配置有信号检测电路sc的第2电容元件cc。第2电容元件cc具有下部电极42b和隔着绝缘层4c的一部分与下部电极42b对置的上部电极42e。绝缘层4c中的被下部电极42b及上部电极42e夹着的部分作为第2电容元件cc的电介质膜发挥功能。上部电极42e(典型地是金属电极)经由通孔vc连接在光电转换元件15的第2电极15c上。该通孔vc是上述连接部cn的一部分。即,第2电容元件cc具有与电荷储存节点44之间的电连接。如果在第2电容元件cc的上部电极42e与下部电极42b之间发生泄漏电流,则起因于泄漏电流的噪声混入到输出信号中,所以构成第2电容元件cc的电介质膜的材料为绝缘性良好的材料是有益的。

[0093]

另外,在该例中,第2电容元件cc的下部电极42b是配线层6b的至少一部分,电连接在第1电容元件cs的下部电极41b上。这里,第2电容元件cc的下部电极42b位于与第1电容元件cs的下部电极41b同层。但是,单位像素单元10内的第2电容元件cc的配置并不限定于图3所示的例子。即,既可以是第2电容元件cc的下部电极42b形成在与绝缘层4b不同的层内,也可以是上部电极42e形成在与绝缘层4c不同的层内。

[0094]

在图3所例示的结构中,第1电容元件cs的下部电极41b经由第2电容元件cc电连接在光电转换元件15的第2电极15c上。这样,第1电容元件cs具有与电荷储存节点44之间的电连接,所以如果在第1电容元件cs的上部电极41c与下部电极41b之间发生泄漏电流,则起因

于泄漏电流的噪声混入到输出信号中。因此,从抑制泄漏电流的观点来说,由绝缘性良好的材料形成第1电容元件cs的电介质膜41d是有益的。

[0095]

如果将第1电容元件cs配置到多层配线构造70内,则作为用来形成电介质膜41d的材料而采用具有比较高的介电常数的材料是比较容易的。例如,作为用来形成电介质膜41d的材料,可以使用与构成将电介质膜41d覆盖的绝缘层4c的材料(例如二氧化硅)不同的材料。

[0096]

第1电容元件cs的电介质膜41d例如由金属氧化物或金属氮化物形成。用来形成电介质膜41d的材料的例子是含有从由zr、al、la、ba、ta、ti、bi、sr、si、y及hf构成的组中选择的1种以上物质的氧化物或氮化物。用来形成电介质膜41d的材料既可以是2元系化合物,也可以是3元系化合物或4元系化合物。

[0097]

在电介质膜41d的形成中,可以使用例如原子层堆积法(atomic layer deposition(ald))。根据ald,能够将相互不同的原子每几个原子地层叠。具体而言,向在内部设置有基板的真空容器内导入原料化合物分子(前体)。使导入的前体吸附在真空容器内的基板表面。然后,通过由化学反应仅使前体中的希望的原子残留,进行原子一层的量的成膜。

[0098]

这里,作为第1电容元件cs的电介质膜41d而使用hf的氧化物的膜。在hf的氧化物的膜的形成中,使用四乙基甲基酰胺铪(

テトラキスエチルメチルアミドハフ

二

ウム

)作为前体,在前体的导入后进行等离子体放电。通过在氧环境中进行等离子体放电,促进hf的氧化。通过重复上述工序,将hfo2一层层地层叠。在本发明的实施方式中,通过将气态的前体的导入和等离子体放电重复250次,形成具有22nm的厚度的膜作为电介质膜41d。

[0099]

根据本发明的实施方式,使用与构成多层配线构造70中的绝缘层的材料不同的材料形成电介质膜41d是比较容易的。因而,能够使用具有比较高的介电常数的材料较容易地形成电介质膜41d。即,容易在单位像素单元内形成具有比较大的电容值的电容元件。根据后述的本发明的摄像装置100的例示性的动作可知,第1电容元件cs的电容值越大,能够得到越高的降低噪声的效果。此外,第1电容元件cs的电容值越大,能够使信号电荷的储存区域整体的电容越大,所以对于高照度下的摄影越有利。另外,电介质膜41d也可以包括由相互不同的材料形成的两种以上的膜。通过将电介质膜41d形成为2层以上的层叠膜,能够得到发挥构成各层的材料的优点的电介质膜。在能够确保充分的电极面积的情况下,也可以使用构成多层配线构造70中的绝缘层(例如绝缘层4c)的材料形成电介质膜41d。

[0100]

从半导体基板2的法线方向观察时的电介质膜41d的形状可以任意地设定。在图3所例示的结构中,电介质膜41d配置在将光电转换元件15的第2电极15c与信号检测晶体管34的栅极电极34e连接的连接部cn的周围。电介质膜41d既可以是连续的单一的膜,也可以包括在同层中配置在相互不同的部位的多个部分。

[0101]

在电介质膜41d的图案形成中,可以采用在通常的半导体工艺中导入的光刻法。通过执行抗蚀剂的涂敷、抗蚀剂的曝光、抗蚀剂的显影及蚀刻等的工序,能够将电介质膜(这里是hf的氧化物的膜)残留在希望的区域中。另外,在将抗蚀剂除去的处理中,有通过将电介质膜41d暴露在用于灰化的等离子体或基团中,电介质膜41d受到伤害的情况。此外,电介质膜41d可能暴露在用于抗蚀剂残渣的除去的抗蚀剂剥离液中。如果电介质膜41d损伤,则上部电极41c与下部电极41b之间的泄漏电流有可能增大。

[0102]

在图3所例示的结构中,在电介质膜41d与上部电极41c之间设有保护膜41p。通过在电介质膜41d的上表面设置保护膜41p,能够抑制由抗蚀剂的除去导致的电介质膜41d的损伤。

[0103]

用来形成保护膜41p的材料的例子是cu、al等的金属或多晶硅。如果作为用来形成保护膜41p的材料而使用具有比较高的电传导率的材料,则能够使保护膜41p的电位大致等于上部电极41c的电位,所以是有益的。设想由与构成电介质膜41d的材料不同的绝缘材料形成保护膜41p的情况。在此情况下,将第1电容元件看作两个电容元件的串联连接。如上述那样,电介质膜41d可以由具有比较高的介电常数的材料形成。此时,如果构成保护膜41p的材料的介电常数比构成电介质膜41d的材料低,则两个电容元件的串联接合的合成电容与不设置保护膜41p的情况相比下降。如果作为用来形成保护膜41p的材料而使用具有比较高的电传导率的材料,则能够抑制由在上部电极41c与下部电极41b之间夹装保护膜41p导致的第1电容元件cs中的这样的电容值的下降。

[0104]

如图3所示,第1电容元件cs的上部电极41c也可以在电介质膜41d中将与下部电极41b对置的面以外的面覆盖。在图3所例示的结构中,第1电容元件cs的上部电极41c形成为,将电介质膜41d的上表面及侧面(将上表面及下表面连结的面)覆盖。

[0105]

在图3所例示的结构中,上部电极41c包括沿着绝缘层4b的上表面延伸的连接部41t。连接部41t在其下表面41g连接在端子43上。端子43是配线层6b的一部分,经由通孔vd连接在作为配线层6a的一部分的配线45上。该配线45具有与未图示的灵敏度调整线32(参照图2)的电连接。即,在该例中,上部电极41c经由作为配线层6b的一部分的端子43、通孔vd、和作为配线层6a的一部分的配线45电连接在灵敏度调整线32上。在摄像装置100动作时,经由灵敏度调整线32向上部电极41c供给规定的电压。典型地,在摄像装置100动作时,通过经由灵敏度调整线32向上部电极41c供给规定的电压,上部电极41c的电位被固定为一定的电位。另外,通过经由灵敏度调整线32控制上部电极41c的电位,能够控制电荷储存节点44的电位。换言之,通过调整经由灵敏度调整线32向上部电极41c供给的电压,能够调整摄像装置100的灵敏度。

[0106]

这样,上部电极41c可以在与对置于光电转换元件15的第2电极15c的上表面相反侧的下表面41g中,与灵敏度调整线32电连接。通过在上部电极41c的下表面41g上设置用于与灵敏度调整线32电连接的接点,能够避免配线的复杂化。此外,能够将第1电容元件cs的上部电极41c与光电转换元件15的第2电极15c之间的距离缩小。本发明的发明者们进行模拟的结果显示,如果使第1电容元件cs的上部电极41c与光电转换元件15的第2电极15c之间的距离尽可能变小,则得到了减小相互邻接的像素间的电荷储存区域彼此的寄生电容的结果。推测这是因为随着上部电极41c与第2电极15c之间的距离缩小,将从某个像素的第2电极15c到邻接于该像素的其他像素的电荷储存区域连结的电力线所穿过的间隙缩小的缘故。

[0107]

如图3所示,上部电极41c当从半导体基板2的法线方向观察时,可以配置在与形成在半导体基板2上的晶体管的沟道区域中的至少1个区域重叠的位置。在该例中,上部电极41c将第2复位晶体管38的沟道区域38c及信号检测晶体管34的沟道区域34c覆盖。上部电极41c可以是遮光性的电极。通过在与晶体管的沟道区域重叠的位置配置遮光性的电极,能够抑制光向半导体基板2上的晶体管的沟道区域的入射。

[0108]

如已经说明那样,在层叠型的摄像装置中,将通过光入射到光电转换部中而生成的电荷用设在各像素中的像素电极来收集,并向电荷储存区域储存。通过将储存在电荷储存区域中的电荷使用信号检测电路读出,能够得到与各像素的光量对应的电信号。即,在层叠型的摄像装置中,收集通过光电转换产生的电荷的像素电极在像素间相互被电分离。典型地,在相互邻接的两个像素电极之间存在间隙。因此,有时入射到光电转换部中的光的一部分穿过像素电极间的空隙。穿过像素电极间的间隙后的光有时通过例如在光电转换部与半导体基板之间反复乱反射而到达半导体基板上的晶体管的沟道区域。

[0109]

如果这样的漫射光入射到半导体基板上的晶体管的沟道区域中,则在沟道区域中发生光激励载流子。如果在沟道区域中发生光激励载流子,则在信号中加入了噪声,画质下降。此外,沟道区域中的光激励载流子的生成可能成为晶体管的误动作的原因。因而,能够抑制穿过像素电极间的间隙后的光到达半导体基板上的晶体管的沟道区域是有益的。

[0110]

参照图5。图5表示从半导体基板2的法线方向观察时的光电转换元件15的第2电极15c及第1电容元件cs的上部电极41c的典型的配置。在图5中,表示4个单位像素单元10和表示各像素的边界的假想线px。

[0111]

如图5所示,在相互邻接的第2电极15c之间,存在用来将第2电极15c电分离的间隙。在图5所例示的结构中,在各单位像素单元10中,第1电容元件cs的上部电极41c具有比光电转换元件15的第2电极15c大的面积。即,上部电极41c的至少一部分与第2电极15c间的间隙重叠。

[0112]

通过使用遮光性的电极作为上部电极41c、并在形成于第2电极15c间的间隙的正下方配置上部电极41,能够将穿过了形成在第2电极15c间的间隙的光通过上部电极41c来遮挡。由此,能够抑制穿过了形成在第2电极15c间的间隙的光入射到半导体基板2上的晶体管(例如信号检测晶体管34)的沟道区域中。上部电极41c例如是金属电极或金属氮化物电极。用来形成上部电极41c的材料的例子是ti、tin、ta、tan及mo。这里使用tan。例如,通过作为上部电极41c而形成厚度为100nm的tan电极,能够实现充分的遮光性。

[0113]

根据本发明的实施方式,能够抑制漫射光向半导体基板2上的晶体管的沟道区域的入射而抑制晶体管的特性的变动(例如阈值电压的变动)。通过抑制漫射光向半导体基板2上的晶体管的沟道区域的入射,各像素的晶体管的特性稳定化,能够减小多个像素间的晶体管的动作的偏差。这样抑制漫射光向半导体基板2上的晶体管的沟道区域的入射,会贡献于摄像装置的可靠性的提高。

[0114]

另外,在图5中,例示了通过将上部电极41c在空间上分离、在单位像素单元10之间将上部电极41c电分离的结构。即,在该例中,上部电极41c不将感光区域的整体覆盖,在相互邻接的上部电极41c之间稍稍形成有间隙。

[0115]

但是,如参照图3说明那样,这里,上部电极41c中的每一个构成为,分别经由灵敏度调整线32被供给规定的电压。因此,能够使相互邻接的上部电极41c间的距离与相互邻接的第2电极15c间的距离相比充分变小。因而,能够将穿过了形成在第2电极15c间的间隙的光的大部分通过上部电极41c来遮挡。另外,在图2所例示的电路结构中,对属于同一行的单位像素单元10中的上部电极41c施加共同的电压。因而,也可以将跨越多个列沿着行方向延伸的多个带状的电极形成为上部电极41c。在此情况下,由于在沿着行方向邻接的单位像素单元10间不发生上部电极间的间隙,所以能够进一步抑制漫射光向半导体基板2上的晶体

管的沟道区域的入射。当然,也可以如图5所示那样将上部电极41c按照每个单位像素单元10在空间上分离,按照各单位像素单元10的每个上部电极41c供给独立的电压。

[0116]

在图5所例示的结构中,将光电转换元件15的第2电极15c与第2电容元件cc的上部电极42e连接的通孔vc被配置在单位像素单元10的中央附近。这里,第1电容元件cs的上部电极41c形成为,将作为连接部cn的一部分的通孔vc包围。如上述那样,通过经由灵敏度调整线32供给规定的电压,摄像装置100动作时的第1电容元件cs的上部电极41c的电位被维持为一定的电位。因此,通过用电位被固定的上部电极41c将连接光电转换元件15的第2电极15c和信号检测晶体管34的栅极电极34e的连接部cn(这里是作为其一部分的通孔vc)包围,能够使上部电极41c作为屏蔽电极发挥功能。通过上部电极41c作为屏蔽电极发挥功能,能够抑制噪声向电荷储存节点44的混入。例如,在邻接的单位像素单元中产生的电噪声能在到达连接部cn之前被第1电容元件cs的上部电极41c吸收。

[0117]

在图5所例示的结构中,上部电极41c具有矩形状,在其中央附近具有矩形状的开口部ap。但是,从半导体基板2的法线方向观察时的第1电容元件cs的上部电极41c的形状并不限定于图5所示的形状。例如,也可以通过设置将开口部ap与上部电极41c连结的切缝,从而使得上部电极41c具有c字状。此外,例如上部电极41c也可以包括多个部分。但是,从减小单位像素单元10内的电容的偏倚的观点来看,将连接部cn配置到单位像素单元10的中央、将上部电极41c的形状形成为关于连接部cn对称性较高的形状是有益的。另外,也可以是代替将第1电容元件cs的上部电极41c的电位固定而将第1电容元件cs的下部电极41b的电位固定,并将第1电容元件cs的上部电极41c和第2电容元件cc的下部电极42b电连接那样的结构。在此情况下,只要将第1电容元件cs的下部电极41b形成为将连接部cn包围就可以。

[0118]

再次参照图3。如上述那样,上部电极41c例如可以由金属或金属氮化物形成。位于将上部电极41c覆盖的绝缘层4c上的光电转换元件15的第2电极15c也同样,可以由金属或金属氮化物形成。也可以由与构成上部电极41c的材料相同的材料形成第2电极15c。

[0119]

在图3所例示的结构中,通过使用金属氮化物(这里是tan),将上部电极41c形成为遮光性的电极。这里,作为用来形成光电转换元件15的第2电极15c的材料而使用金属氮化物。用来形成光电转换元件15的第2电极15c的材料的例子是tin、tan、wn。

[0120]

金属氮化物致密性良好,具有在高温下也不易发生杂质元素的移动及/或混入的性质。因此,通过将位于第1电容元件cs的电介质膜41d的上方的上部电极41c和第2电极15c使用金属氮化物来形成,能够抑制由杂质导致的载流子向电介质膜41d的混入。通过抑制杂质向电介质膜41d的混入,能够减少第1电容元件cs的上部电极41c与下部电极41b之间的泄漏电流。

[0121]

此外,金属氮化物由于在溅镀中不易发生迁移(migration),所以容易形成平坦的表面。如果使用金属氮化物形成光电转换元件15的第2电极15c,则能够实现经由平坦的界面的接合。通过抑制第2电极15c的表面的凹凸,能够实现第2电极15c与光电转换膜15b之间的顺畅的电荷输送。此外,能够抑制由界面缺陷导致的能级的发生,能够抑制暗电流。这样,如果将第1电容元件cs的上部电极41c及光电转换元件15的第2电极15c的两者用金属氮化物形成,则从泄漏电流及暗电流减小的观点看是有益的。进而,如果使用金属氮化物形成第1电容元件cs的下部电极41b,则能够使上部电极41c的平坦性进一步提高,所以是有益的。此外,由于能够抑制电介质膜41d的氧化,所以是有益的。

[0122]

(实施方式2)

[0123]

图6示意地表示本发明的实施方式2的单位像素单元10a的截面。图6所示的单位像素单元10a与参照图3说明的单位像素单元10之间的不同点是,单位像素单元10a具有形成在与光电转换元件15的第2电极15c同层中的屏蔽电极15sd。屏蔽电极15sd配置在相互邻接的两个单位像素单元10a间。此外,屏蔽电极15sd构成为,在摄像装置100动作时被供给一定的电压。

[0124]

在层叠型的摄像装置中,有时由某个单位像素单元的光电转换膜生成的电荷被与该单位像素单元不同的其他单位像素单元的像素电极收集。例如,如果在单位像素单元的边界附近生成电荷,则该电荷有时被与本来应朝向的像素电极不同的其他像素电极(例如邻接的单位像素单元中的像素电极)收集。电荷被从邻接的像素收集可能成为混色的原因。通过将被保持为一定的电位的屏蔽电极设在单位像素单元间,能够抑制向邻接的像素的意图之外的电荷移动。即,能够减少混色的发生。

[0125]

图7表示从半导体基板2的法线方向观察时的屏蔽电极15sd、光电转换元件15的第2电极15c及第1电容元件cs的上部电极41c的典型的配置。在图示的例子中,屏蔽电极15sd形成为包括沿着单位像素单元10a间的边界延伸的多个部分的栅格状。这里,屏蔽电极15sd电连接在设在与第1电容元件cs的上部电极41c同层中的连接部41k(在图6中未图示)上。屏蔽电极15sd构成为通过经由连接部41k电连接在未图示的电源上,而可施加一定的电压。

[0126]

通过以将光电转换元件15的第2电极15c包围的方式配置屏蔽电极15sd,能够减小相互邻接的单位像素单元10a间的寄生电容而抑制噪声。在图示的例子中,屏蔽电极15sd具有将光电转换元件15的第2电极15c包围的配置,在屏蔽电极15sd与第2电极15c之间,形成有用来将它们电分离的间隙。入射到该间隙中的光可能成为形成在半导体基板上的晶体管的特性变动的原因。在图7所例示的结构中,在该间隙的正下方配置有第1电容元件cs的上部电极41c。因此,通过将上部电极41c形成为遮光性的电极,能够将从屏蔽电极15sd与第2电极15c之间入射的光用上部电极41c遮挡,能够实现晶体管的特性的稳定化。

[0127]

另外,在图7所例示的结构中,为了向屏蔽电极15sd施加一定的电荷,在与第1电容元件cs的上部电极41c同层中配置有连接部41k。向屏蔽电极15sd施加的电压典型地与向上部电极41c施加的电压不同。因此,在图示的结构中,通过在连接部41k与上部电极41c之间设置间隙,将连接部41k与上部电极41c电绝缘。由于连接部41k与上部电极41c之间的间隙相比屏蔽电极15sd与第2电极15c之间的间隙充分小,所以穿过了屏蔽电极15sd与第2电极15c之间的间隙的光的大部分被上部电极41c遮挡。当然,屏蔽电极15sd也可以具有将连接部41k与上部电极41c之间的间隙覆盖的形状。

[0128]

另外,在日本特开2010-067827号公报中,公开了在滤色器内或光电转换元件内设有用来防止混色的隔壁的构造。但是,如果将这样的隔壁设在单位像素单元内,则光电转换膜中的实质上贡献于光电转换的部分被减少。此外,因不能得到充分的光量,难以将像素尺寸缩小。进而,通常难以将高纵横比的隔壁形成在单位像素单元内,生产性有可能下降。

[0129]

根据本发明的实施方式,能够比较容易地将屏蔽电极15sd设在与光电转换元件15的第2电极15c同层中。根据本发明的实施方式,由于能够在不在单位像素单元内形成隔壁的情况下抑制混色,所以制造工序不会复杂化。

[0130]

(摄像装置100的动作的概略)

[0131]

接着,参照附图说明摄像装置100的动作的一例。如以下说明那样,根据参照图2说明的结构,通过适当地控制两个复位晶体管36及38的栅极电压,能够切换灵敏度不同的两个动作模式。这里说明的两个动作模式是能够以比较高的灵敏度摄像的第1模式、以及能够以比较低的灵敏度摄像的第2模式。

[0132]

以下,说明第1模式的摄像装置100的动作的概略。第1模式是适合于低照度下的摄像的模式。在低照度下,灵敏度较高是有益的。但是,如果灵敏度比较高,则噪声也有可能被放大。根据本发明的实施方式,能够在实现比较高的灵敏度的同时,将ktc噪声的影响减小及/或除去。

[0133]

图8是用来说明第1模式的晶体管的动作的一例的时序图。在图8中,add、rst1及rst2分别示意地表示寻址晶体管40的栅极电压、第1复位晶体管36的栅极电压及第2复位晶体管38的栅极电压的变化。在图8所示的例子中,在时刻t0,寻址晶体管40、第1复位晶体管36及第2复位晶体管38都是off。为简单起见,以下省略电子开闭器的动作的说明。

[0134]

首先,通过控制寻址信号线30的电位,使寻址晶体管40成为on(时刻t1)。此时,进行储存在电荷储存节点44中的信号电荷的读出。

[0135]

接着,通过控制复位信号线26及反馈控制线28的电位,使第1复位晶体管36及第2复位晶体管38成为on(时刻t2)。由此,电荷储存节点44和反馈线25经由第1复位晶体管36及第2复位晶体管38被连接,形成使信号检测电路sc的输出负反馈的反馈电路fc。对共用反馈线25的多个单位像素单元10中的1个,执行反馈电路fc的形成。

[0136]

这里,反馈电路fc是包括信号检测晶体管34、反转放大器24及第2复位晶体管38的负反馈放大电路。在时刻t1被设为on的寻址晶体管40,将信号检测晶体管34的输出作为对于反馈电路fc的输入供给。

[0137]

通过将电荷储存节点44与反馈线25电连接,将电荷储存节点44复位。此时,通过将信号检测电路sc的输出负反馈,垂直信号线18的电压收敛于施加在反转放大器24的负正侧的输入端子上的电压vref。即,在该例中,复位的基准电压是电压vref。在图2所例示的结构中,能够在电源电压(例如3.3v)与接地(0v)的范围内任意地设定电压vref。换言之,作为复位的基准电压,只要是一定的范围内,可以利用任意的电压(例如电源电压以外的电压)。

[0138]

接着,使第1复位晶体管36成为off(时刻t3)。以下,有时将从在时刻t2使第1复位晶体管36及第2复位晶体管38成为on起到使第1复位晶体管36成为off为止的期间(图8中的时刻t2~时刻t3)称作“复位期间”。在图8中,将复位期间用箭头rst示意地表示。通过在时刻t3使第1复位晶体管36成为off,产生ktc噪声。因此,在复位后的电荷储存节点44的电压中加入了ktc噪声。

[0139]

参照图2可知,第2复位晶体管38为on的期间中,形成有反馈电路fc的状态持续。因此,如果设反馈电路fc的增益为a,则通过在时刻t3使第1复位晶体管36成为off产生的ktc噪声被消除到1/(1 a)的大小。

[0140]

在该例中,使即将第1复位晶体管36成为off之前(噪声消除即将开始之前)的垂直信号线18的电压与施加在反转放大器24的负侧的输入端子上的电压vref大致相等。这样,通过使噪声消除开始时的垂直信号线18的电压接近于噪声消除后的目标电压vref,能够在比较短的时间中将ktc噪声消除。以下,有时将从使第1复位晶体管36成为off起到使第2复位晶体管38成为off为止的期间(图8中的时刻t3~时刻t4)称作“噪声消除期间”。在图8中,

将噪声消除期间用箭头ncl示意地表示。

[0141]

这样,根据本发明的实施方式,将通过使复位晶体管成为off而产生的ktc噪声缩小,并将产生的ktc噪声在比较短的时间中消除成为了可能。

[0142]

接着,使第2复位晶体管38成为off(时刻t4),在规定的期间中执行曝光。通过在时刻t4使第2复位晶体管38成为off,产生ktc噪声。此时,对电荷储存节点44的电压加上的ktc噪声的大小是在单位像素单元10中不设置第1电容元件cs及第2电容元件cc而将第2复位晶体管38直接连接于电荷储存节点44的情况下的(cfd/c1)

1/2

×

(c2/(c2 cfd))倍。在上式中,cfd、c1及c2分别表示电荷储存节点44的电容值、第1电容元件cs的电容值及第2电容元件cc的电容值。另外,式中的

“×”

表示乘法运算。这样,第1电容元件cs的电容值c1越大,产生的噪声本身越小,第2电容元件cc的电容值c2越小,衰减率越大。因而,根据本发明的实施方式,通过适当地设定第1电容元件cs的电容值c1及第2电容元件cc的电容值c2,能够将通过使第2复位晶体管38成为off而产生的ktc噪声充分缩小。

[0143]

在图8中,将曝光的期间用箭头exp示意地表示。在曝光的期间中,在规定的定时进行消除了ktc噪声的复位电压的读出(时刻t5)。另外,由于在复位电压的读出中需要的时间是短时间,所以也可以在寻址晶体管40的on状态为持续不变的情况下执行复位电压的读出。

[0144]

通过取在时刻t1与时刻t2之间读出的信号与在时刻t5读出的信号的差,能够得到除去了固定噪声的信号。这样,能够得到除去了ktc噪声及固定噪声的信号。

[0145]

另外,在使第1复位晶体管36及第2复位晶体管38为off的状态下,第1电容元件cs经由第2电容元件cc连接在电荷储存节点44上。这里,设想不经由第2电容元件cc而将电荷储存节点44与第1电容元件cs直接连接的情况。在此情况下,将第1电容元件cs直接连接时的信号电荷的储存区域整体的电容值是(cfd c1)。即,如果第1电容元件cs具有比较大的电容值c1,则信号电荷的储存区域整体的电容值也为较大的值,所以不能得到较高的转换增益(也可以说是较高的sn比)。所以,在本发明的实施方式中,经由第2电容元件cc将第1电容元件cs连接在电荷储存节点44上。将这样的结构中的信号电荷的储存区域整体的电容值表示为(cfd (c1c2)/(c1 c2))。这里,在第2电容元件cc具有比较小的电容值c2、并且第1电容元件cs具有比较大的电容值c1的情况下,信号电荷的储存区域整体的电容值大约为(cfd c2)。即,信号电荷的储存区域整体的电容值的增加较小。这样,通过经由具有比较小的电容值的第2电容元件cc将第1电容元件cs连接到电荷储存节点44上,能够抑制转换增益的下降。

[0146]

另外,也可以将第2复位晶体管38的源极或漏极与电源配线22连接,作为复位的基准电压而使用电源电压。在此情况下,也能够得到将通过使第1复位晶体管36成为off而产生的ktc噪声消除的效果、以及将通过使第2复位晶体管38成为off而产生的ktc噪声缩小的效果。

[0147]

(摄像装置的变形例)

[0148]

图9示意地表示单位像素单元的另一例示性的电路结构。图9所例示的单位像素单元10b与参照图2说明的单位像素单元10的不同点是,在单位像素单元10b中,复位晶体管36的源极及漏极中的没有连接在电荷储存节点44上的一侧不是连接在复位漏极节点46上、而是连接在反馈线25上。单位像素单元10b的设备构造可以与参照图3及图6说明的设备构造

大致同样。

[0149]

在图9所例示的结构中,不能进行参照图8说明的第1模式和第2模式的切换。但是,由于将复位晶体管36的源极及漏极中的没有连接在电荷储存节点44上的一侧直接连接在反馈线25上,所以能够得到提高用来确保复位晶体管36的驱动力的杂质谱(impurity profile)的设计自由度的优点。另外,图9所例示的结构中的各晶体管的动作定时与上述第1模式是同样的。

[0150]

标号说明

[0151]

2半导体基板

[0152]

2s元件分离区域

[0153]

2d杂质区域

[0154]

2ds源极区域

[0155]

2dd漏极区域

[0156]

4a、4b、4c、4s绝缘层

[0157]

6s、6a、6b、6c配线层

[0158]

10、10a、10b单位像素单元

[0159]

15光电转换元件

[0160]

15a第1电极

[0161]

15b光电转换膜

[0162]

15c第2电极(像素电极)

[0163]

15h受光面

[0164]

15sd屏蔽电极

[0165]

16垂直扫描电路

[0166]

17储存控制线

[0167]

18垂直信号线

[0168]

19负荷电路

[0169]

20纵列信号处理电路

[0170]

21水平信号读出电路

[0171]

22电源配线

[0172]

23水平共用信号线

[0173]

24反转放大器

[0174]

25反馈线

[0175]

26复位信号线

[0176]

28反馈控制线

[0177]

30寻址信号线

[0178]

32灵敏度调整线

[0179]

34信号检测晶体管(放大晶体管)

[0180]

36第1复位晶体管

[0181]

38第2复位晶体管

[0182]

34e、36e、38e栅极电极

[0183]

34g、36g、38g栅极绝缘膜

[0184]

34c、36c、38c沟道区域

[0185]

40寻址晶体管

[0186]

cs第1电容元件

[0187]

41b第1电容元件cs的下部电极

[0188]

41c第1电容元件cs的上部电极

[0189]

41d电介质膜

[0190]

41p保护膜

[0191]

41t上部电极41c的连接部

[0192]

41g上部电极41c的下表面

[0193]

41k连接部

[0194]

cc第2电容元件

[0195]

42b第2电容元件cc的下部电极

[0196]

42e第2电容元件cc的上部电极

[0197]

43端子

[0198]

44电荷储存节点

[0199]

45配线

[0200]

46复位漏极节点

[0201]

49多晶硅配线

[0202]

70多层配线构造

[0203]

cn连接部

[0204]

fc反馈电路

[0205]

pc光电转换部

[0206]

sc信号检测电路

[0207]

px单位像素单元10的边界线

[0208]

100摄像装置

[0209]

s1配线层(多晶硅层)

[0210]

cp1、cpa接触插塞

[0211]

va、vb、vd通孔

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。