1.本发明涉及半导体技术领域,尤其涉及一种用于重分布层的互连结构和半导体封装。

背景技术:

2.近年来,随着设计复杂度的增加,业界已经提出了用于系统集成的先进封装技术。例如,扇出晶圆级芯片级封装(fan

‑

out wafer

‑

level chip

‑

scale package,fo

‑

wlcsp)提供了一种有前途的替代方案,该方案具有小尺寸,更好的信噪比和改进的热特性。

3.如本领域中已知的,微凸块(micro

‑

bump)和重分布层(redistribution layer,rdl)用于多芯片fo

‑

wlcsp中,以连接相邻芯片以及连接到扇出芯片上的输入/输出(input/output,i/o)焊盘上。rdl可以是芯片的上层金属层,并且多个芯片在多芯片fo

‑

wlcsp中共用相同的rdl。在现代ic设计中,i/o焊盘通常沿着芯片的边界放置,rdl用于将i/o焊盘重新分配到受控的塌陷芯片连接(controlled collapse chip connection,c4)凸块焊盘,或连接不同芯片之间i/o焊盘。i/o焊盘可以重新分配到芯片外部的扇出区域,以增加引脚数。

4.c4凸块是扇出芯片封装和电路基板(例如,封装基板)之间的界面。众所周知,由于热膨胀系数不匹配(或cte(coefficient of thermal expansion,热膨胀系数)不匹配),c4凸块通常承受较大的应力。因此,c4凸块的尺寸和间距大于i/o焊盘或微型凸块的尺寸和间距。这导致c4凸块位置可能与其对应的i/o焊盘或微型凸块位置不同。

5.通常,焊盘到凸块(即i/o焊盘到c4凸块焊盘)的相对位置数以千计,因此在rdl布线的设计过程中会生成数千种通孔和焊盘互连图案,这不可避免地增加了运行时间(runtime),并使rdl电路设计过程变得繁重。

技术实现要素:

6.有鉴于此,本发明提供一种用于重分布层的互连结构和半导体封装,以解决上述问题。

7.根据本发明的第一方面,公开一种用于重分布层的互连结构,包括:

8.中间通孔焊盘;

9.一个或一簇上导电通孔,邻接该中间通孔焊盘,并且将该中间通孔焊盘电耦接到上通孔焊盘;以及

10.下导电通孔,将该中间通孔焊盘与该下电路焊盘电耦接,其中,该下导电通孔布置在沿该中间通孔焊盘的周边延伸的马蹄形通孔区域内。

11.根据本发明的第二方面,公开一种半导体封装,包括:

12.至少一个半导体晶粒;

13.模塑料,围绕该半导体晶粒的;以及

14.重分布层,设置在该模塑料的下表面上,其中,该至少一个半导体晶粒电连接至该重分布层的互连结构,其中,该互连结构包括:

15.中间通孔焊盘;

16.一个或一簇上导电通孔,邻接该中间通孔焊盘,并且将该中间通孔焊盘电耦接到该上通孔焊盘;以及

17.下导电通孔,将该中间通孔焊盘与该下电路焊盘电耦接,其中,该下导电通孔布置在沿该中间通孔焊盘的周边延伸的马蹄形通孔区域内。

18.根据本发明的第三方面,公开一种用于重分布层的互连结构,包括:

19.中间通孔焊盘;

20.一个或一簇上导电通孔,邻接该中间通孔焊盘,并且将该中间通孔焊盘电耦接到该上通孔焊盘;和

21.下导电通孔,将该中间通孔焊盘与该下电路焊盘电耦接,其中,该一个或一簇上导电通孔设置在该中间通孔焊盘上的该上通孔焊盘的投影区域内,其中该下导电通孔布置在投影区域外部的中间通孔焊盘的其余部分上,并且不与该上导电通孔簇重叠。

22.本发明的用于重分布层的互连结构由于该下导电通孔布置在沿该中间通孔焊盘的周边延伸的马蹄形通孔区域内。因此本发明中上导电通孔不与下导电通孔重叠,因此避免了应力沿垂直方向传递,可以减轻电路设计人员的负担,并且可以显着减少运行时间;并且本发明的上述方式可以方便重分布层中上导电通孔与下导电通孔之间的布局设计,当上导电通孔或下导电通孔因设计要求需要改变位置时,可以通过旋转的方式改变上导电通孔或下导电通孔的位置,从而满足不同的设计需求,具有更好的设计弹性和灵活性。

附图说明

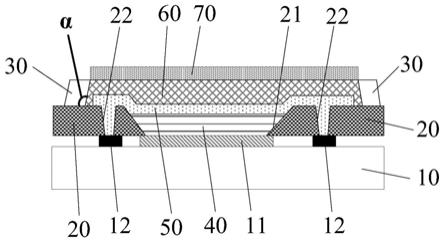

23.图1是示出根据本发明的一个实施例的示例性扇出封装的示意性截面图;

24.图2是根据本发明的一个实施例的示例性互连结构的俯视自上向下的透视图,该互连结构包括中间通孔焊盘(intermediate via land pad),邻接该中间通孔焊盘的一个或一簇(cluster)上导电通孔以及下导电通孔;

25.图3是示出图2中的中间通孔焊盘、上导电通孔和下导电通孔的相对位置的示意性截面图;

26.图4是图2中的示例性互连结构的透视侧视图;以及

27.图5至图7示出了根据本发明的一些实施例的下导电通孔的示例性旋转操作,该下导电通孔布置在通孔区域内以避免通孔重叠。

具体实施方式

28.以下描述是实施本发明的最佳构想模式。进行该描述是为了说明本发明的一般原理,而不应被认为是限制性的。本发明的范围由所附权利要求书确定。

29.在下文中,参考附图对本发明构思进行全面描述,在附图中示出了本发明构思的示例性实施例。根据以下示例性实施例,本发明构思的优点和特征以及实现它们的方法将变得显而易见,所述实施例将参考附图进行更详细地描述。然而,应当注意,本发明构思不限于以下示例性实施例,并且可以以各种形式实现。因此,提供示例性实施例仅是为了公开发明构思,并且使本领域技术人员知道发明构思的类别。而且,所示的附图仅是示意性的,并且是非限制性的。在附图中,出于说明的目的,一些元件的尺寸可能被放大并且未按比例

绘制。在本发明的实践中,尺寸和相对尺寸不对应于实际尺寸。

30.本文所使用的术语仅出于描述特定实施例的目的,并不旨在限制本发明。如本文所使用的,单数术语“一”、“一个”和“该”也旨在包括复数形式,除非上下文另外明确指出。如本文所使用的,术语“和/或”包括一个或多个相关联的所列项目的任何和所有组合。应该理解的是,当一个元件称为“连接”或“接触”到另一个元件时,它可以直接连接或接触另一个元件,或者可以存在中间元件。

31.类似地,应当理解,当诸如层、区域或基板的元件称为在另一元件“上”时,其可以直接在另一元件上,或者可以存在中间元件。相反,术语“直接”是指不存在中间元件。应该理解的是,当在本文中使用时,术语“包括”,和/或“包含”规定了所陈述的特征、整数、步骤、操作、元件和/或部件的存在,但是不排除存在或增加一个或多个其他特征、整数、步骤、操作、元件、部件和/或其组合。

32.现在将参考附图描述本发明的一个或多个实施方式,其中,贯穿全文,相似的附图标记用于指代相似的元件,并且其中所示的结构不必按比例绘制。在整个说明书中,术语“晶粒”、“半导体芯片”和“半导体晶粒”可以互换使用。

33.请参考图1。图1是示出根据本发明的一个实施例的示例性扇出封装的示意性截面图。如图1所示,扇出封装1(可以称为半导体封装)可以包括至少两个电耦接到重分布层(redistribution layer,rdl)20的半导体晶粒11和12。rdl(或rdl插入层(interposer))可以通过在晶圆表面上添加金属层和介电层来定义,以将i/o布局重新布线为更宽松的间距尺寸。这种重分布(层)需要薄膜聚合物(例如苯并环丁烯(benzocyclobutene,bcb)、聚酰亚胺(polyimide,pi)或其他有机聚合物和金属化材料(例如铝(al)或铜(cu)),以将外围焊盘重新布线(reroute)为区域配置(area array configuration)。

34.根据本发明的实施例,例如,rdl 20可以包括至少一个介电层201和至少一个金属层202。介电层201可以包括诸如氮化硅、氧化硅或类似的无机材料,但不限于此。根据本发明的实施例,介电层201可以包括聚合物材料,但不限于此。金属层202可以包括铝、铜、钨、钛、氮化钛等。应当理解,金属层202可以包括多层金属迹线,并且介电层201可以包括多层介电层压板。

35.根据本发明的实施例,翻转(flip)晶粒11和12,使得有源表面(active surface)11a和12a直接面向rdl 20。在晶粒11的有源表面11a上,多个输入/输出(i/o)焊盘111可以例如沿着其有源表面11a的周边设置。同样,在晶粒12的有源表面12a上,例如,可以沿着其有源表面的周边设置多个i/o焊盘121。晶粒11和12的有源表面11a和12a可以由钝化层130共形地(conformally)覆盖。

36.根据本发明的实施例,晶粒11和12可以包括端子(terminal)112和122,其包括但不限于分别设置在i/o焊盘111和121上的金属凸块或微凸块,这些金属凸块或微凸块设置在翻转的有源表面11a和12a上。根据本发明的实施例,端子112和122可以包括大约20

‑

50微米的凸块间距,但不限于此。可选地,诸如介电层或聚合物层的平坦化层210可以被施加在钝化层130上并且可以围绕端子112和122。

37.根据本发明的实施例,晶粒11和12可以被诸如模塑料30的密封剂围绕并支撑。模塑料30可以具有与平坦化层210的下表面210a齐平的下表面30a。模塑料30可以具有与晶粒11和12的后表面11b和12b齐平的上表面30b。可以在芯片级封装制程期间对模塑料30进行

固化制程。根据本发明的实施例,模塑料30可以包括环氧树脂和二氧化硅填充剂的混合物,但不限于此。

38.rdl 20可以包括多层导电通孔,例如v1

‑

v3、通孔焊盘(例如p2、p3)、多层导电迹线(例如t2和t3)、以及凸块焊盘bp,以扇出i/o焊盘111和121至c4凸块sb在rdl 20的下表面上,以具有较宽松的节距(例如微米)。c4凸块sb分别形成在凸块焊盘bp上。为了简单起见,在图1中仅示出了三层导电通孔(例如v1

‑

v3)、以及两层通孔焊盘(例如p2、p3)。通孔和焊盘可能会根据设计要求而有所不同。

39.例如,在图1中,rdl 20可以包括通用互连结构is,其包括中间通孔焊盘pn、与中间通孔焊盘pn邻接并将中间通孔焊盘pn电耦接到上通孔焊盘pn

‑

1的一个或一簇上导电通孔vn

‑

1、以及将中间通孔焊盘pn与下电路焊盘pn 1电耦接的下导电通孔vn。在一些实施例中,下电路焊盘pn 1可以是凸块焊盘,但不限于此。

40.根据本发明的实施例,在基于有利的扇出晶圆级芯片规模(fan

‑

out wafer

‑

level chip

‑

scale)平台实施rdl电路设计时,经过发明人研究之后,认为需要考虑或满足以下条件。首先,考虑到电迁移(electromigration,em)和ir性能,在互连结构is中,相对于每个邻接的通孔焊盘(或凸块焊盘)有一个以上的通孔(标准(criterion)a)。例如,一个或一簇上导电通孔vn

‑

1可以包括个通孔,并且下导电通孔vn可以包括个通孔,但不限于此,例如下导电通孔vn的数量也可以是1个、2个3个或更多。第二,为了避免应力沿垂直方向传递,一个或一簇上导电通孔vn

‑

1不与下导电通孔vn重叠(标准b)。

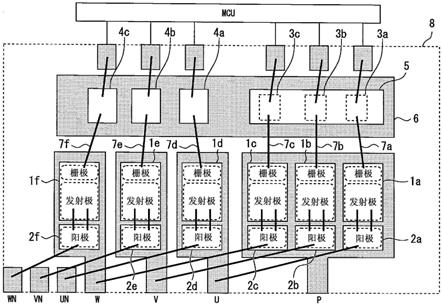

41.请参考图2至图4。图2是示出示例性互连结构的俯视透视图,根据本发明的实施例,该互连结构包括中间通孔焊盘、与该中间通孔焊盘邻接的一个或一簇上导电通孔以及下导电通孔。图3是示出了图2中的中间通孔焊盘、上导电通孔和下导电通孔的相对位置的示意性截面图。图4是图2中的示例性互连结构的侧视透视图,其中相同的数字或卷标表示相似的层、区域或元素。

42.为了清楚起见,忽略了示例性互连结构的介电层或聚合物层。应当理解,通孔焊盘的形状仅用于说明目的。在一些实施例中,通孔焊盘可以具有圆形、矩形、正方形、多边形、椭圆形或不规则形状,但不限于此。

43.如图2至图4所示,根据一个实施例,例如,通用互连结构is包括中间通孔焊盘pn、与该中间通孔焊盘pn邻接并将中间通孔焊盘pn电耦接到上通孔焊盘pn

‑

1的一个或一簇上导电通孔vn

‑

1、以及将中间通孔焊盘pn电耦接到下电路焊盘pn 1的下导电通孔vn。图4还示出了示例性的c4凸块sb可以设置在从下电路焊盘pn 1延伸的凸块焊盘上。

44.应当理解,根据各种实施例,中间通孔焊盘pn可以包括圆形、矩形、正方形、多边形、椭圆形或不规则形状。应当理解,根据各种实施例,上通孔焊盘pn

‑

1可以包括圆形、矩形、正方形、边形、椭圆形或不规则形状。应当理解,根据各种实施例,中间通孔焊盘pn可以具有与上通孔焊盘pn

‑

1的形状不同的形状。应当理解,根据各种实施例,中间通孔焊盘pn和上通孔焊盘pn

‑

1可以具有相同的形状。

45.根据本发明的一个实施例,例如,中间通孔焊盘pn和上通孔焊盘pn

‑

1都可以具有圆形形状,并且当从上方观察时可以相对于中心轴ax同心。一个或一簇上导电通孔vn

‑

1可以设置在半径为r的中间通孔焊盘pn上的半径为r的投影区域ppr内。投影面积ppr基本上等于上通孔焊盘pn

‑

1的上表面面积。中间通孔焊盘pn的位于投影区域ppr外部的其余部分被

定义为具有均匀宽度(等于r

‑

r)的环形区域ra,可以通过与中心轴ax相交的中心虚线cl将其划分为两个镜像对称的马蹄形(或c形或弯曲的带状)区域。根据本发明的一个实施例,将两个镜面对称的马蹄形区域之一(环形区域ra的一半)定义为通孔区域var(用虚线表示)。根据本发明的实施例,下导电通孔vn仅被允许布置在假想的马蹄形通孔区域var内,该区域沿着中间通孔焊盘pn的周长延伸,其大约为环形区域ra的一半,或者马蹄形通孔区域var可以小于等于环形区域ra的一半(例如马蹄形通孔区域var的面积可以小于等于环形区域ra的面积的一半)。本发明的上述方式可以方便rdl中上导电通孔与下导电通孔之间的布局设计,当上导电通孔或下导电通孔因设计要求需要改变位置时,可以通过如下所述的旋转的方式改变上导电通孔或下导电通孔的位置,从而满足不同的设计需求,具有更好的设计弹性和灵活性。在一个实施例中,下导电通孔vn可以包括多个通孔(例如个),以形成下导电通孔阵列;此外上导电通孔vn

‑

1也可以是多个;下导电通孔或/和上导电通孔为多个的设置可以提高电性能,同时多个下导电通孔和多个上导电通孔通过进行上述旋转不会重叠(例如从俯视或仰视的透视图去看不会重叠,或者它们在竖直方向上的投影不会重叠,或者它们在中间通孔焊盘pn上的竖直方向上的投影不会重叠等等),因此本实施例在提高电性能的同时满足了提高设计弹性的需求。此外,多个下导电通孔可以均匀的分布在马蹄形通孔区域var内,以提高电性能,使信号的传递更加均匀。多个上导电通孔可以均匀的分布在中间通孔焊盘pn内,以提高电性能,使信号的传递更加均匀。

46.在某些情况下,当从上方观察时,中间通孔焊盘pn和上通孔焊盘pn

‑

1相对于中心轴ax不同心,则可以通过简单地围绕中心轴ax旋转下导电通孔vn以及假想的通孔区域var即可满足上述标准b。具体可以参考以下实施例的描述。

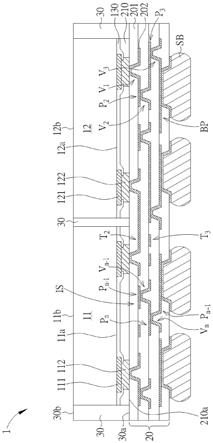

47.图5示出了布置在通孔区域var内的下导电通孔vn的示例性旋转操作。例如,在图5中,一个或一簇上导电通孔vn

‑

1包括两个导电通孔,并且下导电通孔vn包括五个导电通孔。如图5所示,上通孔焊盘pn

‑

1与中间通孔焊盘pn的中心轴线ax偏移。为了避免下导电通孔vn和上导电通孔vn

‑

1之间的重叠,通过实施var的旋转操作,使下导电通孔vn与假想的通孔区域var一起绕中心轴ax旋转。

48.图6示出了布置在通孔区域var内的下导电通孔vn的另一示例性旋转操作。例如,在图6中,一个或一簇上导电通孔vn

‑

1可以包括四个导电通孔,并且下导电通孔vn可以包括六个导电通孔。中间通孔焊盘pn和上通孔焊盘pn

‑

1可以具有矩形形状。如图6所示,上通孔焊盘pn

‑

1与中间通孔焊盘pn的中心轴线ax偏移。为了避免下导电通孔vn和上导电通孔vn

‑

1之间的重叠,通过执行var的旋转操作,使下导电通孔vn和中间通孔焊盘pn绕中心轴ax旋转。因此本实施例中,如图2所示的环形区域ra可以是圆环或者方形环或者其他形状的环形,而如图2所示的马蹄形通孔区域var也可以相对应的为半圆环形、或者方形环的一半、或者其他形状的环形的一半(当然如上所述,也可以小于等于一半),因此马蹄形通孔区域var也可以是半个方形环或其他的形状的环。马蹄形通孔区域var可以小于等于环形区域ra的一半的方式可以在执行var的旋转操作时更容易的避免下导电通孔vn和上导电通孔vn

‑

1之间的重叠,具有更好的设计弹性和布局的灵活性,方便通孔的设计和布线的布局。

49.图7示出了布置在通孔区域var内的下导电通孔vn的又一示例性旋转操作。例如,在图7中,上导电通孔vn

‑

1的簇可以包括四个导电通孔,并且下导电通孔vn可以包括五个导电通孔。中间通孔焊盘pn可以具有圆形形状,而上通孔焊盘pn

‑

1可以具有矩形形状。如图7

所示,上通孔焊盘pn

‑

1与中间通孔焊盘pn的中心轴线ax偏移。为了避免下导电通孔vn和上导电通孔vn

‑

1之间的重叠,通过实施var的旋转操作,使下导电通孔vn与假想通孔区域var一起绕中心轴ax旋转。

50.使用本发明是有利的,因为在实现rdl电路设计时,通过将新颖的通孔配置合并到通用互连结构中,可以减轻电路设计人员的负担,并且可以显着减少运行时间。此外,通用互连结构中的新颖通孔配置使rdl电路设计非常容易在不同的最小c4凸点间距(例如,当前最小)的规则之间转换。扇出晶圆级芯片级封装(fo

‑

wlcsp)的c4凸点间距为130μm。适用于cowos(chip

‑

on

‑

wafer

‑

on

‑

substrate,基片上芯片)技术的c4凸点间距为150μm。本发明为不同的扇出封装技术提供了一种灵活的rdl电路设计方法,可以适用于不同的凸点间距要求,就有更好的设计弹性和布局的灵活性。

51.本领域的技术人员将容易地观察到,在保持本发明教导的同时,可以做出许多该装置和方法的修改和改变。因此,上述公开内容应被解释为仅由所附权利要求书的界限和范围所限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。