有机发光二极管显示装置及其像素

1.相关申请的交叉引用

2.本技术要求于2020年5月11日在韩国知识产权局(kipo)提交的韩国专利申请第10

‑

2020

‑

0055731号的优先权,其公开通过引用整体并入本文。

技术领域

3.本公开的示例实施例涉及显示装置,并且更具体地涉及有机发光二极管(oled)显示装置的像素和oled显示装置。

背景技术:

4.近年来,由于信息技术(it)行业的大量需求,对有机发光二极管(oled)显示装置的需求急剧增加。然而,仍然存在与oled显示装置相关联的许多问题。这些问题中之一是oled显示装置可能消耗装置的大部分功率。因此,可能期望在诸如智能电话、平板计算机等的便携式装置中采用的oled显示装置中减少功耗。近年来,为了减少oled显示装置的功耗,已经开发了通过分析图像数据而以低于正常驱动频率的频率来驱动或刷新显示面板的低频驱动技术。例如,当执行低频驱动时,oled显示装置可以不驱动显示面板至少一帧,或者可以不向显示面板提供数据电压以使显示面板基于已存储的数据电压显示图像,从而减少了功耗。

5.然而,当显示面板基于已存储的数据电压显示图像时,已存储的数据电压可能由于包括在显示面板的像素中的晶体管的泄漏电流而失真。因此,当显示面板的驱动频率改变时,显示面板的亮度可能改变,并且oled显示装置的图像质量可能降低。因此,需要一种维持恒定亮度的新颖的oled显示装置,使得当显示面板的驱动频率改变时图像质量不会降低。

技术实现要素:

6.一些示例实施例提供一种即使驱动频率改变也能够具有基本恒定的亮度的有机发光二极管(oled)显示装置的像素。

7.一些示例实施例提供一种即使驱动频率改变也能够具有基本恒定的亮度的oled显示装置。

8.根据示例实施例,提供一种oled显示装置的像素。像素包括:第一晶体管,包括耦接到第一节点的栅极、耦接到第一电源电压的线的第一端子、以及第二端子;第二晶体管,包括接收第一扫描信号的栅极、耦接到初始化电压的线的第一端子和耦接到第一节点的第二端子;第三晶体管,包括接收第一扫描信号的栅极、耦接到初始化电压的线的第一端子和耦接到有机发光二极管的阳极的第二端子;第四晶体管,包括接收第二扫描信号的栅极、耦接到参考电压的线的第一端子和耦接到第二节点的第二端子;第五晶体管,包括接收第二扫描信号的栅极、耦接到第一晶体管的第二端子的第一端子和耦接到第一节点的第二端子;第六晶体管,包括接收第三扫描信号的栅极、耦接到数据线的第一端子和耦接到第二节

点的第二端子;第七晶体管,包括接收发射信号的栅极、耦接到第一晶体管的第二端子的第一端子和耦接到有机发光二极管的阳极的第二端子;第一电容器,包括耦接到第一电源电压的线的第一电极和耦接到第二节点的第二电极;第二电容器,包括耦接到第二节点的第一电极和耦接到第一节点的第二电极;以及有机发光二极管,包括阳极和耦接到第二电源电压的线的阴极。

9.在示例实施例中,第一晶体管和第七晶体管可以是pmos晶体管,并且第二晶体管、第三晶体管、第四晶体管、第五晶体管和第六晶体管可以是nmos晶体管。

10.在示例实施例中,像素的帧时段可以包括:栅极和阳极初始化时段,在栅极和阳极初始化时段中第一晶体管的栅极和有机发光二极管的阳极被初始化;阈值电压补偿时段,在阈值电压补偿时段中第一晶体管的阈值电压被补偿;数据写入时段,在数据写入时段中数据线的数据电压被施加到第二节点;以及发射时段,在发射时段中有机发光二极管发光。

11.在示例实施例中,在栅极和阳极初始化时段中,发射信号可以具有截止电平,第一扫描信号可以具有导通电平,第二扫描信号和第三扫描信号可以分别具有截止电平,第二晶体管和第三晶体管可以导通,第二晶体管可以将初始化电压施加到第一节点,并且第三晶体管可以将初始化电压施加到有机发光二极管的阳极。

12.在示例实施例中,在阈值电压补偿时段中,发射信号可以具有截止电平,第二扫描信号可以具有导通电平,第一扫描信号和第三扫描信号可以分别具有截止电平,第四晶体管和第五晶体管可以导通,第四晶体管可以将参考电压施加到第二节点,第五晶体管可以将第一晶体管二极管连接,并且从第一电源电压减去阈值电压的电压可以通过被二极管连接的第一晶体管被施加到第一节点。

13.在示例实施例中,在数据写入时段中,发射信号可以具有截止电平,第三扫描信号可以具有导通电平,第一扫描信号和第二扫描信号可以分别具有截止电平,第六晶体管可以导通,并且第六晶体管可以将数据电压施加到第二节点。

14.在示例实施例中,在发射时段中,发射信号可以具有导通电平,第一扫描信号、第二扫描信号和第三扫描信号可以分别具有截止电平,第七晶体管可以导通,第一晶体管可以基于第一节点的电压生成驱动电流,并且第七晶体管可以将驱动电流提供到有机发光二极管。

15.在示例实施例中,阈值电压补偿时段的时间长度可以比数据写入时段的时间长度要长。

16.在示例实施例中,栅极和阳极初始化时段、阈值电压补偿时段和数据写入时段可以具有相等的时间长度。

17.在示例实施例中,像素可以进一步包括第八晶体管,第八晶体管包括接收第四扫描信号的栅极、接收发射信号的第一端子和耦接到第一晶体管的第二端子的第二端子。

18.在示例实施例中,第一晶体管可以是pmos晶体管,并且第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管以及第八晶体管可以是nmos晶体管。

19.在示例实施例中,像素的帧时段可以包括:栅极和阳极初始化时段,在栅极和阳极初始化时段中第一晶体管的栅极和有机发光二极管的阳极被初始化;漏极初始化时段,在漏极初始化时段中第一晶体管的第二端子被初始化;阈值电压补偿时段,在阈值电压补偿时段中第一晶体管的阈值电压被补偿;数据写入时段,在数据写入时段中数据线的数据电

压被施加到第二节点;以及发射时段,在发射时段中有机发光二极管发光。

20.在示例实施例中,在漏极初始化时段中,发射信号可以具有截止电平,第四扫描信号可以具有导通电平,第一扫描信号、第二扫描信号和第三扫描信号可以分别具有截止电平,第八晶体管可以导通,并且第八晶体管可以将具有截止电平的发射信号施加到第一晶体管的第二端子。

21.在示例实施例中,漏极初始化时段可以位于栅极和阳极初始化时段与阈值电压补偿时段之间,并且可以不与栅极和阳极初始化时段及阈值电压补偿时段重叠。

22.在示例实施例中,漏极初始化时段可以位于栅极和阳极初始化时段与阈值电压补偿时段之间,并且可以与栅极和阳极初始化时段及阈值电压补偿时段部分重叠。

23.在示例实施例中,在漏极初始化时段与阈值电压补偿时段彼此重叠的时段中,发射信号可以具有截止电平,第二扫描信号和第四扫描信号可以分别具有导通电平,第一扫描信号和第三扫描信号可以分别具有截止电平,第五晶体管和第八晶体管可以导通,并且具有截止电平的发射信号可以通过第八晶体管和第五晶体管被施加到第一节点。

24.根据示例实施例,提供一种oled显示装置的像素。像素包括:第一晶体管,包括耦接到第一节点的栅极、耦接到第一电源电压的线的第一端子、以及第二端子;第二晶体管,包括接收第一扫描信号的栅极、耦接到初始化电压的线的第一端子和耦接到第一节点的第二端子;第三晶体管,包括接收第四扫描信号的栅极、耦接到初始化电压的线的第一端子和耦接到有机发光二极管的阳极的第二端子;第四晶体管,包括接收第二扫描信号的栅极、耦接到参考电压的线的第一端子和耦接到第二节点的第二端子;第五晶体管,包括接收第二扫描信号的栅极、耦接到第一晶体管的第二端子的第一端子和耦接到第一节点的第二端子;第六晶体管,包括接收第三扫描信号的栅极、耦接到数据线的第一端子和耦接到第二节点的第二端子;第七晶体管,包括接收发射信号的栅极、耦接到第一晶体管的第二端子的第一端子和耦接到有机发光二极管的阳极的第二端子;第一电容器,包括耦接到第一电源电压的线的第一电极和耦接到第二节点的第二电极;第二电容器,包括耦接到第二节点的第一电极和耦接到第一节点的第二电极;以及有机发光二极管,包括阳极和耦接到第二电源电压的线的阴极。

25.在示例实施例中,第一晶体管、第三晶体管和第七晶体管可以是pmos晶体管,并且第二晶体管、第四晶体管、第五晶体管和第六晶体管可以是nmos晶体管。

26.在示例实施例中,第四扫描信号可以是第一扫描信号的反相版本。

27.根据示例实施例,提供一种oled显示装置,包括:显示面板,包括多个像素;数据驱动器,被配置成将数据电压提供到多个像素;扫描驱动器,被配置成将第一扫描信号、第二扫描信号和第三扫描信号提供到多个像素;发射驱动器,被配置成将发射信号提供到多个像素;以及控制器,被配置成控制数据驱动器、扫描驱动器和发射驱动器。多个像素中的每一个包括:第一晶体管,包括耦接到第一节点的栅极、耦接到第一电源电压的线的第一端子、以及第二端子;第二晶体管,包括接收第一扫描信号的栅极、耦接到初始化电压的线的第一端子和耦接到第一节点的第二端子;第三晶体管,包括接收第一扫描信号的栅极、耦接到初始化电压的线的第一端子和耦接到有机发光二极管的阳极的第二端子;第四晶体管,包括接收第二扫描信号的栅极、耦接到参考电压的线的第一端子和耦接到第二节点的第二端子;第五晶体管,包括接收第二扫描信号的栅极、耦接到第一晶体管的第二端子的第一端

子和耦接到第一节点的第二端子;第六晶体管,包括接收第三扫描信号的栅极、耦接到数据线的第一端子和耦接到第二节点的第二端子;第七晶体管,包括接收发射信号的栅极、耦接到第一晶体管的第二端子的第一端子和耦接到有机发光二极管的阳极的第二端子;第一电容器,包括耦接到第一电源电压的线的第一电极和耦接到第二节点的第二电极;第二电容器,包括耦接到第二节点的第一电极和耦接到第一节点的第二电极;以及有机发光二极管,包括阳极和耦接到第二电源电压的线的阴极。

28.如上所述,在oled显示装置的像素和oled显示装置中,像素可以包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管、第一电容器、第二电容器以及有机发光二极管,并且第一至第七晶体管的一部分可以利用nmos晶体管来实现。因此,即使包括像素的显示面板的驱动频率改变,像素也可以在相同的灰度级下以基本恒定的亮度发光。

附图说明

29.从下面结合附图的详细描述,将更清楚地理解例示性的非限制性示例实施例。

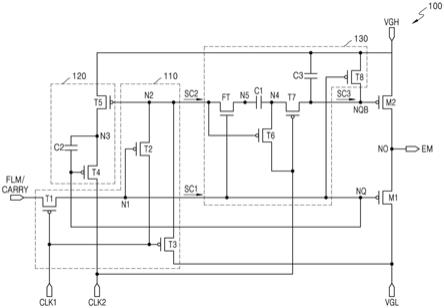

30.图1是示出根据示例实施例的有机发光二极管(oled)显示装置的像素的电路图。

31.图2是用于描述根据示例实施例的像素的操作的示例的时序图。

32.图3是用于描述像素在栅极和阳极初始化时段中的操作的示例的电路图。

33.图4是用于描述像素在阈值电压补偿时段中的操作的示例的电路图。

34.图5是用于描述像素在数据写入时段中的操作的示例的电路图。

35.图6是用于描述像素在发射时段中的操作的示例的电路图。

36.图7是用于描述根据示例实施例的像素的操作的另一示例的时序图。

37.图8是用于描述根据示例实施例的像素的操作的又一示例的时序图。

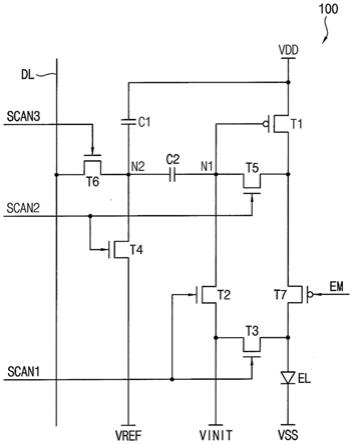

38.图9是示出根据示例实施例的oled显示装置的像素的电路图。

39.图10是用于描述根据示例实施例的像素的操作的示例的时序图。

40.图11是示出根据示例实施例的oled显示装置的像素的电路图。

41.图12是用于描述根据示例实施例的像素的操作的示例的时序图。

42.图13是用于描述像素在漏极初始化时段中的操作的示例的电路图。

43.图14是用于描述根据示例实施例的像素的操作的另一示例的时序图。

44.图15是用于描述像素在漏极初始化时段与阈值电压补偿时段彼此重叠的时段中的操作的示例的电路图。

45.图16是示出根据示例实施例的oled显示装置的框图。

46.图17是示出根据示例实施例的oled显示装置中的发射信号、第一扫描信号、第二扫描信号和第三扫描信号的示例的时序图。

47.图18是用于描述根据示例实施例的oled显示装置的操作的示例的时序图。

48.图19是包括根据示例实施例的oled显示装置的电子装置。

具体实施方式

49.在下文中,将参照附图详细解释本公开的实施例。

50.图1是示出根据示例实施例的有机发光二极管(oled)显示装置的像素的电路图。

51.参照图1,根据示例实施例的oled显示装置的像素100可以包括第一晶体管t1、第二晶体管t2、第三晶体管t3、第四晶体管t4、第五晶体管t5、第六晶体管t6、第七晶体管t7、第一电容器c1、第二电容器c2以及有机发光二极管el。

52.第一晶体管t1可以基于第一节点n1的电压或第一电容器c1的第二电极的电压来生成驱动电流。例如,第一晶体管t1可以是用于生成驱动电流的驱动晶体管。在一些示例实施例中,第一晶体管t1可以包括耦接到第一节点n1的栅极、耦接到第一电源电压vdd(例如,高电源电压)的线的第一端子、以及第二端子。

53.第二晶体管t2可以响应于第一扫描信号scan1将初始化电压vinit施加到第一节点n1。在一些示例实施例中,第二晶体管t2可以包括接收第一扫描信号scan1的栅极、耦接到初始化电压vinit的线的第一端子以及耦接到第一节点n1的第二端子。

54.第三晶体管t3可以响应于第一扫描信号scan1将初始化电压vinit施加到有机发光二极管el的阳极。在一些示例实施例中,第三晶体管t3可以包括接收第一扫描信号scan1的栅极、耦接到初始化电压vinit的线的第一端子以及耦接到有机发光二极管el的阳极的第二端子。

55.第四晶体管t4可以响应于第二扫描信号scan2将参考电压vref施加到第二节点n2。在一些示例实施例中,第四晶体管t4可以包括接收第二扫描信号scan2的栅极、耦接到参考电压vref的线的第一端子以及耦接到第二节点n2的第二端子。

56.第五晶体管t5可以响应于第二扫描信号scan2将第一晶体管t1二极管连接。在一些示例实施例中,第五晶体管t5可以包括接收第二扫描信号scan2的栅极、耦接到第一晶体管t1的第二端子的第一端子以及耦接到第一节点n1的第二端子。

57.第六晶体管t6可以响应于第三扫描信号scan3将数据线dl的数据电压传送到第二节点n2。在一些示例实施例中,第六晶体管t6可以包括接收第三扫描信号scan3的栅极、耦接到数据线dl的第一端子以及耦接到第二节点n2的第二端子。进一步,在一些示例实施例中,第六晶体管t6可以具有包括上栅极和下栅极的双栅极结构。具有双栅极结构的第六晶体管t6可以快速且有效地传送数据电压。

58.第七晶体管t7可以响应于发射信号em将由第一晶体管t1生成的驱动电流提供到有机发光二极管el。在一些示例实施例中,第七晶体管t7可以包括接收发射信号em的栅极、耦接到第一晶体管t1的第二端子的第一端子以及耦接到有机发光二极管el的阳极的第二端子。

59.第一电容器c1可以耦接在第一电源电压vdd的线与第二节点n2之间。在一些示例实施例中,第一电容器c1可以包括耦接到第一电源电压vdd的线的第一电极以及耦接到第二节点n2的第二电极。

60.第二电容器c2可以耦接在第二节点n2与第一节点n1之间。在一些示例实施例中,第二电容器c2可以包括耦接到第二节点n2的第一电极和耦接到第一节点n1的第二电极。进一步,在一些示例实施例中,第二电容器c2可以具有高电容,并且因此可以稳定地存储数据电压。例如,第二电容器c2的电容可以高于第一电容器c1的电容,但是第一电容器c1和第二电容器c2的电容不限于此。

61.当第七晶体管t7导通时,有机发光二极管el可以基于由第一晶体管t1生成的驱动电流而发光。在一些示例实施例中,有机发光二极管el可以包括耦接到第七晶体管t7的第

二端子的阳极以及耦接到第二电源电压vss(例如,低电源电压)的线的阴极。

62.支持低频驱动技术的oled显示装置可以对输入图像数据进行分析,并且可以根据与输入图像数据相对应的图像来改变显示面板的驱动频率。例如,oled显示装置可以在输入图像数据表示移动图像的情况下以正常驱动频率(例如,约240hz、约120hz等)或以输入图像数据的输入帧频率来驱动显示面板,并且可以在输入图像数据表示静止图像的情况下以低于正常驱动频率或输入帧频率的低频来驱动显示面板。因此,当显示静止图像时,可以减小oled显示装置的功耗。然而,当显示面板的驱动频率改变时,即使输入图像数据表示相同的灰度级,随着每个帧时段的时间长度增加,显示面板的像素的亮度也可能由于像素的晶体管t1、t2、t3、t4、t5、t6和t7的泄漏电流或者其端子(例如,源极和/或漏极)直接耦接到第一电容器c1和第二电容器c2的晶体管t2、t4、t5和t6的泄漏电流而减小(特别是在高灰度级时)。

63.然而,在根据示例实施例的oled显示装置的像素100中,如图1中所示,第一晶体管t1和第七晶体管t7可以利用pmos晶体管来实现,并且第二晶体管t2、第三晶体管t3、第四晶体管t4、第五晶体管t5和第六晶体管t6可以利用具有相对小的泄漏电流的nmos晶体管来实现。在这种情况下,由于其端子(例如,源极和/或漏极)直接耦接到第一电容器c1和第二电容器c2的晶体管t2、t4、t5和t6利用nmos晶体管来实现,因此晶体管t2、t4、t5和t6从第一电容器c1和第二电容器c2的泄漏电流可以减小。因此,即使显示面板的驱动频率改变,显示面板的像素100也可以在相同的灰度级下以基本恒定的亮度显示图像。因此,根据示例实施例的像素100可以在宽的驱动频率范围(例如,从约10hz到约240hz)中以基本恒定的亮度显示图像。

64.图2是用于描述根据示例实施例的像素的操作的示例的时序图,图3是用于描述像素在栅极和阳极初始化时段中的操作的示例的电路图,图4是用于描述像素在阈值电压补偿时段中的操作的示例的电路图,图5是用于描述像素在数据写入时段中的操作的示例的电路图,并且图6是用于描述像素在发射时段中的操作的示例的电路图。

65.参照图1和图2,像素100的帧时段fp可以包括栅极和阳极初始化时段gaip、阈值电压补偿时段cmpp、数据写入时段dwp和发射时段emp。在一些示例实施例中,如图1和图2中所示,发射信号em可以是具有低电平作为导通电平on和高电平作为截止电平off的有效低信号,并且第一至第三扫描信号scan1、scan2和scan3可以是具有高电平作为导通电平on和低电平作为截止电平off的有效高信号。例如,信号em、scan1、scan2和scan3的高电平可以是但不限于约8v,并且信号em、scan1、scan2和scan3的低电平可以是但不限于约

‑

6v。

66.在栅极和阳极初始化时段gaip中,第一晶体管t1的栅极和有机发光二极管el的阳极可以被初始化。在栅极和阳极初始化时段gaip中,发射信号em可以具有截止电平off,第一扫描信号scan1可以具有导通电平on,并且第二扫描信号scan2和第三扫描信号scan3可以具有截止电平off。在一些示例实施例中,发射信号em可以被改变成截止电平off,并且然后第一扫描信号scan1可以被改变成导通电平on。在其他示例实施例中,发射信号em和第一扫描信号scan1可以基本上同时分别被改变成截止电平off和导通电平on。进一步,在一些示例实施例中,栅极和阳极初始化时段gaip可以具有对应于但不限于三个水平时间(或3h时间)的时间长度。进一步,在一些示例实施例中,oled显示装置的一个水平时间(或1h时间)可以根据显示面板的最大驱动频率(例如,约240hz)来确定。这里,一个水平时间可以指

示被分配为在帧时段内处理一行像素的时间。

67.在栅极和阳极初始化时段gaip中,如图3中所示,第七晶体管t7可以响应于具有截止电平off的发射信号em而截止,并且第二晶体管t2和第三晶体管t3可以响应于具有导通电平on的第一扫描信号scan1而导通。因此,第二晶体管t2可以将初始化电压vinit施加到第一节点n1或第一晶体管t1的栅极,并且因此第一晶体管t1的栅极可以被初始化。进一步,第三晶体管t3可以将初始化电压vinit施加到有机发光二极管el的阳极,并且因此有机发光二极管el的阳极可以被初始化。例如,初始化电压vinit可以是但不限于约

‑

1v。

68.在阈值电压补偿时段cmpp中,第一晶体管t1(例如,驱动晶体管)的阈值电压可以被补偿。在阈值电压补偿时段cmpp中,发射信号em可以具有截止电平off,第二扫描信号scan2可以具有导通电平on,并且第一扫描信号scan1和第三扫描信号scan3可以具有截止电平off。在一些示例实施例中,第一扫描信号scan1可以被改变成截止电平off,并且然后第二扫描信号scan2可以被改变成导通电平on。在其他示例实施例中,第一扫描信号scan1和第二扫描信号scan2可以基本上同时分别被改变成截止电平off和导通电平on。进一步,在一些示例实施例中,阈值电压补偿时段cmpp可以具有对应于但不限于三个水平时间(或3h时间)的时间长度。在一些示例实施例中,如图2中所示,阈值电压补偿时段cmpp和数据写入时段dwp可以彼此分离,并且阈值电压补偿时段cmpp的时间长度(例如,3h时间)可以比数据写入时段dwp的时间长度(例如,1h时间)要长。在这种情况下,由于阈值电压补偿时段cmpp具有比数据写入时段dwp的时间长度要长的时间长度,因此可以充分补偿第一晶体管t1(例如,驱动晶体管)的阈值电压。

69.在阈值电压补偿时段cmpp中,如图4中所示,第四晶体管t4和第五晶体管t5可以响应于具有导通电平on的第二扫描信号scan2而导通。因此,第四晶体管t4可以将参考电压vref施加到第二节点n2或第二电容器c2的第一电极。例如,参考电压vref可以是但不限于约2v。进一步,第五晶体管t5可以将第一晶体管t1二极管连接。因此,从第一电源电压vdd减去阈值电压vth的电压vdd

‑

vth可以通过被二极管连接的第一晶体管t1被施加到第一节点n1或第二电容器c2的第二电极。例如,第一电源电压vdd可以是但不限于约8v,并且第二电源电压vss可以是但不限于约

‑

5v。

70.在数据写入时段dwp中,数据线dl的数据电压可以被施加到第二节点n2或第二电容器c2的第一电极。在数据写入时段dwp中,发射信号em可以具有截止电平off,第三扫描信号scan3可以具有导通电平on,并且第一扫描信号scan1和第二扫描信号scan2可以具有截止电平off。在一些示例实施例中,第二扫描信号scan2可以被改变成截止电平off,并且然后第三扫描信号scan3可以被改变成导通电平on。在其他示例实施例中,第二扫描信号scan2和第三扫描信号scan3可以基本上同时分别被改变成截止电平off和导通电平on。进一步,在一些示例实施例中,数据写入时段dwp可以具有对应于但不限于一个水平时间(或1h时间)的时间长度。

71.在数据写入时段dwp中,如图5中所示,第六晶体管t6可以响应于具有导通电平on的第三扫描信号scan3而导通。因此,第六晶体管t6可以将数据电压vdat施加到第二节点n2或第二电容器c2的第一电极。因此,第二电容器c2的第一电极的电压可以从参考电压vref改变数据电压vdat与参考电压vref之间的差vdat

‑

vref以改变成数据电压vdat。如果第二电容器c2的第一电极的电压改变数据电压vdat与参考电压vref之间的差vdat

‑

vref,则第

二电容器c2的在浮置状态下的第二电极的电压也可以改变数据电压vdat与参考电压vref之间的差vdat

‑

vref。因此,在数据写入时段dwp中,第二电容器c2的第二电极的电压或第一节点n1的电压可以变为电压vdd

‑

vth vdat

‑

vref,其中数据电压vdat与参考电压vref之间的差vdat

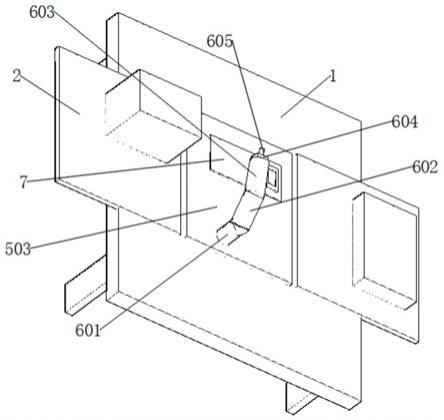

‑

vref被添加到从第一电源电压vdd减去阈值电压vth的电压vdd

‑

vth。

72.在发射时段emp中,有机发光二极管el可以发光。在发射时段emp中,发射信号em可以具有导通电平on,并且第一扫描信号scan1、第二扫描信号scan2和第三扫描信号scan3可以具有截止电平off。在一些示例实施例中,第三扫描信号scan3可以被改变成截止电平off,并且然后发射信号em可以被改变成导通电平on。在其他示例实施例中,第三扫描信号scan3和发射信号em可以基本上同时分别被改变成截止电平off和导通电平on。

73.在发射时段emp中,如图6中所示,第七晶体管t7可以响应于具有导通电平on的发射信号em而导通。因此,第一晶体管t1可以基于第一节点n1的电压vdd

‑

vth vdat

‑

vref或第二电容器c2的第二电极的电压vdd

‑

vth vdat

‑

vref来生成驱动电流idr,第七晶体管t7可以将驱动电流idr提供到有机发光二极管el,并且有机发光二极管el可以基于驱动电流idr而发光。由第一晶体管t1生成的驱动电流idr可以根据等式“β/2*(vsg

‑

vth)

2”来确定。这里,β可以是由第一晶体管t1的迁移率、电容以及沟道的宽度和长度确定的晶体管增益,vsg可以是第一晶体管t1的源极

‑

栅极电压,并且vth可以是第一晶体管t1的阈值电压。进一步,由于第一晶体管t1的源极电压是第一电源电压vdd,并且第一晶体管t1的栅极电压是第一节点n1的电压vdd

‑

vth vdat

‑

vref,所以“vsg

‑

vth”可以是“vdd

‑

vdd vth

‑

vdat vref

‑

vth=vref

‑

vdat”。因此,驱动电流idr可以基于参考电压vref和数据电压vdat来确定,而与第一晶体管t1的阈值电压vth无关。

74.图7是用于描述根据示例实施例的像素的操作的另一示例的时序图。

75.参照图1、图2、图3、图4、图5、图6和图7,像素100的帧时段fp可以包括栅极和阳极初始化时段gaip、阈值电压补偿时段cmpp、数据写入时段dwp和发射时段emp。除了数据写入时段dwp的时间长度从一个水平时间(1h时间)增加到三个水平时间(3h时间)之外,图7中所示的帧时段fp可以与图2中所示的帧时段fp基本上相同。

76.在一些示例实施例中,如图7中所示,栅极和阳极初始化时段gaip、阈值电压补偿时段cmpp和数据写入时段dwp可以具有相同的时间长度,例如三个水平时间(3h时间)。图7示出第n行中的像素100的发射信号em以及第一至第三扫描信号scan1、scan2和scan3的示例,其中n是大于2的整数。第一数据电压可以在数据写入时段dwp的第一1h时间中被写入第n

‑

2行中的像素100,第二数据电压可以在数据写入时段dwp的第二1h时间中被写入第n

‑

1行中的像素100,并且第三数据电压可以在数据写入时段dwp的第三1h时间中被写入第n行中的像素100。在这种情况下,由于在第三数据电压被写入第n行中的像素100之前,提供了用于第n

‑

2行和第n

‑

1行中的像素100的第一数据电压和第二数据电压,因此可以对第n行中的像素100执行预充电操作。

77.图8是用于描述根据示例实施例的像素的操作的又一示例的时序图。

78.参照图1、图2、图3、图4、图5、图6、图7和图8,像素100的帧时段fp可以包括栅极和阳极初始化时段gaip、阈值电压补偿时段cmpp、数据写入时段dwp和发射时段emp。除了栅极和阳极初始化时段gaip的时间长度减小并且阈值电压补偿时段cmpp的时间长度增加之外,图8中所示的帧时段fp可以与图2中所示的帧时段fp基本上相同。

79.在一些示例实施例中,与图2中所示的帧时段fp相比,图8中所示的栅极和阳极初始化时段gaip可以从三个水平时间(3h时间)减小到两个水平时间(2h时间),并且阈值电压补偿时段cmpp可以从三个水平时间(3h时间)增加到四个水平时间(4h时间)。在这种情况下,在维持发射时段emp的时间长度的同时,阈值电压补偿时段cmpp的时间长度可以增加,并且因此可以更充分地补偿第一晶体管t1(例如,驱动晶体管)的阈值电压。

80.图9是示出根据示例实施例的oled显示装置的像素的电路图,并且图10是用于描述根据示例实施例的像素的操作的示例的时序图。

81.参照图9和图10,根据示例实施例的oled显示装置的像素200可以包括第一晶体管t1、第二晶体管t2、第三晶体管t3’、第四晶体管t4、第五晶体管t5、第六晶体管t6、第七晶体管t7、第一电容器c1、第二电容器c2以及有机发光二极管el。除了第三晶体管t3’利用pmos晶体管来实现并且第三晶体管t3’可以不接收第一扫描信号scan1而是接收第四扫描信号scan1b之外,图9的像素200可以具有与图1的像素100基本相同的配置。进一步,除了像素200进一步接收第四扫描信号scan1b之外,图10中所示的被提供到像素200的信号em、scan1、scan1b、scan2和scan3可以与图2中所示的被提供到像素100的信号em、scan1、scan2和scan3基本上相同。即,在栅极和阳极初始化时段gaip期间,第四扫描信号scan1b具有导通电平on,并且在时段cmpp、dwp和emp期间,第四扫描信号scan1b具有截止电平off。

82.第三晶体管t3’可以响应于第四扫描信号scan1b将初始化电压vinit施加到有机发光二极管el的阳极。在一些示例实施例中,第三晶体管t3’可以包括接收第四扫描信号scan1b的栅极、耦接到初始化电压vinit的线的第一端子以及耦接到有机发光二极管el的阳极的第二端子。进一步,在一些示例实施例中,如图9和图10中所示,第三晶体管t3’可以是pmos晶体管,并且第四扫描信号scan1b可以是第一扫描信号scan1的反相版本。因此,在第二晶体管t2导通的同时,第三晶体管t3’可以导通。

83.如图9中所示,第一晶体管t1、第三晶体管t3’和第七晶体管t7可以利用pmos晶体管来实现,并且第二晶体管t2、第四晶体管t4、第五晶体管t5和第六晶体管t6可以利用具有相对小的泄漏电流的nmos晶体管来实现。在这种情况下,由于其端子(例如,源极和/或漏极)直接耦接到第一电容器c1和第二电容器c2的晶体管t2、t4、t5和t6利用nmos晶体管来实现,因此晶体管t2、t4、t5和t6从第一电容器c1和第二电容器c2的泄漏电流可以减小。因此,即使显示面板的驱动频率改变,显示面板的像素200也可以在相同的灰度级下以基本恒定的亮度显示图像。因此,根据示例实施例的像素200可以在宽的驱动频率范围(例如,从约10hz到约240hz)中以基本恒定的亮度显示图像。

84.图11是示出根据示例实施例的oled显示装置的像素的电路图,图12是用于描述根据示例实施例的像素的操作的示例的时序图,并且图13是用于描述像素在漏极初始化时段中的操作的示例的电路图。

85.参照图11和图12,根据示例实施例的oled显示装置的像素300可以包括第一晶体管t1、第二晶体管t2、第三晶体管t3、第四晶体管t4、第五晶体管t5、第六晶体管t6、第七晶体管t7’、第八晶体管t8、第一电容器c1、第二电容器c2以及有机发光二极管el。除了第七晶体管t7’利用nmos晶体管来实现并且像素300进一步包括第八晶体管t8之外,图11的像素300可以具有与图1的像素100基本相同的配置。进一步,除了像素300进一步接收第四扫描信号scan4之外,图12中所示的被提供到像素300的信号em、scan1、scan2、scan3和scan4可

以与图2中所示的被提供到像素100的信号em、scan1、scan2和scan3基本上相同。进一步,除了图12的帧时段fp进一步包括漏极初始化时段dip之外,图12中所示的帧时段fp可以与图2中所示的帧时段fp基本上相同。

86.第七晶体管t7’可以响应于发射信号em将由第一晶体管t1生成的驱动电流提供到有机发光二极管el。在一些示例实施例中,第七晶体管t7’可以是nmos晶体管,并且发射信号em可以是具有高电平作为导通电平on和低电平作为截止电平off的有效高信号。例如,发射信号em的高电平或导通电平on可以是但不限于约8v,并且发射信号em的低电平或截止电平off可以是但不限于约

‑

6v。

87.第八晶体管t8可以响应于第四扫描信号scan4将具有截止电平off(例如,低电平)的发射信号em施加到第一晶体管t1的第二端子或漏极。在一些示例实施例中,第八晶体管t8可以包括接收第四扫描信号scan4的栅极、接收发射信号em的第一端子和耦接到第一晶体管t1的第二端子的第二端子。进一步,在一些示例实施例中,第八晶体管t8可以具有但不限于包括上栅极和下栅极的双栅极结构。

88.如图11中所示,第一晶体管t1可以利用pmos晶体管来实现,并且第二至第八晶体管t2、t3、t4、t5、t6、t7’和t8可以利用具有相对小的泄漏电流的nmos晶体管来实现。在这种情况下,由于其端子(例如,源极和/或漏极)直接或间接耦接到第一电容器c1和第二电容器c2的晶体管t2、t3、t4、t5、t6、t7’和t8利用nmos晶体管来实现,因此晶体管t2、t3、t4、t5、t6、t7’和t8从第一电容器c1和第二电容器c2的泄漏电流可以减小。因此,即使显示面板的驱动频率改变,显示面板的像素300也可以在相同的灰度级下以基本恒定的亮度显示图像。因此,根据示例实施例的像素300可以在宽的驱动频率范围(例如,从约10hz到约240hz)中以基本恒定的亮度显示图像。

89.进一步,如图12中所示,像素300的帧时段fp可以包括栅极和阳极初始化时段gaip、漏极初始化时段dip、阈值电压补偿时段cmpp、数据写入时段dwp以及发射时段emp。在一些示例实施例中,漏极初始化时段dip可以不与阈值电压补偿时段cmpp重叠。例如,如图12中所示,漏极初始化时段dip可以位于栅极和阳极初始化时段gaip与阈值电压补偿时段cmpp之间,并且可以不与栅极和阳极初始化时段gaip及阈值电压补偿时段cmpp重叠。

90.在漏极初始化时段dip中,第一晶体管t1的第二端子或漏极可以被初始化。在漏极初始化时段dip中,发射信号em可以具有截止电平off,第四扫描信号scan4可以具有导通电平on,并且第一扫描信号scan1、第二扫描信号scan2和第三扫描信号scan3可以具有截止电平off。在一些示例实施例中,第一扫描信号scan1可以被改变成截止电平off,并且然后第四扫描信号scan4可以被改变成导通电平on。在其他示例实施例中,第一扫描信号scan1和第四扫描信号scan4可以基本上同时分别被改变成截止电平off和导通电平on。进一步,在一些示例实施例中,漏极初始化时段dip可以具有对应于但不限于两个水平时间(或2h时间)的时间长度。

91.在漏极初始化时段dip中,如图13中所示,第八晶体管t8可以响应于具有导通电平on(例如,高电平)的第四扫描信号scan4而导通。因此,第八晶体管t8可以将具有截止电平off(例如,低电平)的发射信号em施加到第一晶体管t1的第二端子或漏极,并且因此可以初始化第一晶体管t1的漏极。例如,具有截止电平off的发射信号em可以是但不限于约

‑

6v。

92.图14是用于描述根据示例实施例的像素的操作的另一示例的时序图,并且图15是

用于描述像素在漏极初始化时段与阈值电压补偿时段彼此重叠的时段中的操作的示例的电路图。

93.参照图11、图12、图13和图14,像素300的帧时段fp可以包括栅极和阳极初始化时段gaip、漏极初始化时段dip、阈值电压补偿时段cmpp、数据写入时段dwp以及发射时段emp。在一些示例实施例中,漏极初始化时段dip可以与阈值电压补偿时段cmpp部分重叠。例如,如图14中所示,漏极初始化时段dip可以具有对应于两个水平时间(或2h时间)的时间长度,漏极初始化时段dip的第一1h时间可以与栅极和阳极初始化时段gaip重叠,并且漏极初始化时段dip的第二1h时间可以与阈值电压补偿时段cmpp重叠。

94.在栅极和阳极初始化时段gaip中,第一晶体管t1的栅极和有机发光二极管el的阳极可以被初始化。在漏极初始化时段dip中,第一晶体管t1的第二端子或漏极可以被具有截止电平off(例如,低电平)的发射信号em初始化。进一步,在漏极初始化时段dip与阈值电压补偿时段cmpp彼此重叠的时段op中,发射信号可以具有截止电平off,第二扫描信号scan2和第四扫描信号scan4可以具有导通电平on,并且第一扫描信号scan1和第三扫描信号scan3可以具有截止电平off。在这种情况下,如图15中所示,第四晶体管t4和第五晶体管t5可以响应于具有导通电平on的第二扫描信号scan2而导通,并且第八晶体管t8可以响应于具有导通电平on的第四扫描信号scan4而导通。第八晶体管t8可以将具有截止电平off(例如,低电平)的发射信号em施加到第一晶体管t1的第二端子或漏极,并且因此第一晶体管t1的漏极可以被初始化。进一步,具有截止电平off的发射信号em可以通过第八晶体管t8和第五晶体管t5被施加到第一节点n1或第一晶体管t1的栅极,并且因此,第一晶体管t1的栅极可以被具有截止电平off的发射信号em初始化。因此,第一晶体管t1的栅极可以在栅极和阳极初始化时段gaip中被初始化电压vinit初始化,并且然后可以在漏极初始化时段dip与阈值电压补偿时段cmpp彼此重叠的时段op中被具有截止电平off的发射信号em进一步初始化。进一步,由于有机发光二极管el的阳极被初始化电压vinit初始化,并且第一晶体管t1的栅极不仅被初始化电压vinit初始化,而且被具有截止电平off的发射信号em初始化,因此用于初始化有机发光二极管el的阳极和第一晶体管t1的栅极的电压可以彼此分离。

95.图16是示出根据示例实施例的oled显示装置的框图,图17是示出根据示例实施例的oled显示装置中的发射信号、第一扫描信号、第二扫描信号和第三扫描信号的示例的时序图,并且图18是用于描述根据示例实施例的oled显示装置的操作的示例的时序图。

96.参照图16,根据示例实施例的oled显示装置400可以包括显示面板410、数据驱动器420、扫描驱动器430、发射驱动器440和控制器450。

97.显示面板410可以包括多个像素px。根据示例实施例,每个像素px可以是具有图1中所示的七个晶体管和两个电容器(7t

‑

2c)结构的像素100、具有图9中所示的七个晶体管和两个电容器(7t

‑

2c)结构的像素200或具有图11中所示的八个晶体管和两个电容器(8t

‑

2c)结构的像素300等。如图1、图9或图11中所示,像素px的第一晶体管可以利用pmos晶体管来实现,并且一个或多个其他晶体管可以利用nmos晶体管来实现。因此,即使显示面板410的驱动频率df改变,像素px也可以在相同的灰度级下以基本恒定的亮度发光。

98.数据驱动器420可以基于从控制器450接收的数据控制信号dctrl和输出图像数据odat将数据电压vdat提供到多个像素px。在一些示例实施例中,数据控制信号dctrl可以包括但不限于输出数据使能信号、水平起始信号和负载信号。数据驱动器420可以以显示面板

410的驱动频率df接收作为输出图像数据odat的帧数据。在一些示例实施例中,数据驱动器420和控制器450可以利用信号集成电路来实现,并且信号集成电路可以被称为时序控制器嵌入式数据驱动器(ted)。在其他示例实施例中,数据驱动器420和控制器450可以利用分离的集成电路来实现。

99.扫描驱动器430可以基于从控制器450接收的扫描控制信号sctrl将第一扫描信号scan1、第二扫描信号scan2和第三扫描信号scan3提供到多个像素px。在一些示例实施例中,扫描控制信号sctrl可以包括但不限于扫描起始信号和扫描时钟信号。在一些示例实施例中,第一扫描信号scan1、第二扫描信号scan2和第三扫描信号scan3可以逐行顺序地被提供到多个像素px。例如,显示面板410可以包括n行像素px,并且如图17中所示,扫描驱动器430可以输出用于第一行像素px的第一扫描信号scan1_1、第二扫描信号scan2_1和第三扫描信号scan3_1,并且可以输出与用于第一行像素px的第一扫描信号scan1_1、第二扫描信号scan2_1和第三扫描信号scan3_1相比移位了一个水平时间(1h时间)的、用于第二行像素px的第一扫描信号scan1_2、第二扫描信号scan2_2和第三扫描信号scan3_2。以这种方式,扫描驱动器430可以将第一扫描信号scan1、第二扫描信号scan2和第三扫描信号scan3移位一个水平时间(1h时间),以逐行顺序地输出移位的第一扫描信号scan1、第二扫描信号scan2和第三扫描信号scan3,直到输出用于最后一行像素px的第一扫描信号scan1_n、第二扫描信号scan2_n和第三扫描信号scan3_n。尽管图17示出与图2中所示的信号em、scan1、scan2和scan3相对应的示例,但是扫描驱动器430的操作不限于图17的示例。例如,扫描驱动器430可以根据图7、图8、图10、图12或图14中所示的示例进行操作。在一些示例实施例中,在每个像素px是图11的像素300的情况下,扫描驱动器430可以进一步将第四扫描信号scan4提供到多个像素px。在一些示例实施例中,扫描驱动器430可以集成或形成在显示面板410的外围部分中。在其他示例实施例中,扫描驱动器430可以利用一个或多个集成电路来实现。

100.发射驱动器440可以基于从控制器450接收的发射控制信号emctrl将发射信号em提供到多个像素px。在一些示例实施例中,发射控制信号emctrl可以包括但不限于发射起始信号和发射时钟信号。在一些示例实施例中,发射驱动器440可以逐行顺序地将发射信号em提供到多个像素px。例如,显示面板410可以包括n行像素px,并且如图17中所示,发射驱动器440可以输出用于第一行像素px的发射信号em_1,并且可以输出与用于第一行像素px的发射信号em_1相比移位了一个水平时间(1h时间)的、用于第二行像素px的发射信号em_2。以这种方式,发射驱动器440可以将发射信号em移位一个水平时间(1h时间),以逐行顺序地输出移位的发射信号em,直到输出用于最后一行像素px的发射信号em_n。尽管图17示出与图2中所示的信号em、scan1、scan2和scan3相对应的示例,但是发射驱动器440的操作不限于图17的示例。例如,发射驱动器440可以根据图7、图8、图10、图12或图14中所示的示例进行操作。在一些示例实施例中,发射驱动器440可以集成或形成在显示面板410的外围部分中。在其他示例实施例中,发射驱动器440可以利用一个或多个集成电路来实现。

101.控制器450(例如,时序控制器(tcon))可以从外部主机处理器(例如,应用处理器(ap)、图形处理单元(gpu)或图形卡)接收输入图像数据idat和控制信号ctrl。在一些示例实施例中,控制信号ctrl可以包括但不限于垂直同步信号、水平同步信号、输入数据使能信号以及主时钟信号等。控制器450可以基于输入图像数据idat和控制信号ctrl来生成输出

图像数据odat、数据控制信号dctrl、扫描控制信号sctrl和发射控制信号emctrl。控制器450可以通过将输出图像数据odat和数据控制信号dctrl提供到数据驱动器420来控制数据驱动器420的操作,可以通过将扫描控制信号sctrl提供到扫描驱动器430来控制扫描驱动器430的操作,并且可以通过将发射控制信号emctrl提供到发射驱动器440来控制发射驱动器440的操作。

102.在一些示例实施例中,oled显示装置400的控制器450可以通过分析输入图像数据idat来改变显示面板410的驱动频率df。例如,oled显示装置400可以在输入图像数据idat表示移动图像的情况下以正常驱动频率(例如,约240hz)或输入图像数据idat的输入帧频率iff来驱动显示面板410,并且可以在输入图像数据idat表示静止图像的情况下以低于正常驱动频率或输入帧频率iff的低频来驱动显示面板410。因此,即使控制器450以固定的输入帧频率iff(例如,约240hz)接收输入图像数据idat,控制器450也可以以宽的驱动频率范围(例如,从约10hz到约240hz)中的驱动频率df将输出图像数据odat提供到数据驱动器420。例如,如图18中所示,在输入图像数据idat表示移动图像的第一帧时段fp1和第二帧时段fp2中,控制器450可以以约240hz的输入帧频率iff接收帧数据fdat,并且可以以与输入帧频率iff基本上相同的约240hz的驱动频率df将帧数据fdat作为输出图像数据odat提供到数据驱动器420。因此,显示面板410可以以约240hz的驱动频率df被驱动。如果检测到静止图像,则控制器450可以将显示面板410的驱动频率df确定为低频,例如比约240hz的输入帧频率iff低的约80hz。在输入图像数据idat表示静止图像的情况下,控制器450可以在第三帧时段fp3和第六帧时段fp6中将帧数据fdat提供到数据驱动器420,并且可以在第四帧时段fp4、第五帧时段fp5、第七帧时段fp7和第八帧时段fp8中不将帧数据fdat提供到数据驱动器420。因此,在第三帧时段fp3到第八帧时段fp8中,控制器450可以以是约240hz的输入帧频率iff的三分之一的约80hz的驱动频率df将帧数据fdat提供到数据驱动器420,并且数据驱动器420可以以约80hz的驱动频率df驱动显示面板410。尽管图18示出以约240hz的驱动频率df或约80hz的驱动频率df驱动显示面板410的示例,但是在一些示例实施例中,显示面板410可以以宽的驱动频率范围(例如,从约10hz到约240hz)中的驱动频率df进行驱动。

103.进一步,尽管图18示出控制器450以约240hz的固定输入帧频率iff接收输入图像数据idat的示例,但是在其他示例实施例中,控制器450可以以可变输入帧频率iff(例如,从约10hz到约240hz)接收输入图像数据idat。在这种情况下,控制器450可以以与可变输入帧频率iff相对应的可变驱动频率df来驱动显示面板410。

104.如上所描述,显示面板410的驱动频率df可以改变。然而,在根据示例实施例的oled显示装置400中,显示面板410的每个像素px的一个或多个晶体管可以利用nmos晶体管来实现。因此,即使显示面板410的驱动频率df改变,每个像素px也可以在相同的灰度级下以基本恒定的亮度发光。

105.图19是包括根据示例实施例的oled显示装置的电子装置。

106.参照图19,电子装置1100可以包括处理器1110、存储器装置1120、储存装置1130、输入/输出(i/o)装置1140、电源1150以及oled显示装置1160。尽管在图19中未示出,但电子装置1100可以进一步包括用于与视频卡、声卡、存储器卡、通用串行总线(usb)装置、其他电子装置等进行通信的多个端口。

107.处理器1110可以执行各种计算功能或任务。处理器1110可以是应用处理器(ap)、微处理器、中央处理单元(cpu)等。处理器1110可以经由地址总线、控制总线和数据总线等耦接到其他部件。进一步,在一些示例实施例中,处理器1110可以进一步耦接到诸如外围部件互连(pci)总线的扩展总线。

108.存储器装置1120可以存储用于电子装置1100的操作的数据。例如,存储器装置1120可以包括至少一个非易失性存储器装置(诸如可擦除可编程只读存储器(eprom)装置、电可擦除可编程只读存储器(eeprom)装置、闪存装置、相变随机存取存储器(pram)装置、电阻随机存取存储器(rram)装置、纳米浮栅存储器(nfgm)装置、聚合物随机存取存储器(poram)装置、磁性随机存取存储器(mram)装置、铁电随机存取存储器(fram)装置等)和/或至少一个易失性存储器装置(诸如动态随机存取存储器(dram)装置、静态随机存取存储器(sram)装置以及移动动态随机存取存储器(移动dram)装置等)。

109.储存装置1130可以是固态驱动(ssd)装置、硬盘驱动(hdd)装置和cd

‑

rom装置等。i/o装置1140可以是诸如键盘、小键盘、鼠标和触摸屏等的输入装置以及诸如打印机和扬声器等的输出装置。电源1150可以供给用于电子装置1100的操作的电力。oled显示装置1160可以通过总线或其他通信链路耦接到其他部件。

110.在oled显示装置1160中,每个像素可以包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管、第一电容器、第二电容器以及有机发光二极管,并且第一至第七晶体管的一部分可以利用nmos晶体管来实现。因此,即使包括像素的显示面板的驱动频率改变,像素也可以在相同的灰度级下以基本恒定的亮度发光。

111.本公开可以应用于任何oled显示装置1160以及包括oled显示装置1160的任何电子装置1100。例如,本公开可以应用于移动电话、智能电话、可穿戴电子装置、平板计算机、电视机(tv)、数字tv、3d tv、个人计算机(pc)、家用电器、笔记本计算机、个人数字助理(pda)、便携式多媒体播放器(pmp)、数码相机、音乐播放器、便携式游戏机以及导航装置等。

112.前述内容是示例实施例的例示,并且不应被解释为对其的限制。尽管已经描述了一些示例实施例,但是本领域技术人员将容易理解,在实质上不脱离本公开的新颖教导和优点的情况下,对示例实施例的许多修改是可能的。因此,所有这样的修改旨在被包括在如权利要求书所限定的本公开的范围内。因此,应当理解,前述内容是各种示例实施例的例示,并且不应被解释为限于所公开的特定示例实施例,并且对所公开的示例实施例的修改以及其他示例实施例旨在被包括在所附权利要求书的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。