1.本技术涉及半导体制造技术领域,具体涉及一种图像传感器的制作方法。

背景技术:

2.图像传感器中,互补金属氧化物半导体图像传感器(complementary metal oxide semiconductor contact image sensor,cis)是采用cmos器件制作的图像传感器,由于其具有集成度高、供电电压低和技术门槛低等优势,广泛应用于摄影摄像、安防系统、智能便携电话以及医疗电子等领域。

3.图形传感器通常包括像素单元(pixel)区域和逻辑(logic)区域,像素单元区域中每个像素单元器件之间通过阱区(well)进行隔离。然而,随着器件密度地不断提高,工艺节点地不断减小,像素单元器件的尺寸也随之减小,从而造成器件的读取速度和像素满井容量(full well capacity,fwc)的下降。

4.鉴于此,相关技术中,为了提升器件的读取速度,可以增加源跟随晶体管(source follow transistor,sf)沟道宽度(即,离子注入宽度),同时为了提升fwc,可以缩小传输晶体管(transfer transistor,tx)的侧墙(spacer)尺寸,并增加ddn/pdw区域,然而上述改进会导致源跟随晶体管和深二极管n型阱(deep diode n

‑

type well,ddn)/光电二极管阱(photodiode well,pdw)之间的n

‑

to

‑

n漏电,从而降低了器件的可靠性。

技术实现要素:

5.本技术提供了一种图像传感器的制作方法,可以解决相关技术中提供的图像传感器中像素单元器件通过阱区隔离所导致的漏电问题。

6.一方面,本技术实施例提供了一种图像传感器的制作方法,包括:

7.在衬底上覆盖光阻,使目标区域暴露,所述目标区域包括第一目标区域和第二目标区域,所述第一目标区域是所述图像传感器的源跟随晶体管和行选通晶体管(row select transistor,sel)的有源区之间,以及源跟随晶体管和复位晶体管(reset transistor,rst)的有源区之间的区域,所述第二目标区域是所述图像传感器的逻辑器件的有源区之间的区域;

8.进行刻蚀,刻蚀至第一目标深度,在所述目标区域形成第一沟槽;

9.在所述图像传感器的像素单元区域覆盖光阻;

10.进行刻蚀,将所述第二目标区域所述的第一沟槽向下刻蚀至第二目标深度,形成第二沟槽;

11.沉积硅氧化物,所述硅氧化物填充所述第一沟槽和所述第二沟槽;

12.去除光阻,所述第一沟槽中的硅氧化物形成第一浅槽隔离(shallow trench isolation,sti)结构,所述第二沟槽中的硅氧化物形成第二sti结构。

13.可选的,所述第一沟槽的深度为至1500埃。

14.可选的,所述第二沟槽的深度为1700埃至4000埃。

15.可选的,所述第一沟槽的截面为倒梯形,所述倒梯形的腰和下底之间的夹角为55度(

°

)至89度。

16.可选的,所述第二沟槽的截面为倒梯形,所述倒梯形的腰和下底之间的夹角为50度至86度。

17.可选的,所述沉积硅氧化物,包括:

18.通过高密度化学气相沉积(high density plasma chemical vapor deposition,hdp cvd)工艺沉积所述硅氧化物。

19.可选的,所述沉积硅氧化物,包括:

20.通过高深宽比(high aspect ratio process,harp)工艺沉积所述硅氧化物。

21.可选的,在覆盖光阻前,所述衬底上从下至上依次形成有衬垫氧化层和阻挡层。

22.可选的,所述阻挡层包括氮化硅层。

23.本技术技术方案,至少包括如下优点:

24.通过在源跟随晶体管、复位晶体管和行选通晶体管之间形成第一sti结构,在逻辑器件之间形成第二sti结构,解决了相关技术中通过阱区域隔离像素单元区域和逻辑器件区域所导致的漏电现象,提高了器件的可靠性。

附图说明

25.为了更清楚地说明本技术具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本技术的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

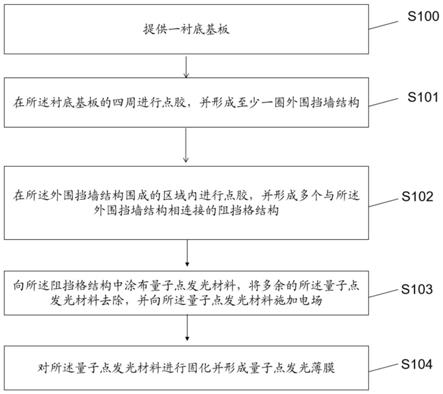

26.图1是本技术一个示例性实施例提供的图像传感器的制作方法的流程图;

27.图2是本技术一个示例性实施例中形成第一沟槽和第二沟槽的剖面示意图;

28.图3是本技术一个示例性实施例中形成的第一sti结构和第二sti结构的剖面图;

29.图4是本技术一个示例性实施例中形成的第一sti结构的俯视图。

具体实施方式

30.下面将结合附图,对本技术中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本技术的一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在不做出创造性劳动的前提下所获得的所有其它实施例,都属于本技术保护的范围。

31.在本技术的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

32.在本技术的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电气连接;可以是直接相连,也可以通过中间媒介间接相连,还可

以是两个元件内部的连通,可以是无线连接,也可以是有线连接。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本技术中的具体含义。

33.此外,下面所描述的本技术不同实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互结合。

34.参考图1,其示出了本技术一个示例性实施例提供的图像传感器的制作方法的流程图,该图像传感器可以是cis,该方法包括:

35.步骤101,在衬底上覆盖光阻,使目标区域暴露。

36.本技术实施例中,衬底上的区域包括像素单元区域和逻辑区域,像素单元区域用于形成像素单元器件,逻辑区域用于形成逻辑器件。其中,像素单元器件包括源跟随晶体管、复位晶体管、行选通晶体管和传输晶体管。

37.示例性的,可在衬底上悬涂光阻,对目标区域进行曝光,显影后使目标区域暴露。其中,目标区域包括第一目标区域和第二目标区域,第一目标区域是源跟随晶体管和行选通晶体管的有源区(active area,aa)之间,以及源跟随晶体管和复位晶体管的有源区之间的区域,第二目标区域是逻辑器件的有源区之间的区域。

38.步骤102,进行刻蚀,刻蚀至第一目标深度,在目标区域形成第一沟槽。

39.可选的,第一目标深度为500埃至1500埃(例如,其可以是1000埃)。

40.步骤103,在像素单元区域覆盖光阻。

41.示例性的,可在衬底上悬涂光阻,对除像素单元区域的其它区域进行曝光,显影后使逻辑区域暴露。

42.步骤104,进行刻蚀,将第二目标区域的第一沟槽向下刻蚀至第二目标深度,形成第二沟槽。

43.可选的,第二目标深度为1700埃至4000埃(例如,其可以是3000埃)。

44.参考图2,其示出了形成第一沟槽和第二沟槽的剖面示意图。如图2所示,本技术实施例中,以衬底210的表面所在的平面建立x轴和y轴,以衬底210的厚度所在的方向为z轴进行描述。

45.衬底210上包括像素单元区域2001和逻辑区域2002,像素单元区域2001用于形成的像素单元器件包括源跟随晶体管、复位晶体管、行选通晶体管和传输晶体管(图2中未示出)。在步骤201之前,衬底210上从下至上依次形成有衬垫氧化层220和阻挡层230。可选的,衬垫氧化层220的厚度h3可以是10埃至150埃(例如,其可以是90埃);可选的,阻挡层230包括氮化硅层,该氮化硅层的厚度h4可以是100埃至1500埃(例如,其可以是900埃)。在第二次刻蚀中,可以以阻挡层230作为掩模进行刻蚀。

46.通过步骤102的刻蚀,在像素单元区域2001形成第一沟槽201,第一沟槽201截断源跟随晶体管和行选通晶体管的有源区,以及源跟随晶体管和复位晶体管的有源区。

47.可选的,如图2所示,第一沟槽201的截面为倒梯形,该倒梯形的腰和下底之间的夹角α为55度至89度(例如,其可以是86度),其深度h1为500埃至1500埃(例如,其可以是1000埃);可选的,如图2所示,第二沟槽202的截面为倒梯形,该倒梯形的腰和下底之间的夹角θ为50度至86度(例如,其可以是85度),其深度h2为1700埃至4000埃(例如,其可以是3000埃)。

48.步骤105,沉积硅氧化物,硅氧化物填充第一沟槽和第二沟槽。

49.示例性的,可通过hdp cvd工艺或harp工艺沉积硅氧化物(例如,二氧化硅sio2),沉积的硅氧化物填充第一沟槽和所述第二沟槽。

50.步骤106,去除光阻,第一沟槽中的硅氧化物形成第一sti结构,第二沟槽中的硅氧化物形成第二sti结构。

51.参考图3,其示出了形成的第一sti结构和第二sti结构的剖面图;参考图4,其示出了形成的第一sti结构的俯视图。

52.如图3所示,去除衬垫氧化层和阻挡层后,第一沟槽201中的硅氧化物形成第一sti结构241,第二沟槽202中的硅氧化物形成第二sti结构242,第二sti结构242位于逻辑器件(图3中未示出)的有源区之间。如图4所示,像素单元区域包括源跟随晶体管的有源区251、行选通晶体管的有源区252、复位晶体管的由于安全253和传输晶体管的有源区254,其中,传输晶体管的有源区254呈梯形,且四个传输晶体管的有源区254相对组成矩形的区域,在后续的工序中,像素单元区域还要形成ddn/pdw,源跟随晶体管的有源区251和行选通晶体管的有源区252之间形成有第一sti结构241,源跟随晶体管的有源区251和复位晶体管的有源区253之间形成有第一sti结构241。

53.综上所述,本技术实施例中,通过在源跟随晶体管、复位晶体管和行选通晶体管之间形成第一sti结构,在逻辑器件之间形成第二sti结构,解决了相关技术中通过阱区域隔离像素单元区域和逻辑器件区域所导致的漏电现象,提高了器件的可靠性。

54.显然,上述实施例仅仅是为清楚地说明所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引伸出的显而易见的变化或变动仍处于本技术创造的保护范围之中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。