1.本技术涉及发光二极管led控制技术领域,特别是涉及一种降低电容啸叫的方法及装置。

背景技术:

2.电容啸叫指电路板上的电容发生形变导致电路板振动而产生噪声的现象。例如,在对焊接在电路板上的陶瓷电容施加交流电之后,该陶瓷电容会分别在与电路板垂直以及平行的方向上发生伸缩形变,进而引发电路板振动。若电路板的振动频率在人耳可听范围内(20hz~20khz),就会听到电容啸叫。

3.在发光二极管(light emitting diode,led)控制场景中,为了使led在显示图像时,呈现出更好地显示效果,需要提高led驱动的分辨率。一般的,分辨率通常需要超过9bit甚至更高达到16bit,从而使得色彩丰富且细腻。

4.而实现丰富的色彩需要高分辨率的电流等级。例如利用脉宽调制(pulse width modulation,pwm)的方式,来获得高分辨率的电流等级。具体地,输出分辨率的原始位数较高的pwm信号,但是随着pwm信号分辨率的原始位数的提高,会出现电容啸叫的问题。再例如通过提高有源晶振(oscillator crystal,osc)的频率来降低电容啸叫的问题。但是随着有源晶振的频率的提高,将会带来额外的电路成本,并且还会带来电磁干扰(electromagnetic interference,emi)。

技术实现要素:

5.为了解决上述技术问题,本技术提供了一种降低电容啸叫的方法,该方法在不改变脉宽调制信号的原有位数的情况下,通过数字抖动的方式,提高脉宽调制信号的分辨率的等效有效位数,既满足了高分辨率的电流等级要求,也不会产生电容啸叫。本技术还提供了一种降低电容啸叫的装置、设置及介质。

6.本技术实施例公开了如下技术方案:

7.第一方面,本技术提供了一种降低电容啸叫的方法,包括:

8.获取脉宽调制信号的分辨率的目标位数;

9.拆分所述目标位数至少为第一子位数和第二子位数;其中,所述第二子位数小于所述第一子位数,所述第一子位数小于等于啸叫位数阈值;

10.根据所述第一子位数确定待调制数字量的非抖动位,根据所述第二子位数确定所述待调制数字量的抖动位;

11.将所述待调制数字量的非抖动位,与所述非抖动位的位数的脉宽调制信号进行调制得到第一信号,将所述待调制数字量的抖动位进行抖动调制得到第二信号;

12.将所述第一信号和所述第二信号相加,以提高所述脉宽调制信号的分辨率的等效有效位数。

13.作为一种可能的实现方式,所述方法还包括:

14.输出所述脉宽调制信号。

15.作为一种可能的实现方式,

16.所述将所述待调制数字量的抖动位进行抖动调制得到第二信号,包括:

17.通过译码器,将所述待调制数字量的抖动位进行抖动调制得到第二信号;其中,所述译码器包括预设的待调制数字量与第二信号的对应关系。

18.作为一种可能的实现方式,所述第二子位数小于等于抖动位数阈值。

19.作为一种可能的实现方式,

20.所述根据所述第一子位数确定待调制数字量的非抖动位,包括:

21.从待调制数字量的最高位连续截取与所述第一子位数对应的位作为非抖动位。

22.作为一种可能的实现方式,

23.所述根据所述第二子位数确定所述待调制数字量的抖动位,包括:

24.从待调制数字量的最低位连续截取与所述第二子位数对应的位作为抖动位。

25.第二方面,本技术提供了一种降低电容啸叫的装置,包括:

26.获取模块,用于获取脉宽调制信号的分辨率的目标位数;

27.拆分模块,用于拆分所述目标位数至少为第一子位数和第二子位数;其中,所述第二子位数小于所述第一子位数,所述第一子位数小于等于啸叫位数阈值;

28.调制模块,用于根据所述第一子位数确定待调制数字量的非抖动位,根据所述第二子位数确定所述待调制数字量的抖动位;将所述待调制数字量的非抖动位,与所述非抖动位的位数的脉宽调制信号进行调制得到第一信号,将所述待调制数字量的抖动位进行抖动调制得到第二信号;

29.合成模块,用于将所述第一信号和所述第二信号相加,以提高所述脉宽调制信号的分辨率的等效有效位数。

30.作为一种可能的实现方式,所述装置还包括:输出模块;

31.所述输出模块,用于输出所述脉宽调制信号。

32.作为一种可能的实现方式,所述调制模块,具体用于通过译码器,将所述待调制数字量的抖动位进行抖动调制得到第二信号;其中,所述译码器包括预设的待调制数字量与第二信号的对应关系。

33.作为一种可能的实现方式,所述第二子位数小于等于抖动位数阈值。

34.作为一种可能的实现方式,所述调制模块,具体用于从待调制数字量的最高位连续截取与所述第一子位数对应的位作为非抖动位。

35.作为一种可能的实现方式,所述调制模块,具体用于从待调制数字量的最低位连续截取与所述第二子位数对应的位作为抖动位。

36.第三方面,本技术提供了一种设备,该设备包括存储器和处理器;

37.所述处理器用于执行所述存储器中的指令,以使得所述设备执行上述第一方面中任一种可能的方法。

38.第四方面,本技术提供了一种计算机可读存储介质,该计算机可读存储介质包括指令,所述指令用于指示上述第三方面中的设备执行上述第一方面中任一种可能的方法。

39.由上述技术方案可以看出,本技术具有以下优点:

40.本技术提供了一种降低电容啸叫的方法,该方法通过数字抖动的方式,在不改变

原脉宽调制信号的原始位数的情况下,提高该脉宽调制信号的等效有效位数。具体地,该方法包括获取脉宽调制信号的分辨率的目标位数,拆分目标位数至少为两个子位数,例如第一子位数和第二子位数,其中第二子位数小于第一子位数,第一子位数小于等于啸叫位数阈值;根据第一子位数确定待调制数字量的非抖动位,根据第二子位数确定待调制数字量的抖动位,将待调制数字量的非抖动位,与该非抖动位的位数的脉宽调制信号进行调制得到第一信号,将待调制数字量的抖动位进行抖动调制得到第二信号,然后将第一信号和第二信号相加,以提高脉宽调制信号的分辨率的等效有效位数。如此,该方法既满足了高分辨率的电流等级要求,也不会产生电容啸叫等问题,进一步地,该方法通过纯数字的控制方式,来提高脉宽调制信号的等效有效位数,无需额外增加硬件电路,降低了成本。

附图说明

41.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

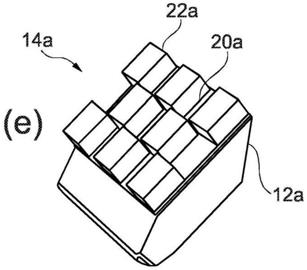

42.图1为本技术实施例提供的一种片式叠层陶瓷电容的示意图;

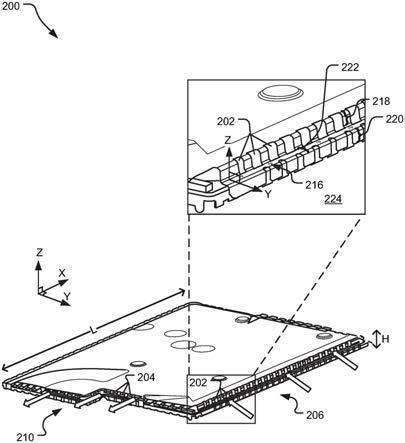

43.图2为本技术实施例提供的压电效应的示意图;

44.图3为本技术实施例提供的一种降低电容啸叫的方法流程图;

45.图4为本技术实施例提供的一种数字抖动的示意图;

46.图5为本技术实施例提供的一种两位数字抖动的示意图;

47.图6为本技术实施例提供的一种降低电容啸叫的装置示意图。

具体实施方式

48.为了使本技术领域的人员更好地理解本技术方案,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

49.为了便于本领域技术人员理解,下面先对本技术中所涉及的技术术语进行介绍。

50.电容啸叫指电路板上的电容发生形变导致电路板振动而产生噪音的现象。一般的,能够产生啸叫的电容大部分是片式叠层陶瓷电容(multi

‑

layer ceramic capacitors,mlcc)。如图1所示,图1示出了一种片式叠层陶瓷电容的示意图。该电容是由印好电极的陶瓷介质膜片以错位的方式叠合起来,经过一次性高温烧结形成陶瓷芯片,再在芯片的两端封上金属层,片式叠层陶瓷电容的端子电极(金属层)可以包括铜底层11、镍镀层12、锡镀层13等。

51.为了更好的理解电容啸叫,下面介绍压电效应。

52.压电效应:在没有对称中心的晶体上施加压力、张力和切向力时,则发生与应力成比例的介质极化,同时在晶体两端面将出现正、负电荷,这一现象称为正压电效应;反之,在晶体上施加电场而引起极化,则产生与电场强度成比例的变形或机械应力,这一现象称为逆压电效应。正压电效应和逆压电效应统称为压电效应。

53.电容啸叫属于逆压电效应的范畴,在外电场的作用下,陶瓷介质会发生伸缩形变,在伸缩形变的程度比较剧烈时,会产生明显啸叫噪声。如图2所示,由于陶瓷介质的强介电性会引起压电效应,片式叠层陶瓷电容在施加交流电之后,会在叠层方向(z轴)和电路板平行的方向(x轴与y轴)发生伸缩形变。由于该电容焊接在电路板上,电容的形变会拉动电路板,从而导致电路板表面振动,当振动频率在人耳可听范围内(20hz~20khz)时,就会听到电容啸叫。

54.随着时代的进步,led灯越来越广泛的应用于人们的生活中。在发光二极管(led)控制场景中,为了使led在显示图像时,呈现出更好地显示效果。例如,从单色到彩色、再到真彩使得图像显示效果越来越丰富,越来越和显示的色彩接近。而为了呈现出更好地显示效果,需要提高led驱动的分辨率。一般的,分辨率通常需要超过9bit甚至高达16bit,从而使色彩丰富且细腻。

55.目前,业界采用高分辨率的电流等级,来提高色彩的丰富度。例如利用分辨率的原始位数较高的pwm信号,来获得高分辨率的电流等级,但是随着pwm信号分辨率的原始位数的提高,会出现电容啸叫的问题。在一些实现方式中,还可以通过提高有源晶振的频率,来降低电容啸叫的问题,但是随着有源晶振的频率的提高,还会带来额外的电路成本,并且会出现电磁干扰的现象。

56.有鉴于此,本技术实施例提供了一种降低电容啸叫的方法,该方法可以由信号处理器执行。具体地,该方法包括:信号处理器获取脉宽调制信号的分辨率的目标位数,拆分目标位数至少为第一子位数和第二子位数,其中,第二子位数小于第一子位数,第一子位数小于等于啸叫位数阈值,根据第一子位数确定待调制数字量的非抖动位,根据第二子位数确定待调制数字量的抖动位,将待调制数字量的非抖动位,与该非抖动位的位数的脉宽调制信号进行调制得到第一信号,将待调制数字量的抖动位进行抖动调制得到第二信号,然后将第一信号和第二信号相加,以提高脉宽调制信号的分辨率的等效有效位数。

57.该方法通过数字抖动的方式,在不改变原脉宽调制信号的原有位数的情况下,通过数字抖动的方式,提高脉宽调制信号的等效有效位数。既满足了高分辨率的电流等级要求,也不会产生电容啸叫等问题,进一步地,该方法通过纯数字的控制方式,来提高脉宽调制信号的等效有效位数,无需额外增加硬件电路,降低了成本。

58.为了使得本技术的技术方案更加清楚、易于理解,下面以信号处理器的角度,对本技术实施例提供的降低电容啸叫的方法进行介绍。

59.如图3所示,该图为本技术实施例提供了一种降低电容啸叫的方法流程图,该方法包括如下步骤:

60.s301:信号处理器获取脉宽调制信号的分辨率的目标位数。

61.目标位数指色彩丰富的情况下,驱动led脉宽调制信号的分辨率的位数,例如9bit、16bit。信号处理器可以通过多种方式获取分辨率的目标位数,在一些实现方式中,信号处理器可以基于预设色彩等级与目标位数的对应关系,根据用户选择的色彩等级,确定目标位数。在另一些实现方式中,信号处理器还可以直接接收用户配置的目标位数,以获取目标位数。

62.本技术不限定信号处理器获取目标位数的具体方式,本领域技术人员可以根据实际需要进行选择。

63.s302:信号处理器拆分目标位数至少为第一子位数和第二子位数。

64.本技术不限定拆分目标位数为两个子位数,在一些实施例中,还可以将目标位数拆分为更多个子位数,例如三个子位数、四个子位数。多个子位数之和为目标位数。后续为了描述方便,下面以拆分目标位数为两个子位数为例进行介绍。

65.在一些实施例中,信号处理器将目标位数拆分为第一子位数和第二子位数,第二子位数小于第一子位数,第一子位数小于等于啸叫位数阈值。啸叫位数阈值指产生啸叫时,脉宽调制信号的分辨率的位数的临界值。

66.请参阅下表1:

[0067][0068]

该表1中,第一行代表有源晶振的频率变化,第一列代表pwm信号分辨率的变化。

[0069]

以有源晶振的频率为16mhz为例,pwm信号分辨率为8bit和9bit时,载波频率分别为62.5khz和31.25khz,而pwm信号分辨率为12bit时,载波频率为3.9khz,此时,该频率位于人耳可听范围内(20hz~20khz),就会听到电容啸叫。在一些实施例中,可以将9bit作为啸叫位数阈值,当pwm信号超过9bit时,则认为会产生电容啸叫。

[0070]

为了便于理解,以目标位数为12bit为例,信号处理器可以将目标位数拆分为9bit和3bit。其中,9bit为第一子位数,3bit为第二子位数。在一些实施例中,第二子位数小于等于抖动位数阈值,抖动位数阈值指抖动导致低频纹波无法通过输出滤波器滤除时,抖动位数的临界值,例如抖动位数阈值可以为3bit。

[0071]

以上仅仅是以目标位数为12bit、第一子位数为9bit,第二子位数为3bit为例进行介绍。在其他实施例中,目标位数为11bit、则第一子位数可以为9bit,第二子位数可以为2bit,又例如,目标位数为10bit、则第一子位数可以为8bit,第二子位数可以为2bit。本技术对此不进行限定,本领域技术人员可以根据实际需要选择合适的拆分方式。

[0072]

s303:信号处理器根据第一子位数确定数字量的非抖动位,根据第二子位数确定数字量的抖动位。

[0073]

数字量包括非抖动位和抖动位,以12bit的数字量为例,例如数字量可以为[0000 0011 1111]。

[0074]

在一些实施例中,信号处理器可以根据第一子位数确定非抖动位的位数,例如第一子位数为9bit时,则确定非抖动位的位数为9。在一些实现方式中,信号处理系统从数字量的最高位连续截取与第一子位数对应的位作为非抖动位。如上例,从数字量[0000 0011 1111]的最高位连续截取9位得到非抖动位[0000 0011 1],然后将剩余的低3位作为抖动位[111]。

[0075]

在一些实施例中,信号处理器可以根据第二子位数确定抖动位的位数,例如第二子位数为3bit时,则确定抖动位的位数为3。在一些实现方式中,信号处理系统从数字量的最低位连续截取与第二子位数对应的位作为抖动位。例如,从数字量[0000 0011 1111]的最低位连续截取3位得到抖动位[111],然后将剩余的高9位作为非抖动位[0000 0011 1]。

[0076]

s304:信号处理器将待调制数字量的非抖动位,与该非抖动位的位数的脉宽调制信号进行调整得到第一信号,将待调制数字量的抖动位进行抖动调制得到第二信号。

[0077]

举例说明,非抖动位为[0000 0011 1]时,非抖动位的位数为9bit,信号处理器则采用9bit的脉宽调制信号与待调制数字量的非抖动位进行调制,得到第一信号。在一些实施例中,当非抖动位为[0000 0011 1]时,第一信号为[00000011 1]。

[0078]

在一些实施例中,信号处理器可以通过译码器,将数字量的抖动位进行抖动调制得到待输出的第二信号;其中,译码器包括预设的待调制数字量与第二信号的对应关系。如下表2所示:

[0079]

抖动位待输出的第二信号0000000 00000010000 00010100001 00010110010 01011000101 01011010101 10111100111 01111110111 1111

[0080]

信号处理器可以通过查阅上述表格,通过译码器,将抖动位进行抖动调制得到第二信号。例如,抖动位为[111]时,则信号处理器进行抖动调制得到的第二信号为[0111 1111]。再例如,抖动位为[101]时,信号处理器进行抖动调制得到的第二信号为[0101 1011]。

[0081]

在另一些实施例中,当抖动位包括2位时,可以参见如下表3,将抖动位进行抖动调制得到待输出的第二信号。

[0082]

抖动位待输出的第二信号000000010001100101110111

[0083]

为了便于理解,下面对数字抖动的原理进行介绍。

[0084]

数字抖动是基于输出电压平均值的原理。参见图4,图4示出了一种数字抖动的示

意图,从该图中可以看出,每4个脉冲为一组,在该组的4个脉冲中,会存在1个脉冲增加了一个最低有效位(least significant bit,lsb)。如此,使输出电压的平均值增加了个lsb所对应的输出电压值。相应的,pwm的输出精度就会提高个lsb,即:

[0085][0086]

其中,δu0为输出电压的平均值的变化值,n

pwm

为数字量的输入位数,u

i

为输入电压。

[0087]

基于上述原理,还可以实现输出电压的平均值增加个lsb,个lsb,如图5所示,该图示出了一种两位数字抖动的示意图。从图中可以看出,两位数字抖动的输出电压的平均值的最小变化量为:

[0088][0089]

其中,δu

0min

为输出电压的平均值的最小变化量,n

dither

为2,即抖动位数。令n

eff

=n

pwm

n

dither

,即pwm输出的等效有效位数n

eff

为n

pwm

与n

dither

之和,如此,提高了pwm输出的等效有效位数。

[0090]

以上介绍了2位数字抖动的原理,3位数字都有的原理相类似,此处不再赘述。

[0091]

s305:信号处理器将第一信号和第二信号相加,以提高脉宽调制信号的分辨率的等效有效位数。

[0092]

在一些实施例中,一个开关动作是指输出一个脉冲,例如,5个开关动作,则输出5个脉冲。在本实施例中,信号处理器可以以第二信号的位数个开关动作为一个周期,例如,第二信号[0111 1111]包括8位,则以8个开关动作为一个周期。

[0093]

例如第一信号为[0000 0011 1],第二信号中每个子信号依次为、[0000 0000]、[0000 0001]、[0001 0001]、[0010 0101]、[0101 0101]、[0101 1011]、[0111 0111]和[0111 1111]。以第二信号为[0111 1111]为例,信号处理器在一个开关动作的周期内输出的脉宽调制信号的占空比为的脉宽调制信号的占空比为进而得到脉宽调制信号的平均占空比如下:

[0094][0095]

可见,该脉宽调制信号的占空比的最小变化量为如下表4所示。

[0096][0097]

在一些实施例中,信号处理器可以输出相加后的脉宽调制信号。由此,信号处理器通过3位数字抖动,在原有位数9位的pwm信号的基础上,实现脉宽调制信号的分辨率的等效有效位数为12位。在不改变原始位数的情况下,提高了脉宽调制信号的分辨率的等效有效位数。参见上表1,在有源晶振的频率为16mhz时,通过原有位数为9bit和3bit数字抖动的方式得到脉宽调制信号的分辨率的等效有效位数为12bit,载波的频率为31.25khz,不在人耳可听范围内(20hz~20khz),因此,将不会听到电容啸叫。进一步地,通过上述方法,无需增加额外的电路,节约了成本。

[0098]

基于上述内容描述,本技术提供了一种降低电容啸叫的方法,该方法通过数字抖动的方式,在不改变原脉宽调制信号的原始位数的情况下,提高脉宽调制信号的分辨率的等效有效位数。具体地,该方法包括获取脉宽调制信号的分辨率的目标位数,拆分目标位数至少为两个位数,例如第一子位数和第二子位数,其中第二子位数小于第一子位数,第一子位数小于等于啸叫位数阈值;根据第一子位数确定数字量的非抖动位,根据第二子位数确定数字量的抖动位,将数字量的非抖动位,与非抖动位的位数的脉宽调制信号进行调制得到第一信号,将数字量的抖动位进行抖动调制得到第二信号,然后将第一信号和第二信号相加,以提高脉宽调制信号的等效有效位数。如此,该方法既满足了高分辨率的电流等级要求,也不会产生电容啸叫等问题,进一步地,该方法通过纯数字的控制方式,来提高脉宽调制信号的分辨率的等效有效位数,无需额外增加硬件电路,降低了成本。

[0099]

本技术实施例还提供了一种降低电容啸叫的装置,如图6所示,该装置包括:获取

模块601,拆分模块602,调制模块603和合成模块604。

[0100]

获取模块601,用于获取脉宽调制信号的分辨率的目标位数;

[0101]

拆分模块602,用于拆分所述目标位数至少为第一子位数和第二子位数;其中,所述第二子位数小于所述第一子位数,所述第一子位数小于等于啸叫位数阈值;

[0102]

调制模块603,用于根据所述第一子位数确定待调制数字量的非抖动位,根据所述第二子位数确定所述待调制数字量的抖动位;将所述待调制数字量的非抖动位,与所述非抖动位的位数的脉宽调制信号进行调制得到第一信号,将所述待调制数字量的抖动位进行抖动调制得到第二信号;

[0103]

合成模块604,用于将所述第一信号和所述第二信号相加,以提高所述脉宽调制信号的分辨率的等效有效位数。

[0104]

作为一种可能的实现方式,所述装置还包括:输出模块;

[0105]

所述输出模块,用于输出所述脉宽调制信号。

[0106]

作为一种可能的实现方式,所述调制模块603,具体用于通过译码器,将所述待调制数字量的抖动位进行抖动调制得到第二信号;其中,所述译码器包括预设的待调制数字量与第二信号的对应关系。

[0107]

作为一种可能的实现方式,所述第二子位数小于等于抖动位数阈值。

[0108]

作为一种可能的实现方式,所述调制模块603,具体用于从待调制数字量的最高位连续截取与所述第一子位数对应的位作为非抖动位。

[0109]

作为一种可能的实现方式,所述调制模块603,具体用于从待调制数字量的最低位连续截取与所述第二子位数对应的位作为抖动位。

[0110]

本技术实施例提供了一种设备,该设备包括存储器和处理器;

[0111]

所述处理器用于执行所述存储器中的指令,以使得所述设备执行上述方法实施例中任一种可能的方法。

[0112]

本技术实施例提供了一种计算机可读存储介质,该计算机可读存储介质包括指令,所述指令用于指示上述设备执行上述方法实施例中任一种可能的方法。

[0113]

本说明书中的各个实施例均采用递进的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。尤其,对于装置实施例而言,由于其基本相似于方法实施例,所以描述得比较简单,相关之处参见方法实施例的部分说明即可。以上所描述的装置实施例仅仅是示意性的,其中所述作为分离部件说明的单元及模块可以是或者也可以不是物理上分开的。另外,还可以根据实际的需要选择其中的部分或者全部单元和模块来实现本实施例方案的目的。本领域普通技术人员在不付出创造性劳动的情况下,即可以理解并实施。

[0114]

应当理解,在本技术中,“至少一个(项)”是指一个或者多个,“多个”是指两个或两个以上。“和/或”,用于描述关联对象的关联关系,表示可以存在三种关系,例如,“a和/或b”可以表示:只存在a,只存在b以及同时存在a和b三种情况,其中a,b可以是单数或者复数。字符“/”一般表示前后关联对象是一种“或”的关系。“以下至少一项(个)”或其类似表达,是指这些项中的任意组合,包括单项(个)或复数项(个)的任意组合。例如,a,b或c中的至少一项(个),可以表示:a,b,c,“a和b”,“a和c”,“b和c”,或“a和b和c”,其中a,b,c可以是单个,也可以是多个。

[0115]

以上,仅是本技术的较佳实施例而已,并非对本技术作任何形式上的限制。虽然本技术已以较佳实施例揭露如上,然而并非用以限定本技术。任何熟悉本领域的技术人员,在不脱离本技术技术方案范围情况下,都可利用上述揭示的方法和技术内容对本技术技术方案做出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本技术技术方案的内容,依据本技术的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本技术技术方案保护的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。