1.本发明属于电源管理技术领域,具体涉及一种采样保持与膝点检测电路。

背景技术:

2.近年来,随着电子设备的发展,电子设备追求具有更高功率密度,更高效率以及更小体积的电源。早期主要的电源类型,线性稳压电源已经不能满足这些日益提高的要求,因此,开关电源成为主流的趋势。传统的反激式变换器采用光耦器件和tl431对输出电压信息进行采样,然而光耦器件和tl431占用体积大,没有办法实现内部集成,不利于实现小型化,且光耦器件受温度和辐照影响较大,采样精度会受环境影响。因此,原边反馈反激式变换器因其更简单的外围结构设计、更小的体积和更低的成本受到市场青睐。

3.由于采样的精确度决定了输出电压的精确度,原边反馈反激式变换器设计的关键点之一就是采样保持和膝点检测电路的设计。具体而言,如图1所示,在副边导通原边关断的时候,输出电压信息通过原边绕组反激到原边,体现在功率管漏端电压v

sw

上,再通过vin钳位电路将反馈电压v

fb

钳位到vin,从而使得反馈电阻r

fb

两端的电压仅包含反激电压信息,再通过参考电阻r

ref

产生反馈参考电压v

rref

,反馈参考电压v

rref

传递到采样保持和膝点检测电路中,系统通过采样得到的输出电压信息对占空比进行调节,从而实现恒定电压输出。因此,输出电压的准确检测才能够保证系统的输出电压有较高的精度。在膝点处,副边的寄生阻抗产生的压降由于副边电感电流为零而不对v

sw

产生影响,此时的v

sw

能够更加精确地描述输出电压的信息。

4.现有的膝点检测和采样保持方案中,有使用多路电路进行依次采样,得到多个采样值,通过上一个采样点的电压减去固定的电压值与当前采样电压值进行对比,得到真实采样值,再将最真实的采样值送到后续模块的采样方法,然而这种方法需要使用多个电容来对采样值进行存储,不利于片内集成,而且对多路电路依次采样的控制电路也较为复杂,且采样的精确度不高。数字辅助利用模数转换器adc和数模转换器dac也常被用于精确膝点检测,但是成本通常过于高昂。还有的方案采用电阻

‑

电容组成延时电路将经过延时后的电压与v

fb

通过额外的比较器进行比较得到膝点,这种方法采用了额外的比较电路,因此功耗相对较大。

技术实现要素:

5.本发明主要设计实现了一种采样保持与膝点检测电路,该电路的缓冲器和比较器复用一个折叠式共源共栅结构,省去了额外的运放,降低了电路了功耗和成本。在反馈电压到达膝点时,电压波形会急剧下降,而缓冲器自身存在延时,两个电压之间形成压差使得比较器翻转,从而检测得到膝点信号,进而将采样开关打开,采样电容c

delay

存储的电荷分享到保持电容c

hold

,一个窄脉冲时间后,关闭比较器,同时采样开关断开,完成采样工作,得到膝点电压值。

6.为实现上述目的,本发明的技术方案为:

7.一种采样保持与膝点检测电路,用于检测原边反馈反激式变换器在副边电感电流为零时的膝点电压,包括缓冲器、比较器、第一nmos管、第二nmos管、第三nmos管、第一电阻、第一电容、第二电容和电压源;

8.所述缓冲器的同相输入端接反馈电压,其反相输入端接其输出端,缓冲器的输出端依次通过第一电阻和第一电容后接地,将缓冲器的使能信号定义为第一使能信号,输出定义为延迟电压;

9.所述比较器的同相输入端接延迟电压,其反相输入端接电压源的正端,电压源的负端接反馈电压,将比较器的使能信号定义为第二使能信号,输出电压定义为判断电压,所述电压源产生固定失调电压;

10.所述第一nmos管的漏极接延迟电压,其栅极接第三使能信号;

11.所述第二nmos管的源极和漏极接第一nmos管的源极,第二nmos管的栅极接第一使能信号的反向信号,第一nmos管源极与第二nmos管源漏极的连接点通过第二电容后接地,将第一nmos管源极、第二nmos管源漏极、第二电容的连接点输出定义为膝点电压保持电压;

12.所述第三nmos管的漏极接第一电阻、第一电容和第一nmos管漏极的连接点,第三nmos管的栅极接脉冲信号,第三nmos管的源极接地;当原边导通时,脉冲信号为高电平,第三nmos管打开,当副边导通时,脉冲信号为低电平,第三nmos管关断;

13.当副边导通且反馈电压上升的时期,第一使能信号控制缓冲器开启,第二使能信号控制比较器关断,使延迟电压一直跟随反馈电压,从而更新第一电容的电压值;当反馈电压进入平台期后,第二使能信号控制比较器开启,在膝点到达时,比较器翻转,判断电压由低电位翻转为高电位,第三使能信号对应翻高,第一nmos管打开进行采样,第一电容的电荷分享到第二电容,第一使能信号控制缓冲器关断使得延迟电压保持膝点电压;经过一个窄脉冲时间之后,第三使能信号翻低,第一nmos管关断而第二nmos管开启,同时第二使能信号控制比较器关断,第一使能信号控制缓冲器开启。

14.进一步的,所述比较器包括第一pmos管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第四nmos管、第五nmos管、第六nmos管、第七pmos管、第八pmos管、第二电阻、第三电阻、第四电阻、第十nmos管、第十二nmos管;所述缓冲器包括第一pmos管、第二pmos管、第三pmos管、第四pmos管、第六pmos管、第四nmos管、第五nmos管、第七pmos管、第八pmos管、第七nmos管、第八nmos管、第九nmos管、第二电阻、第三电阻、第四电阻、第十一nmos管;

15.其中,第一pmos管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第六pmos管的源极均接电源;第一pmos管的栅漏互连,其漏极接电流源;第二pmos管、第三pmos管、第四pmos管、第五pmos管、第六pmos管的栅极均接第一pmos管的漏极;第一pmos管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第六pmos管组成电流镜为电路提供偏置电流,其镜像比为1:8:4:4:4:1;

16.第七pmos管的源极接第二pmos管的漏极,第七pmos管的栅极通过第四电阻后接反馈电压,第七pmos管的漏极通过第二电阻后接地;

17.第二nmos管的漏极通过第四电阻后接反馈电压,第二nmos管的栅极和源极互连,第二nmos管的的源极接地;

18.第八pmos管的源极接第二pmos管的漏极,第八pmos管的栅极接第七nmos管的源极,第八pmos管的漏极通过第三电阻后接地;

19.第四nmos管的栅极和漏极接第三pmos管的漏极,第四nmos管的源极通过第二电阻后接地;第五nmos管的漏极接第四pmos管的漏极,第五nmos管的栅极接第三pmos管的漏极,第五nmos管的源极通过第三电阻后接地;

20.第六nmos管的漏极接第五pmos管的漏极,第六nmos管的栅极接第四pmos管的漏极,第六nmos管的源极接地;

21.第十nmos管的漏极接第五pmos管的漏极,第十nmos管的栅极接第二使能信号,第十nmos管的源极接地;

22.第五pmos管漏极、第六nmos管漏极与第十nmos管漏极的连接点为比较器的输出端;

23.第七nmos管的漏极接电源,第七nmos管的栅极接第四pmos管的漏极;第八nmos管的栅极和漏极接第六pmos管的漏极,第八nmos管的源极接地;第九nmos管的漏极接第七nmos管的源极,第九nmos管的栅极接第六pmos管的漏极,第九nmos管的源极接地;

24.第十一nmos管的漏极接第六pmos管的漏极,第十一nmos管的栅极接第一使能信号,第十一nmos管的源极接地;

25.第七nmos管源极、第八pmos管栅极与第九nmos管漏极的连接点为缓冲器的输出端。

26.本发明的有益效果为:能得到精确的膝点电压值,同时降低了电路了功耗和成本。

附图说明

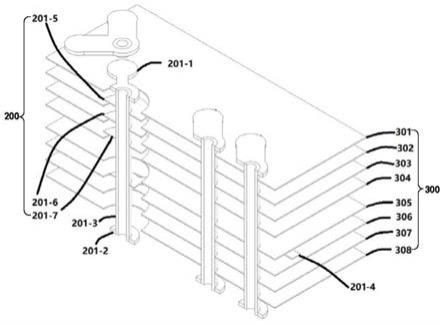

27.图1原边反馈反激式变换器原理图。

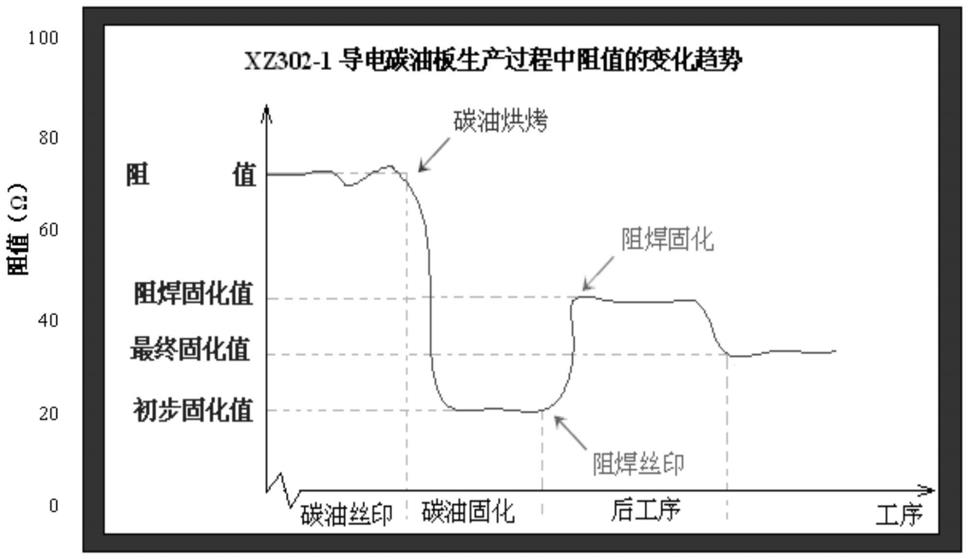

28.图2反馈参考vrref电压和电感电流的波形图。

29.图3本发明提出的采样保持和膝点检测方案框图。

30.图4本发明提出的采样保持和膝点检测方案控制时序图。

31.图5本发明提出的采样保持和膝点检测电路图。

具体实施方式

32.下面结合附图,对本发明技术方案进行详细描述:

33.应用本发明提出的原边反激式变换器的原理图如图1所示。反馈参考v

rref

电压和电感电流的波形如图2所示,其中i

pri

为原边电感电流,i

sec

为副边电感电流。在副边开启的toff时间段内,t0

‑

t1受到漏感和功率管寄生电容的影响,v

sw

会出现振铃从而使得v

rref

也会出现振铃,系统为了避免误触发,一般会选择屏蔽这段时间。振铃结束之后,t1

‑

t2内,受到副边寄生阻抗和副边电流下降的影响,v

sw

会有下降到趋势,这段时间内v

sw

可以表示为

34.v

sw

(t)=vin n

ps

(v

out

v

f

i

sec

(t)r

s

)

35.其中,vin为输入电压,n

ps

为原边和副边变压器的匝比,v

f

为副边二极管的导通压降,r

s

为副边等效阻抗。

36.在t2时刻,副边电流降为0,到达膝点,此时的v

sw

不再包含副边寄生电阻的信息。膝点之后,v

rref

会发生高频谐振,电压纹波变化剧烈。依据膝点的特性,本发明提出的一种采样保持和膝点检测方案如图3所示。该方案主要包括:缓冲器a1,比较器a2,一阶低通滤波器电阻r

delay

和电容c

delay

,保持电容c

hold

,采样开关mn1,虚拟开关mn2以及复位开关管mn3。

37.本发明提出的采样保持和膝点检测方案控制时序如图4所示,当副边导通时,mn3管关断,反馈参考电压v

rref

迅速上升,同时由于缓冲器的作用v

buffer

电压会跟随v

rref

电压从零开始上升。t0

‑

t1,即副边刚刚导通时,功率管寄生电容上还储存着大量的电荷,功率管寄生电容与原边电感形成谐振,为了避免这段时间内比较器a2误触发,en_leb不使能,因此此时仅缓冲器a1工作,a2不工作。t1

‑

t2,v

rref

进入平台期,en_leb使能,比较器a2开始工作,缓冲器a1一直开启v

buffer

电压一直跟随v

rref

电压,更新电容c

delay

的电压值。在t2时刻,副边电感电流下降至0,膝点到达,v

rref

电压迅速下掉,而此时受限于下拉转换速率以及缓冲器延时的影响,v

buffer

无法及时跟随,v

buffer

与v

rref

之间存在压差,使得比较器a2翻转,knee由低电位翻转为高电位,v

ses

电位翻高,采样开关打开,c

delay

的电荷被分享到c

hold

,en_hold信号将缓冲器a1的下拉电流关断使得v

buffer

保持膝点电压,确保膝点电压准确的同时保证v

buffer

与v

rref

的压差,使得比较器不出现误动作。经过一个较小的窄脉冲时间之后,v

ses

电位翻低,采样开关mn1断开,虚拟开关mn2打开,对时钟馈通进行补偿,en_leb电位翻高,关断比较器a2,保证膝点之后的谐振不会使得比较器误触发,en_hold电位翻低,a1开始正常工作。当原边导通时,即pwm信号为高电位时,mn3管打开,将c

delay

上极板的电压复位到零。

38.采样保持和膝点检测电路如图5所示。图中,mp1、mp2、mp3、mp4、mp5和mp6管组成电流镜为电路提供偏置电流,其镜像比为1:8:4:4:4:1。电路主要分为四个部分,第一部分为共源共栅结构,由电流镜mp2、mp3、mp4、mn4和mn5,mn4与mn5的镜像比为1:1,输入对管mp7、mp8,负载电阻r1和r2,限流电阻r3以及用于防护静电放电(esd)的ggnmos管mn12构成;第二部分为mp5和mn6,以及开关管mn10,这一部分与第一部分结合起来构成比较器a2;第三部分由电流镜mp6、mn8和mn9,其中mn8和mn9的镜像比为1:1,源随管mn7,以及开关管mn11构成,这一部分与第一部分结合起来构成缓冲器a1;第四部分由一阶低通滤波器(电阻r

delay

和电容c

delay

),保持电容c

hold

,采样开关mn1,虚拟开关mn2以及复位开关管mn3构成。本发明采用比较器和缓冲器共用一个折叠式共源共栅的结构,省去了额外的运放,降低了电路了功耗和成本。

39.下面对采样保持和膝点检测电路进行具体阐述。第一部分为比较器和缓冲器复用的共源共栅结构,旨在为缓冲器和比较器提供较大的增益。由于v

rref

由芯片外部引入,为了避免较大电流和静电对输入管mp7的损害,分别采用r3限制电流大小,以及ggnmos管mn12进行静电泄放,同时r3和mn12的寄生电容组成一阶低通滤波器,可以对v

rref

进行简单地滤波。折叠式的共源共栅结构在保证输入共模范围的同时保证了该结构具有较大的输出电阻,从而确保了该结构具有较大的增益。

40.输入共模范围为

41.8i

bias

r1‑

|v

thp

|≤icmr≤v

dd

‑

v

ov

‑

|v

thp

|

42.其中,i

bias

为基准电流,v

thp

为pmos管的阈值电压,vov为过驱动电压。

43.复用共源共栅结构的增益为

44.a

v1

=g

m,mp7

{r

o,mp4

||[g

m,mn5

r

o,mn5

(r2||r

o,mp8

)]}

[0045]

其中g

m,mp7

,g

m,mn5

为mp7与mn5的跨导,r

o,mp4

,r

o,mn5

,r

o,mp8

分别为mp4,mn5以及mp8的导通电阻。

[0046]

为了确保采样电压的准确度,首先需要保证缓冲器输出精度。精度需求在0.5%时,缓冲器的开环增益要求在200倍以上。缓冲器的开环增益可以表示为

[0047][0048]

其中g

m,mn7

为mn7的跨导,r

o,mn9

为mn9的导通电阻。

[0049]

膝点检测需要在v

rref

电压下掉时,v

buffer

不会迅速跟随v

rref

下掉,缓冲器的负向转换速率需要较小,可以表示为

[0050][0051]

负向转换速率与下拉电流相关,为了保证较小的下拉电流,mp1:mp6以及mn8:mn9电流镜的比值都为1:1。

[0052]

与缓冲器复用折叠式共源共栅结构的比较器,不需要额外的运放就可以获得较大的开环增益,可以表示为

[0053]

a

v3

=a

v1

×

g

m,mn6

(r

o,mp5

||r

o,mn6

)

[0054]

=g

m,mp7

{r

o,mp4

||[g

m,mn5

r

o,mn5

(r2||r

o,mp8

)]}

×

g

m,mn6

(r

o,mp5

||r

o,mn6

)

[0055]

比较器翻转的延时由小信号延时和大信号延时组成。小信号延时取决于开环状态的

‑

3db带宽,而大信号延时由转换速率决定。膝点到达时,v

rref

迅速下掉,因此大信号延时占据主导地位。比较器的正向转换速率可以表示为

[0056][0057]

其中c

knee

为比较器输出节点的寄生电容,主要包含mp5和mn6的栅漏电容。

[0058]

为了保证采样的精确度,需要利用r

delay

与c

delay

的延时来消除比较器延时的影响,即需要保证

[0059][0060]

其中,v

turn

为knee触发后级控制逻辑的翻转电平,一般为vdd/2。

[0061]

同时当膝点达到,v

ses

控制采样开关开启,c

delay

和c

hold

电容进行电荷分享。根据电荷守恒定理可得,采样保持结束后的v

hold

为:

[0062][0063]

可以看出,当c

delay

越大,c

hold

越小时,v

hold

与膝点电压的误差越小,因此通常需要让c

delay

的容值是c

hold

容值的十倍及以上。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。