1.本发明的实施例涉及存储器电路及其操作方法。

背景技术:

2.在一些应用中,集成电路(ic)包括将数据存储在基于电阻的存储器件(例如,电阻式随机存取存储器(rram)单元)的阵列中的存储器电路。诸如rram单元的基于电阻的存储器件可被编程为高电阻状态(hrs)或低电阻状态(lrs),每个状态代表由rram单元存储的逻辑状态。

技术实现要素:

3.根据本发明实施例的一个方面,提供了一种存储器电路,包括:偏置电压发生器,包括第一电流路径、第一电压钳位器件和第一缓冲器,其中偏置电压发生器被配置为接收参考电压并基于参考电压与第一驱动电压之间的电压差生成第一偏置电压;第一电压钳位器件被配置为基于第一偏置电压通过将第一驱动电压施加至第一电流路径生成第一驱动电压,并且第一缓冲器被配置为接收第一偏置电压并基于第一偏置电压生成第二偏置电压;第二电流路径,包括基于电阻的存储器件;以及第二电压钳位器件,被配置为基于第二偏置电压生成第二驱动电压,并将第二驱动电压施加至第二电流路径。

4.根据本发明实施例的另一个方面,提供了一种存储器电路,包括:第一电流路径,包括第一基于电阻的存储器件;第一电压钳位器件,被配置为在第一电流路径处生成第一驱动电压;和偏置电压发生器,包括第一缓冲器和复制电路,复制电路被配置为模拟包括基于电阻的存储器件的第一电流路径的至少一部分的电阻,其中偏置电压发生器被配置为接收参考电压并生成第一偏置电压,第一缓冲器被配置为基于第一偏置电压生成第二偏置电压,复制电路被配置为基于第二偏置电压生成第二驱动电压,并且偏置电压发生器被配置为基于参考电压和第二驱动电压之间的电压差来调节第一偏置电压。

5.根据本发明实施例的又一个方面,提供了一种存储器电路,包括:参考级,被配置为生成参考电压;电压感测级,被配置为检测参考电压和第一偏置电压之间的电压差;增益级,被配置为基于电压差生成第二偏置电压;缓冲器,被配置为基于第二偏置电压生成第一偏置电压;第一电压钳位器件,被配置为基于第一偏置电压生成第一驱动电压;和第一电流路径,包括第一基于电阻的存储器件,其中,第一电压钳位器件被配置为将第一驱动电压施加至第一电流路径。

附图说明

6.当结合附图进行阅读时,根据下面详细的描述可以最佳地理解本发明的各个方面。应该注意,根据工业中的标准实践,各种部件没有被按比例绘制。实际上,为了清楚的讨论,各种部件的尺寸可以被任意增加或减少。

7.图1a和图1b是根据一些实施例的存储器电路的示图。

8.图2是根据一些实施例的存储器电路的示图。

9.图3是示出根据一些实施例的在读取操作期间的偏置电压的曲线图。

10.图4是根据一些实施例的存储器电路的示图。

11.图5是根据一些实施例的存储器电路的示图。

12.图6是根据一些实施例的存储器电路的示图。

13.图7是根据一些实施例的执行读取操作的方法的流程图。

具体实施方式

14.以下公开内容提供了许多不同实施例或实例,用于实现所提供主题的不同特征。下面描述组件、值、操作、材料、布置等的特定示例以简化本公开。当然这些仅是实例并不旨在限定。可以预期其他组件、值、操作、材料、布置等。例如,在以下描述中,在第二部件上方或上形成第一部件可以包括第一部件和第二部件直接接触的实施例,也可以包括在第一部件和第二部件之间形成额外的部件使得第一部件和第二部件可以不直接接触的实施例。而且,本发明在各个实例中可以重复参考数字和/或字母。这种重复仅是为了简明和清楚,其自身并不表示所论述的各个实施例和/或配置之间的关系。

15.此外,为了便于描述,本文中可以使用诸如“在

…

下方”、“在

…

下面”、“下部”、“在

…

上面”、“上部”等的空间关系术语,以描述如图中所示的一个元件或部件与另一元件或部件的关系。除了图中所示的方位外,空间关系术语旨在包括器件在使用或操作过程中的不同方位。装置可以以其他方式定位(旋转90度或在其他方位),并且在本文中使用的空间关系描述符可以同样地作相应地解释。

16.在一些实施例中,与其他方法相比,存储器电路使用反馈配置来生成偏置电压,由此减小负载并且提高读取操作的速度。存储器电路包括具有基于电阻的存储器件的电流路径和模拟包括基于电阻的存储器件的电流路径的至少一部分的电阻特性的复制电阻器件。在一些实施例中,提供局部缓冲电路以生成偏置电压,该偏置电压在读取操作期间由电压钳位器件用来将驱动电压驱动至电流路径,并且反馈由配置为生成提供给复制电阻器件的另一偏置电压的另一缓冲电路提供。在一些实施例中,使用包括通过复制电阻器件传导以生成参考电压的参考电流的反馈配置来提供偏置电压。

17.与不包括这种反馈布置的方法相比,偏置电压发生器的待机功率降低,并且可以动态传递的电荷量增加,从而降低功耗并提高存储器电路的速度。

18.图1a和图1b是根据一些实施例的存储器电路100的示图。图1a是包括与电压钳位器件120的多个实例耦合的偏置电压发生器110的顶层示图,其串联耦合在感测放大器sa的对应实例与电流路径111之间。图1b是耦合到存储器电路100中的偏置电压发生器110的电流路径111、感测放大器sa和电压钳位器件120的单个实例的示图。

19.图1a描绘了下面讨论的偏置电压发生器110的细节,图1b描绘了包括基于电阻的存储器件150的实例的电流路径111的细节。

20.出于说明的目的,图1b描绘了耦合在导线l1和l2之间的每个基于电阻的存储器件150。在一些实施例中,存储器电路100是存储器宏的子集(未示出),其包括一个或多个附加组件,例如,除了图1a和图1b所示的基于电阻的存储器件150的阵列之外,还包括至少一个控制或逻辑电路。图1a还描绘了电源电压/节点vdd,并且图1a和图1b中的每一个都描绘了

由接地符号表示的参考电源电压/节点,例如地。

21.每个基于电阻的存储器件150是能够具有指示逻辑状态的高电阻状态(hrs)或低电阻状态(lrs)的存储器存储器件。在一些实施例中,每个基于电阻的存储器件150包括耦合到其相应的导线l1的端子152和耦合到其相应的导线l2的端子153。基于电阻的存储器件150包括电阻层(未示出),例如基于一个或多个细丝(也称为导电路径)的相应存在或不存在,该电阻层能够具有与hrs对应的主要绝缘性或与lrs对应的主要导电性。在操作中,形成细丝,例如,从而基于各种机制中的一种或多种,例如空位或缺陷迁移或另一种合适的机制,将基于电阻的存储器件150置位到lrs,并且将其断开,从而基于加热或一种或多种其他合适的机制,将基于电阻的存储器件150复位到hrs。

22.基于电阻的存储器件150包括选择晶体管(未示出),其与电阻层串联耦合并且具有耦合至输入端子(未示出)的栅极,从而被配置为响应于激活电压,将基于电阻的存储器件150耦合至其相应的导线对l1/l2。在一些实施例中,基于电阻的存储器件150包括rram器件、磁隧道结(mtj)器件、相变存储器(pcm)器件等。在图1a和图1b的一些实施例中,每个基于电阻的存储器件150包括rram器件。

23.在一些实施例中,基于电阻的存储器件150在lrs中的电阻值在1千欧(kω)至4kω的范围内和/或在hrs中的电阻值在15kω至30kω的范围内。其他电阻值/范围在本公开的范围内。

24.由此,基于电阻的存储器件150可以基于存储器单元电压v12来读取,该存储器单元电压v12等于端子152处的电压v1与端子153处的电压v2之差,其减小选择晶体管上的漏极

‑

源极电压的水平。

25.存储器电路100或包括存储器电路100的存储器宏被配置为使得存储器单元电压v12具有与在读取操作中检测基于电阻的存储器件150的lrs或hrs对应的读取电压水平。为了对基于电阻的存储器件150进行编程,将存储器单元电压v12设置为第一编程电压水平以将基于电阻的存储器件150设置为lrs,并且将其设置为第二编程电压水平以将基于电阻的存储器件150设置为hrs。在一些实施例中,第一编程电压水平和第二编程电压水平中的每一个都在大小上高于读取电压水平。

26.在各个实施例中,第一写入操作和第二写入操作以及读取操作中的每一个具有相同的极性,或者第一写入操作或第二写入操作或读取操作中的一个具有与第一写入操作或第二写入操作或读取操作中的另两个不同的极性。在第一写入操作和第二写入操作和读取操作的每一个中,施加到基于电阻的存储器件150的存储器单元电压v12使电流id沿由存储器单元电压的极性确定的方向在端子152和153之间流动。

27.在读取操作期间,将存储器单元电压v12设置为读取电压水平,以便生成电流id。当基于电阻的存储器件150处于hrs时,电流id具有第一电流水平,而当基于电阻的存储器件150处于lrs中时,电流id具有第二电流水平。因为hrs的电阻水平高于lrs的电阻水平,所以第一电流水平低于第二电流水平。每个感测放大器sa被配置为检测电流id是具有第一电流水平还是第二电流水平,并且因此检测其对应的基于电阻的存储器件150是在hrs还是在lrs。

28.每个基于电阻的存储器件150都设置在电流路径111中。电压钳位器件120被配置为生成驱动电压vd并将驱动电压vd施加到电流路径111以生成电流id。在图1a和图1b中,每

个感测放大器sa被描绘为耦合到单个相应的基于电阻的存储器件150和一对导线l1、l2。该配置是提供的非限制性示例以简化说明。在一些实施例中,每个感测放大器sa和每个电压钳位器件120耦合到一组基于电阻的存储器件150,其中该组中的每个基于电阻的存储器件150耦合到不同的一对导线。

29.两个或更多个电路元件被认为是基于两个或更多个电路元件之间的一个或多个直接电连接和/或一个或多个间接电连接(包括一个或多个逻辑器件,例如反相器或逻辑门)而耦合的。在一些实施例中,两个或更多个耦合的电路元件之间的电通信能够被一个或多个逻辑器件修改,例如,反转或使其为有条件的。

30.如图1b所示,每个电流路径111耦合在对应的电压钳位器件120和参考电源节点之间。电压钳位器件,例如电压钳位器件120,是开关器件,例如nmos器件,其被配置为基于在控制端子(例如,栅极端子)处接收到的电压来限制传导路径端子(例如,源极端子)处的电压。

31.电流路径111包括路径段130和140、耦合在路径段130和140之间的导线l1和l2以及耦合在导线l1和l2之间的基于电阻的存储器件150。在一些实施例中,路径段130是被配置为选择导线l1的多路复用器。在这种情况下,路径段140是被配置为选择导线l2的多路复用器。在其他实施例中,路径段130是被配置为选择导线l2的多路复用器。在这种情况下,路径段140是被配置为选择导线l1的多路复用器。

32.在操作中,当将多个基于电阻的存储器件150(耦合在它们各自的导线对之间)耦合到每个感测放大器sa和每个电压钳位器件120时,使用路径段130、140在各种基于电阻的存储器件150中进行选择(通过在导线对之间进行选择)。当通过路径段130、140选择基于电阻的存储器件150时,电流id流过基于电阻的存储器件150(并因此流过对应的一对单独的导线),但不流向也耦合到单独的感测放大器sa和电压钳位器件120的另一基于电阻的存储器件150(以及其他对应的导线对)。

33.为了使感测放大器sa在读取操作中检测所选择的基于电阻的存储器件150是处于hrs还是lrs,施加到电流路径111的驱动电压vd保持在适当的驱动电压水平。然而,由于温度变化引起的电压钳位器件120的操作变化会导致驱动电压水平的变化。

34.为了控制由电压钳位器件120生成的驱动电压vd的驱动电压水平,存储器电路100包括耦合到每个电压钳位器件120的偏置电压发生器110。偏置电压发生器110被配置为生成和控制每个电压钳位器件120的偏置电压vgb。更具体地,偏置电压发生器110被配置为将由每个电压钳位器件120生成的驱动电压vd的驱动电压水平保持为接近恒定电压而与耦合在电压钳位器件120和参考电源节点之间的电阻无关,例如,基于电阻状态。偏置电压发生器110被配置为调节偏置电压vgb的电压水平,以将驱动电压vd保持在所需的驱动电压水平,以使感测放大器sa检测相应的基于电阻的存储器件150是在lrs还是在hrs。

35.偏置电压发生器110包括全局控制电路139和局部缓冲器144。在图1a描绘的实施例中,偏置电压发生器110包括三十二个局部缓冲器144,每个电压钳位器件120一个。在其他实施例中,偏置电压发生器110包括多于三十二个或少于三十二个的局部缓冲器144。每个局部缓冲器144被配置为生成在电压钳位器件120的对应一个处接收的偏置电压vgb。在一些实施例中,局部缓冲器144不由缓冲器141的组件加载,其包括组件以模拟电压钳位器件120的表现以及基于电阻的存储器件150的电流路径111。通过提供局部缓冲器144,可以

减小偏置电压发生器110的尺寸,从而节省功率和面积。

36.在图1a和图1b中,每个电压钳位器件120包括nmos器件。nmos器件的栅极被配置为从与其耦合的局部缓冲器144中的相应一个接收偏置电压vgb。nmos器件的漏极耦合至感测放大器(sa)中的相应一个,而nmos器件的源极耦合至电流路径111。nmos器件被配置为从电流路径生成电流id。

37.在图1a中,全局控制电路139被配置为生成偏置电压vg。在操作中,每个局部缓冲器144接收偏置电压vg,并且每个局部缓冲器144被配置为基于偏置电压vg来调节偏置电压vgb。如下所述,全局控制电路139被配置为调节偏置电压vg的偏置电压水平,以便调节偏置电压vgb的偏置电压水平并按照感测放大器sa的要求保持驱动电压vd的驱动电压水平。通过将全局控制电路139与局部缓冲器144分离,全局控制电路139不被电压钳位器件120和电流路径111加载,并且因此与控制电路由电压钳位器件电路加载的方法相比,能够消耗更少的功率并且占用更小的面积。

38.全局控制电路139包括运算放大器143、缓冲器141和复制电路145。复制电路145被配置为模拟具有基于电阻的存储器件150的电流路径111的至少一部分的电阻。复制电路145被配置为基于电流路径111的电阻提供具有预定电阻值的路径电阻。换句话说,复制电路145被配置为随着第一电流路径111的操作条件(例如,温度、物理、电压条件)改变来模拟第一电流路径111的电阻表现。在各种实施例中,复制电路145包括多晶硅材料(poly)、包括硅的化合物材料、半导体材料或化合物或适合于模拟第一电流路径111的电阻表现的其他材料。在一些实施例中,预定电阻值基于基于电阻的存储器件(例如,基于电阻的存储器件150)或包括基于电阻的存储器件150的电流路径111的至少一些部分的电阻值。

39.在各个实施例中,预定电阻值对应于hrs或lrs中基于电阻的存储器件的电阻值、高于hrs中基于电阻的存储器件的电阻值的电阻值、低于lrs中基于电阻的存储器件的电阻值的电阻值或者hrs和lrs中基于电阻的存储器件的电阻值之间的电阻值。在一些实施例中,复制电路145被配置为模拟电压钳位器件120和整个电流路径111的电阻表现。

40.在各种实施例中,复制电路145被配置为具有等于基于电阻的存储器件电阻值或等于从基于电阻的存储器件电阻值导出的另一值(例如,基于电阻的存储器件电阻值的倍数或分数)的预定电阻值。

41.复制电路145不接收由电压钳位器件120接收的偏置电压vgb。取而代之,缓冲器141被配置为生成偏置电压vgb',并且复制电路145被配置为从缓冲器141接收偏置电压vgb'。缓冲器141被配置为从运算放大器143接收偏置电压vg,并基于偏置电压vg来调节偏置电压vgb'。

42.在操作中,运算放大器143和复制电路145用于模拟电流路径111的电阻表现,并确保驱动电压vd保持在适当的驱动电压水平。运算放大器143被配置为生成偏置电压vg,并基于来自复制电路145的反馈来调节偏置电压vg。更具体地,复制电路145被配置为生成驱动电压vrbl。复制电路145被配置为基于偏置电压vgb'来调节驱动电压vrbl。在操作中,因为复制电路145模拟电流路径111的电阻表现,所以驱动电压vrbl的驱动电压水平模拟驱动电压vd的驱动电压水平。

43.偏置电压发生器110被配置为基于参考电压vref和驱动电压vrbl之间的电压差来调节偏置电压vg。在图1a中,运算放大器143具有被配置为接收参考电压vref的同相输入端

子nit、被配置为接收驱动电压vrbl的反相端子it以及被配置为输出偏置电压vg的输出端子ot。参考电压vref被设置为几乎恒定的参考电压水平。参考电压vref具有预定参考电压水平,其被配置为在操作中使运算放大器143调节偏置电压vg,使得驱动电压vd的驱动电压水平将电流id的电流水平维持在适当的读取水平大小,尽管电流路径111的电阻表现由于操作和环境变化而发生变化。

44.图2是根据一些实施例的存储器电路100a的示图。

45.存储器电路100a是存储器电路100的一个实施例。在图2中,存储器电路100a中与存储器电路100中的组件相同的组件用相同的组件编号标记,如在图1a和图1b中那样,为了简洁起见不再赘述。

46.存储器电路100a包括偏置电压发生器110a,其包括全局控制电路139a和局部缓冲器144a。在该实施例中,单个缓冲器被示为局部缓冲器144a。在一些实施例中,所有局部缓冲器144都与局部缓冲器144a相同。在一些实施例中,其他局部缓冲器144具有与局部缓冲器144a不同的配置,诸如下面关于图4和图5讨论的配置。在一些实施例中,以与局部缓冲器144a相同的方式提供一个或多个其他局部缓冲器144,而以不同的配置提供其他一个或多个其他局部缓冲器144。

47.偏置电压发生器110a包括全局控制电路139a,其是图1a所示的全局控制电路139的一个实施例。全局控制电路139a包括上述运算放大器143以及缓冲器141a和复制电路145a。缓冲器141a是缓冲器141的实施例,如上面关于图1a所描述的,复制电路145a是复制电路145的实施例,上面也参考图1a进行了描述。

48.在图2所描绘的实施例中,偏置电压发生器110a包括耦合在运算放大器143的输出端子ot与参考电源节点之间的电容器件c1。在一些实施例中,电容器件,例如电容器件c1,包括电容器或配置为电容器的nmos或pmos器件。在操作中,电容器件c1例如通过使来自局部缓冲器144和/或144a的噪声去耦来起到稳定偏置电压vg的作用。在一些实施例中,偏置电压发生器110a确实包括电容器件c1。

49.局部缓冲器144a包括电流源200和以源极跟随器配置耦合到电流源200的nmos器件202。在该实施例中,nmos器件202的漏极被配置为接收电源电压vdd,nmos器件202的栅极被配置为接收来自运算放大器143的输出端子ot的偏置电压vg,以及nmos器件202的源极耦合至节点bn1。节点bn1耦合到电压钳位器件120的栅极并且耦合到电流源200的阳极。电流源200的阴极耦合到参考电源节点。这样,nmos器件202被配置为在三极管区域中操作。电流源200被配置为生成电流ib1。nmos器件202被配置为从nmos器件202的源极在节点bn1处生成偏置电压vgb。因此,nmos器件202被配置为在操作中传导电流源200的电流ib1,从而调节偏置电压vgb的偏置电压水平,以使得传导的电流与电流源200生成的电流ib1匹配。由此,nmos器件202被配置为根据偏置电压vg的偏置电压水平的变化来调节偏置电压vgb的偏置电压水平,以便确保电流ib1如由电流源200生成的那样传导。局部缓冲器144a的优点在于,nmos器件202在栅极处汲取的电流很小,并且对电压钳位器件120存在低阻抗。

50.电流源200被配置为在活动状态和待机状态下操作。在活动状态下,局部缓冲器144a正在主动操作以执行读取操作。在待机状态下,局部缓冲器144a接通,但是未主动操作以执行读取操作。因此,电流源200被配置为生成电流ib1,其在活动状态下具有第一电流水平,在待机状态下具有第二电流水平,第一电流水平的大小高于第二电流水平。

51.在一些实施例中,电流源200被配置为生成具有范围从100微安(μa)到10毫安(ma)的第一电流水平的电流ib1。在一些实施例中,电流源200被配置为生成具有范围从900μa到1.1ma(例如,在1ma或附近)的第一电流水平的电流ib1。其他第一电流水平/范围在本公开的范围内。

52.在一些实施例中,电流源200被配置为生成具有范围从1μa到100μa的第二电流水平的电流ib1。在一些实施例中,电流源200被配置为生成具有范围从8μa到12μa(例如,在10μa或附近)的第二电流水平的电流ib1。其他第二电流水平/范围在本公开的范围内。

53.缓冲器141a包括电流源204和以源极跟随器配置耦合到电流源204的nmos器件206。在该实施例中,nmos器件206的漏极被配置为接收电源电压vdd,nmos器件206的栅极被配置为接收来自运算放大器143的输出端子ot的偏置电压vg,以及nmos器件206的源极耦合至节点bn2。节点bn2耦合到复制电路145a中的电压钳位器件120r的栅极并且耦合到电流源204的阳极。电流源204的阴极耦合到参考电源节点。这样,nmos器件206被配置为在三极管区域中操作。电流源204被配置为生成电流ib2。nmos器件206被配置为从nmos器件206的源极在节点bn2处生成偏置电压vgb。因此,nmos器件206被配置为在操作中传导电流源204的电流ib2,从而调节偏置电压vgb'的偏置电压水平,以使得传导的电流与电流源204生成的电流ib2匹配。由此,nmos器件206被配置为根据偏置电压vg的偏置电压水平的变化来调节偏置电压vgb'的偏置电压水平,以便确保电流ib2如由电流源204生成的那样传导。缓冲器141a的优点在于,nmos器件206在栅极处汲取的电流很小,并且对电压钳位器件120r存在低阻抗。

54.在该实施例中,当电流源200处于待机模式时,电流ib2的电流水平约等于电流ib1的第二电流水平。在操作中,局部缓冲器141a还保持反馈以在待机状态期间由局部缓冲器144a生成偏置电压vgb,从而与其他方法相比,在待机状态期间显著减少存储器电路100a消耗的功率。此外,局部缓冲器144a能够将电荷的动态变化传递到其相应的电压钳位器件120的栅极,从而在干扰或过渡期间稳定偏置电压vgb。

55.复制电路145a被配置为模拟电压钳位器件120和电流路径111的电阻表现。复制电路145a包括电压钳位器件120r、复制路径段130r、基于电阻的复制存储器件150r和复制路径段140r。电压钳位器件120r被配置为模拟电压钳位器件120的操作,复制路径段130r被配置为模拟路径段130的电阻表现,基于电阻的复制存储器件150r被配置为模拟基于电阻的存储器件150的电阻表现,复制路径段140r被配置为模拟路径段140的电阻表现。复制路径段130r、基于电阻的复制存储器件150r和复制路径段140r组成复制电流路径111r。复制电流路径111r从而被配置为模拟电流路径111的电阻表现。

56.在该实施例中,电压钳位器件120r是nmos器件,其漏极被配置为接收电源电压vdd,栅极被配置为从节点bn2接收偏置电压vgb',源极耦合至反馈节点fbn。电压钳位器件120r被配置为从源极生成驱动电压vrbl,使得在操作中,驱动电压vrbl在反馈节点fbn处被施加到复制电流路径111r,从而生成传播通过复制电流路径111r的复制电流ir。复制路径段130r包括三个串联耦合的fet,以模拟路径段130之一的电阻,在一些实施例中,该路径段是多路复用器。复制路径段140r包括两个串联耦合的fet,以模拟路径段130之一的电阻,在一些实施例中,该路径段是多路复用器。

57.基于电阻的复制存储器件150r包括复制选择晶体管151r和复制电阻器件rp1。复

制选择晶体管151r被配置为模拟基于电阻的存储器件150中的选择晶体管的电阻表现。在一些实施例中,晶体管151r具有与基于电阻的存储器件150的选择晶体管的尺寸匹配的尺寸,使得,对于由复制电流ir的电流水平和放大器143的输出电压定义的给定晶体管偏置,晶体管151r的压降等于基于电阻的存储器件150中的具有相同晶体管偏置的选择晶体管的漏极

‑

源极电压的值。在各种实施例中,晶体管151r具有与选择晶体管的尺寸有关的尺寸,使得,对于给定晶体管偏置,晶体管151生成电压降,该电压降具有从漏极

‑

源极电压值导出的值,例如,漏极

‑

源极电压值的倍数或分数。

58.电阻器件rp1是一个或多个导电段,被配置为提供路径电阻。一个或多个导电段具有被配置为提供具有预定电阻值的路径电阻的尺寸。在各种实施例中,一个或多个导电段包括多晶硅材料(poly)、包括硅的化合物材料、半导体材料或化合物或适合于具有预定电阻值的其他材料。在一些实施例中,预定电阻值基于基于电阻的存储器件(例如,基于电阻的存储器件150)的电阻值。

59.在各个实施例中,预定电阻值对应于hrs或lrs中基于电阻的存储器件150的电阻值。在一些实施例中,高于在hrs中基于电阻的存储器件150的电阻值的电阻值、低于在lrs中基于电阻的存储器件150的电阻值的电阻值或在hrs和lrs中基于电阻的存储器件150的电阻值之间的电阻值。

60.在各种实施例中,电阻器件rp1被配置为具有等于基于电阻的存储器件150电阻值或等于从基于电阻的存储器件150电阻值导出的另一值(例如,基于电阻的存储器件150电阻值的倍数或分数)的预定电阻值。在一些实施例中,除了基于电阻的存储器件150的电阻值之外,电阻器件rp1的预定电阻值还包括一对导线l1、l2的适当部分的电阻值。因此,在这些实施例中,根据基于电阻的存储器件150的电阻值加上一对导线l1、l2的适当部分的电阻值来设置预定电阻值。

61.在一些实施例中,电阻器件rp1被配置为具有范围从1kω至50kω的预定电阻值。在一些实施例中,电阻器件rp1被配置为具有范围从2kω至5kω的预定电阻值。其他预定电阻值/范围在本公开的范围内。

62.在操作中,驱动电压vrbl的驱动电压水平因此被施加到复制电流路径111r,其模拟包括基于电阻的存储器件150的实例的电流路径111之一的电阻表现。驱动电压vrbl被反馈到运算放大器143的反相端子it,并且运算放大器143被配置为调节偏置电压vg的偏置电压水平,直到驱动电压vrbl的驱动电压水平和参考电压vref的参考电压水平近似相等。从而通过缓冲器141a调节在复制电压钳位器件120r的栅极处接收的偏置电压vgb'的偏置电压水平。作为响应,局部缓冲器144a被配置为对在电压钳位器件120的栅极处接收的偏置电压vgb的偏置电压水平提供对应的调节。结果,电压钳位器件120被配置为响应于偏置电压vgb的偏置电压水平的相应调节,调节驱动电压vd的驱动电压水平。以这种方式,根据参考电压vref的参考电压水平,将驱动电压vd的驱动电压水平保持在适当的电压水平。

63.在一些实施例中,复制电路145a被配置为生成复制电流ir,其具有与如上所述待机状态下电流源200生成的第二电流水平对应的电流水平。在一些实施例中,电流源204被配置为生成电流ib2,其具有与待机状态下由电流源200生成的第二电流水平对应的电流水平。在一些实施例中,运算放大器143被配置为汲取与待机状态下由电流源200生成的第二电流水平相同数量级的电流。

64.因此,存储器电路100a被配置为具有小于基于不包括运算放大器143、缓冲器141a、复制电路145a和局部缓冲器144和/或144a的实例的方法的存储器电路的总待机电流。

65.在非限制性示例中,在待机状态下,运算放大器143汲取40μa,缓冲器141a汲取10μa,复制电路145a汲取10μa,局部缓冲器144和/或144a的32个实例中的每一个汲取10μa,使得在待机状态下,存储器电路100a的偏置电压发生器110a总共汲取380μa。其他电流水平/范围在本公开的范围内。

66.图3是示出根据一些实施例的在读取操作期间的偏置电压vgb的曲线图。

67.图3描绘了非限制性示例,其中随时间描绘由图2所示的存储器电路100a的偏置电压发生器110a生成的偏置电压vgb的实例。控制信号c1被配置为时间t1,与存储器电路100a从截止状态切换到待机状态对应地,在低电压状态到高电压状态之间切换。在时间t2,与存储器电路100a从待机状态切换到激活状态对应地,控制信号c2从低电压状态切换到高电压状态,在此期间,存储器电路100a执行读取操作。在时间t3,读取操作结束,控制信号c2从高电压状态切换到低电压状态,并且存储器电路100a从活动状态切换回到待机状态。

68.在图3的非限制性示例中,偏置电压vgb在从时间t1到时间t2之前的一段时间内具有约300毫伏(mv)的初始电压水平。在时间t2和t3之间,偏置电压vgb在读取操作期间表现出约30mv的电压降,然后返回到约300mv的初始电压水平,该性能水平与不使用运算放大器143、缓冲器141a、复制电路145a以及局部缓冲器144和/或144a的实例的情况下生成偏置电压的其他方法相当。其他初始电压水平和/或电压降水平在本公开的范围内。

69.图4是根据一些实施例的存储器电路100b的示图。

70.存储器电路100b是存储器电路100的一个实施例。在图4中,存储器电路100b中与存储器电路100a和存储器电路100中的组件相同的组件用相同的组件编号标记,如在图1a

‑

图2中那样,为了简洁起见不再赘述。

71.存储器电路100b包括偏置电压发生器110b,其包括全局控制电路139a和局部缓冲器144b。在该实施例中,仅缓冲器1被示为局部缓冲器144b。在一些实施例中,所有局部缓冲器144都与局部缓冲器144b相同。在一些实施例中,其他局部缓冲器144具有与局部缓冲器144b不同的配置,诸如上述局部缓冲器144a和/或本文关于图2、图3和图5讨论的配置。

72.在一些实施例中,以与局部缓冲器144b相同的方式提供一个或多个其他局部缓冲器144,而以不同的配置提供其他一个或多个其他局部缓冲器144。

73.局部缓冲器144b包括电流源400和以源极跟随器配置耦合到电流源400的nmos器件402。在该实施例中,nmos器件402的漏极被配置为接收电源电压vdd,nmos器件402的栅极被配置为接收来自运算放大器143的输出端子ot的偏置电压vg,以及nmos器件402的源极耦合至节点bn1。节点bn1耦合到电压钳位器件120的栅极并且耦合到电流源400的阳极。电流源400的阴极耦合到参考电源节点。这样,nmos器件402被配置为在三极管区域中操作。电流源400被配置为生成电流ib1。在该实施例中,电流源400被配置为在待机状态和活动状态下都以第二电流水平生成电流ib1。因此,与以上关于图2讨论的电流源200不同,取决于存储器电路100b是处于待机状态还是处于活动状态,电流源400不以两个不同的电流水平操作。

74.局部缓冲器144b还包括电流源404和nmos器件406。电流源404和nmos器件406被配置为在待机状态下被停用并且在活动状态下被激活。nmos器件406具有被配置为接收偏置

电压vg的栅极。节点408被配置为接收电源电压vdd。开关410耦合在节点408和nmos器件406的漏极之间。开关410被配置为在待机状态下断开并且在活动状态下闭合。因此,在活动状态下,nmos器件406在nmos器件406的漏极处接收电源电压vdd。在待机状态下,nmos器件406在漏极处不接收电源电压vdd,因此是无效的。nmos器件的源极耦合到节点bn3。节点bn3耦合到节点bn1并且耦合到电压钳位器件120的栅极。开关412耦合在节点bn3和电流源404的阳极之间。开关412被配置为在待机状态下断开并且在活动状态下闭合。因此,电流源404在活动状态下被激活而在待机状态下被去激活。当电流源404被激活时,电流源404被配置为生成具有第三电流水平的电流ib3。在一些实施例中,以上关于图2讨论的第一电流水平约等于第二电流水平加第三电流水平。这样,当局部缓冲器144b在读取操作期间处于活动状态时,电流源400和电流源404被配置为生成具有第一电流水平的总电流。当处于待机状态时,电流源404无效,因此不生成电流ib3,并且总电流等于具有第二电流水平的电流ib1。

75.在待机状态期间,节点bn1处的nmos器件402被配置为从nmos器件402的源极生成偏置电压vgb。因此,nmos器件402被配置为在操作中传导电流源400的电流ib1,并且因此nmos器件402被配置为调节偏置电压vgb的偏置电压水平,以使得传导的电流与电流源400生成的电流ib1匹配。由此,nmos器件402被配置为根据偏置电压vg的偏置电压水平的变化来调节偏置电压vgb的偏置电压水平,以便确保电流ib1如由电流源400生成的那样传导。nmos器件406在待机状态下无效,并且因此不利于调节偏置电压vg或极大地降低功耗。

76.在活动状态下,nmos器件406被激活。节点bn1处的nmos器件402和节点bn3处的nmos器件406被配置为从nmos器件402的源极和nmos器件406的源极共同生成偏置电压vgb。因此,nmos器件402和nmos器件406被配置为在操作中传导等于电流源400的电流ib1和电流源404的电流ib3之和的电流。nmos器件402和nmos器件406被配置为调节偏置电压vgb的偏置电压水平,使得传导的电流与由相应电流源400和404生成的电流ib1 ib3匹配。由此,nmos器件402和406被配置为根据偏置电压vg的偏置电压水平的变化来调节偏置电压vgb的偏置电压水平,以便确保电流ib1 ib3如由电流源400和电流源404生成的那样传导。包括nmos器件402和nmos器件406的局部缓冲器144b由此被配置为提供动态电流,该动态电流传递可以在活动状态下快速处理对偏置电压vgb的调节并且可以在待机状态下以低电流和功率水平操作的电荷。

77.图5是根据一些实施例的存储器电路100c的示图。

78.存储器电路100c是存储器电路100的一个实施例。在图5中,存储器电路100c中与存储器电路100中的组件相同的组件用相同的组件编号标记,如在图1a和图1b中那样,为了简洁起见不再赘述。

79.存储器电路100c包括偏置电压发生器110c,其包括全局控制电路139b和局部缓冲器144c。在该实施例中,仅缓冲器1被示为局部缓冲器144c。在一些实施例中,所有局部缓冲器144都与局部缓冲器144c相同。在其他实施例中,其他局部缓冲器144具有与局部缓冲器144c不同的配置,诸如上述局部缓冲器144a和/或上述针对图2和图4所述的配置。在其他实施例中,以与局部缓冲器144c相同的方式提供一个或多个其他局部缓冲器144,而以不同的配置提供其他一个或多个其他局部缓冲器144。

80.局部缓冲器144c包括电流源500和以源极跟随器配置耦合到电流源500的pmos器件502。在该实施例中,pmos器件502的漏极被配置为接收参考电源电压,pmos器件502的栅

极被配置为接收来自运算放大器143的输出端子ot的偏置电压vg,以及pmos器件502的源极耦合至节点bn1。节点bn1耦合到电压钳位器件120的栅极并且耦合到电流源500的阴极。电流源500的阳极被配置为接收电源电压vdd。这样,pmos器件502被配置为在三极管区域中操作。在该实施例中,电流源500被配置为在待机状态和活动状态下都以第二电流水平生成电流ib1。因此,与图2中的电流源200不同,取决于存储器电路100c是处于待机状态还是处于活动状态,电流源500不以两个不同的电流水平操作。

81.局部缓冲器144c还包括电流源504和pmos器件506。电流源504和pmos器件506被配置为在待机状态下被停用并且在活动状态下被激活。pmos器件506具有被配置为接收偏置电压vg的栅极。pmos器件506的漏极被配置为接收参考电源电压。开关512耦合在参考电源节点和pmos器件506的漏极之间。开关512被配置为在待机状态下断开并且在活动状态下闭合。因此,在活动状态下,pmos器件506在pmos器件506的漏极处接收参考电源电压。在待机状态下,pmos器件506在漏极处不接收参考电源电压,因此是无效的。pmos器件506的源极耦合到节点bn3。节点bn3耦合到节点bn1并且耦合到电压钳位器件120的栅极。节点508被配置为接收电源电压vdd。开关510耦合在节点508和电流源504的阳极之间。电流源504的阴极耦合到节点bn3。pmos器件506的源极也耦合到节点bn3。开关510被配置为在待机状态下断开并且在活动状态下闭合。因此,电流源504在活动状态下被激活而在待机状态下被去激活。当电流源504被激活时,电流源504被配置为生成具有第三电流水平的电流ib3。在一些实施例中,以上关于图2讨论的第一电流水平为或约等于第二电流水平加第三电流水平。这样,当局部缓冲器144c在读取操作期间处于活动状态时,电流源500和电流源504被配置为生成具有第一电流水平的总电流。当处于待机状态时,电流源504无效,因此不生成电流ib3,并且总电流等于具有第二电流水平的电流ib1。

82.在待机状态期间,节点bn1处的pmos器件502被配置为从pmos器件502的源极生成偏置电压vgb。因此,pmos器件402被配置为在操作中传导电流源500的电流ib1,并且因此pmos器件502被配置为调节偏置电压vgb的偏置电压水平,以使得传导的电流与电流源生成的电流ib1匹配。因此,pmos器件502被配置为根据偏置电压vg的偏置电压水平的变化来调节偏置电压vgb的偏置电压水平,以便确保电流ib1如由电流源500生成的那样传导。pmos器件506在待机状态下无效,并且因此不利于调节偏置电压vg或极大地降低功耗。

83.在活动状态下,pmos器件506被激活。节点bn1处的pmos器件502和节点bn3处的pmos器件506被配置为从pmos器件502的源极和pmos器件506的源极共同生成偏置电压vgb。因此,pmos器件502和pmos器件506被配置为在操作中传导等于电流源500的电流ib1和电流源504的电流ib3之和的电流。pmos器件502和pmos器件506被配置为调节偏置电压vgb的偏置电压水平,使得传导的电流与由相应电流源500和504生成的电流ib1 ib3匹配。由此,pmos器件502和506被配置为根据偏置电压vg的偏置电压水平的变化来调节偏置电压vgb的偏置电压水平,以便确保电流ib1 ib3如由电流源500和电流源504生成的那样传导。包括pmos器件502和pmos器件506的局部缓冲器144c由此被配置为提供动态电流,该动态电流传递可以在活动状态下快速处理对偏置电压vgb的调节并且可以在待机状态下以低电流和功率水平操作的电荷。

84.全局控制电路139b是图1a所示的全局控制电路139的一个实施例。全局控制电路139b包括以上关于图1a和图2讨论的运算放大器143和复制电路145a,并且还包括缓冲器

141b。

85.缓冲器141b包括电流源514和以源极跟随器配置耦合到电流源514的pmos器件516。在该实施例中,pmos器件516的漏极耦合到参考电源节点,pmos器件516的栅极被配置为接收来自运算放大器143的输出端子ot的偏置电压vg,以及pmos器件516的源极耦合至节点bn2。节点bn2耦合到复制电路145a中的电压钳位器件120r的栅极并且耦合到电流源514的阴极。电流源514的阳极被配置为接收电源电压vdd。这样,pmos器件516被配置为在三极管区域中操作。电流源514被配置为生成电流ib2。节点bn2处的pmos器件516被配置为从pmos器件516的源极生成偏置电压vgb'。因此,pmos器件516被配置为在操作中传导电流源514的电流ib2,从而调节偏置电压vgb'的偏置电压水平,以使得传导的电流与电流源514生成的电流ib2匹配。由此,pmos器件516被配置为根据偏置电压vg的偏置电压水平的变化来调节偏置电压vgb'的偏置电压水平,以便确保电流ib2如由电流源514生成的那样传导。缓冲器141b的优点在于,pmos器件516在栅极处汲取的电流很小,并且对电压钳位器件120r存在低阻抗。缓冲器141b还保持反馈以在待机状态期间由局部缓冲器144c生成偏置电压vgb,从而与其他方法相比,在待机状态期间显著减少存储器电路100c消耗的功率。

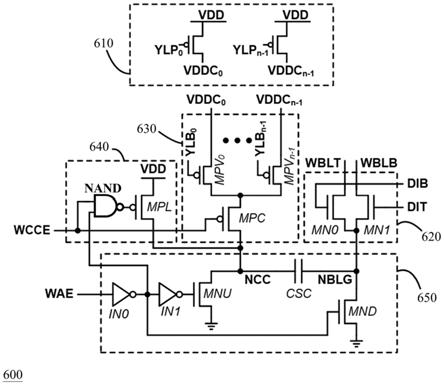

86.图6是根据一些实施例的存储器电路600的示图。

87.存储器电路600包括参考级602、电压感测级604、增益级606、缓冲器608、电压钳位器件610和电流路径612。如下所述,参考级602、电压感测级604、增益级606和缓冲器608共同对应于偏置电压发生器,其被配置为生成以上参考图1

‑

图5讨论的偏置电压vgb。

88.每个电流路径612包括多路复用开关613和基于电阻的存储器件614。多路复用开关613串联耦合在电压钳位器件610中的对应一个和基于电阻的存储器件614之间。每个多路复用开关613被配置为在选择对应的电流路径612时闭合,而在未选择对应的电流路径612时断开。每个基于电阻的存储器件614包括选择晶体管616,其与可变电阻器件618串联耦合并且具有耦合至输入端子(未示出)的栅极,并且因此被配置为响应于激活电压而将基于电阻的存储器件614耦合至对应的导线(未标记)。在一些实施例中,每个可变电阻器件618包括rram器件、mtj器件、pcm器件等。

89.在该实施例中,每个电压钳位器件610是nmos器件,其漏极耦合到感测放大器(未示出),源极耦合到电流路径612中的对应一个,并且栅极耦合到被配置为具有偏置电压vgb的节点nts。在操作中,当给定选择晶体管616导通并且选择晶体管616闭合时,偏置电压vgb使电压钳位器件610将驱动电压vmtj施加到对应的电流路径612,从而生成读取电流imtj。

90.参考级602被配置为生成参考电压vgb_ref。在该实施例中,参考级602包括电流源620、nmos器件m1、电阻器件622和电容器件626。电流源620被配置为在电流源620的阳极处接收电源电压vdd,电流源620的阴极耦合到nmos器件m1的漏极。电流源620被配置为生成具有电流水平iref的电流624。nmos器件m1的漏极耦合到nmos器件m1的栅极。电阻器件622耦合在nmos器件m1的源极与参考电源节点之间。电容器件626耦合在nmos器件m1的栅极与参考电源节点之间。电阻器件622具有rref的电阻,其被配置为以以上关于复制电阻器件rp1和图2所讨论的方式复制电流路径612的电阻。nmos器件m1具有沟道尺寸1x,使得nmos器件m1的电压vgs(未标记)是沟道尺寸1x和电流水平iref的函数。

91.参考级602由此被配置为在操作中生成具有等于nmos器件m1的电压vgs加上电阻器件622上的电压的电压水平的参考电压vgb_ref,每个均基于电流水平iref而生成。在一

些实施例中,电流水平iref对应于可变电阻器件618的预定激活电流。

92.电压感测级604被配置为响应于偏置电压vgb而在节点nrs上生成电压vs。电压感测级604包括nmos器件m3和电阻器件628。nmos器件m3的漏极和栅极都耦合到节点nts,并且因此耦合到彼此,并且被配置为接收偏置电压vgb。nmos器件m3的源极耦合到节点nrs。电阻器件628耦合在节点nrs与参考电源节点之间。电阻器件628具有电阻rref/n,并且nmos器件m3具有沟道尺寸n*x,n是大于或等于1的正数。

93.由此,nmos器件m3和电阻器件628被布置为分压器,其被配置为在操作中通过在节点nts上对偏置电压vgb进行分压来在节点nrs上生成电压vs。电压vs具有基于nmos器件m3的电压vgs(未标记)与电阻器件628上的电压之比的电压水平。该比值基于沟道尺寸n*x和电阻rref/n,并且因此对于数字n的变化值基本恒定。随着数字n的增加,电压感测级604的响应时间减少并且待机电流增加。

94.在一些实施例中,数字n具有范围从一到八的值。在一些实施例中,数字n具有范围从二到六的值,例如四。数字n的其他值/范围在本公开的范围内。

95.增益级606被配置为基于在耦合至电压感测级604的节点nrs的节点nss上接收的电压vs来放大参考电压vgb_ref与偏置电压vgb之间的偏移。增益级606包括电流源630、nmos器件m2和电阻器件632。电流源630的阳极被配置为接收电源电压vdd,并且电流源630的阴极耦合到节点nds。nmos器件m2的漏极耦合到节点nds,nmos器件m2的源极耦合到节点nss,并且nmos器件m2的栅极耦合到参考级602的nmos器件m1的栅极。电阻器件632耦合在节点nss和参考电源节点之间。

96.电流源630被配置为生成具有电流水平m*iref的电流634,电阻器件632具有电阻rref/m,并且nmos器件m2具有沟道尺寸m*x,m为大于或等于1的正数。

97.增益级606由此被布置为公共栅极放大器,其被配置为在操作中响应于在nmos器件m2的栅极处接收的参考电压vgb_ref和在节点nss上接收的电压vs而在节点nds上生成偏置电压vb。增益级606的增益由此被配置为具有对于数字m的变化的值基本恒定的值。随着数字m的增加,增益级606的响应时间减少并且待机电流增加。

98.在一些实施例中,数字m具有范围从一到八的值。在一些实施例中,数字m具有范围从二到六的值,例如四。数字m的其他值/范围在本公开的范围内。

99.缓冲器608被配置为基于在节点nds上接收的偏置电压vb来在节点nts上生成偏置电压vgb。在该实施例中,缓冲器608包括pmos器件mp。pmos器件mp具有被配置为接收电源电压vdd的漏极、耦合至节点nds的栅极以及耦合至节点nts的源极。

100.缓冲器608由此被布置为公共源极放大器,其被配置为在操作中,响应于由电压感测级604生成的电压vs,在节点nts上生成具有由参考级602生成的参考电压vgb_ref和由增益级606生成的偏置电压vb的相对电压水平控制的电压水平的偏置电压vgb。

101.存储器电路600由此包括参考级602、电压感测级604、增益级606和缓冲器608,其具有被配置为生成偏置电压vgb的反馈布置。用于生成偏置电压vgb的总电流是由电流源620生成的电流624、由电流源630生成的电流634和由pmos器件mp控制的电流ivgb之和。

102.在待机和活动状态下,电流624具有预定电流水平iref,电流634具有预定电流水平m*iref。在待机状态下,电流ivgb的电流水平由偏置电压vgb的电压水平以及pmos器件mp和电阻器件628的配置控制。在活动状态下,选择活动使得电流ivgb具有由通过电压钳位器

件610电容耦合到电流路径612触发的一个或多个瞬态电流水平。基于存储器电路600的反馈布置,pmos器件mp被配置为在待机状态下提供具有低电流水平的电流ivgb并且在活动状态下提供具有一个或多个高电流水平的电流ivgb。

103.与其他方法相比,存储器电路600由此能够使用减少的待机功率生成偏置电压vgb,并具有能够动态传递的增加的电荷量,从而降低功耗并提高存储器电路的速度。

104.图7是根据一些实施例的执行读取操作的方法700的流程图。方法700可与存储器电路一起使用,例如,以上关于图1a和图1b讨论的存储器电路100、以上关于图2讨论的存储器电路100a、以上关于图4讨论的存储器电路100b、以上关于图5讨论的存储器电路100c或以上关于图6讨论的存储器电路600。

105.在图7中描述了方法700的操作的顺序仅用于说明;方法700的操作能够以与图7所示的顺序不同的顺序执行。在一些实施例中,除了图7中描绘的那些之外的操作在图7所示的操作之前、之间、之中和/或之后执行。在一些实施例中,方法700的操作是操作存储器宏的方法的操作的子集。

106.在操作702处,基于参考电压和反馈电压生成第一偏置电压。在一些实施例中,基于参考电压和反馈电压生成第一偏置电压包括:如上面关于图1a、图2、图4和图5所讨论的基于参考电压vref和驱动电压vrbl生成偏置电压vg。

107.在一些实施例中,基于反馈电压生成第一偏置电压包括使用第一电压钳位器件基于第一偏置电压生成反馈电压。在一些实施例中,使用第一电压钳位器件基于第一偏置电压生成反馈电压包括:如上面关于图2、图4和图5所讨论的使用电压钳位器件120r基于偏置电压vg生成驱动电压vrbl。

108.在一些实施例中,使用第一电压钳位器件生成反馈电压包括将反馈电压施加到复制电路。在一些实施例中,将反馈电压施加到复制电路包括:如上面关于图2、图4和图5所讨论的将驱动电压vrbl施加到复制电路145a。

109.在一些实施例中,使用第一电压钳位器件基于第一偏置电压生成反馈电压包括使用第一缓冲器来生成由第一电压钳位器件接收的第二偏置电压。在一些实施例中,使用第一缓冲器生成第二偏置电压包括:如以上关于图1a、图2、图4和图5所讨论的使用缓冲器141、141a或141b生成偏置电压vgb'。

110.在一些实施例中,基于参考电压和反馈电压生成第一偏置电压包括:如上面关于图6所讨论的基于参考电压vgb_ref和电压vs生成偏置电压vb。

111.在一些实施例中,基于参考电压和反馈电压生成第一偏置电压包括基于参考电流生成参考电压。在一些实施例中,基于参考电流生成参考电压包括:如上面关于图6所讨论的基于参考电流iref生成参考电压vgb_ref。

112.在一些实施例中,基于参考电流生成参考电压包括利用复制电阻器件传导参考电流。在一些实施例中,利用复制电阻器件传导参考电流包括:如上面关于图6所讨论的利用电阻器件622传导参考电流iref。

113.在操作704处,使用第一缓冲器从第一偏置电压生成第二偏置电压。在一些实施例中,生成第二偏置电压包括如上面关于图1a

‑

图6所讨论的生成偏置电压vgb。

114.在一些实施例中,使用第一缓冲器生成第二偏置电压包括使用局部缓冲器。在一些实施例中,局部缓冲器是多个局部缓冲器中的一个局部缓冲器,第二偏置电压是多个第

二偏置电压中的一个第二偏置电压,并且使用第一缓冲器生成第二偏置电压包括使用多个局部缓冲器生成多个第二偏置电压。

115.在一些实施例中,使用第一缓冲器生成第二偏置电压包括:如上面关于图1a、图2、图4和图5所讨论的使用一个或多个缓冲器144、144a、144b和/或144c生成偏置电压vgb的一个或多个实例。

116.在一些实施例中,使用第一缓冲器从第一偏置电压生成第二偏置电压包括使用包括在反馈配置中的缓冲器。在一些实施例中,使用第一缓冲器从第一偏置电压生成第二偏置电压包括:如上面关于图6所讨论的使用缓冲器608从由增益级606接收的并用于生成电压vb的电压vs生成偏置电压vgb。

117.在操作706处,利用局部电压钳位器件基于第二偏置电压生成第一驱动电压。在一些实施例中,利用局部电压钳位器件基于第二偏置电压生成第一驱动电压包括:如上面关于图1a

‑

图2、图4和图5所讨论的利用电压钳位器件120基于偏置电压vgb生成驱动电压vd。

118.在一些实施例中,利用局部电压钳位器件基于第二偏置电压生成第一驱动电压包括:如上面关于图6所讨论的利用电压钳位器件610基于偏置电压vgb生成驱动电压vmtj。

119.在操作708处,将第一驱动电压施加到包括基于电阻的存储器件的电流路径。在一些实施例中,将第一驱动电压施加到包括基于电阻的存储器件的电流路径包括:包括rram器件或mtj器件的电流路径。

120.在一些实施例中,将第一驱动电压施加到包括基于电阻的存储器件的电流路径包括:如上面关于图1a

‑

图2、图4和图5所讨论的将驱动电压vd施加到包括基于电阻的存储器件150的电流路径111。

121.在一些实施例中,将第一驱动电压施加到包括基于电阻的存储器件的电流路径包括:如上面关于图6所讨论的将驱动电压vmtj施加到包括基于电阻的存储器件614的电流路径612。

122.通过执行方法700的部分或全部操作,基于存储器电路的反馈配置将偏置电压提供给电压钳位器件,从而实现上面关于存储器电路100、100a、100b、100c和600讨论的益处。

123.在一些实施例中,存储器电路包括偏置电压发生器,其包括第一电流路径、第一电压钳位器件和第一缓冲器。偏置电压发生器被配置为接收参考电压并基于参考电压和第一驱动电压之间的电压差生成第一偏置电压,所述第一电压钳位器件被配置为基于所述第一偏置电压通过将所述第一驱动电压施加至所述第一电流路径生成所述第一驱动电压,并且第一缓冲器被配置为接收第一偏置电压并基于第一偏置电压生成第二偏置电压。存储器电路包括第二电流路径,包括基于电阻的存储器件和第二电压钳位器件,其被配置为基于第二偏置电压生成第二驱动电压并将第二驱动电压施加至第二电流路径。在一些实施例中,偏置电压发生器包括运算放大器,其具有被配置为接收基准电压的同相输入端子、被配置为接收第一驱动电压的反相端子以及被配置为输出第一偏置电压的输出端子。在一些实施例中,存储器电路还包括:第二缓冲器,被配置为接收第一偏置电压并基于第一偏置电压生成第三偏置电压;第三电流路径,具有第二基于电阻的存储器件;以及第三电压钳位器件,被配置为基于第三偏置电压生成第三驱动电压,并将第三驱动电压施加至第三电流路径。在一些实施例中,偏置电压发生器包括第二缓冲器,其被配置为基于第一偏置电压生成第三偏置电压,其中,第一电压钳位器件被配置为基于第三偏置电压生成第一驱动电压。在一

些实施例中,第一缓冲器包括第一电流源和以源极跟随器配置耦合到第一电流源的第一nmos器件,其中,第一nmos器件的栅极被配置为接收第一偏置电压,使得从第一nmos器件的源极生成第二偏置电压;第一电流源被配置为生成第一电流,第一电流源被配置为在待机状态和活动状态下操作,其中,第一电流源在活动状态下具有第一电流水平并在待机状态下具有第二电流水平,第一电流水平的大小高于第二电流水平。在一些实施例中,第二缓冲器包括第二电流源和以源极跟随器配置耦合到第二电流源的第二nmos器件,其中,第二nmos器件的栅极被配置为接收第一偏置电压,使得从nmos器件的源极生成第三偏置电压,并且第二电流源被配置为生成约为第二电流水平的第二电流。在一些实施例中,基于电阻的存储器件包括rram器件。在一些实施例中,第一缓冲器包括:第一nmos器件,具有被配置为接收第一偏置电压的栅极;第二nmos器件,被配置为在待机状态下去激活并在活动状态下激活,第二nmos器件具有被配置为接收第一偏置电压的栅极;第一电流源,以源极跟随器配置耦合到第一nmos器件,第一电流源被配置为生成具有第一电流水平的第一电流;第二电流源,被配置为在待机状态下去激活并在活动状态下激活,第二电流源被配置为以高于第一电流水平的第二电流水平生成第二电流,其中,第二电压钳位器件耦合到第一nmos器件的源极并耦合到第二nmos器件的源极以接收第二偏置电压。在一些实施例中,第一缓冲器包括:第一节点,被配置为接收电源电压;以及开关,串联耦合在第二nmos器件的漏极和第一节点之间,其中,开关被配置为在待机状态下断开并在活动状态下闭合。在一些实施例中,第一缓冲器包括耦合在第二nmos器件和第一电流源之间的开关,其中,开关被配置为在待机状态下断开并在活动状态下闭合。在一些实施例中,第一缓冲器包括:第一pmos器件,具有被配置为接收第一偏置电压的栅极;第二pmos器件,被配置为在待机状态下去激活并在活动状态下激活,第二pmos器件具有被配置为接收第一偏置电压的栅极;第一电流源,以源极跟随器配置耦合到第一pmos器件,第一电流源被配置为生成具有第一电流水平的第一电流;第二电流源,被配置为在待机状态下去激活并在活动状态下激活,第二电流源被配置为以高于第一电流水平的第二电流水平生成第二电流,其中,第二电压钳位器件耦合到第一pmos器件的源极并耦合到第二pmos器件的源极以接收第二偏置电压。在一些实施例中,第一缓冲器包括:第一节点,被配置为接收电源电压;以及开关,串联耦合在第二电流源和第一节点之间,其中,开关被配置为在待机状态下断开并在活动状态下闭合。在一些实施例中,第一缓冲器包括耦合在第二pmos器件和参考电源节点之间的开关,其中,开关被配置为在待机状态下断开并在活动状态下闭合。

124.在一些实施例中,一种存储器电路包括:第一电流路径,具有基于电阻的存储器件;第一电压钳位器件,被配置为在第一电流路径处生成第一驱动电压;以及偏置电压发生器,包括第一缓冲器和复制电路,该复制电路被配置为模拟具有基于电阻的存储器件的第一电流路径的至少一部分的电阻。偏置电压发生器被配置为接收参考电压并生成第一偏置电压,第一缓冲器被配置为基于第一偏置电压生成第二偏置电压,第一复制电路被配置为基于第二偏置电压生成第二驱动电压,并且偏置电压发生器被配置为基于参考电压和第二驱动电压之间的电压差来调节第一偏置电压。在一些实施例中,存储器电路包括第二缓冲器,其被配置为接收第一偏置电压并基于第一偏置电压生成第三偏置电压,其中,第一电压钳位器件被配置为基于第三偏置电压生成第一驱动电压。在一些实施例中,存储器电路包括感测放大器,其中,第一电压钳位器件包括nmos器件,该nmos器件的漏极耦合至感测放大

器的输入端子,并且源极耦合至第一电流路径。在一些实施例中,偏置电压发生器包括运算放大器,该运算放大器具有被配置为接收参考电压的同相输入端子、被配置为接收第一驱动电压的反相端子以及被配置为输出第一偏置电压的输出端子,其中,运算放大器的输出端子耦合至第一缓冲器的nmos器件的栅极。在一些实施例中,存储器电路包括:第二电流路径,具有第二基于电阻的存储器件;第二电压钳位器件,被配置为基于第四偏置电压生成第三驱动电压,其中,第二电压钳位器件被配置为将第三驱动电压施加到第二电流路径;以及第三缓冲器,被配置为接收第一偏置电压并基于第一偏置电压生成第四偏置电压。

125.在一些实施例中,存储器电路包括:参考级,被配置为生成参考电压;电压感测级,被配置为检测参考电压与第一偏置电压之间的电压差;增益级,被配置为基于电压差生成第二偏置电压;缓冲器,被配置为基于第二偏置电压生成第一偏置电压;第一电压钳位器件,被配置为基于第一偏置电压生成第一驱动电压;以及第一电流路径,具有第一基于电阻的存储器件,其中,第一电压钳位器件被配置为将第一驱动电压施加到第一电流路径。在一些实施例中,存储器电路包括:第二电压钳位器件,被配置为基于第一偏置电压生成第二驱动电压;以及第二电流路径,具有第二基于电阻的存储器件,其中,第二电压钳位器件被配置为将第二驱动电压施加到第二电流路径。

126.以上论述了若干实施例的部件,使得本领域的技术人员可以更好地理解本发明的各个实施例。本领域技术人员应该理解,可以很容易地使用本发明作为基础来设计或更改其他的处理和结构以用于达到与本发明所介绍实施例相同的目的和/或实现相同优点。本领域技术人员也应该意识到,这些等效结构并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,可以进行多种变化、替换以及改变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。