1.本发明涉及一种闪速存储器等半导体存储装置,尤其涉及供给电压的下降的检测(断电检测),一种断电检测电路及半导体存储装置。

背景技术:

2.与非(nand)型闪速存储器使用熔丝单元,以便保存用于读出、编程、擦除等的电压的设定及用户的选项等设定信息。熔丝单元例如设定于存储单元阵列内的用户无法访问的存储区域。闪速存储器在电源接通时,作为上电操作,从熔丝单元读出设定信息,并将其加载至内部寄存器。上电操作结束后,控制器基于内部寄存器中所保持的设定信息,对各种操作进行控制。

3.在闪速存储器的忙模式中,当因噪声、峰值消耗电流等而产生从外部端子供给的供给电压vcc的下降时,元件无法准确地运行。为了避免此种情况,闪速存储器具有基于对供给电压vcc的下降进行检测的断电检测电路的重置功能。

4.如图1所示,断电检测电路10当检测到供给电压vcc下降至检测电平时,对中央处理器(central processing unit,cpu)或逻辑电路等内部电路20输出重置信号pddrst。内部电路20当接收到重置信号pddrst后,执行断电操作,停止电荷泵电路的操作,或者进行cpu或逻辑电路等的重置。

5.图2是表示现有的断电检测电路10的构成的图。断电检测电路10包括:带隙基准(band gap reference,bgr)电路30,基于供给电压vcc而生成基准电压vrefi;修整电路40,生成基于修整信号tr_vref来对基准电压vrefi进行调整而得的基准电压vref;电阻分割电路50,在节点n生成对供给电压vcc进行电阻分割而得的内部电压vcc_div;以及比较器60,将基准电压vrefi与内部电压vcc_div进行比较,在检测到vcc_div<vrefi时输出l电平的重置信号pddrst。

6.在供给电压vcc下降至断电检测电平时,检测到vrefi>vcc_div,比较器60输出转移为l电平的重置信号pddrst。利用比较器60的检测电路是为了抑制待机模式时的消耗电流而比较简单地构成,即对比较器60的反相输入(

‑

)直接输入bgr电路30的基准电压vrfi,对非反相输入( )输入内部电压vcc_div。另外,将由修整电路40生成的基准电压vref用作闪速存储器的外围电路的基准电压。

7.在图3中示出了bgr电路30的一例。bgr电路30在供给电压vcc与接地(ground,gnd)之间包括第一电流路径及第二电流路径,在第一电流路径包括串联连接的p沟道金属氧化物半导体(p channel metal oxide semiconductor,pmos)晶体管p1、电阻r1、二极管d1,在第二电流路径包括串联连接的pmos晶体管p2、电阻r2、电阻r、二极管d2(二极管d1的电流密度是二极管d2的n倍),bgr电路30还包括差动放大电路amp,所述差动放大电路amp在反相输入端子(

‑

)连接有将电阻r1与二极管d1连接的节点vn,在非反相输入端子( )连接有将电阻r2与电阻r连接的节点vp,将输出端子共用连接于晶体管p1、晶体管p2的栅极。差动放大电路amp以晶体管q1的正向电压与对晶体管q2的正向电压加上电阻r中产生的电压而得的电

压相等的方式对输出电压进行调整,并从输出节点输出基准电压vrefi。

8.bgr电路30生成不依赖于供给电压vcc的变动或操作温度的基准电压vrefi,但基准电压vrefi因bgr电路30的制造偏差等而变动。因此,修整电路40利用熔丝单元中所保存的修整信号tr_vref来对基准电压vrefi进行调整,而生成最终的基准电压vref,并将其提供给内部电路。

9.图4是断电检测电路10的理想的操作波形。例如,供给电压vcc为1.8v,bgr电路30的基准电压vrefi为1.2v,断电检测电平为1.3v。当在时刻t1供给电压vcc下降时,内部电压vcc_div与其相应地下降。当在时刻t2供给电压vcc下降至1.3v时,内部电压vcc_div与基准电压vrefi交叉,即,利用比较器60检测到内部电压vcc_div低于基准电压vrefi,比较器60输出从h电平转移为l电平的重置信号pddrst。

10.当断电检测电平比设想过高时,由于供给电压vcc的下降而频繁地检测到断电,会导致重复重置执行。相反,当断电检测电平比设想过低时,即使供给电压vcc降低,也不会检测到断电,而会引起错误操作等。因此,会需要通过元件的制造偏差或操作条件等因素来对断电检测电平进行调整。举例来言,在图2所示的构成中,由于对比较器60的输入直接输入基准电压vrefi,因此若要变更断电检测电平,必须变更bgr电路30的基准电压vrefi。例如,在将断电检测电平调整为低于1.3v的1.2v的情况下,需要将bgr电路30的基准电压vrefi从1.2v变更为1.1v,在供给电压vcc下降至1.2v时,利用比较器60检测到内部电压vcc_div低于基准电压vrefi。

11.然而,变更bgr电路30的基准电压vrefi会使比较器60产生温度依赖性。bgr电路30以使由二极管或晶体管产生的负温度特性及由电阻产生的正温度特性平衡的方式进行电路设计,以使基准电压vrefi不产生温度依赖。因此,在bgr电路中,例如当要改变电阻而任意地变更基准电压vrefi时,基准电压vrefi产生温度依赖。

12.图5是表示基准电压的温度依赖性的图,且表示以生成1.2v作为基准电压vrefi的方式进行电路设计的例子。可知若基准电压vrefi为1.2v,则从低温到高温几乎是平坦的电压,几乎没有温度依赖性。然而,当基准电压vrefi比1.2v低时,电阻的正温度依赖性变弱,其结果,基准电压vrefi具有负温度依赖性。因此,直接输入基准电压vrefi的比较器60的检测电平产生温度依赖,其结果,在操作温度低时及操作温度高时,断电检测电平不同,从而导致断电检测的操作不稳定。

技术实现要素:

13.本发明解决此种现有的问题,且其目的在于提供一种能够抑制温度依赖性同时对断电检测电平进行调整的断电检测电路及半导体存储装置。

14.本发明的断电检测电路包括:基准电压生成电路,基于供给电压而生成经温度补偿的基准电压;生成电路,对所述基准电压进行调整,而生成低于所述基准电压的断电检测用的基准电压;内部电压生成电路,生成低于所述供给电压的第一内部电压;以及第一检测电路,对所述第一内部电压比所述断电检测用的基准电压低的情况进行检测。

15.本发明的半导体存储装置包括:前述记载的断电检测电路;以及执行部件,响应于所述断电检测电路的所述第一检测电路的检测结果,执行断电操作。

16.根据本发明,根据经温度补偿的基准电压生成断电检测用的基准电压,因此可抑

制温度依赖性同时对断电检测电平进行调整。

附图说明

17.图1是说明闪速存储器的断电检测操作的图,

18.图2是表示现有的断电检测电路的构成的图,

19.图3是表示bgr电路的一般的构成的图,

20.图4是表示现有的断电检测电路的理想的操作波形图,

21.图5是表示bgr电路的基准电压的温度依赖性的图,

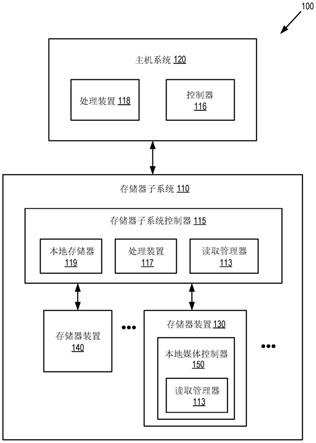

22.图6是表示本发明实施例的闪速存储器的内部构成的框图,

23.图7是表示本发明第一实施例的断电检测电路的构成的图,

24.图8是表示本发明第一实施例的断电检测电路的操作波形图,

25.图9是表示本实施例的修整电路的一例的图,

26.图10的(a)、图10的(b)是表示本发明第一实施例的断电检测电路的温度依赖性的图,

27.图11是表示本发明第二实施例的断电检测电路的构成的图,

28.图12的(a)是表示bgr电路的基准电压降低时的断电检测电路的操作波形图,图12的(b)是表示本发明第二实施例的断电检测电路的操作波形图。

具体实施方式

29.接着,参照附图对本发明的实施方式详细地进行说明。本发明的半导体存储装置可应用于nand型或或非(nor)型的闪速存储器、电阻变化型存储器、磁变化型存储器等非易失性存储器、或者嵌入此种非易失性存储器的微处理器、微控制器、逻辑、专用集成电路(application specific integrated circuit,asic)、对图像或声音进行处理的处理器、对无线信号等信号进行处理的处理器等。在以下的说明中,例示nand型的闪速存储器。

30.将本发明的实施例的闪速存储器的概略构成示于图6。本实施例的闪速存储器100包括:存储单元阵列110,呈矩阵状地排列有多个存储单元;输入输出缓冲器120,连接于外部输入输出端子i/o;地址寄存器130,从输入输出缓冲器120接收地址数据;控制器140,从输入输出缓冲器120接收命令数据等来对各部进行控制;字线选择电路150,基于来自地址寄存器130的行地址信息ax的解码结果来进行块的选择及字线的选择等;页缓冲器/读出电路160,保持从由字线选择电路150所选择的页读出的数据,或者保持应编程至所选择的页的数据;列选择电路170,基于来自地址寄存器130的列地址信息ay的解码结果来选择列等;断电检测电路180,对供给至电源端子的供给电压vcc进行监测,在检测到供给电压vcc下降至检测电平时输出重置信号pddrst;以及操作电压产生电路190,生成数据的读出、编程及擦除等各种操作所需要的各种电压(编程电压vpgm、通过电压vpass、读出电压vread、擦除电压vers等)。

31.存储单元阵列110具有沿列方向配置的m个块blk(0)、blk(1)、

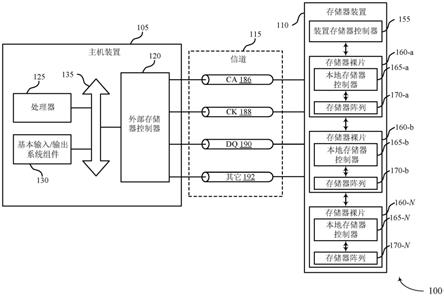

…

、blk(m

‑

1)。在一个块形成有多个nand串,一个nand串是将多个存储单元(例如64个)、位线侧选择晶体管、及源极线侧选择晶体管串联连接而构成。位线侧选择晶体管的漏极连接于对应的一个位线,源极线侧选择晶体管的源极连接于共用的源极线。nand串既可二维地形成于基板表面上,

也可三维地形成于基板表面上。另外,存储单元既可为存储一个位的单层单元(single level cell,slc)型,也可为存储多个位的多层单元(multi

‑

level cell,mlc)型。

32.在读出操作时,对位线施加某正电压,对选择字线施加某电压(例如0v),对非选择字线施加通过电压vpass(例如4.5v),使位线侧选择晶体管及源极线侧选择晶体管导通,对共用源极线施加0v。在编程操作时,对选择字线施加高电压的编程电压vpgm(15v~20v),对非选择字线施加中间电位(例如10v),使位线侧选择晶体管接通,使源极线侧选择晶体管断开,将与“0”或“1”的数据相应的电位供给至位线。在擦除操作时,对块内的选择字线施加0v,对p阱(well)施加高电压(例如20v)。

33.断电检测电路180当检测到供给电压vcc下降至断电检测电平时,对控制器140输出从h电平转移为l电平的重置信号pddrst。控制器140响应于重置信号pddrst,根据从只读存储器(read only memory,rom)/随机存取存储器(random access memory,ram)读出的码执行断电操作。在断电操作中,例如进行包括控制器140的内部电路的重置、或操作电压产生电路190中所包括的电荷泵电路的停止等。

34.在图7中示出了本发明第一实施例的断电检测电路180的内部构成。图中,对与图2所示的断电检测电路10相同的构成标注相同的参照编号。本实施例的断电检测电路180不仅包括图2所示的构成,还包括修整电路182,所述修整电路182基于bgr电路30的基准电压vrefi而生成断电检测用的基准电压vrefpdd(以下称为pd检测用基准电压)。修整电路182基于断电检测用的修整信号tr_vrefpdd(以下称为pd检测用修整信号)来对基准电压vrefi进行调整,而生成温度依赖性得到抑制的pd检测用基准电压vrefpdd(vrefpdd<vrefi)。另外,电阻分割电路50a包括连接于供给电压vcc与gnd之间的电阻梯,在节点n生成对供给电压vcc进行电阻分割而得的内部电压vcc_div。在本实施例中,使用低于基准电压vrefi的pd检测用基准电压vrefpdd来进行断电检测。因此,在供给电压vcc下降至断电检测电平时,调整内部电压vcc_div以使比较器60检测到vcc_div<vrefpdd。

35.修整电路182无特别限定,但例如包括生成与pd检测用修整信号tr_vrefpdd相应的模拟电压的数模转换器(digital analog converter,dac)(可变电阻)。在图8中示出了修整电路182的一例。在连接于基准电压vrefi与gnd之间的电阻梯的多个抽头(tap)间连接有开关sw1、开关sw2~开关swn。pd检测用修整信号tr_vrefpdd包括修整码(例如3位),使利用修整码选择的一个或多个开关sw1~swn接通,从输出节点n1输出pd检测用基准电压vrefpdd。

36.特别说明的是,供给至修整电路182的基准电压vrefi是由bgr电路30生成的经温度补偿的电压,为温度依赖性得到抑制的电压。本发明接着通过根据基准电压vrefi生成pd检测用基准电压vrefpdd,可使pd检测用基准电压vrefpdd的温度依赖性得到抑制,进而使比较器60可进行没有温度依赖性的断电检测。pd检测用修整信号tr_vrefpdd与用于对基准电压vref进行调整而输入至修整电路40的修整信号tr_vref同样地,保存于存储单元阵列110的熔丝存储器,这些修整信号在电源接通时或上电检测时从熔丝存储器读出至控制器140的寄存器。

37.在图9中示出了本实施例的断电检测电路的操作波形。当在时刻t1供给电压vcc因噪声或者峰值电流等某些因素而下降时,对供给电压vcc进行电阻分割而得的内部电压vcc_div也同样地下降。当在时刻t2供给电压vcc达到断电检测电平时,比较器60检测到内

部电压vcc_div比pd检测用基准电压vrefpdd低(vcc_div<vrefpdd),输出转移为l电平的重置信号pddrst。pd检测用基准电压vrefpdd的由虚线表示的范围h1表示能够利用pd检测用修整信号tr_vrefpdd来对pd检测用基准电压进行调整的范围,断电检测电平的虚线的范围h2表示与pd检测用基准电压vrefpdd的调整范围对应的断电检测电平的能够调整的范围。例如,在供给电压vcc为1.8v、基准电压vrefi为1.2v时,可通过将pd检测用基准电压vrefpdd调整为1.1v而将断电检测电平从1.3v变更为1.2v。

38.图10的(a)表示基准电压vrefi的温度依赖性,图10的(b)表示pd检测用基准电压vrefpdd的温度依赖性。由bgr电路30生成的基准电压vrefi(例如1.2v)是经温度补偿的电压。对此种基准电压vrefi进行调整而得的pd检测用基准电压vrefpdd仍是温度依赖性得到抑制的电压。如图5所示,变更为1.1v或1.0v的基准电压vrefi具有温度依赖性,与此相对,如图10的(b)所示,调整为1.1v或1.0v的pd检测用基准电压vrefpdd的温度依赖性得到抑制。由此,比较器60可不依赖于操作温度而进行稳定的断电检测。另外,修整电路182是独立于修整电路40以断电检测用途来设置,因此可不受到修整电路40的限制而各别地对断电检测电平进行调整。

39.接着,对本发明的第二实施例进行说明。当bgr电路30因供给电压vcc的下降而在低电压下操作时,有可能输出低于所期待的基准电压vrefi的电压。例如,在以生成1.2v的基准电压vrefi的方式进行设计时,当供给电压vcc下降至1.3v左右的断电检测电平时,基准电压vrefi有时低于1.2v。于是,尽管供给电压vcc下降至断电检测电平,比较器60也无法检测到vcc_div<vrefpdd,从而产生无法适当地执行重置操作的情况。

40.将所述情况示于图12的(a)。在时刻t1,供给电压vcc下降,内部电压vcc_div与其相应地下降。在时刻t2,供给电压vcc下降至断电检测电平。在时刻t2之前的时刻t1a,bgr电路30的操作不稳定,基准电压vrefi开始降低,同时pd检测用基准电压vrefpdd也降低。其结果,在时刻t2,pd检测用基准电压vrefpdd与内部电压vcc_div不交叉,而无法检测到内部电压vcc_div的下降。

41.第二实施例解决此种情况。图11表示本发明第二实施例的断电检测电路180a的构成,对与图7相同的构成标注相同的参照编号。本实施例的断电检测电路180a还包括:比较器60a,对供给电压vcc下降至一定电平的情况进行检测;切换电路200,基于比较器60a的检测结果,将供给至bgr电路30的电压从供给电压vcc切换为经升压的电压vxx;以及升压电路210,生成对供给电压vcc进行升压而得的升压电压vxx。升压电路210例如包括电荷泵电路,升压电路210可用于闪速存储器100的读出、编程、擦除等的操作,也可专用地设置于断电检测电路180a。

42.本实施例的电阻分割电路50b在节点n1生成第一内部电压vcc_div1,进而在节点n2生成第二内部电压vcc_div2。第一内部电压vcc_div1与第一实施例的内部电压vcc_div相同。第二内部电压vcc_div2是用于在供给电压vcc下降至断电检测电平之前对供给电压vcc下降至一定电平的情况进行检测的电压,且具有vcc_div2<vcc_div1的关系。比较器60a中,将pd检测用基准电压vrefpdd与第二内部电压vcc_div2进行比较,当检测到vcc_div2<vrefpdd时,输出转移为l电平的检测信号det。

43.切换电路200包括:p型的晶体管pmos1,连接于供给电压vcc与bgr电路30的电压供给节点vcc_bgr之间;p型的晶体管pmos2,连接于升压电路210的输出与电压供给节点vcc_

bgr之间;以及反相器in,输入从比较器60输出的检测信号det。对晶体管pmos1的栅极施加反相器in的输出,对晶体管pmos2的栅极施加检测信号det。在vcc_div2>vrefpdd的期间,比较器60a输出h电平的检测信号det,在所述期间,晶体管pmos1导通,晶体管pmos2不导通,对bgr电路30供给供给电压vcc。当利用比较器60a检测到vcc_div2<vrefpdd时,检测信号det转移为l电平,晶体管pmos1不导通,晶体管pmos2导通,对bgr电路30供给由升压电路210生成的升压电压vxx。

44.在图12的(b)中示出了本实施例的断电检测电路的操作波形。当在时刻t1供给电压vcc下降时,电压供给节点vcc_bgr的电压、第一内部电压vcc_div1及第二内部电压vcc_div2也与其相应地下降。当在时刻t2供给电压vcc下降至切换检测电平时,比较器60a检测到vcc_div2<vrefpdd,输出从h电平转移为l电平的检测信号det。切换电路200响应于检测信号det而使晶体管pmos1断开,使晶体管pmos2接通,从而对电压供给节点vcc_bgr供给升压电压vxx。然后,即使供给电压vcc进一步下降(由虚线表示),电压供给节点vcc_bgr的电压(由实线表示)因受到来自升压电压vxx的充电而不会立即下降,而是在一定期间保持某程度的电位。通过抑制电压供给节点vcc_bgr的电压的降低,在所述期间,bgr电路30的操作稳定,并生成所期待的基准电压vrefi,修整电路180也同样地生成所期待的pd检测用基准电压vrefpdd。

45.当在时刻t3供给电压vcc下降至断电检测电平时,比较器60检测到vcc_div1<vrefpdd,输出从h电平转移为l电平的重置信号pddrst。

46.如上所述,根据本实施例,利用升压电压vxx保证供给电压vcc降低时的bgr电路30的操作,因此可抑制基准电压vrefi的降低,确实地检测到供给电压vcc达到断电检测电平。

47.以上对本发明的优选实施方式进行了详述,但本发明并不限定于特定的实施方式,可在权利要求记载的发明的主旨范围内进行各种变形及变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。