1.本发明大体上涉及内存存储装置及其操作方法,且更具体地说,涉及一种电阻式内存存储装置及其操作方法。

背景技术:

2.电阻式内存(诸如电阻式随机存取内存(resistive random access memory,rram))具备低功耗、高速运作、高密度以及兼容于互补式金属氧化物半导体(complementary metal oxide semiconductor,cmos)制程技术的潜在优势,因此非常适合作为下一世代的非挥发性内存组件。

3.现行的电阻式内存通常包括相对配置的上电极与下电极以及位于上电极与下电极之间的介电层。在现行的电阻式内存可反复地在高低电阻状态间切换以存储数据前,首先需进行通道形成(forming)的程序。形成的程序包括对电阻式内存施加一偏压,例如正偏压,使电流从上电极流至下电极,使得介电层中产生氧空缺和氧离子而形成电流路径,使电阻式内存自高阻态(high resistance state,hrs)变为低阻态(low resistance state,lrs),以形成导电灯丝(filament)。通常,在所形成的灯丝中,邻近上电极处的部分的直径会小于邻近下电极处的部分的直径。之后,可对电阻式内存进行重置(reset)或设定(set),使电阻式内存分别切换为高阻态与低阻态,以完成数据的存储。此外,当对现行的电阻式内存进行重置时,包括对电阻式内存施加与设定时极性相反的偏压,使电流从下电极流至上电极。此时,邻近上电极处的氧空缺与部分氧离子结合而中断电流路径,使得灯丝在邻近上电极处断开。当对现行的电阻式内存进行设定时,包括可对电阻式内存施加与灯丝成形的程序时极性相同的偏压,使电流从上电极流至下电极。此时,邻近上电极处的氧离子脱离,重新形成氧空缺,使得灯丝在邻近上电极处重新形成。

4.然而在现有技术中,在电阻式内存完成形成程序或设定程序的期间,需要在施加形成电压或设定电压之后进行验证操作,此验证操作包括放电操作与施加验证电压,并且在验证失败时需执行充电操作并再一次地提供形成电压或设定电压。因此,完成形成程序或设定程序所需的时间相当冗长。此外,在现有技术中,在电阻式内存经过形成程序或设定程序之后,可能因为不同的内存晶胞在制程上的变异使得晶胞电流分布不均匀,从而造成高的位错误率(bit error rate,ber)。

技术实现要素:

5.本发明提供一种电阻式内存存储装置及其操作方法,可有效降低位错误率。

6.本发明的电阻式内存存储装置包括内存阵列、第一选择晶体管以及内存控制器。内存阵列包括多个内存晶胞,各内存晶胞在写入脉冲宽度期间输出写入电流。第一选择晶体管耦接至内存晶胞。内存控制器耦接至第一选择晶体管及内存晶胞。内存控制器用以在写入脉冲宽度期间的第一电阻转态期间,将依据写入电流而逐渐变化至第一电压电平的第一控制电压施加至第一选择晶体管的控制端,且在第一电阻转态期间之后的第一灯丝稳定

期间将第一控制电压设定为第一电压电平,以使写入电流限制在第一预设电流值。

7.本发明的电阻式内存存储装置的操作方法包括:在写入脉冲宽度期间,自多个内存晶胞的其中一者读出写入电流,写入脉冲宽度期间包括第一电阻转态期间、第一灯丝稳定期间、第二电阻转态期间与第二灯丝稳定期间;在第一电阻转态期间,对第一选择晶体管的控制端提供依据写入电流而逐渐变化至第一电压电平的控制电压,以提供写入电流至这些内存晶胞的其中一者;在第一电阻转态期间之后的第一灯丝稳定期间,对第一选择晶体管的控制端提供固定至第一电压电平的控制电压,以让写入电流限制在第一预设电流值;在第一灯丝稳定期间之后的第二电阻转态期间,对第一选择晶体管的控制端提供依据写入电流而逐渐变化至大于第一电压电平的第二电压电平的控制电压;及在第二电阻转态期间之后第二灯丝稳定期间,对第一选择晶体管的控制端提供固定至第二电压电平的控制电压,以让写入电流限制在第二预设电流值。

8.基于上述,在本发明的实施例中,内存控制器将控制电压施加至第一选择晶体管的控制端,以使写入电流在写入脉冲宽度期间的电阻转态期间逐渐变化至预设电流值,并使写入电流在写入脉冲宽度期间的灯丝稳定期间限制在一或多个预设电流值,可有效降低位错误率。

9.为了使前述内容更容易理解,以下详细地描述伴有附图的若干实施例。

附图说明

10.包含附图以提供对本发明内容的进一步理解,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,且与描述一起用于解释本发明的原理。

11.图1示出本发明一实施例的电阻式内存存储装置的概要示意图;

12.图2a示出图1实施例的电阻式内存存储装置的内部概要示意图;

13.图2b示出图2a实施例的内存控制器的方块示意图;

14.图3示出本发明一实施例的写入电流在写入脉冲宽度期间的波形示意图;

15.图4示出本发明另一实施例的写入电流在写入脉冲宽度期间的波形示意图;

16.图5a、图5b、图5c及图5d示出本发明一实施例的内存晶胞在不同阶段的灯丝结构的概要示意图;

17.图6示出本发明一实施例的内存存储装置的电压及电流的波形示意图;

18.图7示出本发明一实施例的电阻式内存存储装置的操作方法的步骤流程图。

19.附图标号说明

20.100:电阻式内存存储装置

21.110:第一选择器电路

22.120:第二选择器电路

23.130:内存控制器

24.132:逻辑控制电路

25.134:时序控制电路

26.136:电压调节电路

27.138:电流感测电路

28.140:内存晶胞

29.300:内存晶胞转态

30.bl:位线

31.e:电场方向

32.e-:电子移动的方向

33.id:写入电流

34.iref、iref1、iref2、iref3:预设电流值

35.l1、l2、l3:电压电平

36.p0、p2、p4:电阻转态期间

37.p1、p3、p5:灯丝稳定期间

38.r:内存晶胞的电阻

39.s100、s110:方法步骤

40.sl:源极线

41.t1:第一选择晶体管

42.t2:第二选择晶体管

43.t3:内存晶胞的晶体管

44.ta、tb、tc、t0、t0a、t1、t2、t3、t4、t5、t6:时间点

45.t_wpw:写入脉冲宽度期间

46.v1:控制电压

47.v2:电压

48.v3:字线电压

49.vbl、vsl、vd:电压。

具体实施方式

50.应理解,在不脱离本发明的范围的情况下,可以利用其它实施例,且可以作出结构性改变。此外,应理解,本文中所使用的措词和术语是出于描述的目的且不应被视为是限制性的。本文中使用“包含”、“包括”或“具有”及其变体意在涵盖其后列出的项目和其等效物以及额外项目。除非另有限制,否则术语“连接(connected)”、“耦合(coupled)”以及“安装(mounted)”和其在本文中的变体是广义上使用的并且涵盖直接和间接连接、耦合以及安装。

51.图1示出本发明一实施例的电阻式内存存储装置的概要示意图。请参考图1,本实施例的电阻式内存存储装置100包括第一选择器电路110、第二选择器电路120、内存控制器130及内存阵列。内存阵列包括多个内存晶胞140。在图1中,仅示出一个内存晶胞140作例示说明。内存控制器130被配置为于写入脉冲宽度期间对第一选择器电路110提供控制电压v1。写入脉冲宽度期间包括电阻转态期间p0与随后的灯丝稳定期间p1(标示于图3)。亦即,灯丝稳定期间p1是在电阻转态期间p0之后的期间,且两者之间可不存在其他的时间区间,但本发明不限于两者之间是否存在其他的时间区间。写入脉冲宽度期间是指特定数据成功地写入至所选择的内存晶胞140所需的时间。

52.图2a示出图1实施例的电阻式内存存储装置的内部概要示意图。请参考图1及图2a,在本实施例中,内存晶胞140例如具有一个晶体管t3及一个可变电阻r(1t1r)的结构,或

者二个晶体管及二个可变电阻(2t2r)的结构,其实施方式可以由本领域的公知常识获得足够的教导、建议与实施说明。本发明对内存晶胞140的结构并不加以限制。

53.在本实施例中,内存控制器130可以是处理器芯片、场可程序化门阵列(field-programmable gate arrays,fpga)芯片、可程序化控制器、特殊应用集成电路(application specific integrated circuits,asic)、可程序化逻辑设备(programmable logic device,pld)或其他类似装置或这些装置的组合,或不同的电路区块但具有相同功能,其实施方式可以由本领域的公知常识获得足够的教导、建议与实施说明。

54.具体而言,内存晶胞140的一端经由第一选择器电路110耦接至位线bl,且另一端经由第二选择器电路120耦接至源极线sl。第一选择器电路110及第二选择器电路120可以位于同一个选择器电路区块或是由不同的电路区块来实施,本发明并不加以限制。在写入脉冲宽度期间,内存晶胞140的晶体管t3的控制端被提供电压v3(字线电压),第二选择晶体管t2的控制端被提供电压v2,内存控制器130对第一选择器电路110提供控制电压v1,使第一选择器电路110对内存阵列的多个内存晶胞140提供写入电流id,写入电流id通过内存晶胞140而提供至第二选择器电路120的第一端,并且内存控制器130从第二选择器电路120的第二端接收写入电流id,并且依据自第二选择器电路120读出的写入电流id更新控制电压v1,以输出更新后的控制电压v1至第一选择器电路110,使内存阵列中被写入至同一状态的多个内存晶胞140的写入电流id于电阻转态期间p0朝向预设电流值变化,并限制在相同的预设电流值。内存控制器130还被配置为在写入电流id达预设电流值后于灯丝稳定期间p1持续地对第一选择器电路110提供控制电压v1,使写入电流id于灯丝稳定期间p1持续地通过内存晶胞140。

55.第一选择器电路110包括一或多个第一选择晶体管t1,第二选择器电路120包括一或多个第二选择晶体管t2。在图2a中,仅示出各选择器电路包括一个选择晶体管作例示说明,惟其数量不用以限定本发明。具体而言,第一选择晶体管t1包括第一端、第二端及控制端。第一选择晶体管t1的第一端耦接至位线bl,第一选择晶体管t1的第二端耦接至内存晶胞140。第一选择晶体管t1的控制端耦接至内存控制器130。第二选择晶体管t2包括第一端、第二端及控制端。第二选择晶体管t2的第一端耦接至内存晶胞140。第二选择晶体管t2的第二端耦接至源极线sl及内存控制器130。

56.图2b示出图2a实施例的内存控制器的功能方块示意图。请参考图2b,本实施例的内存控制器130包括逻辑控制电路132、时序控制电路134、电压调节电路136及电流感测电路138。逻辑控制电路132作为内存控制器130的核心电路,被配置以接收多个设定值(例如预设电流值的设定、步阶数量的设定以及灯丝稳定期间的时间长度的设定)且被配置以比对自电流感测电路138输出的写入电流id,并根据写入电流id与这些设定值控制时序控制电路134及电压调节电路136的操作。电压调节电路136被配置以依据写入电流id、逻辑控制电路132的输出及时序控制电路134的输出来调节并输出控制电压v1。时序控制电路134被配置以控制各信号的回授时序及控制时序。电流感测电路138用以检测写入电流id,并且将写入电流id输出给逻辑控制电路132。其中,电压调节电路136与电流感测电路138可以是模拟式。

57.图3示出本发明一实施例的写入电流在写入脉冲宽度期间的波形示意图。在本实施例中,在写入脉冲宽度期间t_wpw,内存控制器130对第一选择器电路110提供初始控制电

压v1i(如图6所示),使第一选择器电路110对内存阵列的多个内存晶胞140提供写入电流id,各内存晶胞140的电阻值响应于写入电流id的变化而变化,内存控制器130自内存晶胞140读出写入电流id,并依据自内存晶胞140读出的写入电流id将更新后的控制电压v1施加至第一选择晶体管t1的控制端。在内存阵列中被写入至同一状态的多个内存晶胞140的写入电流id超过预设电流值iref后,内存控制器130将对应的控制电压v1设定为固定的控制电压v1f,并基于固定的控制电压v1f于灯丝稳定期间p1持续地对第一选择晶体管t1的控制端提供固定的控制电压v1f,使这些内存晶胞140的写入电流id在灯丝稳定期间p1限制在预设电流值iref,以完成写入操作。于本实施例中,在电阻转态期间p0,内存控制器130所提供的控制电压v1由初始控制电压v1i渐增至固定的控制电压v1f,使自各内存晶胞140读出的电流(即写入电流id)随着控制电压v1的上升而渐增。于一实施例中,如图6所示,在电阻转态期间p0,内存控制器130所提供的控制电压v1由初始控制电压v1i渐增至大于固定的控制电压v1f的最终控制电压v1t,使自各内存晶胞140读出的电流(即写入电流id)随着控制电压v1的上升而渐增至大于预设电流值iref,且在达最终控制电压v1t后降为固定的控制电压v1f,使自各内存晶胞140读出的电流(即写入电流id)随着控制电压v1的下降而降低至等于预设电流值iref。

58.一般而言,在内存晶胞经过形成程序或设定程序之后,有可能因为晶胞电流分布不均匀而造成高的位错误率。而此不均匀的晶胞电流分布,可能起因于内存晶胞在制程上的变异。此外,由于制程上的变异,在写入脉冲宽度期间t_wpw自不同的内存晶胞所读出的写入电流可能也不同,如图3中标号300所标示之处。在本发明的实施例中,通过将内存阵列中被写入至同一状态的多个写入电流id限制在预设电流值iref,可使晶胞电流分布更加均匀,并且通过于灯丝稳定期间p1持续地对第一选择晶体管t1的控制端提供上述固定的控制电压v1f,可使内存晶胞的导电灯丝结构更加强健,从而可以有效降低位错误率。此外,于本实施例中,于写入脉冲宽度期间并未执行写入验证操作,从而可缩短写入所需的时间。

59.图4示出本发明另一实施例的写入电流在写入脉冲宽度期间的波形示意图。在本实施例中,写入脉冲宽度期间t_wpw包括多个电阻转态期间与随后的灯丝稳定期间。内存控制器130在各电阻转态期间对第一选择晶体管t1的控制端提供渐增的控制电压v1,且前一个电阻转态期间的初始控制电压小于后一个电阻转态期间的初始控制电压。藉此,写入电流id从预设电流值iref1逐步增加至预设电流值iref2、预设电流值iref3。其中,预设电流值iref3大于预设电流值iref2,且预设电流值iref2大于预设电流值iref1。上述预设电流值的数量不用以限定本发明。

60.举例而言,写入脉冲宽度期间t_wpw包括电阻转态期间p0、p2、p4,以及各电阻转态期间随后的灯丝稳定期间p1、p3、p5。内存控制器130在电阻转态期间p0对第一选择晶体管t1的控制端提供渐增的控制电压v1,使写入电流id在电阻转态期间p0逐渐上升至预设电流值iref1,并且最终被限制在预设电流值iref1(第一预设电流值)。接着,内存控制器130在灯丝稳定期间p1对第一选择晶体管t1的控制端提供如图6所示的固定的控制电压v1f,使写入电流id在灯丝稳定期间p1维持为预设电流值iref1。其中,灯丝稳定期间p1的时间长度小于电阻转态期间p0的时间长度。接着,内存控制器130在电阻转态期间p2对第一选择晶体管t1的控制端提供渐增的控制电压v1’,使写入电流id在电阻转态期间p2逐渐上升至预设电流值iref2,并且最终被限制在预设电流值iref2(第二预设电流值)。接着,内存控制器130

在灯丝稳定期间p3对第一选择晶体管t1的控制端提供如图6所示的固定的控制电压v1’f,使写入电流id在灯丝稳定期间p3维持为预设电流值iref2。其中,预设电流值iref2大于预设电流值iref1。其中,灯丝稳定期间p3的时间长度小于电阻转态期间p2的时间长度。类似地,内存控制器130在电阻转态期间p4对第一选择晶体管t1的控制端提供渐增的控制电压v1”,使写入电流id在电阻转态期间p4逐渐上升至预设电流值iref3,并且最终被限制在预设电流值iref3(第三预设电流值)。接着,内存控制器130在灯丝稳定期间p5对第一选择晶体管t1的控制端提供如图6所示的固定的控制电压v1”f,使写入电流id在灯丝稳定期间p5维持为预设电流值iref3。其中,预设电流值iref3大于预设电流值iref2。其中,灯丝稳定期间p5的时间长度小于电阻转态期间p4的时间长度。

61.图5a至图5d示出本发明一实施例的内存晶胞在不同阶段的灯丝分布的概要示意图。请参考图4及图5,在电阻转态期间p0,内存晶胞140在进行转态,例如从hrs变为lrs,其灯丝分布较为松弛如图5a所示。在转态之后,内存控制器130对第一选择晶体管t1的控制端持续地施加固定的控制电压v1f,以让写入电流id在灯丝稳定期间p1被限制在预设电流值iref1,藉此使内存晶胞140的灯丝分布在灯丝稳定期间p1变为稳定(stabilization)状态,如图5b所示。接着,在电阻转态期间p2,利用对第一选择晶体管t1的控制端提供渐增的控制电压v1’,使处于松弛状态的灯丝被重建或复原,如图5c所示。在图5c中,e表示电场方向,e-表示电子移动的方向。接着,在灯丝稳定期间p3,通过对第一选择晶体管t1的控制端持续地施加固定的控制电压v1’f,使内存晶胞140的灯丝分布再次变得稳定,如图5d所示。

62.类似地,在电阻转态期间p4,内存晶胞140的灯丝分布处于较松弛的状态;在灯丝稳定期间p5,内存晶胞140的灯丝分布再次变得较稳定。也就是说,在本实施例中,通过将步阶型态的控制电压v1施加至第一选择晶体管t1的控制端,可以让写入电流id分段地在电阻转态期间p0、p2、p4逐渐变化至预设电流值iref1、iref2、iref3,且让写入电流id在灯丝稳定期间p1、p3、p5分别被限制在预设电流值iref1、iref2、iref3。通过这种操作方式,内存晶胞140会重复经历灯丝分布的松弛状态及稳定状态,可以让其灯丝更为强健且使晶胞电流分布更加均匀,以降低位错误率。

63.在图4的实施例中,虽然是以三步阶为例,但本发明并不限于此,预设电流值的数量及大小可依实际设计需求进行调整。例如,在图3的实施例中,内存控制器130仅将写入电流id限制在预设电流值iref,即一步阶。

64.图6示出本发明一实施例的内存存储装置的电压及电流的波形示意图。请参考图2a及图6,在图6中,电压v1、v1’、v1”是施加到第一选择晶体管t1的控制端的控制电压,电压v2是施加到第二选择晶体管t2的控制端的另一控制电压,电压v3是施加到内存晶胞140的晶体管t3的控制端的字线电压。电压vbl、vsl分别是施加到位线bl及源极线sl的电压。电压v2、v3、vbl、vsl可以由内存控制器130提供或者由内存存储装置100的其他内存控制器或电源供应装置提供。电压vd是第一选择晶体管t1的第二端的电压。

65.在时间点ta,内存存储装置100处于初始状态,电压v1、v2、v3、vbl、vsl都是0伏特。在时间点tb,电压v2、v3被拉高,以同时将第二选择晶体管t2及晶体管t3导通,并且使第二选择晶体管t2及晶体管t3处于全开状态(fully on)。例如,对第二选择晶体管t2的控制端施加高电位的电压v2,且对源极线sl施加低电压(例如接地电压)以使第二选择晶体管t2全开。此外,对内存晶胞140的晶体管t3的控制端施加高电位的字线电压v3以使内存晶胞140

的晶体管t3全开。在时间点tc,电压vbl被拉高,以将第一选择晶体管t1的第一端拉高至电压vbl。其中电压vbl的电平可设定较高,以避免箝制住写入电流id。

66.在时间点t0,依据预设电流值iref1,内存控制器130对第一选择晶体管t1的控制端施加渐增的控制电压v1,以使第一选择晶体管t1导通。自时间点t0a至时间点t1(电阻转态期间),内存晶胞140依据控制电压v1与电压vbl发生转态,并且于时间点t1,内存控制器130将控制电压v1降低为固定的第一电压电平l1,使写入电流id被限制在预设电流值iref1,并且持续至时间点t2。固定的第一电压电平l1所施加的时间长度(灯丝稳定期间)可依实际需求设计,使灯丝变得较稳定。于一实施例中,自时间点t0至时间点t1为数个皮秒(picosecond)。于一实施例中,灯丝稳定期间的时间长度(即固定的第一电压电平l1所施加的时间长度)大于电阻转态期间的时间长度(即自时间点t0a至时间点t1的时间长度)。

67.在时间点t2,依据预设电流值iref2,内存控制器130逐渐增加控制电压v1’至大于第二电压电平l2。在本实施例中,预设电流值iref2大于预设电流值iref1,且第二电压电平l2大于第一电压电平l1。时间点t2至时间点t3为电阻转态期间,灯丝于此期间处于松弛以进行重建或复原。

68.类似地,自时间点t3至时间点t4,控制电压v1’降低为固定的第二电压电平l2,使写入电流id被限制在预设电流值iref2,内存晶胞140再次处于稳定状态。类似地,自时间点t4至时间点t5(电阻转态期间),依据预设电流值iref3,内存控制器130逐渐增加控制电压v1”至大于第三电压电平l3,内存晶胞140的灯丝再次处于松弛状态。接着,自时间点t5至时间点t6,控制电压v1”降低至固定的第三电压电平l3,写入电流id被限制在预设电流值iref3,内存晶胞140再次处于稳定状态。预设电流值iref3大于预设电流值iref2,且第三电压电平l3大于第二电压电平l2。也就是说,在本实施例中,控制电压v1、v1’、v1”是随着时间逐步增加的步阶电压,从第一电压电平l1依序增加至第二电压电平l2、第三电压电平l3。

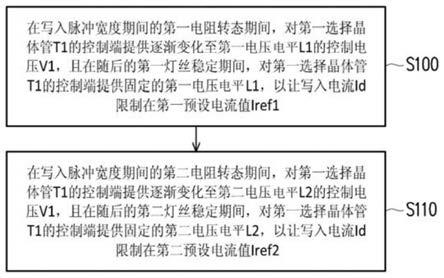

69.图7示出本发明一实施例的电阻式内存存储装置的操作方法的步骤流程图。请参考图2a、图4、图6及图7,本实施例的操作方法至少适用于图2a的电阻式内存存储装置100,惟本发明并不加以限制。以图2a的电阻式内存存储装置100为例,在步骤s100中,内存控制器130在写入脉冲宽度期间的第一电阻转态期间,对第一选择晶体管t1的控制端提供逐渐变化至第一电压电平l1的控制电压v1,且在随后的第一灯丝稳定期间,内存控制器130对第一选择晶体管t1的控制端提供固定的第一电压电平l1,以让写入电流id限制在第一预设电流值iref1。在步骤s110中,内存控制器130在写入脉冲宽度期间的第二电阻转态期间,对第一选择晶体管t1的控制端提供逐渐变化至第二电压电平l2的控制电压v1,且在随后的第二灯丝稳定期间,内存控制器130对第一选择晶体管t1的控制端提供固定的第二电压电平l2,以让写入电流id限制在第二预设电流值iref2。第二电压电平l2大于第一电压电平l1,且第二预设电流值iref2大于第一预设电流值iref1。

70.另外,本发明的实施例的电阻式内存存储装置的操作方法可以由图1至图6实施例的叙述中获得足够的教导、建议与实施说明,因此不再赘述。此外,本发明的实施例的电阻式内存存储装置的操作方法至少可应用在单层单元(single-level cell,slc)的内存存储装置或多层单元(multi-level cell,mlc)的内存存储装置,本发明并不加以限制。本发明的实施例的电阻式内存存储装置的操作方法也可应用在一次性可编程(one-time programmable,otp)的内存存储装置或多次性可编程(multi-time programmable,mtp)的

内存存储装置,本发明并不加以限制。

71.综上所述,在本发明的实施例中,内存控制器将控制电压施加至第一选择晶体管的控制端,以使写入电流在写入脉冲宽度期间的电阻转态期间逐渐变化至预设电流值,并使写入电流在写入脉冲宽度期间的灯丝稳定期间限制在一或多个预设电流值。通过在灯丝稳定期间将写入电流限制在一或多个预设的电流值,可使晶胞电流分布更加均匀,并且使内存晶胞的导电灯丝结构更加强健,从而可以有效降低位错误率。

72.本领域技术人员将明白,可在不脱离本发明的范围或精神的情况下对所公开实施例的结构进行各种修改和更改。鉴于前述内容,希望本发明涵盖属于所附权利要求和其等效物的范围内的本发明的修改和变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。