1.本发明涉及振荡电路技术领域,尤其涉及一种振荡电路。

背景技术:

2.石英晶体振荡器是利用石英晶体的压电效应制成的一种谐振器件,由于石英晶体具有非常高的品质因数,因此石英晶体振荡器能够产生频率准确而稳定的振荡波形,广泛用于对振荡频率要求较高的钟表、军工、通信等领域。

3.随着近年来通信领域中便携式设备的高速发展,对低功耗低成本的集成电路的设计需求日益突出。

技术实现要素:

4.本发明实施例提供一种振荡电路,以在脉冲电流输出电路以较短的脉冲时间给谐振电路提供电流时,谐振电路的其中一端与提供等效负电阻的反馈放大电路断开,避免谐振电路的两端与提供等效负电阻的反馈放大电路一直连接,导致脉冲电流输出电路给予谐振电路的驱动电流,被提供负阻功能的反馈放大电路直接导向地,造成极大的功率损失的情况发生,从而极大降低振荡电路的功耗。

5.本发明实施例提供了一种振荡电路,包括:谐振电路、反馈放大电路、电流通断控制电路和脉冲电流输出电路;其中,谐振电路的第一端经电流通断控制电路与反馈放大电路的第一端电连接;脉冲电流输出电路与谐振电路电连接;电流通断控制电路用于在谐振电路达到第一预设振荡状态之后,使谐振电路的第一端和反馈放大电路的第一端之间周期性呈通流状态和阻流状态;脉冲电流输出电路用于在谐振电路达到第一预设振荡状态之后,且通过电流通断控制电路使谐振电路的第一端和反馈放大电路的第一端之间呈阻流状态时,输出电流至谐振电路。

6.进一步地,脉冲电流输出电路用于在谐振电路达到第一预设振荡状态之后,且通过电流通断控制电路使谐振电路的第一端和反馈放大电路的第一端之间呈通流状态时,以及在谐振电路达到第一预设振荡状态之前,不输出电流至谐振电路;电流通断控制电路用于在谐振电路达到第一预设振荡状态之前,使谐振电路的第一端和反馈放大电路的第一端之间呈通流状态。

7.进一步地,脉冲电流输出电路包括第一直流电流源、第一晶体管和第一控制电路,其中,第一直流电流源与第一晶体管的第一极电连接;第一晶体管的第二极与谐振电路电连接;第一控制电路与第一晶体管的控制极电连接;第一控制电路用于在谐振电路达到第一预设振荡状态之后,且通过电流通断控制电路使谐振电路的第一端和反馈放大电路的第一端之间呈阻流状态时,控制第一晶体管导通。

8.进一步地,第一控制电路包括时钟信号产生电路和续流脉冲产生电路,其中,时钟信号产生电路的输入端与谐振电路电连接;时钟信号产生电路的输出端与续流脉冲产生电

路的输入端电连接;续流脉冲产生电路的输出端与第一晶体管的控制极电连接。

9.进一步地,续流脉冲产生电路包括信号延迟电路、或非门电路和第一反相器;其中,信号延迟电路的输入端,以及或非门电路的第一输入端均与时钟信号产生电路的输出端电连接;或非门电路的输出端经第一反相器与续流脉冲产生电路的输出端电连接;信号延迟电路包括串联的多个第二反相器。

10.进一步地,电流通断控制电路包括第一开关;其中,第一开关的第一端与谐振电路的第一端电连接;第一开关的第二端与反馈放大电路的第一端电连接;第一开关的控制端与第一控制电路电连接;第一控制电路用于在谐振电路达到第一预设振荡状态之后,控制第一开关周期性导通或关断。

11.进一步地,反馈放大电路包括:反馈电阻、第二电流源和放大电路;其中,反馈电阻的第一端与反馈放大电路的第一端电连接;反馈电阻的第二端与谐振电路的第二端电连接;放大电路的第一端与反馈电阻的第二端电连接;放大电路的第二端与反馈放大电路的第一端电连接;第二电流源与放大电路的第二端电连接。

12.进一步地,放大电路为跨导可调放大电路,其中,在谐振电路达到第二预设振荡状态之前放大电路的跨导大于在谐振电路达到第二预设振荡状态之后放大电路的跨导;和/或,第二电流源为可调电流源,其中,在谐振电路达到第二预设振荡状态之前第二电流源输出的电流大于在谐振电路达到第二预设振荡状态之后第二电流源输出的电流。

13.进一步地,放大电路包括第二晶体管、第三晶体管、第四晶体管和第二控制电路;其中,第二晶体管的控制极,以及第三晶体管的控制极,均与放大电路的第一端电连接;第二晶体管的第一极,以及第三晶体管的第一极,均与放大电路的第二端电连接;第二晶体管的第二极接地;第三晶体管的第二极与第四晶体管的第一极电连接;第四晶体管的第二极接地;第四晶体管的控制极与第二控制电路电连接;第三晶体管的尺寸大于第二晶体管的尺寸;第二控制电路用于在谐振电路达到第二预设振荡状态之前,控制第四晶体管导通;在谐振电路达到第二预设振荡状态之后,控制第四晶体管关断;第二电流源包括第一直流电流源单元、第二直流电流源单元和第五晶体管;其中,第一直流电流源单元与放大电路的第二端电连接;第二直流电流源单元与第五晶体管的第一极电连接;第五晶体管的第二极与放大电路的第二端电连接;第五晶体管的控制极与第二控制电路电连接;第二控制电路用于在谐振电路达到第二预设振荡状态之前,控制第五晶体管导通;在谐振电路达到第二预设振荡状态之后,控制第五晶体管关断。

14.进一步地,第二控制电路包括振荡状态识别电路和选择信号产生电路,其中,振荡状态识别电路的输出端与选择信号产生电路的输入端电连接;选择信号产生电路的第一输出端与第四晶体管的控制极电连接;选择信号产生电路的第二输出端与第五晶体管的控制极电连接。

15.进一步地,谐振电路包括晶体、第一电容和第二电容,其中,晶体的第一端经第一电容接地;晶体的第二端经第二电容接地;晶体的第一端与谐振电路的第一端电连接;晶体的第二端与谐振电路的第二端电连接;脉冲电流输出电路与谐振电路的第一端电连接;或者,脉冲电流输出电路与谐振电路的第二端电连接。

16.本发明实施例的技术方案中的振荡电路包括谐振电路、反馈放大电路、电流通断控制电路和脉冲电流输出电路;谐振电路的第一端经电流通断控制电路与反馈放大电路的第一端电连接;脉冲电流输出电路与谐振电路电连接;电流通断控制电路用于在谐振电路达到第一预设振荡状态之后,使谐振电路的第一端和反馈放大电路的第一端之间周期性呈通流状态和阻流状态;脉冲电流输出电路用于在谐振电路的振幅大于或等于预设振幅,且通过电流通断控制电路使谐振电路的第一端和反馈放大电路的第一端之间呈阻流状态时,输出电流至谐振电路。通过在脉冲电流输出电路以较短的脉冲时间给谐振电路提供电流时,谐振电路的其中一端与提供等效负电阻的反馈放大电路断开,避免谐振电路的两端与提供等效负电阻的反馈放大电路一直连接,导致脉冲电流输出电路给予谐振电路的驱动电流,被提供负阻功能的反馈放大电路直接导向地,造成极大的功率损失的情况发生,从而极大降低振荡电路的功耗。

附图说明

17.图1为本发明实施例提供的一种振荡电路的结构示意图;图2为本发明实施例提供的一种脉冲电流输出电路输出电流时的示意图;图3为本发明实施例提供的一种脉冲电流输出电路不输出电流时的示意图;图4为本发明实施例提供的一种波形图;图5为本发明实施例提供的又一种振荡电路的结构示意图;图6为本发明实施例提供的一种第一控制电路的结构示意图;图7为本发明实施例提供的一种第二控制电路的结构示意图;图8为本发明实施例提供的一种振幅较小时各晶体管的开关状态示意图;图9为本发明实施例提供的一种稳定振荡状态时t1时间段内各晶体管的开关状态示意图;图10为本发明实施例提供的一种稳定振荡状态时t2时间段内各晶体管的开关状态示意图;图11为本发明实施例提供的又一种波形图;图12为本发明实施例提供的又一种振荡电路的结构示意图。

具体实施方式

18.下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

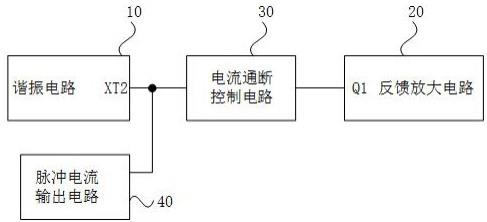

19.本发明实施例提供一种振荡电路。图1为本发明实施例提供的一种振荡电路的结构示意图。该振荡电路可设置于时钟电路中。该振荡电路包括:谐振电路10、反馈放大电路20、电流通断控制电路30和脉冲电流输出电路40。

20.其中,谐振电路10的第一端xt2经电流通断控制电路30与反馈放大电路20的第一端q1电连接;脉冲电流输出电路40与谐振电路10电连接;电流通断控制电路30用于在谐振电路10达到第一预设振荡状态之后,使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间周期性呈通流状态和阻流状态;脉冲电流输出电路40用于在谐振电路10达到第一

预设振荡状态之后,且通过电流通断控制电路30使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间呈阻流状态时,输出电流至谐振电路10。

21.其中,该振荡电路可为皮尔斯振荡电路等。谐振电路10可以包括晶体、电容等。谐振电路10可产生正弦波信号。反馈放大电路20可用于使谐振电路10正常起振,并稳定工作。脉冲电流输出电路40输出的脉冲电流的周期可等于谐振电路10的周期。脉冲电流输出电路40可用于在谐振电路10达到第一预设振荡状态之后,且通过电流通断控制电路30使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间呈通流状态时,不输出电流至谐振电路10。脉冲电流输出电路40可脉冲式的给予电流至谐振电路10,补充谐振电路10维持振荡所需要的能量。可根据需要设置脉冲电流输出电路40输出的脉冲电流的频率和宽度,本发明实施例对此不作限定。脉冲电流输出电路40输出的脉冲电流的频率可大于或等于谐振电路10的频率,示例性的,脉冲电流输出电路40输出的脉冲电流的频率可等于谐振电路10的频率的整数倍。电流通断控制电路30可包括第一开关。

22.振荡电路上电后,谐振电路10开始起振,振荡一段时间后,振幅逐渐增大直至达到设定振幅,即达到稳定振荡状态。第一预设振荡状态可以是谐振电路10的振幅达到设定振幅后的稳定振荡状态。图2为本发明实施例提供的一种脉冲电流输出电路输出电流时的示意图。图3为本发明实施例提供的一种脉冲电流输出电路不输出电流时的示意图。图4为本发明实施例提供的一种波形图。其中,sig1可为谐振电路10产生的正弦波信号的波形,i1为脉冲电流输出电路40输出的电流的波形。谐振电路10达到第一预设振荡状态之后,可在任一周期t的t1时间段内,使脉冲电流输出电路40输出电流至谐振电路10,使电流通断控制电路30呈阻流状态,如图2所示,使第一开关s1断开,以使谐振电路的第一端xt2与提供等效负电阻的反馈放大电路20断开,避免谐振电路的两端与提供等效负电阻的反馈放大电路一直连接,导致脉冲电流输出电路给予谐振电路的驱动电流,被提供负阻功能的反馈放大电路直接导向地,造成极大的功率损失的情况发生,从而极大降低振荡电路的功耗,以使振荡电路工作在低功耗模式下。谐振电路10达到第一预设振荡状态之后,可在任一周期t的t2时间段内,使脉冲电流输出电路40不输出电流至谐振电路10,使电流通断控制电路30呈通流状态,如图3所示,使第一开关s1导通。

23.本实施例的技术方案中的振荡电路包括谐振电路、反馈放大电路、电流通断控制电路和脉冲电流输出电路;谐振电路的第一端经电流通断控制电路与反馈放大电路的第一端电连接;脉冲电流输出电路与谐振电路电连接;电流通断控制电路用于在谐振电路达到第一预设振荡状态之后,使谐振电路的第一端和反馈放大电路的第一端之间周期性呈通流状态和阻流状态;脉冲电流输出电路用于在谐振电路的振幅大于或等于预设振幅,且通过电流通断控制电路使谐振电路的第一端和反馈放大电路的第一端之间呈阻流状态时,输出电流至谐振电路。通过在脉冲电流输出电路以较短的脉冲时间给谐振电路提供电流时,谐振电路的其中一端与提供等效负电阻的反馈放大电路断开,避免谐振电路的两端与提供等效负电阻的反馈放大电路一直连接,导致脉冲电流输出电路给予谐振电路的驱动电流,被提供负阻功能的反馈放大电路直接导向地,造成极大的功率损失的情况发生,从而极大降低振荡电路的功耗。

24.可选的,脉冲电流输出电路40用于在谐振电路10达到第一预设振荡状态之前,不输出电流至谐振电路10。

25.其中,可在谐振电路10的振幅未达到设定振幅前,相当于在谐振电路10未达到稳定振荡状态之前,脉冲电流输出电路40不输出电流至谐振电路10。

26.可选的,电流通断控制电路30用于在谐振电路10达到第一预设振荡状态之前,使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间呈通流状态。

27.其中,可在谐振电路10的振幅未达到设定振幅前,相当于在谐振电路10未达到稳定振荡状态之前,电流通断控制电路30使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间呈通流状态。

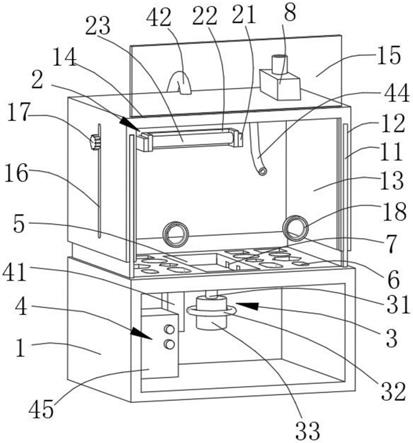

28.可选的,在上述实施例的基础上,图5为本发明实施例提供的又一种振荡电路的结构示意图,脉冲电流输出电路40包括:第一直流电流源41、第一晶体管p4和第一控制电路42。

29.其中,第一直流电流源41与第一晶体管p4的第一极电连接,第一晶体管p4的第二极与谐振电路10电连接,第一控制电路42与第一晶体管p4的控制极电连接。

30.其中,第一控制电路42用于在谐振电路10达到第一预设振荡状态之后,且通过电流通断控制电路30使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间呈阻流状态时,控制第一晶体管p4导通,以使第一直流电流源41输出电流至谐振电路10。

31.其中,第一控制电路42可用于在谐振电路10达到第一预设振荡状态之后,且通过电流通断控制电路30使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间呈通流状态时,控制第一晶体管p4关断,以使第一直流电流源41不输出电流至谐振电路10。第一控制电路42可输出高电平或低电平至第一晶体管p4的控制极,以控制第一晶体管p4的导通或关断。第一晶体管p4可包括pmos管,第一晶体管p4的第一极可为源极,第一晶体管p4的第二极可为漏极,第一晶体管p4的控制极可为栅极。

32.可选的,在上述实施例的基础上,继续参见图5,第一直流电流源41可包括第六晶体管p3。其中,第六晶体管p3的第一极与第二电压源60电连接;第六晶体管p3的第二极与第一晶体管p4的第一极电连接;第六晶体管p3的控制极可与第一电压源50电连接。

33.其中,第一直流电流源41可输出恒定的电流。第六晶体管p3可以包括pmos管,第六晶体管p3的第一极可为源极,第六晶体管p3的第二极可为漏极,第六晶体管p3的控制极可为栅极。通过调节第六晶体管p3的控制极的电压,可以调节流过第六晶体管p3的电流。可根据需要设置第一电压源50的输出电压的大小,以使第一直流电流源41输出的电流大小满足要求。第一电压源50可输出恒定的电压。第二电压源60可输出恒定的电压。

34.可选的,在上述实施例的基础上,图6为本发明实施例提供的一种第一控制电路的结构示意图,结合图5和图6所示,第一控制电路42包括时钟信号产生电路421和续流脉冲产生电路422。

35.其中,时钟信号产生电路421的输入端in1与谐振电路10电连接;时钟信号产生电路421的输出端out1与续流脉冲产生电路422的输入端电连接;续流脉冲产生电路422的输出端与第一晶体管p4的控制极电连接。

36.其中,时钟信号产生电路421的输入端in1可与谐振电路10的第二端xt1电连接。时钟信号产生电路421可将谐振电路10产生的正弦波信号转换成时钟信号。续流脉冲产生电路422可将时钟信号进行反相延迟、或非逻辑运算等处理,产生脉冲宽度较小的续流脉冲信号,以控制第一晶体管p4周期性导通或关断。续流脉冲信号的宽度与被延迟的时钟信号的

延迟时间相等。续流脉冲信号的宽度可决定脉冲电流输出电路40输出的脉冲信号的宽度。

37.可选的,在上述实施例的基础上,继续参见图6,时钟信号产生电路421包括低通滤波器4214、第一比较器4211、第一计数器4212和与非门电路4213。

38.其中,低通滤波器4214的输入端,以及第一比较器4211的第一输入端,均与时钟信号产生电路421的输入端in1电连接;低通滤波器4214的输出端与第一比较器4211的第二输入端电连接;第一比较器4211的输出端与与非门电路4213的第一输入端电连接;第一比较器4211的输出端经第一计数器4212与与非门电路4213的第二输入端电连接;与非门电路4213的输出端与时钟信号产生电路421的输出端out1电连接。

39.其中,可选的,第一比较器4211的第一输入端可为正相输入端,第一比较器4211的第二输入端可为反相输入端。可选的,第一比较器4211的第一输入端可为反相输入端,第一比较器4211的第二输入端可为正相输入端。低通滤波器4214可包括:第二电阻r3和第三电容c3,低通滤波器4214的输入端经第二电阻r3与低通滤波器4214的输出端电连接;低通滤波器4214的输出端经第三电容c3接地。

40.其中,时钟信号产生电路421的输入端in1输入的正弦波,经过低通滤波器4214后输出的直流信号作为第一比较器4211的负端输入,而正弦波直接作为第一比较器4211的正端输入,第一比较器4211的输出端将输出方波,第一计数器4212计数方波的脉冲边沿的个数,达到第一设定值后,第一计数器4212的输出端输出信号发生翻转,例如由低电平变为高电平,使能与非门电路4213,时钟信号产生电路421的输出端out1将输出时钟信号。第一设定值可决定第一预设振荡状态。第一设定值越大,达到第一预设振荡状态所需时间越长。可根据需要设置第一设定值的大小,本发明实施例对此不作限定。

41.可选的,在上述实施例的基础上,继续参见图6,续流脉冲产生电路422包括信号延迟电路4221、或非门电路4222和第一反相器4223。其中,信号延迟电路4221的输入端,以及或非门电路4222的第一输入端均与时钟信号产生电路421的输出端out1电连接;或非门电路4222的输出端经第一反相器4223与续流脉冲产生电路422的输出端电连接。

42.其中,信号延迟电路4221可为反相延迟电路。可选的,信号延迟电路4221包括串联的多个第二反相器42211。图6示例性的画出信号延迟电路4221包括串联的三个第二反相器42211的情况。时钟信号产生电路421产生的时钟信号经过三个第二反相器42211的延迟后,延迟的信号与原来的时钟信号一起经过或非门电路4222,之后将产生时间较短的脉冲信号,该脉冲信号的脉宽与被延迟的时钟信号的延迟时间相等。

43.可选的,在上述实施例的基础上,继续参见图5,电流通断控制电路30可以包括第一开关s1。

44.其中,第一开关s1的第一端与谐振电路10的第一端xt2电连接;第一开关s1的第二端与反馈放大电路20的第一端q1电连接;第一开关s1的控制端与第一控制电路42电连接;第一控制电路42用于在谐振电路10达到第一预设振荡状态之后,控制第一开关s1周期性导通或关断。

45.其中,第一控制电路42可用于在谐振电路10达到第一预设振荡状态之后,脉冲电流输出电路40输出电流至谐振电路10时,控制第一开关s1关断,以使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间呈阻流状态。第一控制电路42可用于在谐振电路10达到第一预设振荡状态之后,脉冲电流输出电路40不输出电流至谐振电路10时,控制第一

开关s1导通,以使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间呈通流状态。第一控制电路42可用于在谐振电路10达到第一预设振荡状态之前,控制第一开关s1导通,以使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间呈通流状态。第一开关s1可包括金属

‑

氧化物

‑

半导体(metal oxide semiconductor,mos)晶体管、双极型(bipolar junction transistor,bjt)晶体管或继电器等。第一控制电路42可输出高电平或低电平至第一开关s1的控制端,以控制第一开关s1周期性导通或关断。第一开关s1的控制端可与第一反相器4223的输出端电连接。

46.可选地,在上述实施例的基础上,继续参见图5,反馈放大电路20包括反馈电阻r0、第二电流源21和放大电路22。

47.其中,反馈电阻r0的第一端与反馈放大电路20的第一端q1电连接;反馈电阻r0的第二端与谐振电路10的第二端xt1电连接;放大电路22的第一端与反馈电阻r0的第二端电连接;放大电路22的第二端与反馈放大电路20的第一端q1电连接;第二电流源21与放大电路22的第二端电连接。

48.其中,反馈电阻r0可使放大电路22内的晶体管工作在线性区或亚阈值区,不会工作在完全导通或完全截止的状态。放大电路22正常工作时,等效为负阻,该负阻可以抵消谐振电路10中的晶体等效内阻的功耗损耗,从而整个振荡电路得以维持稳定的振荡。

49.可选的,放大电路22为跨导可调放大电路,其中,在谐振电路10达到第二预设振荡状态之前放大电路22的跨导大于在谐振电路10达到第二预设振荡状态之后放大电路的跨导。

50.其中,第二预设振荡状态可以是谐振电路10的振幅达到设定振幅后的稳定振荡状态。第二预设振荡状态可以在第一预设振荡状态之前或之后。

51.其中,电路上电时,因振荡电路尚未起振或者振动幅度较小,没有达到设定振幅的稳定振荡状态,相当于谐振电路10未达到第二预设振荡状态,使放大电路22的跨导较大,等效的负电阻绝对值也较大,利于振荡电路的起振,让振荡电路快速振荡起来。当启动后,振荡电路稳定振荡后,相当于谐振电路10达到第二预设振荡状态之后,为了节省功耗,将放大电路22的跨导减小,振荡电路将由启动阶段转换到低功耗模式。

52.可选的,第二电流源21为可调电流源,其中,在谐振电路10达到第二预设振荡状态之前第二电流源21输出的电流大于在谐振电路10达到第二预设振荡状态之后第二电流源21输出的电流。

53.其中,电路上电时,因振荡电路尚未起振或者振动幅度较小,没有达到设定振幅的稳定振荡状态,相当于谐振电路10未达到第二预设振荡状态,使第二电流源21输出的电流较大,以使放大电路22的工作电流较大,利于振荡电路的起振,让振荡电路快速振荡起来。当启动后,振荡电路稳定振荡后,相当于谐振电路10达到第二预设振荡状态之后,为了节省功耗,将第二电流源21输出的电流减小,以使放大电路22的工作电流减小,振荡电路将由启动阶段转换到低功耗模式。

54.可选的,在上述实施例的基础上,继续参见图5,放大电路22包括第二晶体管n2、第三晶体管n0、第四晶体管n1和第二控制电路23。

55.其中,第二晶体管n2的控制极,以及第三晶体管n0的控制极,均与放大电路22的第一端电连接;第二晶体管n2的第一极,以及第三晶体管n0的第一极,均与放大电路22的第二

端电连接;第二晶体管n2的第二极接地;第三晶体管n0的第二极与第四晶体管n1的第一极电连接;第四晶体管n1的第二极接地;第四晶体管n1的控制极与第二控制电路23电连接;第三晶体管n0的尺寸大于第二晶体管n2的尺寸;第二控制电路23用于在谐振电路10达到第二预设振荡状态之前,控制第四晶体管n1导通;在谐振电路10达到第二预设振荡状态之后,控制第四晶体管n1关断。

56.其中,第二控制电路23可输出高电平或低电平至第四晶体管n1的控制极,以控制第四晶体管n1的导通或关断。第二晶体管n2可包括nmos管,第二晶体管n2的第一极可为漏极,第二晶体管n2的第二极可为源极,第二晶体管n2的控制极可为栅极。第三晶体管n0可包括nmos管,第三晶体管n0的第一极可为漏极,第三晶体管n0的第二极可为源极,第三晶体管n0的控制极可为栅极。第四晶体管n1可包括nmos管,第四晶体管n1的第一极可为漏极,第四晶体管n1的第二极可为源极,第四晶体管n1的控制极可为栅极。晶体管的尺寸越大,跨导越大。

57.其中,电路上电时,因振荡电路尚未起振或者振动幅度较小,没有达到设定振幅的稳定振荡状态,相当于谐振电路10未达到第二预设振荡状态,第二控制电路23控制第四晶体管n1导通,第三晶体管n0起作用,以使放大电路22的跨导较大,等效的负电阻绝对值也较大,利于振荡电路的起振,让振荡电路快速振荡起来。当启动后,振荡电路稳定振荡后,相当于谐振电路10达到第二预设振荡状态之后,为了节省功耗,第二控制电路23控制第四晶体管n1关断,第三晶体管n0不起作用,以使放大电路22的跨导减小,振荡电路将由启动阶段转换到低功耗模式。

58.可选的,在上述实施例的基础上,继续参见图5,第二电流源21包括第一直流电流源单元211、第二直流电流源单元212和第五晶体管p2。

59.其中,第一直流电流源单元211与放大电路22的第二端电连接;第二直流电流源单元212与第五晶体管p2的第一极电连接;第五晶体管p2的第二极与放大电路22的第二端电连接;第五晶体管p2的控制极与第二控制电路23电连接;第二控制电路23用于在谐振电路10达到第二预设振荡状态之前,控制第五晶体管p2导通;在谐振电路10达到第二预设振荡状态之后,控制第五晶体管p2关断。

60.其中,第二控制电路23可输出高电平或低电平至第五晶体管p2的控制极,以控制第五晶体管p2的导通或关断。第五晶体管p2可包括pmos管,第五晶体管p2的第一极可为源极,第五晶体管p2的第二极可为漏极,第五晶体管p2的控制极可为栅极。

61.其中,电路上电时,因振荡电路尚未起振或者振动幅度较小,没有达到设定振幅的稳定振荡状态,相当于谐振电路10未达到第二预设振荡状态,第二控制电路23控制第五晶体管p2导通,第一直流电流源单元211起作用,以使放大电路22的工作电流较大,等效的负电阻绝对值也较大,利于振荡电路的起振,让振荡电路快速振荡起来。当启动后,振荡电路稳定振荡后,相当于谐振电路10达到第二预设振荡状态之后,为了节省功耗,第二控制电路23控制第五晶体管p2关断,第一直流电流源单元211不起作用,以使放大电路22的工作电流减小,振荡电路将由启动阶段转换到低功耗模式。

62.可选的,在上述实施例的基础上,继续参见图5,第一直流电流源单元211可以包括第七晶体管p0。其中,第七晶体管p0的第一极与第二电压源60电连接;第七晶体管p0的第二极与放大电路22的第二端电连接;第七晶体管p0的控制极与第一电压源50电连接。

63.其中,第一直流电流源单元211可输出恒定的电流。第七晶体管p0可以包括pmos管,第七晶体管p0的第一极可为源极,第七晶体管p0的第二极可为漏极,第七晶体管p0的控制极可为栅极。通过调节第七晶体管p0的控制极的电压,可以调节流过第七晶体管p0的电流。可根据需要设置第一电压源50的输出电压的大小,以使第一直流电流源单元211输出的电流大小满足要求。

64.可选的,在上述实施例的基础上,继续参见图5,第二直流电流源单元212可以包括第八晶体管p1。其中,第八晶体管p1的第一极与第二电压源60电连接;第八晶体管p1的第二极与第五晶体管p2的第一极电连接;第八晶体管p1的控制极与第一电压源50电连接。

65.其中,第二直流电流源单元212可输出恒定的电流。第八晶体管p1可以包括pmos管,第八晶体管p1的第一极可为源极,第八晶体管p1的第二极可为漏极,第八晶体管p1的控制极可为栅极。通过调节第八晶体管p1的控制极的电压,可以调节流过第八晶体管p1的电流。可根据需要设置第一电压源50的输出电压的大小,以使第二直流电流源单元212输出的电流大小满足要求。

66.可选地,在上述实施例的基础上,图7为本发明实施例提供的一种第二控制电路的结构示意图,结合图5和图7所示,第二控制电路23包括振荡状态识别电路231和选择信号产生电路232。

67.其中,振荡状态识别电路231的输出端与选择信号产生电路232的输入端电连接;选择信号产生电路232的第一输出端与第四晶体管n1的控制极电连接;选择信号产生电路232的第二输出端与第五晶体管p2的控制极电连接。

68.其中,振荡状态识别电路231可与谐振电路10电连接。振荡状态识别电路231可用于识别谐振电路10的振荡状态。在谐振电路10达到第二预设振荡状态时,振荡状态识别电路231的输出信号发生翻转,进而选择信号产生电路232的第一输出端的输出信号发生翻转,例如由低电平变为高电平,且选择信号产生电路232的第二输出端的输出信号发生翻转,例如由高电平变为低电平,以使第四晶体管n1由导通变为关断,第五晶体管p2由导通变为关断,以使放大电路22的跨导减小,第二电流源21的输出电流减小,以使振荡电路将由启动阶段转换到低功耗模式。

69.可选的,在上述实施例的基础上,继续参见图7,振荡状态识别电路231可包括第二比较器2311和第二计数器2312。其中,第二比较器2311的第一输入端可与谐振电路10电连接;第二比较器2311的第二输入端与参考电压源70电连接;第二比较器2311的输出端经第二计数器2312与选择信号产生电路232的输入端电连接。

70.其中,可选的,第二比较器2311的第一输入端可为正相输入端,第二比较器2311的第二输入端可为反相输入端。可选的,第二比较器2311的第一输入端可为反相输入端,第二比较器2311的第二输入端可为正相输入端。

71.示例性的,谐振电路10产生的正弦信号幅度较小时,第二比较器2311输出信号为低电平,振荡一段时间后,谐振电路10产生的正弦信号幅度较大,第二比较器2311输出信号为方波信号,第二计数器2312计数的脉冲数量,达到第二预设值时,第二计数器2312输出信号发生翻转,例如由低电平变为高电平。

72.可选的,在上述实施例的基础上,继续参见图7,选择信号产生电路232可包括d触发器2321和第三反相器2322。其中,d触发器2321的信号输入端d可与选择信号产生电路232

的输入端电连接;d触发器2321的信号输出端q经第三反相器2322与选择信号产生电路232的第一输出端电连接;d触发器2321的信号输出端q与选择信号产生电路232的第二输出端电连接。

73.示例性的,当振荡状态识别电路231输出信号发生翻转时,进而d触发器2321的脉冲信号输入端clk有上升边沿的信号到来时,该d触发器2321输出信号发生翻转,锁住高电平信号,直到有清零信号输入清零端clr,将该状态清零。d触发器的时钟输入端clk可与一时钟信号源电连接。d触发器2321输出信号发生翻转时,第三反相器2322的输出信号将发生翻转,以使第四晶体管n1由导通变为关断,第五晶体管p2由导通变为关断。

74.可选的,在上述实施例的基础上,继续参见图5,谐振电路10包括晶体y1、第一电容c0和第二电容c1。

75.其中,晶体y1的第一端经第一电容c0接地,晶体y1的第一端与谐振电路10的第一端xt2电连接;晶体y1的第二端经第二电容c1接地;晶体y1的第二端与谐振电路10的第二端xt1电连接。

76.其中,晶体y1可为石英晶体。振荡电路中主要是通过晶体y1的振荡,从而产生周期性的正弦波信号。石英晶体y1、第一电容c0和第二电容c1构成π型网络形式的带通滤波器,在石英晶体y1的共振频率上,提供180度相移与所需的电压增益。

77.结合图5、图6和图7所示,具有相同标记的电气节点之间为电性连接,如drvstb、drvst1、drvb和xtout。

78.图8为本发明实施例提供的一种振幅较小时各晶体管的开关状态示意图。其中,画

×

标记的晶体管为关断状态。结合图6、图7和图8所示,当电路上电时,因振荡电路尚未起振或者振动幅度较小,没有达到设定振幅值的稳定振荡状态,振动幅度较小的正弦波信号输入振荡状态识别电路231中的第二比较器2311后输出低电平,经过d触发器2321后输出仍为低电平(即节点drvstb为低电平),再经过第三反相器2322后输出为高电平(即节点drvst1为高电平),以使第五晶体管p2和第四晶体管n1导通,从而可以供给放大电路22中的第二晶体管n2和第三晶体管n0较大的偏置电流,并且第三晶体管n0的尺寸远大于第二晶体管n2的尺寸,因此,启动时振荡电路的跨导较大,等效的负电阻绝对值也较大,有利于振荡电路的起振。此时,第一比较器4211的输出端输出方波,第一计数器4212计数方波的脉冲边沿的个数,未达到第一设定值,第一计数器4212的输出端输出低电平,与非门电路4213输出高电平,或非门电路4222输出低电平,第一反相器4223输出高电平(即节点drvb为高电平),以使第一晶体管p4关断,第一开关s1导通。

79.图9为本发明实施例提供的一种稳定振荡状态时t1时间段内各晶体管的开关状态示意图。图10为本发明实施例提供的一种稳定振荡状态时t2时间段内各晶体管的开关状态示意图。图11为本发明实施例提供的又一种波形图。其中,sig1可为谐振电路10的第二端xt1的电压的波形,sig2可为谐振电路10的第一端xt2的电压的波形,ck可为时钟信号产生电路421的输出端out1输出的时钟信号的波形,i1可为脉冲电流输出电路40输出的电流的波形。结合图6、图7、图9和图11所示,当振荡电路振荡一段时间后,放大电路22的第二端(即节点xtout)达到设定振幅值的稳定振荡状态,输入的正弦波信号振动幅度较大,第二比较器2311输出方波信号,在第二计数器2312计数达到第二预设值时,第二计数器2312输出信号翻转,例如由低电平变为高电平,经过d触发器2321后输出为高电平,再经过第三反相器

2322后输出的信号为低电平,以使控制第五晶体管p2和第四晶体管n1关断,振荡电路将由启动阶段转换到低功耗模式。第一比较器4211的输出端输出方波,第一计数器4212计数方波的脉冲边沿的个数,达到第一设定值后,第一计数器4212的输出端输出信号发生翻转,例如由低电平变为高电平,使能与非门电路4213,时钟信号产生电路421的输出端out1将输出时钟信号。时钟信号产生电路421产生的时钟信号经过信号延迟电路4221的延迟后,延迟的信号与原来的时钟信号一起经过或非门电路4222,之后将产生时间较短的脉冲信号,以控制第一晶体管p4和第一开关s1的周期性导通或关断。结合图9、图10和图11所示,从第一控制电路42输出的方波信号驱动第一晶体管p4周期性导通,维持振荡电路的振荡,进入低功耗工作模式。在低功耗工作模式下,在t1阶段,第一开关s1关断,第一晶体管p4导通,第一晶体管p4给予晶体y1的电流全被晶体y1吸收,避免给予晶体y1的驱动电流,会被提供负阻功能的第二晶体管n2直接导向地,造成极大的功率损失的情况发生。

80.可选的,在上述实施例的基础上,继续参见图5,脉冲电流输出电路40与谐振电路10的第一端xt2电连接。

81.可选的,在上述实施例的基础上,图12为本发明实施例提供的又一种振荡电路的结构示意图,脉冲电流输出电路40与谐振电路10的第二端xt1电连接。

82.可选的,在上述实施例的基础上,继续参见图12,振荡电路还包括隔离电阻r1。反馈放大电路20的第一端q1依次经隔离电阻r1、电流通断控制电路30与谐振电路10的第一端xt2电连接。反馈放大电路20的第一端q1经隔离电阻r1与反馈电阻r0的第一端电连接。

83.其中,隔离电阻r1可将反馈放大电路20的输出与石英晶体y1、第一电容c0和第二电容c1构成π型网络隔离开来。隔离电阻r1可抑制高频混附振荡,以获得干净的输出信号;降低石英晶体的驱动功率,以防止超过石英晶体的容许驱动功率。

84.可选的,在上述实施例的基础上,继续参见图12,电流通断控制电路30包括第二开关s2和第一电阻r2。其中,第二开关s2的第一端,以及第一电阻r2的第一端,均与谐振电路10的第一端xt2电连接;第二开关s2的第二端,以及第一电阻r2的第二端,均经隔离电阻r1与反馈放大电路20的第一端q1电连接;第二开关s2的控制端与第一控制电路42电连接;第一控制电路42用于在谐振电路10达到第一预设振荡状态之后,控制第二开关s2周期性导通或关断。

85.其中,第一电阻r2的阻值较大。第一控制电路42可用于在谐振电路10达到第一预设振荡状态之后,脉冲电流输出电路40输出电流至谐振电路10时,控制第二开关s2关断,第一电阻r2将起作用,以使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间呈阻流状态。第一控制电路42可用于在谐振电路10达到第一预设振荡状态之后,脉冲电流输出电路40不输出电流至谐振电路10时,控制第二开关s2导通,第一电阻r2被短路,将不起作用,以使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间呈通流状态。第一控制电路42可用于在谐振电路10达到第一预设振荡状态之前,控制第二开关s2导通,第一电阻r2被短路,将不起作用,以使谐振电路10的第一端xt2和反馈放大电路20的第一端q1之间呈通流状态。第二开关s2可包括金属

‑

氧化物

‑

半导体(metal oxide semiconductor,mos)晶体管、双极型(bipolar junction transistor,bjt)晶体管或继电器等。

86.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、

重新调整、相互结合和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。