1.本发明涉及电子器件的技术领域,具体涉及一种灵敏放大器半缓冲器。

背景技术:

2.目前的数字电路主要分为同步和异步两种设计方法。由于同步电路较为简单,因而目前应用更为广泛。但是同步电路也有一些缺点:时钟信号持续翻转造成巨大功耗;需要严格的时序约束,难度较高;在面对工艺、电压、温度(power

‑

voltage

‑

temperature,pvt)扰动时可能发生错误等。

3.而异步电路则能克服这些缺点:异步电路具有更放松的时序约束;面对pvt扰动有更好的鲁棒性;由于没有全局时钟信号,信号反转更少,功耗更低;系统性能取决于平均路径延迟而非关键路径延迟,具有更高的性能潜力。

4.异步电路数据通信依靠异步传输协议,可根据时序方法分为三种类型:1)延迟不灵敏(delay

‑

insensitive,di);2)数据捆绑(bundled

‑

data,bd);3)准延时不灵敏(quasi

‑

delay

‑

insensitive,qdi)/时间流水线(timed

‑

pipeline,tp)/单轨(single

‑

track,st)。对于di电路,由于它们不假设门、线延迟,导致电路仅包含缓冲单元和c

‑

muller单元,所以并不实用。对于bd电路,它们的实现依赖于与同步电路类似的捆绑门、线延迟,因此在设计上有一定挑战性。对于tp和st电路,它们需要时序约束,较为复杂。而qdi电路无需对逻辑门和信号线进行时序约束,设计简单;根据实际工作负载和操作条件检测数据的完成情况,最为实用;适应未知的pvt变化,鲁棒性较强。

5.在qdi电路中,有pchb(precharged half buffer,预充电半缓冲器)和sahb(sense amplifier half

‑

buffer,灵敏放大器半缓冲器)等电路类型。pchb标准单元采用异步qdi协议,在lcd和功能块f之间的线叉(wire fork)是等时的假设下工作。pchb有功耗低、鲁棒性强等优点,并且已经成功商业化实现,但它也有面积大、速度不够快、不适合亚阈值操作等缺点。

6.现有的sahb是异步qdi四相协议,其示意图如图1所示。sahb与pchb相比具有面积小、能耗低等优点,但缺点也很明显:已有的sahb由两部分组成,即运算块和放大块,因而面积不够小;其上拉网络由nmos组成,且串联的晶体管数目比较大,因此速度不够快。

技术实现要素:

7.本发明提供了一种可灵敏放大器半缓冲器,解决了现有灵敏放大器半缓冲器的面积大、速度慢等问题。

8.本发明可通过以下技术方案实现:

9.一种灵敏放大器半缓冲器,包括传输模块和握手信号产生模块,所述传输模块用于数据传输,所述握手信号产生模块用于根据传输的数据,生成握手信号,采用或非门结构,其输入端与传输模块的输出端连接,其输出端设置为握手信号lack,

10.所述传输模块包括多个握手信号晶体管和多个逻辑晶体管,所述握手信号晶体管

包括:第一握手信号晶体管m1、第二握手信号晶体管m4、第三握手信号晶体管m7;所述逻辑晶体管包括:第一逻辑晶体管m2、第二逻辑晶体管m3、第三逻辑晶体管m5、第四逻辑晶体管m6;

11.其中,第一逻辑晶体管m2的栅极设置为输入数据a.f端口,源极与第一握手信号晶体管m1的漏极相连,漏极与第二握手信号晶体管m4的漏极、第三逻辑晶体管m5的漏极及输出端q.t相连,同时还与第四逻辑晶体管m6的栅极连接;

12.第二逻辑晶体管m3的栅极设置为输入数据a.t端口,源极与第一握手信号晶体管m1的漏极相连,漏极与第四逻辑晶体管m6的漏极、第三握手信号晶体管m7的漏极及输出端q.f相连,同时还与第三逻辑晶体管m5的栅极连接;

13.第三逻辑晶体管m5的栅极与输出端q.f相连,源极接地,漏极与第一逻辑晶体管m2的漏极、第二握手信号晶体管m4的漏极相连;

14.第四逻辑晶体管m6的栅极与输出端q.t相连,源极接地,漏极与第二逻辑晶体管m3的漏极、第三握手信号晶体管m7的漏极相连;

15.第一握手信号晶体管m1的栅极与握手信号rack相连,源极与电源vdd相连,漏极与第一逻辑晶体管m2的源极、第二逻辑晶体管m3的源极相连;

16.第二握手信号晶体管m4的栅极与握手信号rack相连,源极接地,漏极与第一逻辑晶体管m2的漏极、第三逻辑晶体管m5的漏极相连;

17.第三握手信号晶体管m7的栅极与握手信号rack相连,源极接地,漏极与第二逻辑晶体管m3的漏极、第四逻辑晶体管m6的漏极相连;

18.所述握手信号rack设置为同一线路上相邻的上一个异步模块的握手输出信号。

19.进一步,所述握手信号产生模块包括第四握手信号晶体管m8、第五握手信号晶体管m9、第六握手信号晶体管m10、第七握手信号晶体管m11,其输入端与输出端q.t和q.f连接。

20.本发明有益的技术效果在于:

21.本发明的sahb仅使用了11个晶体管,与现有sahb的33个晶体管相比减小了面积;没有使用数据信号的逻辑互补信号,降低了信号的复杂度,提高了运算速度。

附图说明

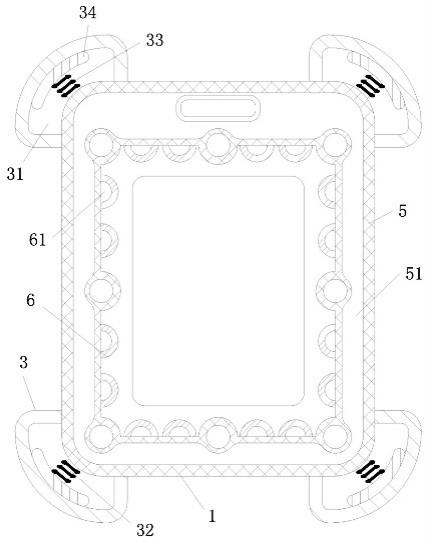

22.图1是本发明的现有灵敏放大器半缓冲器的总体电路结构示意图;

23.图2是本发明的灵敏放大器半缓冲器的总体电路结构示意图;

24.图3是本发明的逻辑晶体管m2、m3、m5、m6组成灵敏放大器的等效电路示意图。

具体实施方式

25.下面结合附图及较佳实施例详细说明本发明的具体实施方式。

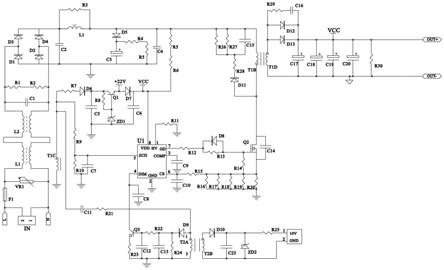

26.如图2所示,本发明提供了一种灵敏放大器半缓冲器,包括传输模块和握手信号产生模块,所述传输模块用于数据传输,其输入端除了连接待传输的输入数据,还连接同一线路上相邻的上一个异步模块的握手输出信号;所述握手信号产生模块用于根据传输的数据,生成握手信号,采用或非门结构,其输入端与传输模块的输出端连接,其输出端设置为握手信号lack,具体如下:

27.所述传输模块包括多个握手信号晶体管和多个逻辑晶体管,所述握手信号晶体管包括:第一握手信号晶体管m1、第二握手信号晶体管m4、第三握手信号晶体管m7;所述逻辑晶体管包括:第一逻辑晶体管m2、第二逻辑晶体管m3、第三逻辑晶体管m5、第四逻辑晶体管m6;

28.其中,第一逻辑晶体管m2的栅极设置为输入数据a.f端口,源极与第一握手信号晶体管m1的漏极相连,漏极与第二握手信号晶体管m4的漏极、第三逻辑晶体管m5的漏极及输出端q.t相连,同时还与第四逻辑晶体管m6的栅极连接;

29.第二逻辑晶体管m3的栅极设置为输入数据a.t端口,源极与第一握手信号晶体管m1的漏极相连,漏极与第四逻辑晶体管m6的漏极、第三握手信号晶体管m7的漏极及输出端q.f相连,同时还与第三逻辑晶体管m5的栅极连接;

30.第三逻辑晶体管m5的栅极与输出端q.f相连,源极接地,漏极与第一逻辑晶体管m2的漏极、第二握手信号晶体管m4的漏极相连;

31.第四逻辑晶体管m6的栅极与输出端q.t相连,源极接地,漏极与第二逻辑晶体管m3的漏极、第三握手信号晶体管m7的漏极相连;

32.第一握手信号晶体管m1的栅极与握手信号rack相连,源极与电源vdd相连,漏极与第一逻辑晶体管m2的源极、第二逻辑晶体管m3的源极相连;

33.第二握手信号晶体管m4的栅极与握手信号rack相连,源极接地,漏极与第一逻辑晶体管m2的漏极、第三逻辑晶体管m5的漏极相连;

34.第三握手信号晶体管m7的栅极与握手信号rack相连,源极接地,漏极与第二逻辑晶体管m3的漏极、第四逻辑晶体管m6的漏极相连;

35.所述握手信号rack设置为同一线路上相邻的上一个异步模块的握手输出信号。

36.由此可见,第一逻辑晶体管m2、第二逻辑晶体管m3的栅极组成输入数据的双轨信号a.t和a.f,其中第一逻辑晶体管m2为a.f,第二逻辑晶体管m3为a.t。第三逻辑晶体管m5、第四逻辑晶体管m6的栅极连接了输出数据的双轨信号q.t和q.f,其中第三逻辑晶体管m5为q.f,第四逻辑晶体管m6为q.t。第一握手晶体管m1、第二握手晶体管m4、第三握手晶体管m7的栅极为上一异步模块的握手输出信号的输入端。

37.该握手信号产生模块包括第四握手信号晶体管m8、第五握手信号晶体管m9、第六握手信号晶体管m10、第七握手信号晶体管m11,其输入端与输出端q.t和q.f连接。

38.本发明的灵敏放大器半缓冲器sahb也遵守四相握手协议,包括两个交替的操作:求值和复位。在复位时,输入握手信号rack=1,表示输入数据无效,即为空,即输入端a.t=a.f=0。此时上拉逻辑中的第一握手信号晶体管m1关闭,上拉电路不通;下拉逻辑中的第二握手信号晶体管m4和第三握手信号晶体管m7打开,输出信号q.t=q.f=0,同时通过握手信号产生模块中的或非门得到输出握手信lack=1,表示输出为空。

39.在求值时,输入握手信号rack=0,输入数据有效,即不为空。此时上拉逻辑中的第一握手信号晶体管m1打开,下拉逻辑中的第二握手信号晶体管m4和第三握手信号晶体管m7关闭,逻辑晶体管m2、m3、m5、m6组成灵敏放大器,等效电路如图3所示。

40.当输入数据为1时,即输入端a.t=1,输入端a.f=0时,第一逻辑晶体管m2打开,第二逻辑晶体管m3关闭,输出端q.t被拉高到1,从而第四逻辑晶体管m6打开,使输出端q.f保持为0;输出端q.f为0使第三逻辑晶体管m5保持关闭,从而保证输出端q.t不会被拉低到1,

此时输出握手信号lack=0,表示输出数据有效。

41.当输入数据为0,即输入端a.t=0,输入端a.f=1时,第一逻辑晶体管m2关闭,第二逻辑晶体管m3打开,输出端q.f被拉高到1,从而第三逻辑晶体管m5打开,使输出端q.t保持为0;输出端q.t为0使第四逻辑晶体管m6保持关闭,从而保证输出端q.f不会被拉低到1,此时输出握手信号lack=0,表示输出数据有效。

42.如图1所示的现有sahb包含两个模块:计算块和敏感放大器块。计算块包含输入的确认信号rack和逻辑部分,上拉部分和下拉部分全部使用nmos晶体管,以减少寄生电容。计算块的逻辑部分与组合电路的逻辑相似,rack信号用以控制输出;敏感放大器块的上拉部分由输入信号和rack信号共同控制,当数据有效且rack信号为0时将下半部分的敏感放大器接到电源vdd,对输出进行放大。

43.而本发明的sahb考虑将计算块和敏感放大器块合并以减少面积,并将计算块的上拉部分换成pmos晶体管以加快输出速度。将现有sahb标准单元计算块的上拉电路替换为pmos晶体管,下拉电路替换成的敏感放大器的下半部分,上拉电路与下拉电路共同组成敏感放大器,放大器的工作与否由握手信号rack控制。当握手信号rack为0时,放大器应当起到放大并锁存输出的作用;当确认信号rack=1时,放大器应当被断开,而通向vss的电路应打开,将输出拉低。

44.因此,本发明的sahb仅使用了11个晶体管,与现有sahb的33个晶体管相比减小了面积;没有使用数据信号的逻辑互补信号,降低了信号的复杂度,提高了运算速度。

45.此外要说明的时,本发明不仅限于缓冲器,可将第一逻辑晶体管m2和第二逻辑晶体管m3替换为其他逻辑电路的上拉逻辑,如与非、或非等,即可成为使用sahb逻辑的异步逻辑单元。

46.虽然以上描述了本发明的具体实施方式,但是本领域的技术人员应当理解,这些仅是举例说明,在不背离本发明的原理和实质的前提下,可以对这些实施方式做出多种变更或修改,因此,本发明的保护范围由所附权利要求书限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。