基于fpga和微处理器的芯片模拟系统及实现方法

技术领域

1.本发明涉及通信领域,具体地,涉及一种基于fpga和微处理器的芯片模拟系统及实现方法。

背景技术:

2.目前众多1553b协议实现方法中,单纯的使用硬件描述语言,或者纯软件模拟1553b的协议功能。硬件描述语言设计复杂,占用资源多,不容易扩展多功能模块。软件模拟不能够作为实际的芯片使用,仅作为软件仿真。并且两种方法都不能兼容bu61580的芯片功能。

3.专利文献为cn102831096a的发明专利公开了一种1553b总线协议ip核,包括axi从设备接口、寄存器模块、bc模块、rt模块、ram仲裁模块、共享ram、通道选择模块、编码器模块8、解码器模块、输出选择模块、计时器;其中,axi从设备接口分别连接到寄存器模块、ram仲裁模块,寄存器模块分别连接到bc模块、rt模块,bc模块分别连接到ram仲裁模块、通道选择模块,rt模块分别连接到ram仲裁模块、通道选择模块,ram仲裁模块还连接到共享ram,通道选择模块还分别连接到编码器模块、解码器模块,编码器模块、解码器模块各自连接到输出选择模块。但是上述方案设计复杂,仅采用硬件描述语言实现,设计难度大,并且不能扩展多功能单元,不能够兼容bu61580的功能。

4.专利文献为cn103077147b的发明专利公开了一种基于链表的全功能1553b总线ip核,包含bc模块、rt模块、bm模块、编码器、解码器、消息解析模块、存储模块、中断模块、时标模块、自检测模块、全局寄存器、总线仲裁模块。与传统的1553b总线ip核相比,本发明通过链表的方式管理bc模块、rt模块、bm模块的数据,通过指针自动获取下一个地址,不占用资源进行寻址计算,数据在存储空间中连续存储,不浪费存储资源,保证资源最大限度的被利用,有利于系统的精简和小型化,而且系统性能获得很大提高。但是上述方案设计复杂,仅采用硬件描述语言实现,设计难度大,并且不能扩展多功能单元,不能够兼容bu61580的功能。

5.专利文献为cn104679693b的发明专利公开了一种1553b总线协议ip核的多接口模式实现方法,提供了一种1553b总线协议ip核的多接口模式实现方法。该方法是通过接收并识别微处理器的相关配置指令,实现对1553b总线协议ip核中接口单元的读写控制模式的识别。可识别出透明模式下的读写1553b总线协议ip核的外部存储器、读写1553b总线协议ip核内部的共享存储器两种读写控制模式,并可识别出缓冲模式下的16位非零等待缓冲模式、以及16位零等待缓冲模式两种读写控制模式,还可识别出缓冲模式下的8位非零等待缓冲模式、以及8位零等待缓冲模式两种读写控制模式,从而解决了现有1553b总线协议ip核的接口形式单一的问题,提高了可扩展性。但是上述方案设计复杂,仅采用硬件描述语言实现,设计难度大,并且扩展多功能单元模块难度大、占有资源多且复杂。

6.专利文献为cn111209154a的发明专利公开了一种虚拟1553b总线设备的实现方法,包括:按照真实1553b板卡,设置供应用程序调用的api接口;通过虚拟1553b总线对本机

的通用寄存器进行虚拟化,以及对虚拟1553b总线数据传输时的控制逻辑和响应状态进行仿真;编写网络调用程序,向虚拟1553b设备提供网络接入服务;通过网络调用程序,设置模拟的总线控制器和远程终端,并通过总线控制器和远程终端执行对总线指令字、数据字、状态字的计算;设置故障数据的格式和注入机制,并对虚拟1553b总线设备的通讯过程进行虚拟。但是上述方案为纯软件模拟1553b的收发协议,并不能实现真实的芯片功能,不能够兼容bu61580的功能。

7.专利文献为cn109992554b的发明专利公开了一种基于通用的schema结构描述的1553b总线通信协议的实现方法,所述方法包括:对于1553b总线通信协议中各类消息采用预定的格式进行预定义得到消息封装;对于各类消息的通信方式采用预定的格式进行封装得到中断封装;基于消息封装和中断封装分别对1553b总线通信协议的通信时序关系、总线系统设置和各用户消息类型进行描述,生成描述代码;在通信实体中,直接编译或解释执行所述描述代码,实现1553b总线通信协议。上述方案采用封装的方式,设计难度大,且无法兼容bu61580的功能。

技术实现要素:

8.针对现有技术中的缺陷,本发明的目的是提供一种基于fpga和微处理器的芯片模拟系统及实现方法。

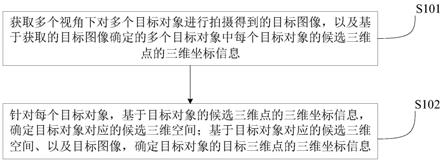

9.根据本发明提供的一种基于fpga和微处理器的芯片模拟系统,包括fpga模块、总线收发器、隔离器,其中:

10.fpga模块包括微处理器,所述fpga模块接入总线并与总线收发器通信连接;

11.fpga模块、总线收发器、隔离器依次电性连接;

12.隔离器接入1553b总线。

13.优选地,所述fpga模块包括数据接收单元、数据发送单元、定时器单元以及中断控制单元,其中:

14.数据接收单元接收收发器中的并行数据,将接收的并行数据加时间戳、进行类型标识以及进行错误标识;

15.数据发送单元根据要发送的数据,按照时间节点、数据类型进行发送,将数据发送给总线收发器;

16.定时器单元作为数据接收和发送的时间计时,将实时时间发送给接收单元和发送单元;

17.中断控制单元接收到总线数据产生中断信号,发送给微处理器。

18.优选地,所述微处理器包括第一微处理器和第二微处理器,其中:

19.第一微处理器运行总线解析代码;

20.第二微处理器运行bu61580芯片逻辑代码。

21.优选地,第一微处理器和第二微处理器共享内存。

22.优选地,所述微处理器执行c语言代码。

23.根据本发明提供的一种基于上述的基于fpga和微处理器的芯片模拟系统的实现方法,包括如下步骤:

24.启动步骤:fpga模块启动,微处理器启动;

25.第一运行步骤:第一微处理器运行总线解析代码;

26.第一判断步骤:判断是否外部总线操作及数据更新,若判断结果为是,则进行控制读写逻辑;若判断结果为否,则重复第一判断步骤;

27.第二运行步骤:第二微处理器运行bu61580芯片逻辑代码;

28.工作模式判定步骤:判定工作模式,并基于判定的结果运行对应的代码;

29.第二判断步骤:判断是否有收发及数据更新,若判断结果为是,则进行控制读写逻辑;若判断结果为否,则重复第二判断步骤。

30.优选地,所述工作模式包括bc模式、rt模式、bm模式。

31.优选地,第一微处理器的控制读写逻辑和第二微处理器的控制读写逻辑之间共享内存。

32.优选地,第一微处理器与外部总线通信连接。

33.优选地,第二微处理器与1553b收发器通信连接。

34.与现有技术相比,本发明具有如下的有益效果:

35.1、本发明通过采用1553b总线协议预处理技术,将接收到的数据加入时间信息,从而实现命令字、响应字以及数据字的预判断,以及协议帧错误预判断。

36.2、本发明通过采用fpga内的软核或者微处理器,读取预处理数据,以及将要发送的数据,对hi

‑

1573总线收发模块的控制。

37.3、本发明通过采用软核或者微处理器执行c语言代码,实现对bu61580芯片功能的模拟控制,解决了以往通过硬件描述语言(hdl)来实现bu61580功能的复杂度以及难度。

38.4、本发明通过采用软核或者微处理器执行c语言代码,实现对bu61580芯片功能的模拟控制(bc、rt、bm),能够解决单板上实现多个bu61580的功能,避免了单纯使用fpga逻辑实现bu61580功能,占有资源量多,实现功能单元少的缺点。

附图说明

39.通过阅读参照以下附图对非限制性实施例所作的详细描述,本发明的其它特征、目的和优点将会变得更明显:

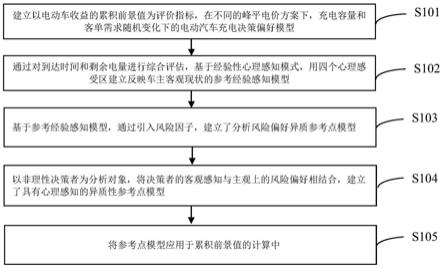

40.图1为基于fpga和微处理器的芯片模拟系统示意图。

41.图2为基于fpga和微处理器的芯片模拟实现方法流程图。

具体实施方式

42.下面结合具体实施例对本发明进行详细说明。以下实施例将有助于本领域的技术人员进一步理解本发明,但不以任何形式限制本发明。应当指出的是,对本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变化和改进。这些都属于本发明的保护范围。

43.如图1和图2所示,本发明提供的一种基于fpga和微处理器的芯片模拟系统,包括fpga模块、总线收发器、隔离器,fpga模块包括微处理器,所述fpga模块接入总线并与总线收发器通信连接;fpga模块、总线收发器、隔离器依次电性连接;隔离器接入1553b总线。fpga模块包括数据接收单元、数据发送单元、定时器单元以及中断控制单元,数据接收单元接收收发器中的并行数据,将接收的并行数据加时间戳、进行类型标识以及进行错误标识;

数据发送单元根据要发送的数据,按照时间节点、数据类型进行发送,将数据发送给总线收发器;定时器单元作为数据接收和发送的时间计时,将实时时间发送给接收单元和发送单元;中断控制单元接收到总线数据产生中断信号,发送给微处理器。微处理器包括第一微处理器和第二微处理器,其中:第一微处理器运行总线解析代码;第二微处理器运行bu61580芯片逻辑代码。第一微处理器和第二微处理器共享内存。微处理器执行c语言代码。

44.本发明提供了一种基于上述的基于fpga和微处理器的芯片模拟系统的实现方法,包括如下步骤:启动步骤:fpga模块启动,微处理器启动;第一运行步骤:第一微处理器运行总线解析代码;第一判断步骤:判断是否外部总线操作及数据更新,若判断结果为是,则进行控制读写逻辑;若判断结果为否,则重复第一判断步骤;第二运行步骤:第二微处理器运行bu61580芯片逻辑代码;工作模式判定步骤:判定工作模式,并基于判定的结果运行对应的代码;第二判断步骤:判断是否有收发及数据更新,若判断结果为是,则进行控制读写逻辑;若判断结果为否,则重复第二判断步骤。

45.进一步地,工作模式包括bc模式、rt模式、bm模式。第一微处理器的控制读写逻辑和第二微处理器的控制读写逻辑之间共享内存。第一微处理器与外部总线通信连接。第二微处理器与1553b收发器通信连接。

46.进一步的,本发明采用hi

‑

1573作为总线收发器,采用fpga的逻辑资源作为bu61580的寄存器、内存以及总线接口,采用fpga内的软核或者微处理器实现bu61580的工作流程控制,进而实现bu61580的芯片功能。

47.本发明还一种基于fpga 微处理器的bu61580芯片模拟实现方法,包括:

48.hi

‑

1573总线收发器单元,总线收发器单元,接收1553b的总线信号,将总线串行信号转化为并行数据,以及将并行数据转化为串行数据,包括:命令字、数据字以及状态字。

49.1553b总线协议预处理单元,包括:数据接收单元、数据发送单元、定时器单元、中断控制单元。数据接收单元,接收总线收发器中的并行数据,将接收的数据加时间戳、进行类型标识以及进行错误标识;数据发送单元,根据要发送的数据,按照时间节点、数据类型进行发送,将数据发送给总线收发器;定时器单元,作为数据接收和发送的时间计时,将实时时间发送给接收单元和发送单元;中断控制单元,接收到总线数据产生中断信号,发送给软核或者微处理器。

50.模拟bu61580工作流程处理单元,读取协议预处理单元的数据,通过c语言解析数据得到对应的指令,根据指令将数据、状态写入对应的内存,并将解析的协议帧,帧状态、帧错误以及帧时间写入相应寄存器中;读取cpu总线处理单元的数据,通过c语言解析数据,得到对应的指令,根据指令将数据写入相应的内存或寄存器中,并进行发送或接收操作。或者根据指令将内存或者寄存器中的数据读出,并发送给cpu总线处理单元,供cpu读取。

51.cpu总线处理单元,将cpu读写命令记录,并产生中断给处理单元;解析cpu写时序,并将cpu写入数据提供给模拟工作流程单元;解析cpu的读时序,并将模拟工作流程处理单元的提供的数据放在cpu的数据总线上。

52.本领域技术人员知道,除了以纯计算机可读程序代码方式实现本发明提供的系统及其各个装置、模块、单元以外,完全可以通过将方法步骤进行逻辑编程来使得本发明提供的系统及其各个装置、模块、单元以逻辑门、开关、专用集成电路、可编程逻辑控制器以及嵌入式微控制器等的形式来实现相同功能。所以,本发明提供的系统及其各项装置、模块、单

元可以被认为是一种硬件部件,而对其内包括的用于实现各种功能的装置、模块、单元也可以视为硬件部件内的结构;也可以将用于实现各种功能的装置、模块、单元视为既可以是实现方法的软件模块又可以是硬件部件内的结构。

53.以上对本发明的具体实施例进行了描述。需要理解的是,本发明并不局限于上述特定实施方式,本领域技术人员可以在权利要求的范围内做出各种变化或修改,这并不影响本发明的实质内容。在不冲突的情况下,本技术的实施例和实施例中的特征可以任意相互组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。