1.本发明涉及预失真技术,特别是涉及一种具有频率选择特性的数字预失真校正方法与装置。

背景技术:

2.功放的非线性会导致功放输出信号出现非线性失真。假设功放基带输入信号为一个宽带信号,将功放基带输出减功放输入就可以得到基带非线性失真信号。频谱示意如图1所示。可以看到,功放输入信源信号为在频带

‑

f1~f1的宽带信号,但是非线性失真的失真信号分布在一个扩展了的频带范围内。我们将频段

‑

f1~f1,f1~f2以及f2~f3分别记为主信道频段,相邻信道频段1,以及相邻信道频段2。

3.非线性失真有两个不好的影响:1、恶化接收机端的误码率,降低本信道的通信质量;2、泄露到相邻信道的失真分量会对相邻信道的通信进行干扰。对相邻信道的干扰是通信标准中不允许的,因此相邻信道的失真分量功率必须被抑制到指标以下。比如要求发射机发射信号的邻信道功率比(acpr)小于

‑

45dbc的指标。

4.为了解决非线性失真的不良影响同时保证功放的效率,工程中通常采用数字预失真技术对功放进行线性化,从而遏制非线性失真。传统数字预失真技术对整体非线性失真进行抑制,即抑制整个频段内的非线性失真。这种数字预失真技术在功放处于强失真不具备频率选择特性,即无法关注于抑制某一个特定频段的非线性失真。

技术实现要素:

5.本发明的目的在于克服现有技术的不足,提供一种具有频率选择特性的数字预失真校正方法与装置,通过线性化频段选择滤波器来选择失真抑制的频段,通过调整线性化频段选择滤波器的通带频率范围,可以指定任意频段的非线性失真进行抑制。

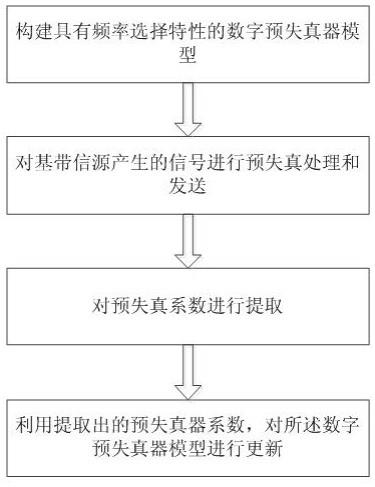

6.本发明的目的是通过以下技术方案来实现的:一种具有频率选择特性的数字预失真校正方法,包括以下步骤:

7.s1.构建具有频率选择特性的数字预失真器模型;

8.s2.对基带信源产生的信号进行预失真处理和发送;

9.s3.对预失真系数进行提取;

10.s4.利用提取出的预失真器系数,对所述数字预失真器模型进行更新。

11.进一步地,所述步骤s1包括以下子步骤:

12.s101.将数字预失真器模型分为线性部分模型和非线性部分模型:

13.其中,线性部分模型表示为:

[0014][0015]

非线性部分模型表示为:

[0016][0017]

其中,a

kq

为预失真系数,k=1,2,

…

,k,q=1,2,

…

,q;初始状态下,预失真模型的系数首项a

11

为1,其他项全部为0;x(n)信源信号,k为最大非线性阶数,q为最大记忆深度;

[0018]

s102.对于输入数字预失真器模型的信源信号x(n),将信源信号x(n)输入线性部分模型中,得到输出信号y

l

(n);同时将信源信号x(n)输入非线性部分模型中,得到输出信号y

n

(n);

[0019]

s103.将非线性部分模型的输出信号y

n

(n)经过频段选择滤波器进行处理后,与线性部分模型的输出信号y

l

(n)相加,得到数字预失真器模型的输出信号,该信号即为具有频率选择性的数字预失真信号z(n),所述频段选择滤波器的系数为h=[h1,h2,...,h

l

]

t

,得到的数字预失真信号z(n)为:

[0020][0021]

进一步地,所述步骤s2包括:

[0022]

s201.将基带信源产生的信号送入数字预失真器模型中得到数字预失真信号;

[0023]

s202.将数字预失真信号进行数模转换、上变频后送入功放pa进行放大;

[0024]

s203.将功放pa放大后的信号经过耦合器送往天线进行发射。

[0025]

进一步地,所述步骤s3包括以下子步骤:

[0026]

s301.抓取数字预失真器模型输出的信号数据x=[x(1),x(2),...,x(n)]

t

作为功放输入信号对应的基带数字信号;

[0027]

s302.从耦合器中获取耦合信号,经下变频和模数转换后,得到u=[u(1),u(2),...,u(n)]

t

作为功放输出信号对应的基带数字信号;

[0028]

s303.重构功放的输出信号,得到重构后的信号u

r

:

[0029][0030]

其中h=[h1,h2,...,h

l

]

t

,表示频段选择滤波器的系数,表示卷积;

[0031]

s304.采用间接学习架构,将重构后的功放输出信号u

r

拟合到输入信号x,即将步骤s103的中数字预失真信号公式中的信号x(n)替换为u

r

(n),z(n)替换为x(n),其中u

r

(n)表示u

r

中的样本,即u

r

=[u

r

(1),u

r

(2),

…

,u

r

(n),

…

,u

r

(n)]

t

;此时预失真系数相对于模型是线性的,用如下式所最小二乘法求出预失真系数:

[0032][0033]

其中a=[a

11

,a

12

,

…

,a

1q

,a

21

,a

22

,

…

,,a

2q

,

…

,a

kq

]

t

为预失真系数,矩阵u

r

是采用u

r

=[u

r

(1),u

r

(2),

…

,u

r

(n)]

t

中的数据,根据数字预失真信号公式中基函数构建的数据矩阵;u

r

一共有k

×

q列,其中第1到第q列对应q=1,2,3,

…

,q的基函数u

r

(n

‑

q 1),第一列为u

r1

=[u

r

(1),u

r

(2),

…

,u

r

(n)]

t

,第q列为u

rq

=[u

r

(1

‑

q 1),u

r

(2

‑

q 1),

…

,u

r

(n

‑

q 1)]

t

;

[0034]

第q 1列到第q

×

k列对应q=1,2,3,

…

,q与k=2,3,

…

,k的基函数,k的基函数其中第q 1列为

第q

×

k列为列为

[0035]

进一步地,所述步骤s4包括:

[0036]

利用求出的预失真系数a=[a

11

,a

12

,

…

,a

1q

,a

21

,a

22

,

…

,,a

2q

,

…

,a

kq

]

t

对数字预失真器模型中的预失真系数进行更新,并采用更新后的数字预失真器对后续输入的信源信号进行预失真处理。

[0037]

一种具有频率选择特性的数字预失真校正装置,包括:

[0038]

基带信源,用于提供信源信号;

[0039]

数字预失真器构建模块,用于构建具有频率选择特性的数字预失真器模型,并利用数字预失真器模型对信源信号进行处理,得到数字预失真信号;

[0040]

前置处理模块,用于对数字预失真信号进行数模转换和上变频处理后传输给功放pa;

[0041]

功放pa,用于对接收到的信号进行放大,并将放大后的信号通过耦合器传输给发射天线进行发射;

[0042]

耦合处理模块,用于从耦合器中获取耦合信号,并进行系变频和模数模数转换;

[0043]

预失真系数提取模块,用于抓取数字预失真器模型输出的信号数据和耦合处理模块输出的信号数据,并据此进行预失真系数提取,利用提取的系数

[0044]

其中,所述前置处理模块包括dac模块和上变频混频器,所述dac模块的输入端接收数字预失真器模型输出的数字预失真信号,dac模块的输出端与上变频混频器连接,上变频混频器的输出端与所述功放pa连接。

[0045]

其中,所述耦合处理模块包括下变频混频器和adc模块,所述下变频混频器的输入端与所述耦合器连接,下变频混频器的输出端与adc模块连接,所述adc模块的输出端与预失真系数提取模块连接。

[0046]

所述数字预失真校正装置还包括本振源,所述本振源分别与上变频混频器和下变频混频器连接,用于为上变频混频器和下变频混频器提供本振信号。

[0047]

本发明的有益效果是:本发明预失真器系数提取过程简单,不需要复杂的迭代,具有频率选择特性的数字预失真器模型简单,与传统的数字预失真执行器相比,仅多了一个滤波器的滤波处理,并可以通过设计滤波器的幅度响应,对线性化结果进行控制,可以指定任意的频段进行失真抑制。

附图说明

[0048]

图1为非线性失真的频谱示意图;

[0049]

图2为本发明的方法流程图;

[0050]

图3为本发明的装置原理框图。

具体实施方式

[0051]

下面结合附图进一步详细描述本发明的技术方案,但本发明的保护范围不局限于以下所述。

[0052]

考虑到在某些情况下,我们只需要关注于抑制某一特定频段的非线性失真。例如,当evm需求较低时,我们只关注于抑制带外失真。再例如频分复用(fdd)收发机中,我们只需要抑制上边带或者下边带的非线性失真。

[0053]

因此我们提出具有频率选择特性的数字预失真技术。该数字预失真技术通过一个线性化频段选择滤波器来选择失真抑制的频段。通过调整线性化频段选择滤波器的通带频率范围,可以指定任意频段的非线性失真进行抑制,具体地:

[0054]

如图2所示,一种具有频率选择特性的数字预失真校正方法,包括以下步骤:

[0055]

s1.构建具有频率选择特性的数字预失真器模型;

[0056]

s2.对基带信源产生的信号进行预失真处理和发送;

[0057]

s3.对预失真系数进行提取;

[0058]

s4.利用提取出的预失真器系数,对所述数字预失真器模型进行更新。

[0059]

所述步骤s1包括以下子步骤:

[0060]

普通的预失真器模型为如下所示的mp模型:

[0061][0062]

我们将k等于1的项称为线性项,大于1的称为非线性项。即,预失真模型划分为如下线性部分和非线性部分,从而:

[0063]

s101.将数字预失真器模型分为线性部分模型和非线性部分模型:

[0064]

其中,线性部分模型表示为:

[0065][0066]

非线性部分模型表示为:

[0067][0068]

其中,a

kq

为预失真系数,x(n)信源信号,k为最大非线性阶数,q为最大记忆深度;

[0069]

在本技术的实施例中,在本技术的实施例中,这个预失真器模型是以mp模型为例。在应用其他模型例如gmp模型时,也可以这样分为线性部分和非线性部分,构建频率选择性的数字预失真模型。

[0070]

s102.对于输入数字预失真器模型的信源信号x(n),将信源信号x(n)输入线性部分模型中,得到输出信号y

l

(n);同时将信源信号x(n)输入非线性部分模型中,得到输出信号y

n

(n);

[0071]

s103.将非线性部分模型的输出信号y

n

(n)经过频段选择滤波器进行处理后,与线性部分模型的输出信号y

l

(n)相加,得到数字预失真器模型的输出信号,该信号即为具有频

率选择性的数字预失真信号z(n),所述频段选择滤波器的系数为h=[h1,h2,...,h

l

]

t

,得到的数字预失真信号z(n)为:

[0072][0073]

在本技术的实施例中,频段选择滤波器的通带就是所选择的进行非线性抑制频带。例如将频段选择滤波器设计为一个高通滤波器,此时具有频率选择特性的数字预失真只会抑制高通滤波器通带内的带外失真。在上述模型中,忽略滤波器h引入的延时,若需要非常精确时,考虑到频段选择滤波器的时延,在线性部分模型后可以通过一个时延模块以保证信号同步。

[0074]

进一步地,所述步骤s2包括:

[0075]

s201.将基带信源产生的信号送入数字预失真器模型中得到数字预失真信号;

[0076]

s202.将数字预失真信号进行数模转换、上变频后送入功放pa进行放大;

[0077]

s203.将功放pa放大后的信号经过耦合器送往天线进行发射。

[0078]

进一步地,所述步骤s3包括以下子步骤:

[0079]

s301.抓取数字预失真器模型输出的信号数据x=[x(1),x(2),...,x(n)]

t

作为功放输入信号对应的基带数字信号;

[0080]

s302.从耦合器中获取耦合信号,经下变频和模数转换后,得到u=[u(1),u(2),...,u(n)]

t

作为功放输出信号对应的基带数字信号;

[0081]

s303.重构功放的输出信号,得到重构后的信号u

r

:

[0082][0083]

其中h=[h1,h2,...,h

l

]

t

,表示频段选择滤波器的系数,表示卷积;

[0084]

s304.采用间接学习架构,将重构后的功放输出信号u

r

拟合到输入信号x,即将步骤s103中数字预失真信号公式中的信号x替换为信号u

r

,信号z替换为信号x,进行模型拟合;此时预失真系数相对于模型是线性的,用如下式所最小二乘法求出预失真系数

[0085][0086]

其中矩阵u

r

是采用u

r

中的数据,根据数字预失真信号公式中基函数构建的数据矩阵。

[0087]

进一步地,所述步骤s4包括:

[0088]

利用求出的预失真系数a=[a

11

,a

12

,

…

,a

1q

,a

21

,a

22

,

…

,,a

2q

,

…

,a

kq

]

t

对数字预失真器模型中的预失真系数进行更新,并采用更新后的数字预失真器对后续输入的信源信号进行预失真处理。

[0089]

如图3所示,一种具有频率选择特性的数字预失真校正装置,包括:

[0090]

基带信源,用于提供信源信号;

[0091]

数字预失真器构建模块,用于构建具有频率选择特性的数字预失真器模型,并利用数字预失真器模型对信源信号进行处理,得到数字预失真信号;

[0092]

前置处理模块,用于对数字预失真信号进行数模转换和上变频处理后传输给功放pa;

[0093]

功放pa,用于对接收到的信号进行放大,并将放大后的信号通过耦合器传输给发射天线进行发射;

[0094]

耦合处理模块,用于从耦合器中获取耦合信号,并进行系变频和模数模数转换;

[0095]

预失真系数提取模块,用于抓取数字预失真器模型输出的信号数据和耦合处理模块输出的信号数据,并据此进行预失真系数提取,利用提取的系数

[0096]

其中,所述前置处理模块包括dac模块和上变频混频器,所述dac模块的输入端接收数字预失真器模型输出的数字预失真信号,dac模块的输出端与上变频混频器连接,上变频混频器的输出端与所述功放pa连接。

[0097]

其中,所述耦合处理模块包括下变频混频器和adc模块,所述下变频混频器的输入端与所述耦合器连接,下变频混频器的输出端与adc模块连接,所述adc模块的输出端与预失真系数提取模块连接。

[0098]

所述数字预失真校正装置还包括本振源,所述本振源分别与上变频混频器和下变频混频器连接,用于为上变频混频器和下变频混频器提供本振信号。

[0099]

在本技术的实施例中,通过设计不同的滤波器系数h,实现不同的dpd线性化效果。特别的,滤波器的通带频率范围就是dpd线性化的频段。

[0100]

当滤波器是一个截止频率为f1的高通滤波器时,本发明中的dpd只抑制频率范围在

‑

f1~f1之外的非线性失真。当滤波器是一个截止频率为f1的低通滤波器时,本发明中的dpd只抑制频率范围在

‑

f1~f1之内的非线性失真。当滤波器是一个通带为f1~f2的带通滤波器时,本发明中的dpd只抑制频率范围在f1~f2之内的非线性失真。

[0101]

当我们可以用下式构造滤波器系数:

[0102]

h=h1 αh2[0103]

其中h1是截止频率为f1的高通滤波器,h2是截止频率为f1的低通滤波器,α是0到1之前的一个数。所示的滤波器将完全的抑制频率范围在

‑

f1~f1之外的非线性失真,部分的抑制频率范围在

‑

f1~f1之内的非线性失真(抑制程度由α决定,α越大,抑制程度越大,当为1时,表示完全的抑制频率范围在

‑

f1~f1之内的非线性失真)。

[0104]

上述说明示出并描述了本发明的一个优选实施例,但如前所述,应当理解本发明并非局限于本文所披露的形式,不应看作是对其他实施例的排除,而可用于各种其他组合、修改和环境,并能够在本文所述发明构想范围内,通过上述教导或相关领域的技术或知识进行改动。而本领域人员所进行的改动和变化不脱离本发明的精神和范围,则都应在本发明所附权利要求的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。