经由电力线的数据传输

技术实现要素:

1.本说明书的各个方面提供一种电路。在一些示例中,该电路包括被配置为输出usb格式的双线数据的通用串行总线(usb)设备。该电路还包括嵌入式usb(eusb2)中继器,该eusb2中继器耦合到usb设备并被配置为将usb格式的双线数据转换为eusb2格式的双线数据。该电路还包括eusb2至电力线(e2pwr)中继器,该e2pwr中继器耦合到eusb2中继器并被配置为将双线数据编码成单个传输信号。

2.本说明书的其他方面提供一种系统。在一些示例中,该系统包括设备和外围设备。该设备包含被配置为传送usb格式的双线数据的usb主机设备。该设备还包含eusb中继器,该eusb中继器耦合到usb设备并被配置为在usb格式和eusb2格式之间转换双线数据。该设备还包含e2pwr中继器,该e2pwr中继器耦合到eusb2中继器并被配置为将双线数据编码成单个传输信号。该外围设备包含第二e2pwr中继器,该第二e2pwr中继器被配置为接收单个传输信号并解码单个传输信号以恢复eusb2格式的双线数据。

3.本说明书的其他方面提供一种方法。在一些示例中,该方法包括接收eusb格式的双线数据。该方法还包括将双线数据编码成单个信号。该单个信号包含对应于双线数据的第一状态变化的第一符号和对应于双线数据的第二状态变化的第二符号。

附图说明

4.对于各种示例的详细描述,现在将参考附图,其中:

5.图1示出各种示例中的说明性通信系统的框图;

6.图2示出各种示例中的说明性编码器的示意图;

7.图3示出各种示例中的说明性解码器的示意图;

8.图4示出各种示例中的说明性时序图;以及

9.图5示出各种示例中的说明性方法的流程图。

具体实施方式

10.通用串行总线(usb)是建立用于互连布线、连接器和通信协议的规范的标准。如本文所述,usb是指usb规范的任何版本,包括任何修订或补充,由usb实施者论坛(usb if)或者替代和/或协助usb if监督usb规范的任何合适机构所认证,无论是现在存在的还是以后开发的。在一些示例中,usb涵盖usb 2.0规范、usb 3.0规范、usb 4.0规范或其任何衍生规范中的任何一个或多个,诸如上述规范的修订版本或“.x”变体。此外,传统usb指的是usb 2.x。在一些示例中,嵌入式usb(eusb)指的是eusb2。

11.开始时,usb主要用于指定个人计算机和外围设备之间的连接和通信的标准的实施方式。然而,随着usb标准的采用范围的扩大,并且随着对usb标准的支持在计算设备中的实施方式已经普及,已经做出努力来扩展和扩大usb的适用性。例如,虽然最初建立的是个人计算机和外围设备之间的通信规范,但usb已扩展到外围设备之间、个人计算机之间以及其他用例之间的通信。此外,usb已发展成为一种高效和高性能的通信协议,其适用于意想

不到的应用,诸如汽车中的部件之间的通信等。由于usb的这种广泛实施和使用,正在进一步努力利用usb作为个体子系统或电路(例如,片上系统(soc))之间的通信协议。此类实施方式有时被称为eusb2。在实施eusb2时面临新的挑战。例如,在电路级,计算设备通常在不同于常规usb的电压水平下运行,从而为eusb2和传统usb系统之间的直接通信造成障碍。为了缓解这一障碍,eusb2中继器作为eusb2和传统usb系统之间的桥接器或非线性再驱动器进行工作,或者反之亦然,以在传统usb信令电压电平(通常约为3.3伏(v))和电路级的eusb2信令电压电平(例如,硅适当电压)(诸如约1.0v、1.2v、1.4v或小于3.3v的任何其他适当值)之间进行转换。

12.在一些示例中,usb和/或eusb2系统中的信令线是差分和双向通信线。在一些示例中,通信线是半双工通信线。在高速操作中,usb系统中至少有一些信令线是差分的。在其他示例中,诸如在全速和低速操作中,信令线不是差分的,而是独立切换的。无论是否差分,根据usb协议在其上发生信令的信令线在本文中都被称为d 和d

‑

。无论是否差分,根据eusb2协议在其上发生信令的信令线在本文中都被称为ed 和ed

‑

。此外,在一些示例中,经由ed 和ed

‑

传送的数据被称为双线数据。类似地,在一些示例中,经由d 和d

‑

传送的数据被称为双线数据。在一些应用中,在进行通信的设备之间缺少双通信线的同时具有usb和/或eusb2的数据通信能力是有利的、有益的或可能是合乎期望的。例如,保留usb和/或eusb2的双线数据信令,但经由单个导体或传输线来传输该双线数据。在一些示例中,减少耦合根据usb和/或eusb2进行通信的设备的导体的数目将降低在设备中实施usb的成本。在一些示例中,例如在上面提到的汽车示例中,减少导体的数目进一步具有减轻重量的累积效应。这种重量的降低有助于实现进一步的系统改进,这些改进源于usb和/或eusb2设备通过单个导体执行双线数据信令的能力。在一些示例中,将双线数据调制到耦合usb和/或eusb2设备的电力线上,使得仅需要一个导体而不是多个导体在usb和/或eusb2设备之间传输双线数据。

13.本说明书的一些方面提供了通过将第一设备耦合到第二设备的单线来传输双线数据。在一些示例中,单线是将第一设备耦合到第二设备的唯一导体。在一些示例中,单线是在第一设备和第二设备之间传输电压的电力线。通过调制经由第一设备和第二设备之间的单线传输的信号,双线数据经由电力线在第一设备和第二设备之间传送。在一些示例中,根据通信标准(诸如usb标准)传输调制信号。例如,某些通信标准包括用于被认为符合通信标准的传输数据的时序、抖动或其他要求。在一些示例中,根据描述经由单线传输的调制信号满足那些时序要求。

14.在一些示例中,根据接收到的双线数据调制单线。例如,单线被调制为包括单个脉冲以切换/拴系(toggle)一种类型的数据位,并且包括两个脉冲以切换另一种类型的数据位。作为说明书的一种实施方式的更具体示例,单个脉冲指示ed 的状态变化(例如上升沿或下降沿),而两个脉冲指示ed

‑

的状态变化(例如上升沿或下降沿)。类似地,在其他示例中,单线被调制为包括任何其他数目的脉冲以切换另一类型的数据位。在又一其它示例中,除脉冲之外的其他波形类型(例如,方波)也用于将双线数据调制到单线上。例如,在一些示例中,使用正弦波将双线数据调制到单线上。在至少一些实施方式中,在将双线数据调制到单线上之后,将附加数据调制到单线上。例如,在一些实施方式中,在将双线数据调制到单线上之后,将与通用异步接收器/发送器(uart)通信兼容的数据调制到单线上。

15.在一些示例中,单线是第一设备和第二设备之间的半双工通信线。在至少一些实

施方式中,第一设备和第二设备中的每一个包括或被配置为耦合到包含编码器和解码器的中继器。编码器接收ed 和ed

‑

并将ed 和ed

‑

编码到电力线上以作为调制信号。解码器接收调制或编码信号和时钟信号,并且对调制信号进行解码,以逐位重建ed 和ed

‑

。在一些示例中,编码器和解码器各自包括多个逻辑电路,诸如能够执行逻辑操作的电路和/或d触发器。

16.现在转到图1,其示出说明性通信系统100的框图。在一些示例中,系统100表示usb系统。在一些示例中,系统100包括设备102,该设备102包括usb主机设备104、usb至eusb2中继器106和eusb2至电力线(e2pwr)中继器108。系统100还包括设备110,该设备110至少包括e2pwr中继器112和处理器114。在一些示例中,设备110是在根据eusb2指定的信号电平下操作的设备。在其他示例中,设备110接收具有根据eusb2指定的电平的信号,并且将这些信号转换为其他信号电平,诸如由usb或其他通信协议指定的信号电平。通常,系统100示出了实施根据usb协议进行通信的设备的任何系统。在一些示例中,如本文别处所述,usb主机设备104是传统usb设备。在一些示例中,eusb2中继器106或e2pwr中继器108中的一个或两个在设备102外部实施,并且被配置为通过适当的接口(例如,适于根据eusb2或usb协议执行通信的端口和插座)耦合到设备102。

17.eusb2中继器106至少经由e2pwr中继器108和e2pwr中继器112将usb主机设备104通信地耦合到设备110。在一些示例中,eusb2中继器106将适用于usb主机设备104的信号转换为符合eusb2规范的信号,反之亦然。例如,在一些实施方式中,在约0.8v至约1.4v的范围内执行符合eusb2的信令,诸如在e2pwr中继器108中。类似地,在一些实施方式中,usb主机设备104中的信令在约3.3v下执行。在一些示例中,eusb2中继器106作为位级(bit

‑

level)中继器进行操作,从usb主机设备104或e2pwr中继器108中的一个接收信号,并且转换信号以供usb主机设备104或e2pwr中继器108中的另一个使用(例如,通过基于通信的方向上移或下移信号的电压电平)。

18.在一些示例中,tx 116即发射器116根据usb协议或标准传输数据作为d 和/或d

‑

,这些数据由eusb2中继器106接收。rx 118即接收器118根据usb协议或标准经由d 和/或d

‑

接收数据,这些数据由eusb2中继器106传输。usb主机设备104和eusb2中继器106以及在一些示例中的eusb2中继器106和e2pwr中继器108还通过总线电压信号线(vbus)和接地信号线(gnd)耦合在一起。eusb2中继器106从tx 116接收根据usb协议传输的d 和/或d

‑

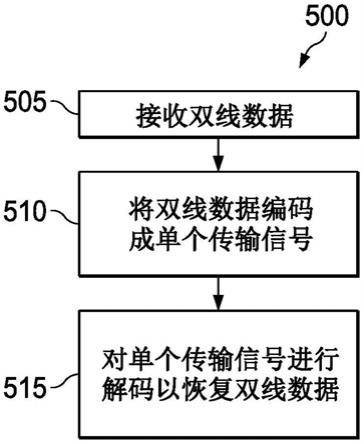

并将d 和/或d

‑

转换至eusb2协议作为ed 和/或ed

‑

,之后将eusb2协议中的ed 和/或ed

‑

传输到e2pwr中继器108。类似地,eusb2中继器106从e2pwr中继器108接收根据eusb2协议传输的ed 和/或ed

‑

并将ed 和/或ed

‑

转换至usb协议,之后将usb协议中的d 和/或d

‑

传输到rx 118。

19.e2pwr中继器108从eusb2中继器106接收ed 和/或ed

‑

,并且将ed 和/或ed

‑

调制到将设备102耦合到设备110的单个数据传输线120上。在一些示例中,传输线120是电力线,设备102或设备110中的一个通过该电力线从设备102或设备110中的另一个接收功率信号。在其他示例中,传输线120是耦合设备102和设备110的单个数据传输线,但在设备102和设备110之间不通过其传输功率。在一些示例中,尽管未示出,但是诸如vbus信号线的其他信号线也被耦合在设备102和设备110之间。在一些示例中,e2pwr中继器108从eusb2中继器106接收ed 和/或ed

‑

并将ed 和/或ed

‑

编码到传输线120上。例如,e2pwr中继器108调制传输线120上存在的信号以包括一个或多个脉冲或其他信号波形,从而指示ed 和/或ed

‑

的数据位中的状态变化(例如,上升沿或下降沿)。

20.在一些实施方式中,为了指示ed 的数据位的状态变化,e2pwr中继器108对传输线120进行编码以包括方波脉冲。在一些示例中,脉冲具有约10纳秒(ns)的脉冲宽度。在其他示例中,脉冲具有根据由系统100实施的通信协议或标准确定的任何适当时间量的脉冲宽度。在其他示例中,为了指示ed 的状态变化,e2pwr中继器108对传输线120进行编码以包括正弦波。类似地,在一些实施方式中,为了指示ed

‑

的状态变化,e2pwr中继器108对传输线120进行编码以包括两个方波脉冲。在一些示例中,每个脉冲的脉冲宽度约为10ns且脉冲对之间的间隔约为10ns。在其他示例中,每个脉冲具有由根据系统100实施的通信协议或标准确定的任何适当时间量的脉冲宽度。在一些示例中,脉冲具有相同的脉冲宽度,而在其他示例中,脉冲对中的一个与脉冲对中的另一个具有不同的脉冲宽度。在一些示例中,当至少一些脉冲具有不同的宽度时,每个状态变化被编码成具有唯一宽度的单个脉冲以指示不同的数据类型,而不是多个脉冲指示不同的数据类型。

21.在一些示例中,e2pwr中继器112经由传输线120接收由e2pwr中继器108生成的脉冲。e2pwr中继器112解码这些脉冲以重建符合eusb2信令协议的ed 和/或ed

‑

。在一些示例中,e2pwr中继器112进一步从处理器114接收时钟信号(clk)。在一些示例中,clk匹配在设备102中生成ed 和/或ed

‑

时使用的操作频率或不同的时钟信号。在一些示例中,clk使得e2pwr中继器112能够准确地检测和重构由e2pwr中继器108调制到传输线120上的ed 和/或ed

‑

。在一些示例中,在重构ed 和/或ed

‑

之后,e2pwr中继器112向处理器114或设备110的另一部件(未示出)提供ed 和/或ed

‑

。在一些示例中,另一部件是改变ed 和/或ed

‑

(诸如重新创建d 和/或d

‑

)的信号电平的中继器。

22.在一些示例中,处理器114进一步向e2pwr中继器112提供第二ed 和/或ed

‑

。e2pwr中继器112以基本上类似于上文关于e2pwr中继器108描述的方式将第二ed 和/或ed

‑

编码到传输线120上,并且在此不再重复。e2pwr中继器108然后以基本上类似于上文关于e2pwr中继器112描述的方式从传输线120上存在的脉冲中解码ed 和/或ed

‑

,并且在此不再重复。

23.现在转到图2,其示出说明性编码器200的示意图。在一些示例中,编码器200适合于在e2pwr中继器中实施,诸如图1的系统100的e2pwr中继器108和/或e2pwr中继器112。在一些示例中,编码器200被配置为接收ed 和/或ed

‑

并将ed 和/或ed

‑

编码成适合在单个传输线上传输的单个传输信号。

24.在一些示例中,通过用指示包含在单个传输信号中的各种数据类型的状态变化的符号对单个传输信号进行编码,编码器200将ed 和/或ed

‑

编码成单个传输信号。例如,第一符号指示第一数据类型的状态变化,诸如ed 的状态变化。第二符号指示第二数据类型的状态变化,诸如ed

‑

的状态变化。尽管在编码器200中未示出,但是在一些示例中,编码器200是可修改的,使得第三符号指示第三数据类型的状态变化。以这种方式,编码器200能够基于指示每种类型的数据的状态变化的唯一符号,用多种类型的数据对单个传输信号进行编码。

25.在一些示例中,编码器200包括多个逻辑结构,诸如and逻辑电路、or逻辑电路、反相电路、延迟电路和数据触发器(d触发器)。在一些示例中,延迟电路是能够在信号路径中引起(预定的和/或可编程的)延迟的任何电路或部件。许多类型的延迟电路适合于在本说明书中实施,并且这些合适的延迟电路的范围在此不受限制。例如,编码器200的至少一个实施方式包括or逻辑电路202、and逻辑电路204、and逻辑电路206、反相电路208、d触发器

210、d触发器212、d触发器214、反相电路216、d触发器218、or逻辑电路220和延迟电路224。编码器200还包括or逻辑电路226、or逻辑电路228、延迟电路230、or逻辑电路232、or逻辑电路234、反相电路236、d触发器238、d触发器240、d触发器242、or逻辑电路244、d触发器246、延迟电路248、or逻辑电路250、多路复用器252、d触发器254、or逻辑电路256和or逻辑电路258。

26.在编码器200的示例架构中,or逻辑电路202具有耦合到节点264的第一输入端子、耦合到节点266的第二输入端子和输出端子。and逻辑电路204具有耦合到节点260的输入端子、耦合到or逻辑电路202的输出端子的反相输入端子和耦合到节点274的输出端子。如本文所用,反相输入端子或反相输出端子是这样一个端子,在该端子所属的设备和该端子所耦合的节点之间,信号的值被反相。在一些示例中,反相输入端子或反相输出端子在功能上等效于在反相端子所耦合的节点和反相输入端子所属的设备的非反相输入端子之间耦合一个反相电路。and逻辑电路206具有耦合到节点264的反相输入端子、耦合到节点266的输入端子和耦合到节点276的输出端子。反相电路208具有耦合到节点274的输入端子并具有输出端子。d触发器210具有被配置为接收逻辑高值的数据输入端子、耦合到节点274的时钟输入端子、复位输入端子和输出端子。d触发器212具有被配置为接收逻辑高值的数据输入端子、耦合到反相电路208的输出端子的时钟输入端子、耦合到节点282的复位输入端子,以及输出端子。d触发器214具有被配置为接收逻辑高值的数据输入端子、耦合到节点276的时钟输入端子、耦合到节点283的复位输入端子,以及输出端子。反相电路216具有耦合到节点276的输入端子并具有输出端子。

27.d触发器218具有被配置为接收逻辑高值的数据输入端子、耦合到反相电路216的输出端子的时钟输入端子、耦合到节点283的复位输入端子,以及输出端子。or逻辑电路220具有耦合到d触发器210的输出端子的第一输入端子、耦合到d触发器212的输出端子的第二输入端子以及耦合到节点278的输出端子。延迟电路224具有耦合到节点278的输入端子并具有输出端子。or逻辑电路226具有耦合到节点262的第一输入端子、耦合到延迟电路224的输出端子的第二输入端子以及耦合到节点282的输出端子。or逻辑电路228具有耦合到d触发器214的输出端子的第一输入端子,耦合到d触发器218的输出端子的第二输入端子以及耦合到节点280的输出端子。

28.延迟电路230具有耦合到节点280的输入端子和耦合到节点281的输出端子。or逻辑电路232具有耦合到节点262的第一输入端子、耦合到节点281的第二输入端子以及耦合到节点283的输出端子。or逻辑电路234具有耦合到节点274的第一输入端子、耦合到节点276的第二输入端子,以及输出端子。反相电路236具有耦合到节点281的输入端子并具有输出端子。d触发器238具有被配置为接收逻辑高值的数据输入端子、耦合到节点276的反相时钟输入端子、耦合到节点286的复位输入端子,以及输出端子。d触发器240具有被配置为接收逻辑高值的数据输入端子、耦合到or逻辑电路234的输出端子的时钟输入端子、复位输入端子以及耦合到节点270的输出端子。d触发器242具有耦合到d触发器238的输出端子的数据输入端子、耦合到节点276的反相时钟输入端子、耦合到节点286的复位输入端子,以及输出端子。

29.or逻辑电路244具有耦合到节点278的第一输入端子、耦合到节点280的第二输入端子、耦合到节点284的第三输入端子以及耦合到节点272的输出端子。d触发器246具有被

配置为接收逻辑高值的数据输入端子、耦合到反相电路236的输出端子的时钟输入端子、复位输入端子以及耦合到节点284的输出端子。延迟电路248具有耦合到节点284的输入端子并且具有输出端子。or逻辑电路250具有耦合到节点262的第一输入端子、耦合到延迟电路248的输出端子的第二输入端子以及耦合到d触发器246的复位输入端子的输出端子。多路复用器252具有耦合到d触发器238的输出端子的第一输入端子、耦合到d触发器242的输出端子的第二输入端子、耦合到节点268的选择输入端子,以及输出端子。

30.d触发器254具有耦合到多路复用器252的输出端子的数据输入端子、耦合到节点272的反相时钟输入端子、耦合到节点262的复位输入端子,以及输出端子。or逻辑电路256具有耦合到d触发器254的输出端子的第一输入端子、耦合到节点262的第二输入端子以及耦合到d触发器240的复位输入端子的输出端子。or逻辑电路258具有耦合到节点270的反相输入端子、耦合到节点262的输入端子以及耦合到节点286的输出端子。

31.在一些示例中,编码器200被配置为在节点260处接收ed 并在节点266处接收ed

‑

。编码器200还被配置为在节点262处接收复位信号(reset),并且在节点264处接收编码器停用信号(encoder_disable)。编码器200还被配置为在节点268处接收多路复用器选择信号。在一些示例中,多路复用器选择信号指示编码器200(例如,在节点260和/或节点266处)正在接收的数据包的来源。在一些示例中,编码器200被配置为在节点272处输出编码信号(pulse)。编码器200还被配置为在节点270处输出解码器停用信号(decoder_disable)。在一些示例中,当编码器200对节点260和/或节点266处存在的数据进行编码以在节点272处生成pulse时,decoder_disable具有被配置为停用接收decoder_disable的解码器对pulse进行解码的值。

32.在编码器200的操作示例中,数据在节点260和/或节点266处被接收并被编码到节点272。在一些示例中,当encoder_disable被解除效果(de

‑

asserted)时,表明耦合到节点272的传输线上的数据没有被同样包含编码器200的设备中的解码器解码,则执行该编码。在一些示例中,对于在节点260处接收的每个上升沿和在节点260处接收的每个下降沿,编码器200切换pulse。在一些示例中,pulse包括脉冲宽度或持续时间约为10ns的方波脉冲,以指示在节点260处接收的上升沿或下降沿。类似地,对于在节点266处接收的每个上升沿和在节点266处接收的每个下降沿,编码器200进一步切换pulse。在一些示例中,该信号是两个方波脉冲,每个方波脉冲具有约为10ns的脉冲宽度或持续时间并且在时间上间隔约10ns,以指示在节点266处接收到的上升沿或下降沿。以这种方式,用在节点260和节点266处接收到的数据对pulse进行编码。

33.现在转到图3,其示出说明性解码器300的示意图。在一些示例中,解码器300适于在e2pwr中继器中实施,诸如图1的系统100的e2pwr中继器108和/或e2pwr中继器112。在一些示例中,解码器300被配置为在单个传输线上接收pulse,并且将pulse解码为ed 和/或ed

‑

。在一些示例中,解码器300被配置为在与例如图2的编码器200相同的设备中实施,使得编码器200和解码器300耦合在一起和/或耦合到相同的单个传输线。

34.在一些示例中,解码器300通过检测和解码指示包含在pulse中的各种数据类型的状态变化的符号,对pulse进行解码以生成ed 和/或ed

‑

。在一些示例中,这些符号如上文关于编码器200所述的那样。

35.在一些示例中,解码器300包括多个逻辑结构,诸如and逻辑电路、or逻辑电路、反

相or逻辑电路、反相电路和d触发器。例如,解码器300的至少一种实施方式包括and逻辑电路302、d触发器304、d触发器306、d触发器308、d触发器310、反相or逻辑电路312、d触发器314、d触发器316、d触发器318、d触发器320、反相or逻辑电路322、and逻辑电路324、反相or电路326、and逻辑电路328、or逻辑电路330、or逻辑电路332、or逻辑电路334、d触发器336、d触发器338、d触发器340、多路复用器342、d触发器344、or逻辑电路346以及or逻辑电路348。

36.在解码器300的示例架构中,and逻辑电路302具有耦合到节点350的反相输入端子、耦合到节点352的输入端子和耦合到节点366的输出端子。d触发器304具有数据输入端子、耦合到节点366的反相时钟输入端子、复位输入端子以及耦合到节点360的输出端子。d触发器306具有数据输入端子、耦合到节点366的时钟输入端子、耦合到节点380的复位输入端子以及耦合到节点370的输出端子。d触发器308具有耦合到节点370的数据输入端子、耦合到节点356的时钟输入端子、耦合到节点354的复位输入端子和耦合到节点372的输出端子。d触发器310具有数据输入端子、耦合到节点356的时钟输入端子、耦合到节点354的复位输入端子以及耦合到节点376的输出端子。反相or逻辑电路312具有耦合到节点360的第一输入端子、耦合到节点358的第二输入端子、耦合到节点384的第三输入端子以及耦合到d触发器304的数据输入端子的输出端子。

37.d触发器314具有耦合到节点370的数据输入端子、耦合到节点366的时钟输入端子、耦合到节点380的复位输入端子、耦合到d触发器310的数据输入端子的输出端子以及耦合到d触发器306的数据输入端子的反相输出端子。d触发器316具有耦合到节点372的数据输入端子、耦合到节点356的时钟输入端子、耦合到节点354的复位输入端子以及耦合到节点374的输出端子。d触发器318具有耦合到节点376的数据输入端子、耦合到节点356的时钟输入端子、耦合到节点354的复位输入端子以及耦合到节点378的输出端子。d触发器320具有耦合到节点370的数据输入端子、耦合到节点366的时钟输入端子、耦合到节点354的复位输入端子以及耦合到节点358的输出端子。

38.反相or逻辑电路322具有耦合到节点372的第一输入端子、耦合到节点374的第二输入端子,以及反相输出端子。and逻辑电路324具有耦合到反相or逻辑电路322的反相输出端子的第一输入端子、耦合到节点376的第二输入端子、耦合到节点378的第三输入端子,以及输出端子。反相or逻辑电路326具有耦合到节点376的第一输入端子、耦合到节点378的第二输入端子,以及反相输出端子。and逻辑电路328具有耦合到节点374的第一输入端子、耦合到节点372的第二输入端子、耦合到反相or逻辑电路326的反相输出端子的第三输入端子,以及输出端子。

39.or逻辑电路330具有耦合到节点358的第一输入端子、耦合到节点354的第二输入端子以及耦合到d触发器304的复位输入端子的输出端子。or逻辑电路332具有耦合到节点354的第一输入端子、耦合到and逻辑电路324的输出端子的第二输入端子以及耦合到and逻辑电路328的输出端子的第三输入端子。or逻辑电路332还具有耦合到d触发器320的复位输入端子、d触发器314的复位输入端子和d触发器306的复位输入端子的输出端子。or逻辑电路334具有耦合到节点360的第一输入端子、耦合到节点358的第二输入端子,以及输出端子。

40.d触发器336具有被配置为接收逻辑高值的数据输入端子、耦合到节点358的反相时钟输入端子、耦合到节点382的复位输入端子和耦合到节点384的输出端子。d触发器338

具有耦合到节点384的数据输入端子、耦合到节点358的反相时钟输入端子、耦合到节点382的复位输入端子,以及输出端子。d触发器340具有被配置为接收逻辑高值的数据输入端子、耦合到or逻辑电路334的输出端子的时钟输入端子、复位输入端子以及耦合到节点364的输出端子。多路复用器342具有耦合到节点384的第一输入端子、耦合到d触发器338的输出端子的第二输入端子、耦合到节点362的选择输入端子,以及输出端子。

41.d触发器344具有耦合到多路复用器342的输出端子的数据输入端子、耦合到节点366的反相时钟输入端子、耦合到节点354的复位输入端子,以及输出端子。or逻辑电路346具有耦合到d触发器344的输出端子的第一输入端子、耦合到节点354的第二输入端子以及耦合到d触发器340的复位输入端子的输出端子。or逻辑电路348具有耦合到节点354的输入端子、耦合到节点364的反相输入端子以及耦合到节点382的输出端子。

42.在一些示例中,解码器300被配置为在节点352处接收pulse,在节点358处输出ed ,并且在节点360处输出ed

‑

。解码器300还被配置为在节点354处接收reset,并且在节点350处接收decoder_disable。解码器300还被配置为在节点362处接收多路复用器选择信号。在一些示例中,多路复用器选择信号指示解码器300(例如,在节点352处)正在接收的数据包的源。解码器300还被配置为在节点364处输出encoder_disable。在一些示例中,当解码器300对pulse进行解码以生成ed 和/或ed

‑

时,encoder_disable具有被配置为停用接收encoder_disable的编码器对ed 和/或ed

‑

进行编码的值。

43.在一些示例中,解码器300的节点364耦合到编码器200的节点264。类似地,解码器300的节点350耦合到编码器200的节点270。类似地,在一些示例中,编码器200的节点352和节点272耦合在一起,编码器200的节点358和节点266耦合在一起,并且编码器200的节点360和节点260耦合在一起。

44.在解码器300的操作示例中,在节点352处接收pulse形式的编码数据。在一些示例中,当decoder_disable信号被解除效果时,表明耦合到节点352的传输线上的数据没有被也包含解码器300的设备中的编码器编码,则执行该解码。在一些示例中,解码器300检测在节点352处的pulse中存在的符号,并且处理这些符号以在节点358处生成ed 并且在节点360处生成ed

‑

。例如,对于在节点352处检测到的每个上升沿,在节点358或节点360处生成的信号中发生状态变化。例如,当在节点352处接收到包括两个上升沿的符号(例如,包括两个信号脉冲的符号)时,解码器300在节点358处切换信号。例如,当在节点352处接收到包括两个上升沿的符号时,如果节点358处的信号被解除效果,则解码器300响应于这种接收在节点358处激活该信号,反之亦然。类似地,当在节点352处接收到包括一个上升沿的符号(例如,包括一个信号脉冲的符号)时,解码器300在节点360处切换信号。例如,当在节点352处接收到包括一个上升沿的符号时,如果节点360处的信号被解除效果,则解码器300响应于这种接收在节点360处激活信号,反之亦然。以这种方式,在节点352处存在的信号被解码以在节点358和节点360处生成双线数据。

45.现在转到图4,其示出e2pwr数据传输的说明性时序图表400。图表400说明了存在于图1的系统100中的至少一些信号、由图2的编码器200生成的信号和/或由图3的解码器300生成的信号,并且在描述图表400时参考了图1、图2和/或图3中的至少一些。图表400包括信号reset(复位)、clk(时钟)、host_ed _out、host_ed

‑

_out、host_ed _in、host_ed

‑

_in、pulse(脉冲)、device_ed _out、device_ed

‑

_out、device_ed _in和device_ed

‑

_in。在

一些示例中,host_ed _out和host_ed

‑

_out是由eusb2中继器106输出到e2pwr中继器108的信号。因此,在一些示例中,host_ed _out和host_ed

‑

_out分别对应于图2的ed 和ed

‑

(当图2代表e2pwr中继器108的部件时)。在一些示例中,host_ed _in和host_ed

‑

_in是由e2pwr中继器108输出到eusb2中继器106的信号。因此,在一些示例中,host_ed _in和host_ed

‑

_in分别对应于图3的ed 和ed

‑

(当图2代表e2pwr中继器108的部件时)。在一些示例中,device_ed _in和device_ed

‑

_in是由e2pwr中继器112输出到处理器114的信号。因此,在一些示例中,device_ed _in和device_ed

‑

_in分别对应于图3的ed 和ed

‑

(当图3代表e2pwr中继器112的部件时)。在一些示例中,device_ed _out和device_ed

‑

_out是由处理器114输出到e2pwr中继器112的信号。因此,在一些示例中,device_ed _out和device_ed

‑

_out分别对应于图2的ed 和ed

‑

(当图2代表e2pwr中继器112的部件时)。在一些示例中,pulse(脉冲)是在e2pwr中继器108和e2pwr中继器112之间传输的信号,并且对应于图2和图3。

46.如图表400所示,对于host_ed _out和device_ed _out的每个上升沿或下降沿,使用宽度大约为10ns的信号脉冲对pulse进行编码。类似地,对于host_ed

‑

_out和device_ed

‑

_out的每个上升沿或下降沿,用各自宽度大约为10ns且间隔开约10ns的一对信号脉冲对pulse进行编码。类似地,当pulse包括根据host_ed _out或host_ed

‑

_out进行编码的脉冲时,通过对pulse进行解码而生成对应的信号device_ed _in和device_ed

‑

_in。当pulse包括根据device_ed _out或device_ed

‑

_out进行编码的脉冲时,通过对pulse进行解码而生成对应的信号host_ed _in和host_ed

‑

_in。

47.现在转到图5,其示出说明性方法500的流程图。在一些示例中,方法500是usb系统中的数据传输的方法。在一些示例中,方法500由图1的系统100实施。此外,在一些示例中,方法500的至少一部分由图2的编码器200和/或图3的解码器300实施。

48.在操作505处,接收双线数据。在一些示例中,双线数据被接收为ed 和ed

‑

。在其他示例中,双线数据是差分数据。

49.在操作510处,将双线数据编码成单个传输信号。在一些示例中,通过在单个传输信号上生成多个脉冲来将双线数据编码成单个传输信号。在一些示例中,每组脉冲被称为符号(symbol)。例如,对于双线数据的第一分量中的上升沿,用一个信号脉冲对单个传输线进行编码。类似地,对于双线数据的第一分量中的下降沿,用另一信号脉冲对单个传输线进行编码。在一些示例中,每个信号脉冲的持续时间约为10ns。对于双线数据的第二分量中的上升沿,用一对脉冲对单个传输线进行编码。类似地,对于双线数据的第二分量中的下降沿,用另一对信号脉冲对单个传输线进行编码。在一些示例中,每个信号脉冲的持续时间约为10ns,并且该对信号脉冲被间隔开约10ns。

50.在操作515处,对单个传输信号进行解码以恢复双线数据。在一些示例中,单个传输信号中的每个符号对应于双线数据的分量中的状态变化。例如,对于包括两个信号脉冲的符号,单个传输信号被解码以切换双线数据的一个分量中的信号。类似地,对于包括一个信号脉冲的符号,单个传输信号被解码以切换双线数据的另一分量中的信号。

51.在一些示例中,操作505和操作510由一个设备执行,而操作515由另一个设备执行。例如,在一些实施方式中,在将数据传输到e2pwr中继器112时由e2pwr中继器108执行操作505和操作510,并且e2pwr中继器112在从e2pwr中继器108接收数据后执行操作515。类似地,在一些实施方式中,在将数据传输到e2pwr中继器108时由e2pwr中继器112执行操作505

和操作510,并且e2pwr中继器108在从e2pwr中继器112接收数据后执行操作515。此外,尽管参考信号脉冲来描述方法500,但是在其他实施方式中,可以使用其他类型的信号。例如,在一些实施方式中,根据多个正弦波将双线数据编码成单个传输信号。

52.尽管已经描述并用参考数字标记了方法300的操作,但是在各种示例中,方法300包括本文未叙述的附加操作。在一些示例中,本文叙述的任何一个或多个操作包括一个或多个子操作(例如,中间比较、逻辑操作、诸如经由多路复用器的输出选择、格式转换、确定等)。在一些示例中,本文叙述的任何一个或多个操作被省略。在一些示例中,本文叙述的任何一个或多个操作以不同于在此呈现的顺序执行(例如,以相反的顺序、基本上同时、重叠等)。这些备选方案中的每一个均在本说明书的范围内。

53.在上述讨论中,术语“包括”和“包含”以开放式方式使用,并且意指“包括但不限于

……”

。术语“耦合”在整个说明书中使用。该术语可涵盖使得功能关系与说明书的描述一致的连接件、通信或信号路径。例如,如果设备a生成信号以控制设备b执行动作,则在第一示例中,设备a耦合到设备b,或者,在第二示例中,如果中间部件c没有实质性地改变设备a和设备b之间的功能关系,使得设备b经由设备a生成的控制信号由设备a控制,则设备a通过中间部件c耦合到设备b。“被配置为”执行某一任务或功能的设备可由制造商在制造时配置(例如,编程和/或硬接线)以执行该功能,和/或可由用户在制造后配置(或可重新配置)以执行该功能和/或其他附加或替代功能。配置可通过设备的固件和/或软件编程,通过设备的硬件部件和互连的构造和/或布局或者它们的组合。此外,被称为包括某些部件的电路或设备可以改为被配置为耦合到那些部件以形成所描述的电路或设备。例如,被描述为包括一个或多个半导体元件(诸如晶体管)、一个或多个无源元件(诸如电阻器、电容器和/或电感器)和/或一个或多个源(诸如电压源和/或电流源)的结构可以改为仅包括单个物理设备(例如,半导体管芯和/或集成电路(ic)封装件)内的半导体元件,并且可被配置为耦合到至少一些无源元件和/或源,以便例如由最终用户和/或第三方在制造时或制造后形成所描述的结构。

54.尽管本文将某些部件描述为特定工艺技术(例如,场效应晶体管(fet)、金属氧化物半导体fet(mosfet)、n型、p型等),但这些部件可被替换为其他工艺技术的部件(例如,用双极结晶体管(bjt)替换fet和/或mosfet),用p型替换n型,反之亦然,等等),并且重新配置包括被替换部件的电路,以提供至少部分类似于部件替换之前可用的功能的期望功能。除非另有说明,否则图示为电阻器的部件通常代表串联和/或并联的任何一个或多个元件,以提供由图示电阻器表示的阻抗量。此外,短语“接地电压电势”包括底盘接地、大地接地、浮动接地、虚拟接地、数字接地、公共接地和/或适用于或适合于说明书教导的任何其他形式的接地连接。除非另有说明,数值前的“约(about)”、“大约(approximately)”或“基本上(substantially)”是指所述值 /

‑

10%。

55.在权利要求的范围内,对所描述的实施例进行修改是可能的,并且其他实施例也是可能的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。