一种基于uc1843的可编程恒流源系统

技术领域

1.本发明属于可编程恒流源技术领域,尤其涉及一种基于uc1843的可编程恒流源系统。

背景技术:

2.可编程恒流源是指:根据基准电流信号线性调整输出电流幅值。目前,常用的恒流源多为线性工作模式,效率低。在可编程恒流源中多采用微控制器的编程方法实现直流恒流源的产生,电路复杂,可靠性不高。

技术实现要素:

3.本发明的技术解决问题:克服现有技术的不足,提供一种基于uc1843的可编程恒流源系统,解决了现有编程恒流源效率低、线路复杂的问题。

4.为了解决上述技术问题,本发明公开了一种基于uc1843的可编程恒流源系统,包括:

5.基准信号调理电路,用于对基准电流信号进行调理,输出与基准电流信号线性关系的第一信号;

6.uc1843控制电路,用于接收基准信号调理电路输出的第一信号和输出电流采样电路输出的第二信号;根据第一信号和第二信号进行逻辑处理,输出脉宽调制信号;

7.恒流源主电路,用于接收uc1843控制电路输出的脉宽调制信号,根据脉宽调制信号对输入电压进行隔离变换,输出恒定电流;

8.输出电流采样电路,用于对恒流源主电路输出的恒定电流进行采样、调理,输出与恒定电流线性关系的第二信号。

9.在上述基于uc1843的可编程恒流源系统中,uc1843控制电路,包括:控制芯片uc1843、电阻r5、电阻r6、电阻r7、电容c5、电容c6、电容c7和电容c8;其中,控制芯片uc1843上设置有vref端、vcc端、rt端、out端、vfb端、cs端、comp端、pgnd端和gnd端;

10.控制芯片uc1843的pgnd端和gnd端接地;

11.电容c7的两端分别接控制芯片uc1843的vfb端和comp端;

12.电容c8和电阻r7串联后与电容c7并联;

13.电阻r6的两端分别接控制芯片uc1843的vref端和rt端;

14.电容c6的两端分别接控制芯片uc1843的rt端和地;

15.电容c5的两端分别接控制芯片uc1843的cs端和地;

16.电阻r5的一端接控制芯片uc1843的out端。

17.在上述基于uc1843的可编程恒流源系统中,恒流源主电路,包括:变压器t2、mos管v1、电容c1、二极管d1;其中,变压器t2设置有四个引脚;

18.mos管v1的漏极连接变压器t2的第二引脚;

19.二极管d1的阳极接变压器t2的第三引脚,二极管d1的阴极连接到电容c1的一端,

电容c1的另一端连接变压器t2的第四引脚。

20.在上述基于uc1843的可编程恒流源系统中,输出电流采样电路,包括:电阻r1、电阻r16、电阻r17、电阻r18、电阻r19、运放q3和电阻r8;

21.电阻r1的一端串联电阻r16后接运放q3的反向输入端,电阻r1的另一端串联电阻r18后接运放q3的正向输入端;

22.电阻r8的两端分别接运放q3的输出端和控制芯片uc1843的vfb端;

23.电阻r17的两端分别接电阻r16和电阻r8;

24.电阻r19的两端分别接电阻r18和地。

25.在上述基于uc1843的可编程恒流源系统中,基准信号调理电路,包括:电阻r9、电阻r10、电阻r11、电阻r12、电阻r13、电阻r14和运放q4;

26.电阻r9的两端分别接控制芯片uc1843的vfb端和地;

27.电阻r10的两端分别接运放q4的输出端和控制芯片uc1843的vfb端;

28.电阻r11的两端分别接运放q4的反向输入端和运放q4的输出端;

29.电阻r12的两端分别接基准电流信号v_zl和运放q4的反向输入端;

30.电阻r13的两端分别接控制芯片uc1843的vref端和接运放q4的正向输入端;

31.电阻r14的两端分别接电阻r13和地。

32.在上述基于uc1843的可编程恒流源系统中,输出电流采样电路的电阻r1串联于恒流源主电路的输出地线中,实现对恒流源主电路输出的恒定电流的采样,并通过运放q3对采样信号进行放大处理,通过电阻r8将与恒定电流线性关系的第二信号输出至控制芯片uc1843的vfb端。

33.在上述基于uc1843的可编程恒流源系统中,控制芯片uc1843根据第一信号和第二信号逻辑处理后的反馈信号的幅值,输出脉宽调制信号pwm;其中,脉宽调制信号pwm用于恒流源主电路中mos管v1的驱动。

34.在上述基于uc1843的可编程恒流源系统中,反馈信号与脉宽调制信号pwm为负相关关系,输出电流采样电路通过反馈信号实现对恒流源主电路输出的恒定电流的幅值调整。

35.在上述基于uc1843的可编程恒流源系统中,反馈信号中包括:输出电流及基准电流信号的信息。

36.本发明具有以下优点:

37.(1)本发明具有开关工作模式控制输出电流恒定的特点,进而在处理热耗问题时,效率更高。

38.(2)本发明具有结构简单、元器件可获得性高的特点,因此成本低,可靠性高。

附图说明

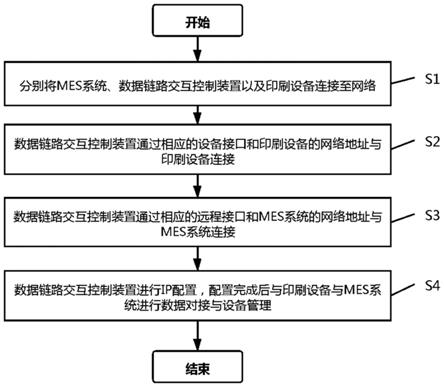

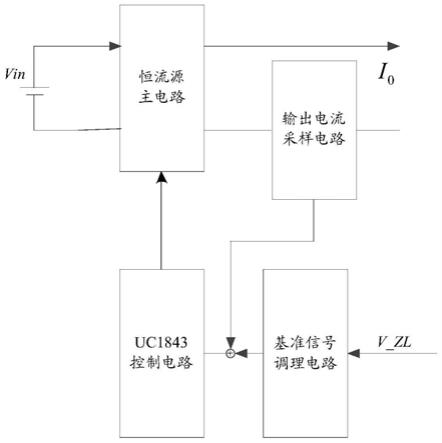

39.图1是本发明实施例中一种基于uc1843的可编程恒流源系统的结构框图;

40.图2是本发明实施例中一种基准信号调理电路的电路结构示意图;

41.图3是本发明实施例中一种uc1843控制电路的电路结构示意图;

42.图4是本发明实施例中一种恒流源主电路的电路结构示意图;

43.图5是本发明实施例中一种输出电流采样电路的电路结构示意图。

具体实施方式

44.为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明公开的实施方式作进一步详细描述。

45.如图1,在本实施例中,该基于uc1843的可编程恒流源系统,包括:

46.基准信号调理电路,用于对基准电流信号进行调理,输出与基准电流信号线性关系的第一信号。

47.在本实施例中,如图2,基准信号调理电路具体可以包括:电阻r9、电阻r10、电阻r11、电阻r12、电阻r13、电阻r14和运放q4。优选的,基准信号调理电路的具体电路连接关系如下:电阻r9的两端分别接控制芯片uc1843的vfb端和地;电阻r10的两端分别接运放q4的输出端和控制芯片uc1843的vfb端;电阻r11的两端分别接运放q4的反向输入端和运放q4的输出端;电阻r12的两端分别接基准电流信号v_zl和运放q4的反向输入端;电阻r13的两端分别接控制芯片uc1843的vref端和接运放q4的正向输入端;电阻r14的两端分别接电阻r13和地。

48.uc1843控制电路,用于接收基准信号调理电路输出的第一信号和输出电流采样电路输出的第二信号;根据第一信号和第二信号进行逻辑处理,输出脉宽调制信号。

49.在本实施例中,uc1843控制电路具体可以包括:控制芯片uc1843、电阻r5、电阻r6、电阻r7、电容c5、电容c6、电容c7和电容c8。其中,其中,控制芯片uc1843上设置有vref端、vcc端、rt端(振荡电阻端)、out端(输出端)、vfb端(反馈信号输入端)、cs端(采样电流输入端)、comp端、pgnd端和gnd端。如图3,uc1843控制电路的具体电路连接关系如下:控制芯片uc1843的pgnd端和gnd端接地;电容c7的两端分别接控制芯片uc1843的vfb端和comp端;电容c8和电阻r7串联后与电容c7并联;电阻r6的两端分别接控制芯片uc1843的vref端和rt端;电容c6的两端分别接控制芯片uc1843的rt端和地;电容c5的两端分别接控制芯片uc1843的cs端和地;电阻r5的一端接控制芯片uc1843的out端。

50.恒流源主电路,用于接收uc1843控制电路输出的脉宽调制信号,根据脉宽调制信号对输入电压进行隔离变换,输出恒定电流。

51.在本实施例中,如图4,恒流源主电路具体可以包括:变压器t2、mos管v1、电容c1、二极管d1。其中,变压器t2设置有四个引脚(图4中的引脚1~4)。优选的,恒流源主电路的具体电路连接关系如下:mos管v1的漏极连接变压器t2的第二引脚;二极管d1的阳极接变压器t2的第三引脚,二极管d1的阴极连接到电容c1的一端,电容c1的另一端连接变压器t2的第四引脚。

52.输出电流采样电路,用于对恒流源主电路输出的恒定电流进行采样、调理,输出与恒定电流线性关系的第二信号。

53.在本实施例中,如图5,输出电流采样电路具体可以包括:电阻r1、电阻r16、电阻r17、电阻r18、电阻r19、运放q3和电阻r8。优选的,输出电流采样电路的具体电路连接关系如下:电阻r1的一端串联电阻r16后接运放q3的反向输入端,电阻r1的另一端串联电阻r18后接运放q3的正向输入端;电阻r8的两端分别接运放q3的输出端和控制芯片uc1843的vfb端;电阻r17的两端分别接电阻r16和电阻r8;电阻r19的两端分别接电阻r18和地。

54.在本实施例中,

55.输出电流采样电路的电阻r1串联于恒流源主电路的输出地线中,实现对恒流源主

电路输出的恒定电流的采样,并通过运放q3放大后与基准电流信号进行调理(如反向、叠加常值、放大等处理)、相加处理后,通过电阻r8送入控制芯片uc1843的vfb端。进一步的,控制芯片uc1843根据第一信号和第二信号逻辑处理后的反馈信号(vfb端的信号)的幅值,输出脉宽调制信号pwm,通过脉宽调制信号pwm驱动恒流源主电路的mos管v1。其中,反馈信号与脉宽调制信号pwm为负相关关系,输出电流采样电路通过反馈信号实现对恒流源主电路输出的恒定电流的幅值调整,反馈信号中含有输出电流及基准电流信号的信息。

56.其中,该基于uc1843的可编程恒流源系统的工作原理如下:

57.在电路稳态工作时,uc1843控制电路的vfb端电压表达式为:

[0058][0059]

可见,i0可随v_zl的幅值大小进行线性调节。其中,vfb表式vfb端电压,v_zl表式基准电流信号电平,i0表式恒流源主电路输出的恒定电流,k表式输出的恒定电流的采样放大系数,vref表式vref端电压,r8~r14分别表式电阻r8~电阻r14的阻值。

[0060]

在本实施例中,uc1843控制电路的vfb端稳态工作时的电平为2.5v,如果vfb端电压低于2.5v,out端的pwm的占空比变大,vfb端电压高于2.5v时,控制芯片uc1843的out端的pwm的占空比变小。其中,当pwm的占空比变大时,mos管v1的导通时间变长,输出的恒定电流i0变大,根据公式(1)可知,vfb端电压变高,直到vfb端电压达到2.5v时电路进入稳定工作状态。当pwm的占空比变小时,mos管v1的导通时间变短,输出的恒定电流i0变小,根据公式(1)可知,vfb端电压变低,直到vfb端电压达到2.5v时电路进入稳定工作状态。

[0061]

优选的,将vfb=2.5代入公式1中可知:v_zl与i0是线性关系,实现了输出电流随指令电平变化而变化。进一步的,可设计电阻r8~r14的阻值,使下述公式(2)成立,进而实现v_zl与i0为线性比例关系:

[0062][0063]

本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

[0064]

本发明说明书中未作详细描述的内容属于本领域专业技术人员的公知技术。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。