1.本发明属于微电子和光电子技术领域,尤其涉及一种高速大面阵红外成像电路。

背景技术:

2.红外成像技术在军用领域已成为当今世界研究的热点。第三代红外探测器的问世,使得红外成像技术在军事应用上又上升了一个台阶。高帧频、大面阵探测器也应运而生。高帧频、大面阵红外探测器在导引头系统中的运用,使得导引头的性能有极大的提升。多阵列可提高产品的灵敏阈,使产品探测更远的目标;高帧频可使产品的目标信息迅速更新,使得导弹的预推轨迹更加准确,带宽增加,减少目标丢失,实现精确制导。

3.目前大多数红外成像电路只实现小面阵红外探测器的采集。对于高帧频、大面阵的探测器采集电路的设计还有待验证。

技术实现要素:

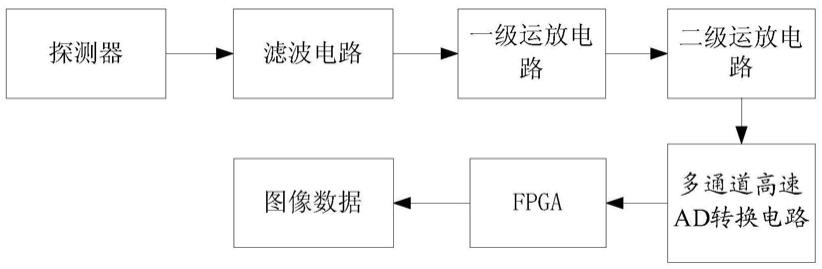

4.本发明解决的技术问题是:克服现有低速图像采样技术的不足,提供了一种高速大面阵红外成像电路,通过滤波电路完成探测器信号的高频滤波,一级运放电路将滤波后的信号进行跟随及偏置以提高探测器的带载能力,二级运放电路将一级运放处理的信号进行比例缩放及差分变换,以减少电路上的共模干扰,匹配高速采集模块的输入;多通道高速ad转换电路将差分信号模数转换后送至处理器fpga;处理器fpga采集多通道高速ad转换电路的数据,实现了信号的高速采集。

5.本发明目的通过以下技术方案予以实现:一种高速大面阵红外成像电路,包括:滤波电路、一级运放电路、二级运放电路、多通道高速ad转换电路和处理器fpga;其中,所述滤波电路将探测器输出信号进行滤波后得到滤波后的信号送给所述一级运放电路;所述一级运放电路将滤波后的信号进行直流偏置与隔离后得到偏置后的信号送给所述二级运放电路;所述二级运放电路将偏置后的信号进行比例缩放和差分变换后得到差分信号送给所述多通道高速ad转换电路;所述多通道高速ad转换电路将差分信号进行模数转换后送给处理器fpga。

6.上述高速大面阵红外成像电路中,所述滤波电路包括电容c100、电阻r1、电容c101、电阻r4、电容c102、电阻r11、电容c103和电阻r14;其中,电容c100的正极、电阻r1的正极均与一级运放电路的n1a的3脚连接,c100的负极、电阻r1的负极均与gnd_tcq连接;电容c101的正极、电阻r4的正极均与一级运放电路的n1c的10脚连接,c101的负极、电阻r4的负极均与gnd_tcq连接;电容c102的正极、电阻r11的正极均与一级运放电路的n2a的3脚连接,c102的负极、电阻r11的负极均与gnd_tcq连接;电容c103的正极、电阻r14的正极均与一级运放电路的n1a的3脚连接,c103的负极、电阻r14的负极均与gnd_tcq连接。

7.上述高速大面阵红外成像电路中,一级运放电路包含运放n1a、运放n1b、电阻r7、电阻r8、电容c1、电容c7、运放n1c、运放n1d、电阻r9、电阻r10、电容c8、运放n2a、运放n2b、电阻r17、电阻r18、电容c4、电容c9、运放n2c、运放n2d、电阻r19、电阻r20和电容c10;其中,运

放n1a的2脚接电阻r7的负极,运放n1a的4脚分别接电源vc、电容c1的正极,运放n1a的1脚分别接电阻r7的正极、电阻r29的正极,运放n1a的11脚分别接gnd_tcq、电容c7的负极;电容c1的负极接gnd_tcq;电容c7的正极分别接直流偏置vf、运放n1b的5脚;运放n1b的6脚接电阻r8的负极,运放n1b的7脚分别接r8的正极、电阻r30的正极;运放n1c的9脚接电阻r9的负极,运放n1c的8脚分别接电阻r9的正极、电阻r31的正极,电容c8正极分别接直流偏置vf、运放n1d的12脚,电容c8的负极接gnd_tcq,运放n1d的13脚接电阻r10的负极,运放n1d的14脚分别接电阻r10的正极、电阻r32的正极;运放n2a的2脚接电阻r17的负极,运放n2a的4脚分别接电源vc、电容c4的正极,运放n2a的1脚分别接电阻r17的正极、电阻r33的正极,运放n2a的11脚分别接gnd_tcq、电容c9的负极;电容c4的负极接gnd_tcq;电容c9的正极接直流偏置vf、运放n2b的5脚;运放n2b的6脚接电阻r18的负极,运放n2b的7脚分别接r18的正极、电阻r34的正极;运放n2c的9脚接电阻r19的负极,运放n2c的8脚分别接电阻r19的正极、电阻r35的正极,电容c10正极分别接直流偏置vf、运放n2d的12脚,电容c10的负极接gnd_tcq,运放n1d的13脚接电阻r20的负极,运放n1d的14脚分别接电阻r20的正极、电阻r36的正极。

8.上述高速大面阵红外成像电路中,二级运放电路包括差分运放电路n3、电阻r21、电阻r22、电阻r29、电阻r30、电容c11、电容c2、差分运放电路n4、电阻r23、电阻r24、电阻r31、电阻r32、电容c12、电容c3、差分运放电路n5、电阻r25、电阻r26、电阻r33、电阻r34、电容c13、电容c5、差分运放电路n6、电阻r27、电阻r28、电阻r35、电阻r36、电容c14和电容c6;其中,差分运放电路n3的1脚分别接电阻r30的负极、电阻r22的正极,差分运放电路n3的2脚分别接电容c11的正极、电阻r45的正极,差分运放电路n3的3脚分别接电源vc、电容c2的正极,差分运放电路n3的4脚分别接电阻r22的负极、电阻r61的正极,差分运放电路n3的5脚分别接电阻r21的负极、电阻r60的正极,差分运放电路n3的6脚接gnd_tcq,差分运放电路n3的7脚悬空,差分运放电路n3的8脚分别接电阻r29的负极、电阻r21的正极;电容c13的负极、电容c5的负极均接gnd_tcq;差分运放电路n4的1脚分别接电阻r32的负极、电阻r24的正极,差分运放电路n4的2脚分别接电容c12的正极、电阻r45的正极,差分运放电路n4的3脚分别接电源vc、电容c3的正极,差分运放电路n4的4脚分别接电阻r22的负极、电阻r62的正极,差分运放电路n4的5脚分别接电阻r23的负极、电阻r63的正极,差分运放电路n4的6脚接gnd_tcq,差分运放电路n4的7脚悬空,差分运放电路n4的8脚分别接电阻r31的负极、电阻r23的正极;电容c12的负极、电容c3的负极均接gnd_tcq;差分运放电路n5的1脚分别接电阻r34的负极、电阻r26的正极,差分运放电路n5的2脚分别接电容c13的正极、电阻r45的正极,差分运放电路n5的3脚分别接电源vc、电容c5的正极,差分运放电路n5的4脚分别接电阻r22的负极、电阻r65的正极,差分运放电路n5的5脚分别接电阻r25的负极、电阻r64的正极,差分运放电路n5的6脚接gnd_tcq,差分运放电路n5的7脚悬空,差分运放电路n5的8脚分别接电阻r33的负极、电阻r25的正极;电容c13的负极、电容c5的负极均接gnd_tcq;差分运放电路n6的1脚分别接电阻r35的负极、电阻r27的正极,差分运放电路n6的2脚分别接电容c14的正极、电阻r45的正极,差分运放电路n6的3脚分别接电源vc、电容c6的正极,差分运放电路n6的4脚分别接电阻r28的负极、电阻r66的正极,差分运放电路n6的5脚分别接电阻r27的负极、电阻r67的正极,差分运放电路n6的6脚接gnd_tcq,差分运放电路n6的7脚悬空,差分运放电路n6的8脚分别接电阻r35的负极、电阻r27的正极;电容c14的负极、电容c6的负极均接gnd_tcq。

9.上述高速大面阵红外成像电路中,多通道高速ad转换电路包括ad采样芯片n10、电阻r45、电阻r60、电阻r60、电阻r61、电阻r62、电阻r63、电阻r64、电阻r65、电阻r66、电阻r67、电阻r68、电容c15、电容c16、电容c17、电容c18、电容c19、电容c20,电容c21、电容c22、电容c23、电容c24、电容c25、电容c26、电容c27、电容c28、电容c29、电容c76、电容c77、电容c78、电容c19、电容c84、电容c84、电容c30、电容c31、电容c32;其中,ad采样芯片n10的0脚接agnd,ad采样芯片n10的1脚分别接电阻r66的负极、电容c79的负极,ad采样芯片n10的2脚分别接电阻c79的正极、电阻r67的负极,ad采样芯片n10的3脚、4脚、7脚、34脚、39脚、45脚、4脚均接1.8va,ad采样芯片n10的8脚、29脚均接1.8vad,ad采样芯片n10的5脚接电容c31的负极,ad采样芯片n10的6脚接电容c32的负极,ad采样芯片n10的27脚分别接电阻r49的负极、fpga芯片n7e的p16脚,ad采样芯片n10的28脚分别接电阻r49的正极、fpga芯片n7e的r16脚,ad采样芯片n10的26脚分别接电阻r50的负极、fpga芯片n7e的n16脚,ad采样芯片n10的25脚分别接电阻r50的正极、fpga芯片n7e的n15脚,ad采样芯片n10的24脚分别接电阻r51的负极、fpga芯片n7e的l13脚,ad采样芯片n10的23脚分别接电阻r51的正极、fpga芯片n7e的l16脚,ad采样芯片n10的22脚分别接电阻r52的负极、fpga芯片n7e的k16脚,ad采样芯片n10的21脚分别接电阻r52的正极、fpga芯片n7e的k15脚,ad采样芯片n10的20脚分别接电阻r58的负极、fpga芯片n7e的j14脚,ad采样芯片n10的19脚分别接电阻r58的正极、fpga芯片n7e的j12脚,ad采样芯片n10的16脚分别接电阻r53的负极、fpga芯片n7e的j16脚,ad采样芯片n10的15脚分别接电阻r53的正极、fpga芯片n7e的j15脚,ad采样芯片n10的14脚分别接电阻r54的负极、fpga芯片n7f的h16脚,ad采样芯片n10的13脚分别接电阻r54的正极、fpga芯片n7f的h15脚,ad采样芯片n10的12脚分别接电阻r55的负极、fpga芯片n7f的c16脚,ad采样芯片n10的11脚分别接电阻r55的正极、fpga芯片n7e的c15脚,ad采样芯片n10的10脚分别接电阻r56的负极、fpga芯片n7f的d16脚,ad采样芯片n10的9脚分别接电阻r56的正极、fpga芯片n7f的d15脚,ad采样芯片n10的18脚分别接电阻r49的负极、fpga芯片n7e的p16脚,ad采样芯片n10的17脚分别接电阻r49的正极、fpga芯片n7e的r16脚,ad采样芯片n10的30脚接fpga芯片n7c的r7脚,ad采样芯片n10的31脚接fpga芯片n7c的t6脚,ad采样芯片n10的32脚接fpga芯片n7c的r6脚,ad采样芯片n10的44脚接fpga芯片n7c的t7脚,ad采样芯片n10的43脚分别接电阻r45的负极、电容c30的正极,ad采样芯片n10的47脚分别接电阻r64的负极、电容c78的负极,ad采样芯片n10的48脚分别接电阻c78的正极、电阻r65的负极,ad采样芯片n10的37脚分别接电阻r62的负极、电容c77的负极,ad采样芯片n10的38脚分别接电阻c77的正极、电阻r63的负极,ad采样芯片n10的35脚分别接电阻r60的负极、电容c76的负极,ad采样芯片n10的36脚分别接电阻c76的正极、电阻r61的负极,ad采样芯片n10的41脚接agnd;电容c15的正极、电容c16的正极、电容c17的正极、电容c18的正极、电容c19的正极、电容c20的正极、电容c22的正极、电容c23的正极、电容c24的正极、电容c25的正极、电容c26的正极、电容c27的正极和电容c28的正极均接1.8va;电容c15的负极、电容c16的负极、电容c17的负极、电容c18的负极、电容c19的负极、电容c20的负极,、电容c21的负极、电容c22的负极、电容c23的负极、电容c24的负极、电容c25的负极、电容c26的负极、电容c27的负极、电容c28的负极、电容c29的负极和电容c30的负极均接agnd。

10.上述高速大面阵红外成像电路中,处理器fpga包括fpga芯片n7a、fpga芯片n7i、fpga芯片n7j、fpga芯片n7d、fpga芯片n7k、fpga芯片n7l、fpga芯片n7m、晶振n9、闪存n8、电

阻r37、电阻r38、电阻r39、电阻r40、电阻r41、电阻r42、电阻r49、电阻r50、电阻r51、电阻r52、电阻r53、电阻r54、电阻r55、电阻r56、电阻r57、电阻r5、电容c44、电容c45、电容c46、电容c47、电容c48、电容c49、电容c50、电容c51、电容c52、电容c53、电容c54、电容c55、电容c56、电容c57、电容c58、电容c59、电容c60、电容c61、电容c62、电容c63、电容c64、电容c65、电容c66、电容c67、电容c68、电容c69、电容c70、电容c71、电容c72、电容c73、电容c74、电容c75和电容c80;其中,fpga芯片n7a的c1脚接闪存n8的5脚,fpga芯片n7a的d2脚接闪存n8的1脚,fpga芯片n7a的h2脚接闪存n8的2脚,fpga芯片n7i的r9脚接晶振n9的3脚,fpga芯片n7j的h4脚接电阻r37的负极,fpga芯片n7j的j4脚接烧写接插件jtag的1脚,fpga芯片n7j的h3脚接电阻r38的负极,fpga芯片n7j的j5脚接电阻r39的负极,fpga芯片n7j的h13脚、h12脚均接2.5vd,fpga芯片n7j的g12脚、j3脚均接dgnd,fpga芯片n7j的h1脚接闪存n8的6脚,fpga芯片n7j的h14脚接电阻r40的负极,fpga芯片n7j的h5脚接电阻r41的负极,fpga芯片n7j的f4脚接电阻r42的负极,fpga芯片n7k的e3脚、g3脚、a16脚、c10脚、c13脚、a1脚、c4脚、c7脚均接3.3vd,fpga芯片n7k的k3脚、m3脚、p10脚、p13脚、t16脚、k14脚、m14脚、e14脚、g14脚、l5脚、f12脚、f5脚、l12脚均接2.5vd,fpga芯片n7k的p4脚、p7脚、t1脚均接1.8vd,fpga芯片n7k的f7脚、f11脚、g6脚、g7脚、g8脚、g9脚、g10脚、h6脚、h11脚、j6脚、k7脚、k11脚、n4脚、d13脚、n13脚均接1.2vd,fpga芯片n7l的h7脚、h8脚、h9脚、h10脚、j7脚、j8脚、j9脚、j10脚、f6脚、f10脚、j11脚、k8脚、b2脚、b15脚、c5脚、c12脚、d7脚、d10脚、e4脚、e13脚、g4脚、g13脚、k4脚、k13脚、m4脚、m13脚、n7脚、n10脚、p5脚、p12脚、r2脚、r15脚、m5脚、e12脚、e5脚、m12脚均接dgnd;晶振n9的1脚悬空,晶振n9的2脚分别接电容c80的负极、dgnd,晶振n9的4脚接2.5vd;闪存n8的3脚接3.3vd,闪存n8的4脚接dgnd,闪存n8的7脚、8脚均接3.3vd、电容c81的正极;电容c81的负极接dgnd,电阻r37、电阻r39的正极均接3.3vd,电阻r38的负极接dgnd,电阻r40接2.5vd,电阻r41、电阻r42均接3.3vd;电容c44、电容c45、电容c46、电容c47、电容c48、电容c49、电容c50、电容c51、电容c52、电容c53、电容c54、电容c55、电容c56、电容c57、电容c58、电容c59、电容c60、电容c61、电容c62、电容c63、电容c64、电容c65、电容c66、电容c67、电容c68、电容c69、电容c70、电容c71、电容c72、电容c73、电容c74、电容c75和电容c80的负极接dgnd;电容c44、电容c45、电容c46、电容c47、电容c48、电容c49、电容c50、电容c51、电容c52、电容c53、电容c54和电容c55的正极接1.2vd;电容c56、电容c57、电容c58、电容c59、电容c60、电容c61、电容c62、电容c63和电容c64接2.5vd;电容c65、电容c66和电容c67接1.8vd;电容c68、电容c69、电容c70、电容c71、电容c72、电容c73、电容c74和电容c75正极接3.3vd;fpga芯片n7m的l5脚、f12脚、f5脚、l12脚接2.5vd;n4脚、d13脚、d4脚、n13脚接1.2vd;m5脚、e12脚、e5脚、m12脚接dgnd。

11.上述高速大面阵红外成像电路中,运放n1a、运放n1b、运放n1c、运放n1d、运放n2a、运放n2b、运放n2c和运放n2d的型号均为opa4354。

12.上述高速大面阵红外成像电路中,差分运放电路n3、差分运放电路n4、差分运放电路n5和差分运放电路n6的型号均为lt1994。

13.上述高速大面阵红外成像电路中,fpga芯片n7a、、n7i、n7j、n7k、n7l、n7m型号为ep3c16u256i7。

14.上述高速大面阵红外成像电路中,一级运放n1、n2的型号为opa4354。

15.上述高速大面阵红外成像电路中,二级差运放n3、n4、n5、n6的型号为lt1994。

16.上述高速大面阵红外成像电路中,ad芯片n10的型号为ad9245。

17.上述高速大面阵红外成像电路中,fpga芯片n7a的型号为ep3c16u25617。

18.上述高速大面阵红外成像电路中,fpga芯片n7c的型号为ep3c16u25617。

19.上述高速大面阵红外成像电路中,fpga芯片n7i的型号为ep3c16u25617。

20.上述高速大面阵红外成像电路中,fpga芯片n7j的型号为ep3c16u25617。

21.上述高速大面阵红外成像电路中,fpga芯片n7k的型号为ep3c16u25617。

22.上述高速大面阵红外成像电路中,fpga芯片n7l的型号为ep3c16u25617。

23.上述高速大面阵红外成像电路中,fpga芯片n7m的型号为ep3c16u25617。

24.上述高速大面阵红外成像电路中,闪存n8的型号为epcq4asi8n。

25.上述高速大面阵红外成像电路中,晶振n9的型号为zpb28

‑

64mhz。

26.本发明与现有技术相比具有如下有益效果:

27.(1)本发明滤波器带宽可调,可根据不同的采样率设置滤波器的截至频率点,减少高频图像采集噪声。

28.(2)本发明将输入信号通过差分运放比例缩小,提高了信号的采样频率。

29.(3)本发明通过多通道数据采集,提高了图像采集速度。

30.(4)本发明提高产品的灵敏域。

31.(5)本发明可使产品的目标信息迅速更新,使得制导的预推轨迹更加准确,带宽增加,减少目标丢失,实现精确制导。

附图说明

32.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。而且在整个附图中,用相同的参考符号表示相同的部件。在附图中:

33.图1是本发明的高速大面阵红外成像电路的结构框图;

34.图2是本发明滤波电路的示意图;

35.图3(a)是本发明的一级运放电路的一个示意图;

36.图3(b)是本发明的一级运放电路的另一示意图;

37.图3(c)是本发明的一级运放电路的又一示意图;

38.图3(d)是本发明的一级运放电路的又一示意图;

39.图4(a)是本发明的二级运放电路的一个示意图;

40.图4(b)是本发明的二级运放电路的另一个示意图;

41.图4(c)是本发明的二级运放电路的又一个示意图;

42.图4(d)是本发明的二级运放电路的又一个示意图;

43.图5是本发明的多通道高速ad转换电路示意图;

44.图6是本发明的fpga配置引脚连接图;

45.图7是本发明的fpga电源引脚连接图;

46.图8是本发明去耦电容连接的示意图。

具体实施方式

47.下面将参照附图更详细地描述本公开的示例性实施例。虽然附图中显示了本公开的示例性实施例,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施例所限制。相反,提供这些实施例是为了能够更透彻地理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本发明。

48.图1是本发明的高速大面阵红外成像电路的结构框图。如图1所示,该高速大面阵红外成像电路包括:滤波电路、一级运放电路、二级运放电路、多通道高速ad转换电路、处理器fpga;其中,

49.处理器fpga完成探测器及多通道高速ad转换电路的配置,使探测器正常输出图像信号,多通道高速ad能够开始采集信号;滤波电路将原始图像信号低通滤波后发送至一级运放电路;一级运放电路将滤波后的信号进行跟随及偏置;二级运放电路将一级运放处理的信号进行比例缩放及差分变换;多通道高速ad转换电路采集差分信号并数字化送至处理器fpga;处理器fpga采集多通道高速ad转换电路的数据,打包后送至下一级系统。

50.如图2所示,滤波电路包含通道1的电容c100、电阻r1,通道2的电容c101、电阻r4,通道3的电容c102、电阻r11,通道4的电容c103、电阻r14;其中,

51.通道1的电容c100的正极、电阻r1的正极与一级运放电路的n1a的3脚连接,c100的负极、电阻r1的负极与gnd_tcq连接。

52.通道2的电容c101的正极、电阻r4的正极与一级运放电路的n1c的10脚连接,c101的负极、电阻r4的负极与gnd_tcq连接。

53.通道3的电容c102的正极、电阻r11的正极与一级运放电路的n2a的3脚连接,c102的负极、电阻r11的负极与gnd_tcq连接。

54.通道4的电容c103的正极、电阻r14的正极与一级运放电路的n1a的3脚连接,c103的负极、电阻r14的负极与gnd_tcq连接。

55.如图3(a)、图3(b)、图3(c)和图3(d)所示,一级运放电路包含:通道1的运放n1a、n1b、电阻r7、电阻r8、电容c1、c7,通道2的运放n1c、n1d、电阻r9、电阻r10、电容c8,通道3的运放n2a、n2b、电阻r17、电阻r18、电容c4、c9,通道4的运放n2c、n2d、电阻r19、电阻r20、电容c10;其中,

56.通道1的运放n1a的2脚接电阻r7的负极,4脚接电源vc、电容c1的正极,1脚接电阻r7的正极、电阻r29的正极,11脚接gnd_tcq、电容c7的负极;电容c1的负极接gnd_tcq;电容c7的正极接直流偏置vf、运放n1b的5脚;运放n1b的6脚接电阻r8的负极,7脚接r8的正极、电阻r30的正极。

57.通道2的运放n1c的9脚接电阻r9的负极,8脚接电阻r9的正极、电阻r31的正极,电容c8正极接直流偏置vf、运放n1d的12脚,电容c8的负极接gnd_tcq,运放n1d的13脚接电阻r10的负极,14脚接电阻r10的正极、电阻r32的正极。

58.通道3的运放n2a的2脚接电阻r17的负极,4脚接电源vc、电容c4的正极,1脚接电阻r17的正极、电阻r33的正极,11脚接gnd_tcq、电容c9的负极;电容c4的负极接gnd_tcq;电容c9的正极接直流偏置vf、运放n2b的5脚;运放n2b的6脚接电阻r18的负极,7脚接r18的正极、电阻r34的正极。

59.通道4的运放n2c的9脚接电阻r19的负极,8脚接电阻r19的正极、电阻r35的正极,电容c10正极接直流偏置vf、运放n2d的12脚,电容c10的负极接gnd_tcq,运放n1d的13脚接电阻r20的负极,14脚接电阻r20的正极、电阻r36的正极。

60.如图4(a)、图4(b)、图4(c)和图4(d)所示,二级运放电路包含于:通道1的差分运放电路n3,比例变换电阻r21、r22、r29、r30,电容c11、电容c2;通道2的差分运放电路n4,比例变换电阻r23、r24、r31、r32,电容c12、电容c3;通道3的差分运放电路n5,比例变换电阻r25、r26、r33、r34,电容c13、电容c5;通道4的差分运放电路n6,比例变换电阻r27、r28、r35、r36,电容c14、电容c6;其中,

61.通道1的差分运放n3的1脚接电阻r30的负极、电阻r22的正极,2脚接电容c11的正极、电阻r45的正极,3脚接电源vc、电容c2的正极,4脚接电阻r22的负极、电阻r61的正极,5脚接电阻r21的负极、电阻r60的正极,6脚接gnd_tcq,7脚悬空,8脚接电阻r29的负极、电阻r21的正极;电容c13的负极、电容c5的负极接gnd_tcq。

62.通道2的差分运放n4的1脚接电阻r32的负极、电阻r24的正极,2脚接电容c12的正极、电阻r45的正极,3脚接电源vc、电容c3的正极,4脚接电阻r22的负极、电阻r62的正极,5脚接电阻r23的负极、电阻r63的正极,6脚接gnd_tcq,7脚悬空,8脚接电阻r31的负极、电阻r23的正极;电容c12的负极、电容c3的负极接gnd_tcq。

63.通道3的差分运放n5的1脚接电阻r34的负极、电阻r26的正极,2脚接电容c13的正极、电阻r45的正极,3脚接电源vc、电容c5的正极,4脚接电阻r22的负极、电阻r65的正极,5脚接电阻r25的负极、电阻r64的正极,6脚接gnd_tcq,7脚悬空,8脚接电阻r33的负极、电阻r25的正极;电容c13的负极、电容c5的负极接gnd_tcq。

64.通道4的差分运放n6的1脚接电阻r35的负极、电阻r27的正极,2脚接电容c14的正极、电阻r45的正极,3脚接电源vc、电容c6的正极,4脚接电阻r28的负极、电阻r66的正极,5脚接电阻r27的负极、电阻r67的正极,6脚接gnd_tcq,7脚悬空,8脚接电阻r35的负极、电阻r27的正极;电容c14的负极、电容c6的负极接gnd_tcq。

65.如图5所示,多通道高速ad转换电路包含:ad采样芯片n10,电阻r45,电阻r60,电阻r60,电阻r61,电阻r62,电阻r63,电阻r64,电阻r65,电阻r66,电阻r67,电阻r68,电容c15,电容c16,电容c17,电容c18,电容c19,电容c20,电容c21,电容c22,电容c23,电容c24,电容c25,电容c26,电容c27,电容c28,电容c29,电容c76,电容c77,电容c78,电容c19,电容c84,电容c84,电容c30,电容c31,电容c32;其中,

66.ad采样芯片n10的0脚接agnd,1脚接电阻r66的负极、电容c79的负极,2脚接电阻c79的正极、电阻r67的负极,3脚、4脚、7脚、34脚、39脚、45脚、4脚接1.8va,8脚、29脚接1.8vad,5脚接电容c31的负极,6脚接电容c32的负极,27脚接电阻r49的负极、n7e的p16脚,28脚接电阻r49的正极、n7e的r16脚,26脚接电阻r50的负极、n7e的n16脚,25脚接电阻r50的正极、n7e的n15脚,24脚接电阻r51的负极、n7e的l13脚,23脚接电阻r51的正极、n7e的l16脚,22脚接电阻r52的负极、n7e的k16脚,21脚接电阻r52的正极、n7e的k15脚,20脚接电阻r58的负极、n7e的j14脚,19脚接电阻r58的正极、n7e的j12脚,16脚接电阻r53的负极、n7e的j16脚,15脚接电阻r53的正极、n7e的j15脚,14脚接电阻r54的负极、n7f的h16脚,13脚接电阻r54的正极、n7f的h15脚,12脚接电阻r55的负极、n7f的c16脚,11脚接电阻r55的正极、n7e的c15脚,10脚接电阻r56的负极、n7f的d16脚,9脚接电阻r56的正极、n7f的d15脚,18脚接电

阻r49的负极、n7e的p16脚,17脚接电阻r49的正极、n7e的r16脚,30脚接n7c的r7脚,31脚接n7c的t6脚,32脚接n7c的r6脚,44脚接n7c的t7脚,43脚接电阻r45的负极,电容c30的正极,47脚接电阻r64的负极、电容c78的负极,48脚接电阻c78的正极、电阻r65的负极,37脚接电阻r62的负极、电容c77的负极,38脚接电阻c77的正极、电阻r63的负极,35脚接电阻r60的负极、电容c76的负极,36脚接电阻c76的正极、电阻r61的负极,41脚接agnd;电容c15的正极,电容c16的正极,电容c17的正极,电容c18的正极,电容c19的正极,电容c20的正极,电容c22的正极,电容c23的正极,电容c24的正极,电容c25的正极,电容c26的正极,电容c27的正极,电容c28的正极接1.8va;电容c15的负极,电容c16的负极,电容c17的负极,电容c18的负极,电容c19的负极,电容c20的负极,电容c21的负极,电容c22的负极,电容c23的负极,电容c24的负极,电容c25的负极,电容c26的负极,电容c27的负极,电容c28的负极,电容c29的负极,电容c30的负极,接agnd。

67.如图6、图7和图8所示,处理器fpga包含fpga芯片n7,晶振n9,闪存n8,电阻r37,电阻r38,电阻r39,电阻r40,电阻r41,电阻r42,电阻r49,电阻r50,电阻r51,电阻r52,电阻r53,电阻r54,电阻r55,电阻r56,电阻r57,电阻r5,电容c44,电容c45,电容c46,电容c47,电容c48,电容c49,电容c50,电容c51,电容c52,电容c53,电容c54,电容c55,电容c56,电容c57,电容c58,电容c59,电容c60,电容c61,电容c62,电容c63,电容c64,电容c65,电容c66,电容c67,电容c68,电容c69,电容c70,电容c71,电容c72,电容c73,电容c74,电容c75,电容c80;其中,fpga芯片n7a的c1脚接闪存n8的5脚,d2脚接闪存n8的1脚,h2脚接闪存n8的2脚,n7i的r9脚接晶振n9的3脚,,n7j的h4脚接电阻r37的负极,j4脚接jtag的1脚,h3脚接电阻r38的负极,j5脚接电阻r39的负极,h13脚、h12脚接2.5vd,g12脚、j3脚接dgnd,h1脚接闪存n8的6脚,h14脚接电阻r40的负极,h5脚接电阻r41的负极,f4脚接电阻r42的负极,n7d的p14脚接电阻r69的正极,r14脚接电阻r70的正极,n7k的e3、g3、a16、c10、c13、a1、c4、c7脚接3.3vd,k3、m3、p10、p13、t16、k14、m14、e14、g14、l5、f12、f5、l12脚接2.5vd,p4、p7、t1脚接1.8vd,f7、f11、g6、g7、g8、g9、g10、h6、h11、j6、k7、k11、n4、d13、n13脚接1.2vd,n7lh7、h8、h9、h10、j7、j8、j9、j10、f6、f10、j11、k8、b2、b15、c5、c12、d7、d10、e4、e13、g4、g13、k4、k13、m4、m13、n7、n10、p5、p12、r2、r15、m5、e12、e5、m12脚接dgnd;n9的1脚悬空,2脚接电容c80的负极、dgnd,4脚接2.5vd;n8的3脚接3.3vd,4脚接dgnd,7脚、8脚接3.3vd、电容c81的正极;电容c81的负极接dgnd,电阻r37、r39的正极接3.3vd,电阻r38的负极接dgnd,电阻r40接2.5vd,电阻r41、r42接3.3vd;电容c44,电容c45,电容c46,电容c47,电容c48,电容c49,电容c50,电容c51,电容c52,电容c53,电容c54,电容c55,电容c56,电容c57,电容c58,电容c59,电容c60,电容c61,电容c62,电容c63,电容c64,电容c65,电容c66,电容c67,电容c68,电容c69,电容c70,电容c71,电容c72,电容c73,电容c74,电容c75,电容c80的负极接dgnd;电容c44,电容c45,电容c46,电容c47,电容c48,电容c49,电容c50,电容c51,电容c52,电容c53,电容c54,电容c55的正极接1.2vd;电容c56,电容c57,电容c58,电容c59,电容c60,电容c61,电容c62,电容c63,电容c64接2.5vd;电容c65,电容c66,电容c67接1.8vd;电容c68,电容c69,电容c70,电容c71,电容c72,电容c73,电容c74,电容c75正极接3.3vd。

68.一级运放n1、n2的型号为opa4354。二级差运放n3、n4、n5、n6的型号为lt1994。ad芯片n10的型号为ad9245。fpga芯片n7a的型号为ep3c16u25617。fpga芯片n7c的型号为ep3c16u25617。fpga芯片n7i的型号为ep3c16u25617。fpga芯片n7j的型号为ep3c16u25617。

fpga芯片n7k的型号为ep3c16u25617。fpga芯片n7l的型号为ep3c16u25617。fpga芯片n7m的型号为ep3c16u25617。闪存n8的型号为epcq4asi8n。晶振n9的型号为zpb28

‑

64mhz。

69.本发明滤波器带宽可调,可根据不同的采样率设置滤波器的截至频率点,减少高频图像采集噪声。本发明将输入信号通过差分运放比例缩小,提高了信号的采样频率。本发明通过通道数据采集,提高了图像采集速度。本发明提高产品的灵敏域。本发明可使产品的目标信息迅速更新,使得制导的预推轨迹更加准确,带宽增加,减少目标丢失,实现精确制导。

70.本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。