1.本技术案主张2020年4月16日申请的美国正式申请案第16/850,427号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

2.本公开涉及一种半导体存储器元件以及其制备方法。特别是涉及一种在多个导电特征之间具有气隙以降低电容偶合的半导体存储器元件。

背景技术:

3.半导体元件是广泛地使用在电子产业。半导体元件可具有相对小的尺寸、多功能特性及/或相对低的制造成本。半导体元件可归类为以下其中之一:存储逻辑数据的半导体存储器元件、处理逻辑数据的半导体逻辑元件,以及同时具有半导体存储元件的功能与半导体逻辑元件的功能的混合半导体元件。

4.相对高速与相对低电压的半导体元件可满足电子晶粒的所欲的特性(意即高速及/或低功耗),而电子元件包括半导体元件。半导体元件可相对地高度整合。半导体元件的可靠度可通过半导体元件的相对高度整合密度而降低。

5.上文的“先前技术”说明仅是提供背景技术,并未承认上文的“先前技术”说明揭示本公开的标的,不构成本公开的先前技术,且上文的“先前技术”的任何说明均不应作为本案的任一部分。

技术实现要素:

6.本公开的一实施例提供一种半导体存储器元件,包括一绝缘层,界定一第一主动区在一基底中;一第一掺杂区,位在该第一主动区中;一第一字元线,埋入在一第一沟槽中,该第一沟槽邻近该第一掺杂区设置;一高位面字元线接触点,位在该第一掺杂区上;以及一第一气隙,围绕该高位面位元线接触点设置;其中该第一字元线包括一下电极结构以及一上电极结构,该上电极结构位在该下电极结构上;以及其中该上电极结构包括一源极层、一导电层以及一功函数调整层,该源极层大致覆盖该第一沟槽的一侧壁,该导电层位在该源极层上,该功函数调整层设置在该源极层与该导电层之间。

7.在本公开的一些实施例中,该半导体存储器元件还包括:一第二字元线,埋入在一第二沟槽中,该第二沟槽位在该基底的一第二主动区中,该第二主动区与该第一主动区通过该绝缘层而相互分开设置;一第二掺杂区,位在邻近该第二字元线处;一低位面位元线,位在该第二掺杂区上;以及一第二气隙,位在邻近该低位面位元线处。

8.在本公开的一些实施例中,该半导体存储器元件还包括:一高位面位元线,位在该高位面位元线接触点上;以及一低位面位元线接触点,位在该低位面位元线与该第二主动区之间;其中该低位面位元线接触点的一高度是低于该高位面位元线接触点的一高度。

9.在本公开的一些实施例中,该低位面位元线的一宽度是大于该低位面位元线接触点的一宽度。

10.在本公开的一些实施例中,该高位面位元线的一宽度是大于该高位面位元线接触

点的一宽度。

11.在本公开的一些实施例中,该高位面位元线接触点的一高度是大致相同于该低位面位元线接触点与该低位面位元线的一结合高度。

12.在本公开的一些实施例中,该高位面位元线接触点的一上表面以及该低位面位元线的一上表面大致在相同的一位面。

13.在本公开的一些实施例中,该高位面位元线非对称地位在该高位面位元线接触点上。

14.在本公开的一些实施例中,该下电极结构的一功函数是高于该上电极结构的一功函数。

15.在本公开的一些实施例中,该功函数调整层保形地覆盖该源极层的一内侧壁。

16.在本公开的一些实施例中,该源极层延伸在该下电极结构与该导电层之间,以覆盖该下电极结构的一上表面。

17.本公开的另一实施例提供一种半导体存储器元件的制备方法,包括:形成一绝缘层以界定一第一主动区在一基底中;形成一第一掺杂区在该第一主动区中;形成一第一字元线以埋入在一第一沟槽中,该第一沟槽邻近该第一掺杂区设置;形成一高位面位元线接触点以位在该第一掺杂区上;以及形成一第一气隙以围绕该高位面位元线接触点;其中形成该第一字元线包括:形成一下电极结构以及一上电极结构,该上电极结构位在该下电极结构上;其中形成该上电极结构包括:形成一源极层以大致覆盖该第一沟槽的一侧壁;形成一导电层在该源极层上;以及形成一功函数调整层以位在该源极层与该导电层之间。

18.在本公开的一些实施例中,该半导体存储器元件的制备方法还包括:形成一第二掺杂区在该基底的一第二主动区中,该第二主动区与该第一主动区通过该绝缘层而分开设置;形成一第二字元线以埋入在一第二沟槽中,该第二沟槽邻近该第二掺杂区设置;形成一低位面位元线在该第二掺杂区上;以及形成一第二气隙以邻近该低位面位元线。

19.在本公开的一些实施例中,该半导体存储器元件的制备方法还包括:形成一高位面位元线在该高位面位元线接触点上;以及形成一低位面位元线接触点在该低位面位元线与该第二掺杂区之间;其中该低位面位元线接触点的一高度是小于该高位面位元线接触点的一高度。

20.在本公开的一些实施例中,该第一气隙与该第二气隙为一体成形,且该低位面位元线接触点、该低位面位元线以及该高位面位元线接触点为一体成形。

21.在本公开的一些实施例中,该高位面位元线接触点的一上表面以及该低位面位元线的一上表面大致位在相同位面。

22.在本公开的一些实施例中,该下电极结构的一功函数是高于该上电极结构的一功函数。

23.在本公开的一些实施例中,该功函数调整层保形地覆盖该源极层的一内侧壁。

24.在本公开的一些实施例中,该功函数调整层包含一金属或一金属氮化物,且其中该功函数调整元素包含镧(la)。

25.综上所述,该功函数调整层是具有一相对低的功函数,并设置在该上电极结构的外侧处,是可降低或最小化一栅极引发漏极漏电流(gate

‑

induced drain leakage,gidl),其是该字元线道所述掺杂区所产生。此外,该上电极结构的功函数可通过调整该功函数调

整层的一掺杂浓度进行调整。因此,可达到该上电极结构的一所欲的低功函数。

26.再者,该半导体存储器元件具有多个气隙,且所述导电特征是通过所述气隙而相互分开设置。因此,可降低在所述导电接触点之间的寄生电容。结果,可改善整体元件效能(意即减少功耗以及电阻

‑

电容(rc)延迟),且可提升该半导体元件的良率。

27.上文已相当广泛地概述本公开的技术特征及优点,而使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中具有通常知识者应了解,可相当容易地利用下文揭示的概念与特定实施例可作为修改或设计其它结构或制程而实现与本公开相同的目的。本公开所属技术领域中具有通常知识者亦应了解,这类等效建构无法脱离后附的权利要求所界定的本公开的精神和范围。

附图说明

28.参阅实施方式与权利要求合并考量图式时,可得以更全面了解本技术案的揭示内容,图式中相同的元件符号是指相同的元件。

29.图1为依据本公开一些实施例中一种具有气隙以降低在多个导电特征之间的电容耦合的半导体存储器结构的制备方法的流程示意图。

30.图2为依据本公开一些实施例在如图1所示的步骤s11中形成一绝缘层以界定多个主动区在一基底中的一中间阶段的剖视示意图。

31.图3到图4为依据本公开一些实施例在如图1所示的步骤s13中形成多个沟槽在该基底中的该主动区中的一中间阶段的剖视示意图。

32.图5为依据本公开一些实施例在如图1所示的步骤s15中形成一下电极结构以大致充填所述沟槽的一下部的一中间阶段的剖视示意图。

33.图6为依据本公开一些实施例在如图1所示的步骤s17中形成一源极层以及一第一扩散层在所述沟槽的一侧壁与一下表面上的一中间阶段的剖视示意图。

34.图7为依据本公开一些实施例在如图1所示的步骤s19中形成一功函数层,其是通过扩散功函数调整元素从该源极层到该第一扩散层的至少一部分的一中间阶段的剖视示意图。

35.图8为依据本公开一些实施例在如图1所示的步骤s21中形成一导电层在该第一扩散层上的一中间阶段的剖视示意图。

36.图9为依据本公开一些实施例形成多个字元线在所述沟槽中的一中间阶段的剖视示意图。

37.图10为依据本公开一些实施例形成一第二掺杂区在所述主动区中,而所述主动区是为在相互邻近的二字元线之间的一中间阶段的剖视示意图。

38.图11到图20为依据本公开一些实施例在如图1所示的步骤s23中形成一高位面位元线接触点、一低位面位元线接触点以及一低位面位元线在该基底上的一中间阶段的剖视示意图。

39.图21及图22为依据本公开一些实施例在如图1所示的步骤s25中形成多个气隙在该基底上的一中间阶段的剖视示意图。

40.图23及图24为依据本公开一些实施例在如图1所示的步骤s27中形成一高位面位

元线接触点以及一高位面位元线在该基底上的一中间阶段的剖视示意图。

41.图25为依据本公开一些实施例在如图1所示的步骤s29中形成多个导电栓塞在该基底上的一中间阶段的剖视示意图。

42.图26到图28为依据本公开一些实施例在如图1所示的步骤s31中形成多个电容结构自该基底上的一中间阶段的剖视示意图。

43.其中,附图标记说明如下:

44.100:半导体存储器结构

45.10:方法

46.101:基底

47.103:绝缘层

48.105:第一主动区

49.107:第二主动区

50.109a:第一掺杂区

51.109b:第二掺杂区

52.110:遮罩层

53.111:导电栓塞

54.113:电容结构

55.115:电容下电极

56.117:电容隔离层

57.119:电容上电极

58.121:电容沟槽

59.203:字元线隔离层

60.205:下电极结构

61.209:字元线沟槽

62.211:源极层

63.213:第一扩散层

64.215:功函数调整层

65.217:导电层

66.219:上电极结构

67.221:字元线

68.223:第一罩盖图案

69.252:导电层

70.301:高位面位元线

71.303:高位面位元线接触点

72.305:高位面位元线接触点

73.307:接触点开口

74.309:高位面位元线接触点开口

75.311:高位面位元线沟槽

76.313:高位面位元线接触点开口

77.401:低位面位元线

78.403:低位面位元线接触点

79.405:低位面位元线沟槽

80.407:低位面位元线接触点开口

81.501:第一间隙子层

82.503:第一间隙子

83.505:第二间隙子层

84.507:第二间隙子

85.509:衬垫层

86.511:第一气隙

87.513:第二气隙

88.515:第一衬垫

89.517:第二衬垫

90.519:第三衬垫层

91.601:第一隔离膜

92.603:第二隔离膜

93.605:第三隔离膜

94.607:第四隔离膜

95.609:第五隔离膜

96.611:第六隔离膜

97.703:第二遮罩图案

98.s11:步骤

99.s13:步骤

100.s15:步骤

101.s17:步骤

102.s19:步骤

103.s21:步骤

104.s23:步骤

105.s25:步骤

106.s27:步骤

107.s29:步骤

108.s31:步骤

109.y:方向

110.z:方向

具体实施方式

111.以下描述了组件和配置的具体范例,以简化本公开的实施例。当然,这些实施例仅用以例示,并非意图限制本公开的范围。举例而言,在叙述中第一部件形成于第二部件之上,可能包含形成第一和第二部件直接接触的实施例,也可能包含额外的部件形成于第一

和第二部件之间,使得第一和第二部件不会直接接触的实施例。另外,本公开的实施例可能在许多范例中重复参照标号及/或字母。这些重复的目的是为了简化和清楚,除非内文中特别说明,其本身并非代表各种实施例及/或所讨论的配置之间有特定的关系。

112.此外,为易于说明,本文中可能使用例如“之下(beneath)”、“下面(below)”、“下部的(lower)”、“上方(above)”、“上部的(upper)”等空间相对关系用语来阐述图中所示的一个元件或特征与另一(其他)元件或特征的关系。所述空间相对关系用语旨在除图中所绘示的取向外亦囊括元件在使用或操作中的不同取向。所述装置可具有其他取向(旋转90度或处于其他取向)且本文中所用的空间相对关系描述语可同样相应地进行解释。

113.应当理解,当形成一个部件在另一个部件之上(on)、与另一个部件相连(connected to)、及/或与另一个部件耦合(coupled to),其可能包含形成这些部件直接接触的实施例,并且也可能包含形成额外的部件介于这些部件之间,使得这些部件不会直接接触的实施例。

114.应当理解,尽管这里可以使用术语第一,第二,第三等来描述各种元件、部件、区域、层或区段(sections),但是这些元件、部件、区域、层或区段不受这些术语的限制。相反,这些术语仅用于将一个元件、组件、区域、层或区段与另一个区域、层或区段所区分开。因此,在不脱离本发明进步性构思的教导的情况下,下列所讨论的第一元件、组件、区域、层或区段可以被称为第二元件、组件、区域、层或区段。

115.除非内容中另有所指,否则当代表定向(orientation)、布局(layout)、位置(location)、形状(shapes)、尺寸(sizes)、数量(amounts),或其他量测(measures)时,则如在本文中所使用的例如“同样的(same)”、“相等的(equal)”、“平坦的(planar)”,或是“共面的(coplanar)”等术语(terms)并非必要意指一精确地完全相同的定向、布局、位置、形状、尺寸、数量,或其他量测,但其意指在可接受的差异内,是包含差不多完全相同的定向、布局、位置、形状、尺寸、数量,或其他量测,而举例来说,所述可接受的差异是可因为制造流程(manufacturing processes)而发生。术语“大致地(substantially)”是可被使用在本文中,以表现出此意思。举例来说,如大致地相同的(substantially the same)、大致地相等的(substantially equal),或是大致地平坦的(substantially planar),是为精确地相同的、相等的,或是平坦的,或者是其是可为在可接受的差异内的相同的、相等的,或是平坦的,而举例来说,所述可接受的差异是可因为制造流程而发生。

116.在本公开中,一半导体存储器元件通常意指可通过利用半导体特性(semiconductor characteristics)运行的一元件,而一光电元件(electro

‑

optic device)、一发光显示元件(light

‑

emitting display device)、一半导体线路(semiconductor circuit)以及一电子元件(electronic device),是均包括在半导体元件的范畴中。

117.应当理解,在本公开的描述中,上方(above)(或之上(up))是对应z方向箭头的该方向,而下方(below)(或之下(down))是对应z方向箭头的相对方向。

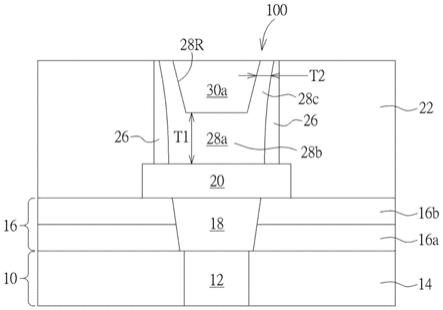

118.图1为依据本公开一些实施例中一种具有气隙以降低在多个导电特征之间的电容耦合的半导体存储器结构100的制备方法10的流程示意图。方法10可作为多个步骤执行。应当理解,方法10可以任何顺序执行,并可具有相同、更多或较少的步骤。应当理解,方法10可通过一或多个半导体制造设备或制造工具所执行。在一些实施例中,方法10包括步骤s11、

s13、s15、s17、s19、s21、s23、s25、s27、s29以及s31。图1的步骤s11到s31是结合下列图式进行详细说明。

119.图2为依据本公开一些实施例在如图1所示的方法10的步骤s11中形成一绝缘层以界定多个主动区在一基底中的一中间阶段的剖视示意图。在一些实施例中,执行所述制造程序以形成一绝缘层103,而绝缘层103是界定出一第一主动区105以及一第二主动区107在一基底101中。第一主动区105与第二主动区107可相互邻近设置。举例来说,绝缘层103可使用一浅沟隔离(sti)方法所形成。隔离层103可包括以下至少其中的一:一氮化硅层、一氧化硅层或一氮氧化硅层。绝缘层103可延伸进入基底101。

120.在一些实施例中,基底101可为一半导体晶圆,例如硅晶圆。另外或此外,半导体基底101可包括元素半导体材料、化合物半导体材料及/或合金半导体材料。元素半导体材料的例子可包括结晶硅(crystal silicon)、多晶硅(polycrystalline silicon)、非晶硅(amorphous silicon)、锗(germanium)及/或钻石(diamond),但并不以此为限。化合物半导体材料的例子可包括碳化硅(silicon carbide)、砷化镓(gallium arsenic)、磷化镓(gallium phosphide)、磷化铟(indium phosphide)、砷化铟(indium arsenide)、及/或锑化铟(indium antimonide),但并不以此为限。合金半导体材料的例子可包括硅锗(sige)、砷磷化镓(gaasp)、铟砷化铝(alinas)、镓砷化铝(algaas)、铟砷化镓(gainas)、铟磷化镓(gainp)、及/或磷砷化镓铟(gainasp),但并不以此为限。

121.在一些实施例中,半导体基底101具有一外延层(epitaxial layer)。举例来说,半导体基底101具有一外延层,是覆盖一块状半导体(bulk semiconductor)。在一些实施例中,半导体基底101为一绝缘体上覆半导体(semiconductor

‑

on

‑

insulator)基底,其是可包括一基底、在该基底上的一埋入氧化物层以及在该埋入氧化物层上的一半导体层,例如一绝缘体上覆硅(silicon

‑

on

‑

insulator,soi)基底、一绝缘体上覆硅锗(silicon germanium

‑

on

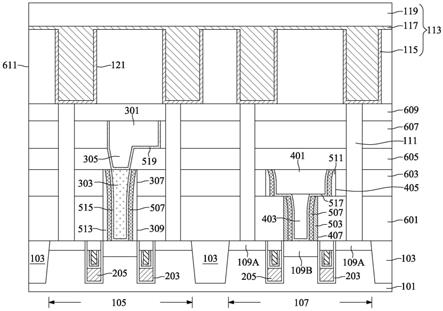

‑

insulator,sgoi)基底,或一绝缘体上覆锗(germanium

‑

on

‑

insulator,goi)基底。所述绝缘体上覆半导体基底可使用氧离子布植隔离(separation by implantation of oxygen,simox)制程、一晶圆接合(wafer bonding)制程、其他可应用的方法来制造。

122.在一些实施例中,半导体基底101可为多种材料,包括蓝宝石(sapphire)、硅、氮化锗(gallium nitride,gan)、锗或碳化硅,但并不以此为限。半导体基底101可为绝缘体上覆硅(soi)。在本公开的一些实施例中,半导体基底101为硅。一大致单晶体半导体(monocrystalline semiconductor)基底的晶体方向(crystallographic orientation),可为在米勒指数(miller indices)上的(100)、(111)或(110)中任一个。亦可能为其他晶体方向。半导体基底101的晶体方向可为偏切(offcut)。在本公开的一些实施例中,半导体基底101为具有结晶基底表面区的(100)硅,而该结晶机底表面区具有立方结晶度(cubic crystallinity)。在其他的实施例中,对于一(100)硅半导体基底101而言,半导体表面可斜切(miscut)或偏切(offcut),举例来说,朝向(110)的2

‑

10度角。在其他实施例中,半导体基底101为具有结晶基底表面区的(111)硅,而该结晶基底表面区具有六角结晶度(hexagonal crystallinity)。

123.图3到图4为依据本公开一些实施例在如图1所示的方法10的步骤s13中形成多个沟槽在该基底中的该主动区中的一中间阶段的剖视示意图。请参考图3,多个第一掺杂区109a可形成在基底101的第一主动区105的一上部中,以及在基底101的第二主动区107的一

上部中。多个第一掺杂区109a可掺杂有一掺杂物,例如磷、砷或锑(antimony)。所述第一掺杂区109a可使用一离子植入制程所形成。

124.请参考图4,多个字元线沟槽209可朝内分别形成在第一主动区105的上部中以及在第二主动区107的上部中。多个字元线沟槽209的底部可位在一垂直位面,是低于多个第一掺杂区109a的底面的一垂直位面。

125.在一些实施例中,一遮罩层110可形成在基底101上。可形成遮罩层110以具有多个开口110a,其是界定所述字元线沟槽209,而多个字元线(在下列会更详细描述)可形成在所述字元线沟槽209中。遮罩层110可为多个遮罩图案,举例来说,所述遮罩图案为氮化硅或光阻图案。基底101与绝缘层103可使用遮罩层110当作一蚀刻遮罩进行蚀刻,以形成所述字元线沟槽209,所述字元线沟槽209具有线性形状,并在第二方向y延伸。所述沟槽209的下表面可暴露所述主动区105。在执行蚀刻制程之后,可移除遮罩层110。举例来说,当遮罩层110为所述光阻图案时,遮罩层110可通过一灰化(aching)制程进行移除。当遮罩层110具有硬所述遮罩图案时,例如氮化硅,则遮罩层110可通过使用磷酸(phosphoric acid)的一清洗制程进行移除。

126.图5为依据本公开一些实施例在如图1所示的方法10的步骤s15中形成一下电极结构以大致充填所述沟槽的一下部的一中间阶段的剖视示意图。请参考图5,多个字元线隔离层203可分别对应形成在多个字元线沟槽209中,且多个下电极结构205可形成在每一字元线沟槽209的一下部中,而隔离层203是形成在字元线沟槽209中。

127.在一些实施例中,隔离层203可使用热氧化制程、一原子层沉积(ald)制程及/或一化学气相沉积(cvd)制程所形成。举例来说,隔离层203可包括一氧化硅层。在一些实施例中,一导电材料可沉积在具有隔离层203的基底101的大致一整个上表面上。此时,导电材料可大致充填所述沟槽209。导电材料的沉积可使用cvd制程来实现。导电材料可包括以下至少其一:一掺杂半导体材料(例如掺杂硅或掺杂锗)、一导电金属氮化物(例如氮化钛或氮化钽)、一金属(例如钨、钛或钽)或一金属半导体化合物(例如硅化钨、硅化钴或硅化钛)。接下来,可蚀刻沉积的导电材料,以形成所述下电极结构205。蚀刻制程可连续执行,直到导电材料维持有一所欲厚度在所述沟槽209中为止。

128.图6为依据本公开一些实施例在如图1所示的方法10的步骤s17中形成一源极层以及一第一扩散层在所述沟槽的一侧壁与一下表面上的一中间阶段的剖视示意图。在一些实施例中,执行所述制造程序以形成一初步源极层211以及一第一扩散层213在每一沟槽209的一侧壁与一下表面上,其中源极层可包含一功函数调整元素(element)。在一些实施例中,可形成初步源极层211以保形的覆盖所述下电极结构205的上表面以及隔离层203。初步源极层211可使用一cvd制程所形成。初步源极层211可包括一功函数调整元素或是功函数调整元素的化合物。举例来说,功函数调整元素可包含一金属,例如镧(lanthanum)、锶(strontium)、锑(antimony)、钇(yttrium)、铝、钽、铪(hafnium)、铱(iridium)、锆(zirconium)或镁(magnesium)。

129.在一些实施例中,一第一初步扩散层213可形成在基底101上。可形成第一初步扩散层213以保形地覆盖初步源极层211。第一初步扩散层213可使用一cvd制程所形成。第一初步扩散层213可包含一金属材料或一金属材料氮化物。金属材料可包括一金属元素,其是不同于功函数调整元素。举例来说,金属材料可包括一金属元素,例如钛或钨。

130.图7为依据本公开一些实施例在如图1所示的方法10的步骤s19中形成一功函数层,其是通过扩散功函数调整元素从该源极层到该第一扩散层的至少一部分的一中间阶段的剖视示意图。在一些实施例中,一初步功函数调整层215可通过以来自源极层211的功函数调整元素掺杂第一初步扩散层213所形成。初步功函数调整层215可具有一有效功函数,是低于第一初步扩散层213的有效功函数。举例来说,初步源极层2113的功函数调整元素可扩散进入第一初步扩散层213,以形成初步功函数扩散层215。功函数调整元素的扩散可通过一热处理制程(例如一退火制程)来执行。初步源极层211的功函数调整元素可通过热处理制程而扩散进入第一初步扩散层213。此时,大致整体第一初步扩散层213可掺杂有功函数调整元素,也因此第一初步扩散层213可完全地形成或是转变成初步功函数调整层215。因此,在初步源极层211的功函数调整元素扩散进入第一初步扩散层213之后,无须保留第一初步扩散层213。由于初步源极层211的功函数调整元素是扩散进入第一初步扩散层213,所以可缩减初步源极层213的一厚度。

131.在本公开的一举例的实施例中,通过功函数调整元件的化合物所分解的氧或氮,是可朝向下电极结构205扩散。如一个例子,由热处理制程的分解所产生的功函数调整元素可扩散进入第一初步扩散层213,且余留的氧或氮可朝向下电极结构205扩散。在一些实施例中,在扩散制程(例如热处理制程)之后,大致整体第一初步扩散层213可掺杂有功函数调整元素,且可能不会留下第一初步扩散层213。然而,本公开的实施例并未以此为限。在本公开的一举例的实施例中,第一初步扩散层213邻近导电层252的一部分无须掺杂功函数调整元素,但可将其保留下来。

132.图8为依据本公开一些实施例在如图1所示的方法10的步骤s21中形成一导电层在该第一扩散层上的一中间阶段的剖视示意图。在一些实施例中,一导电层217可形成在基底101上。导电层217可充填所述沟槽209的余留部分,并可覆盖基底101具有第一初步扩散层213的大致的一整体上表面。举例来说,导电层217可覆盖第一初步扩散层213相对初步源极层211的大致的一整体表面。导电层217可包含一低电阻材料,其电阻是低于第一初步扩散层213的电阻。举例来说,导电层217可包含一金属,例如钨、钛或钽。包含一导电材料的导电层217可形成在包含金属或金属氮化物的第一初步扩散层213上。

133.图9为依据本公开一些实施例形成多个字元线在所述沟槽中的一中间阶段的剖视示意图。在一些实施例中,可蚀刻导电层217、初步功函数调整层215以及初步源极层211,以形成一上电极结构219在每一沟槽209中。多个字元线221形成在基底101中的所述沟槽209中的所述主动区105、107中。蚀刻制程可连续执行,直到初步源极层211、初步功函数调整层215以及导电层217在所述沟槽209中维持有所欲厚度为止。通过蚀刻制程所形成的源极层211、功函数调整层215与导电层217的上表面可设置在相同位面。

134.接下来,可移除未被上电极结构219所覆盖但却暴露的隔离层203。因此,多个栅极隔离图案可形成在主动区105、107与电极结构205之间,及/或在绝缘层103与电极结构205之间。此外,绝缘层103与主动区105、107的上表面是可通过蚀刻制程而暴露。

135.图10为依据本公开一些实施例形成一第二掺杂区在所述主动区105、107中,而所述主动区是为在相互邻近的二字元线之间的一中间阶段的剖视示意图。在一些实施例中,一离子植入制程可执行在基底101上,以形成一第二掺杂区109b在主动区105、107中,而主动区105、107位在相互邻近的二字元线221之间。第二掺杂区109b可具有与第一掺杂区109a

相同的导电类型。举例来说,第二掺杂区109b可掺杂有n型掺杂物。在一些实施例中,第二掺杂区109b可深于在基底101中的第一掺杂区109a。

136.在一些实施例中,多个第一罩盖图案223可分别形成在所述沟槽209中。举例来说,一罩盖层(capping layer)可形成在基底101大致的一整体上表面上,然后一平坦化制程可执行在罩盖层上,以形成所述第一罩盖图案223。所述第一罩盖图案223可包括以下至少其一:一氮化硅层、一氧化硅层或一氮氧化硅层。

137.在本公开的一举例的实施例中,在形成源极层211、第一扩散层213以及导电层217之后,可执行参考图7及图8所描述的功函数调整元素的扩散制程。举例来说,退火制程可执行在源极层211、第一扩散层213以及导电层217上。源极层211的功函数调整元素可扩散进入第一扩散层213,以形成功函数调整层215。大致整体的第一扩散层213可通过扩散制程而掺杂有功函数调整元素,且在扩散制程之后无须保留第一扩散层213。或者是,在扩散制程之后,可保留第一扩散层213的一部分。在本公开所举例的一实施例中,在形成源极层211、第一扩散层213与导电层217之后,可立刻执行功函数调整元素的扩散制程,或者是在形成源极层211、第一扩散层213与导电层217之后的制造半导体存储器元件期间才进行。

138.图11到图20为依据本公开一些实施例在如图1所示的方法10的步骤s23中形成一高位面位元线接触点、一低位面位元线接触点以及一低位面位元线在该基底上的一中间阶段的剖视示意图。请参考图11,一第一隔离膜601可形成在基底101上,且一第二隔离膜603可形成在第一隔离膜601上。一第一微影制程可使用一第一遮罩图案701来执行,以界定出在第二隔离膜603上的高位面位元线接触点303以及低位面位元线401。

139.请参考图12,在第一微影制程之后,可执行一第一蚀刻制程,例如非等向性干蚀刻制程,以形成高位面位元线的一接触点开口307以及一低位面位元线沟槽405在第二隔离膜603中。

140.请参考图13,可使用一第二遮罩图案703以执行一第二微影制程,以界定出高位面位元线接触点303的位置以及在第一隔离膜601上的低位面位元线接触点403的一位置。

141.请参考图14,在第二微影制程之后,可执行一第二蚀刻制程,例如非等向性干蚀刻制程,以形成一较低的高位面位元线接触点开口309以及一低位面位元线接触点开口407在第一隔离膜601中。设置在第一主动区105中的相邻对字元线201之间以及在第二主动区107中的相邻对字元线201之间的多个掺杂区109b,可分别经由较低的高位面位元线接触点开口309与低位面位元线接触点开口407而暴露。

142.请参考图15,可形成一第一间隙子层501以覆盖第二隔离膜603的上表面、较上面的高位面位元线接触点开口307的侧壁、较低的高位面位元线接触点开口309的侧壁与底部、低位面位元线沟槽405的侧壁与底部以及第位面位元线接触点开口407的侧壁与底部。第一间隙子层501可由掺杂氧化物所制,例如硼二氧化硅玻璃(borosilica glass)、磷硅酸盐玻璃(phosphosilica glass)、硼磷硅酸盐玻璃(borophosphosilica glass)、氟硅酸盐玻璃(fluoride silicate glass)、掺杂有碳的氧化硅(carbon doped silicon oxide)或其类似物。或者是,在其他实施例中,第一间隙子层501可由一热可分解聚合物(thermal decomposable polymer)或一热可降解聚合物(thermal degradable polymer)所制。

143.可执行一蚀刻制程,例如非等向性干蚀刻制程,以形成多个第一间隙子503,其是贴合到较上面的高位面位元线接触点开口307的侧壁、较低的高位面位元线接触点开口309

的侧壁、低位面位元线沟槽405的侧壁以及低位面位元线接触点开口407的侧壁。

144.请参考图17,可形成一第二间隙子层505,以覆盖第二隔离膜603的上表面、低位面位元线沟槽405的底部、低位面位元线接触点开口407的底部以及多个第一间隙子503的表面。举例来说,第二间隙子层505可由氮化硅所制。

145.请参考图18,可执行一蚀刻制程,例如非等向性干蚀刻制程,以形成多个第二间隙子507,其是贴合到多个第一间隙子503的表面。

146.请参考图19,可形成一衬垫层509,以覆盖第二隔离膜603的上表面、多个第二间隙子507的表面、低位面位元线沟槽405的底部以及低位面位元线接触点开口407的底部。举例来说,衬垫层509可由下列材料所制:钛、氮化钛、氮化硅钛(titanium silicon nitride)、钽、氮化钽、氮化硅钽(tantalum silicon nitride)或其组合。

147.请参考图20,通过一金属化制程,一导电材料可沉积进入较上面的高位面位元线接触点开口307、较低的高位面位元线接触点开口309、低位面位元线沟槽405以及低位面位元线接触点开口407中,举例来说,导电材料为掺杂多晶硅、金属、金属氮化物或金属硅化物。在所述的实施例中,导电材料可为钨。在金属化制程之后,可执行一平坦化制程,例如化学机械研磨,以移除多余的填充材料,提供一大致平坦表面给接下来的处理步骤,并保形地形成高位面位元线接触点303、低位面位元接触点403以及低位面位元线401。在一些实施例中,低位面位元线接触点303、低位面位元线401以及高位面位元线接触点303通过相同制造程序而形成在一起,并可具有类似的物理特性以及化学特性,而物理特性是例如硬度(hardness),化学特性是例如蚀刻率。

148.图21及图22为依据本公开一些实施例在如图1所示的方法10的步骤s25中形成多个气隙在该基底上的一中间阶段的剖视示意图。请参考图21,可执行一平坦化制程,例如化学机械研磨,以移除部分的衬垫层509。在平坦化制程之后,衬垫层509可转变成一第一衬垫515以及一第二衬垫517,第一衬垫515设置在邻近高位面位元线接触点303的侧壁处,而第二衬垫517设置在低位面位元线401的侧边上、在低位面位元线接触点403的侧边上、在低位面位元线接触点403的一底部上以及在第一隔离膜601的一上表面的一部分上,且第二衬垫517贴合到低位面位元线401的侧边、在低位面位元线接触点403的侧边、在低位面位元线接触点403的一底部以及在第一隔离膜601的一上表面的该部分。在平坦化制程之后,可暴露设置在邻近高位面位元线接触点303处的多个第一间隙子503的上表面,以及设置在邻近低位面位元线401处的多个第一间隙子503的上表面。

149.请参考图21,在一些实施例中,低位面位元线接触点403的高度是低于高位面位元线接触点303的高度。在一些实施例中,低位面位元线401的宽度是大于低位面位元线接触点403的宽度。在一些实施例中,由于平坦化制程,所以高位面位元线接触点303的上表面与低位面位元线401的上表面大致位在相同位面,且高位面位元线接触点303的高度大致相同于低位面位元线接触点403与低位面位元线401的组合高度。

150.请参考图22,可移除设置在邻近高位面位元线接触点303处的多个第一间隙子503以及设置在邻近低位面位元线401处的多个第一间隙子503,以形成多个气隙。在一些实施例中,可引入一气相氟化氢(vapor hydrogen fluoride),并可蚀刻设置在邻近高位面位元线接触点303处的多个第一间隙子503以及设置在邻近低位面位元线401处的多个第一间隙子503。气相氟化氢在多个第一间隙子503上具有一较高的蚀刻率,而所述第一间隙子503是

由掺杂氧化物所制;因此,可移除设置在邻近高位面位元线接触点303处的多个第一间隙子503以及设置在邻近低位面位元线401处的多个第一间隙子503,且可保留由氮化硅所制的多个第二间隙子507。在接下来的制程步骤期间,例如热处理,多个第二间隙子507可避免高位面位元线接触点303、低位面位元线401或低位面位元线接触点403的材料流入多个气隙中。多个气隙可包括多个第一气隙511以及多个第二气隙513。所述第一气隙511可设置在邻近低位面位元线401处。所述第二气隙513可设置在邻近高位面位元线接触点303处。

151.在一些实施例中,气隙513与气隙511通过选择性蚀刻掺杂氧化物的所述第一间隙子503而形成在一起。在一些实施例中,气隙513围绕高位面位元线接触点303(圆柱或拴柱),而第一衬垫515与所述第二间隙子507将高位面位元线接触点303与气隙513分开;且气隙511形成在低位面位元线401的两侧,而第二衬垫517与所述第二间隙子507将低位面位元线401与气隙511分开。在一些实施例中,并未移除位在低位面位元线接触点403的各侧边处的所述第一间隙子503,且气隙511选择性地形成在低位面位元线401的各侧边处,并未位在低位面位元线接触点303的各侧边处。

152.请参考图22,或者是,在其他实施例中,多个第一间隙子503是由热可分解聚合物或热可降解聚合物所制,并施加一热处理制程以移除热可分解聚合物或热可降解聚合物。热处理制程的一温度可介于大约300℃到大约450℃之间。优选地,热处理制程的温度可介于大约350℃到大约420℃之间。

153.图23及图24为依据本公开一些实施例在如图1所示的方法10的步骤s27中形成一高位面位元线接触点以及一高位面位元线在该基底上的一中间阶段的剖视示意图。一高位面位元线接触点305以及一高位面位元线301可形成在基底101上。请参考图23,举例来说,一第三隔离膜605可通过旋涂式玻璃无间隙填充沉积(spin

‑

on

‑

glass non

‑

gap fill deposition)而形成在第二隔离膜603上。应当理解,在第三隔离膜605形成之后,并未充填所述第一气隙2511与所述第二气隙513。一第四隔离膜607可形成在第三隔离膜605上。可执行一第一微影制程以界定在第四隔离膜607上的高位面位元线301的位置。在第一微影制程之后,可执行第一蚀刻制程,例如非等向性干蚀刻制程,以形成一高位面位元线沟槽311在第四隔离膜607中。可执行一第二微影制程以界定在第三隔离膜605上的高位面位元线接触点305的位置。

154.请参考图23,在第二微影制程之后,可执行一第二蚀刻制程,例如非等向性干蚀刻制程,以形成一高位面位元线接触点开口313在第三隔离膜605中。高位面位元线接触点开口313的一下开口的一宽度,可小于高位面位元线接触点开口313的一上开口的一宽度;换言之,高位面位元线接触点开口313的一轮廓是从上到下逐渐变小。意即,高位面位元线接触点开口313的侧壁可相互倾斜。高位面位元线接触点开口313的下开口的宽度可大约相同于高位面位元线接触点303的一上表面的一宽度。高位面位元线接触点303的上表面可经由高位面位元线接触点开口313与高位面位元线沟槽311而暴露。可选择地执行使用一还原剂(reducing agent)的一清洗制程,以移除多个缺陷,所述缺陷是位在高位面位元线接触点303的上表面上,而高位面位元线接触点303是包含有钨所制。还原剂可为四氯化钛(titanium tetrachloride)、四氯化钽(tantalum tetrachloride)或其组合。

155.请参考图24,一导电材料可通过一金属化制程而沉积进入高位面位元线沟槽311与高位面位元线接触点开口313,举例来说,导电材料为掺杂多晶硅、金属、金属氮化物或金

属硅化物。在金属化制程之后,可执行一平坦化制程,例如化学机械研磨,以移除多余填充材料,提供一大致平坦表面给接下来的处理步骤,且保形地形成高位面位元线301与高位面位元线接触点305。此外,在形成高位面位元线301与高位面位元线接触点305之前,一第三衬垫层519可形成在高位面位元线沟槽311的侧壁上、在高位面位元线沟槽311的一底部的一部分上、高位面位元线接触点开口313的侧壁上以及在高位面位元线接触点开口313的底部上,并贴合到高位面位元线沟槽311的侧壁、在高位面位元线沟槽311的底部的该部分上、高位面位元线接触点开口313的侧壁以及在高位面位元线接触点开口313的底部。

156.请参考图24,在一些实施例中,高位面位元线301的宽度大于高位面位元线接触点305与高位面位元线接触点303的宽度。在一些实施例中,高位面位元线301非对称地位在高位面位元线接触点305与高位面位元线接触点303上。

157.图25为依据本公开一些实施例在如图1所示的方法10的步骤s29中形成多个导电栓塞在该基底上的一中间阶段的剖视示意图。在一些实施例中,一第五隔离膜609可形成在第四隔离膜607上。可执行一微影制程以界定在第五隔离膜609中的多个导电栓塞111的位置。在微影制程之后,可执行一蚀刻制程,例如非等向性干蚀刻制程,以形成多个导电栓塞开口,是穿过第五隔离膜609、第四隔离膜607、第三隔离膜605、第二隔离膜605以及第一隔离膜601。设置在隔离层103与多个字元线201之间的多个掺杂区的上表面,是经由多个导电栓塞开口而暴露,而多个字元线是均位在第一主动区105与第二主动区107中。

158.请参考图25,一导电材料可通过一金属化制程而沉积进入多个导电栓塞开口,举例来说,导电材料为掺杂多晶硅、钛、氮化钛、钽、氮化钽、钨、铜、铝或铝合金。在金属化制程之后,可执行一平坦化制程,例如化学机械研磨,以移除多余填充材料,提供一大致平坦表面给接下来的处理步骤,且保形地形成多个导电栓塞111。多个导电栓塞111可分别对应电性连接到多个掺杂区109a,而多个掺杂区109a是设置在绝缘层103与多个字元线201之间,且多个字元线201是均位在第一主动区105与第二主动区107中。

159.图26到图28为依据本公开一些实施例在如图1所示的方法10的步骤s31中形成多个电容结构自该基底上的一中间阶段的剖视示意图。在一些实施例中,多个电容结构113可形成在基底101上。请参考图26,一第六隔离膜611可形成在第五隔离膜609上。可执行一微影制程以界定在第六隔离膜611中的多个电容结构113的位置。在微影制程之后,可执行一蚀刻制程,例如非等向性干蚀刻制程,以形成多个电容沟槽121在第六隔离膜611中。多个导电栓塞111的上表面可经由多个电容沟槽121而暴露。多个电容下电极115可分别对应形成在多个电容沟槽121中。

160.请参考图27,一电容隔离层117可形成在多个电容下电极115上,并可充填多个电容沟槽121。

161.请参考图28,一电容上电极119可形成在电容隔离层117上,并可充填多个电容沟槽121。多个电容下电极115、电容隔离层117以及电容上电极119一起形成多个电容结构113。

162.本公开的一实施例提供一种半导体存储器元件,包括一绝缘层,界定一第一主动区在一基底中;一第一掺杂区,位在该第一主动区中;一第一字元线,埋入在一第一沟槽中,该第一沟槽邻近该第一掺杂区设置;一高位面字元线接触点,位在该第一掺杂区上;以及一第一气隙,围绕该高位面位元线接触点设置;其中该第一字元线包括一下电极结构以及一

上电极结构,该上电极结构位在该下电极结构上;以及其中该上电极结构包括一源极层、一导电层以及一功函数调整层,该源极层大致覆盖该第一沟槽的一侧壁,该导电层位在该源极层上,该功函数调整层设置在该源极层与该导电层之间。

163.本公开的另一实施例提供一种半导体存储器元件的制备方法,包括:形成一绝缘层以界定一第一主动区在一基底中;形成一第一掺杂区在该第一主动区中;形成一第一字元线以埋入在一第一沟槽中,该第一沟槽邻近该第一掺杂区设置;形成一高位面位元线接触点以位在该第一掺杂区上;以及形成一第一气隙以围绕该高位面位元线接触点;其中形成该第一字元线包括:形成一下电极结构以及一上电极结构,该上电极结构位在该下电极结构上;其中形成该上电极结构包括:形成一源极层以大致覆盖该第一沟槽的一侧壁;形成一导电层在该源极层上;以及形成一功函数调整层以位在该源极层与该导电层之间。

164.综上所述,该功函数调整层是具有一相对低的功函数,并设置在该上电极结构的外侧处,是可降低或最小化一栅极引发漏极漏电流(gidl),其是该字元线道所述掺杂区所产生。此外,该上电极结构的功函数可通过调整该功函数调整层的一掺杂浓度进行调整。因此,可达到该上电极结构的一所欲的低功函数。

165.再者,该半导体存储器元件具有多个气隙,且所述导电特征是通过所述气隙而相互分开设置。因此,可降低在所述导电接触点之间的寄生电容。结果,可改善整体元件效能(意即减少功耗以及电阻

‑

电容(rc)延迟),且可提升该半导体元件的良率。

166.虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的精神与范围。例如,可用不同的方法实施上述的许多制程,并且以其他制程或其组合替代上述的许多制程。

167.再者,本技术案的范围并不受限于说明书中所述的制程、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的揭示内容理解可根据本公开而使用与本文所述的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的制程、机械、制造、物质组成物、手段、方法、或步骤。据此,此等制程、机械、制造、物质组成物、手段、方法、或步骤是包含于本技术案的权利要求内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。