一种小型化x波段雷达信号处理装置

技术领域

1.本实用新型属于雷达技术领域,尤其涉及一种小型化x波段雷达信号处理装置。

背景技术:

2.x波段雷达根据观测目标对x波段电磁波的反射或后向散射回波,对目标进行位置、距离、速度等参数进行测量。x波段电磁波波长约3厘米,对云、雨粒子有较好的探测效果,可以实现降水强度、云高、云厚、云内含水量等气象数据的探测,为天气预报、交通运输、人工影响天气等业务提供有效的数据支撑。

3.雷达系统由天线、发射机、接收机、信号处理装置、显示装置组成。雷达信号处理装置具有采集雷达回波信号功能,并对回波信号进行计算,获取距离、方位、速度、强度等信息,是雷达系统中的重要组成部分。

4.随着嵌入式设计技术和芯片技术革新,高密度现场可编程逻辑器件(field programmable gate array)具有设计灵活、功能强大的优势,在数字信号处理领域有较为广泛的应用。

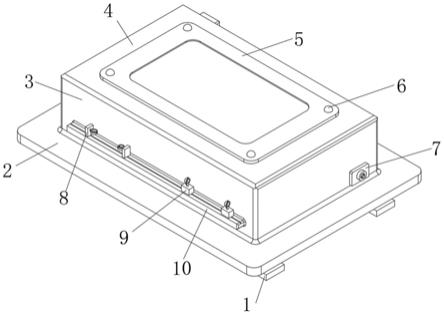

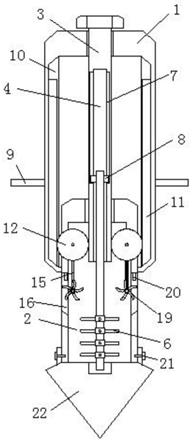

5.现有技术使用fpga芯片和dsp芯片组合进行信号处理运算,信号处理装置电路结构如附图1所示,中频输入接口接收来自接收机的信号,依次经过高速adc芯片、fpga芯片、dsp芯片、网络接口芯片输出至显示设备接口,时钟发生电路为高速adc芯片、fpga芯片、dsp芯片提供时钟脉冲;现有的雷达系统由如附图2所示装置构成,天线、接收机、信号处理装置、显示装置依次相连;显示装置、波形产生装置、发射机、天线依次相连。

6.由于fpga芯片和dsp芯片面积较大,外围设备芯片数量较大,无法集成到小型化板卡中导致信号处理器体积大、功耗较高。随着设备小型化趋势,较大尺寸的信号处理装置在应用时具有局限性。

技术实现要素:

7.本实用新型的目的就在于为了解决上述问题而提供一种小型化x波段雷达信号处理装置,包括高速模数转换器、低速模数转换器、fpga模块、直接数字频率合成器、时钟发声电路;低速模数转换器输入端用于发射功率信号输入;高速模数转换器输入端用于接收机中频信号输入;低速模数转换器输出端、高速模数转换器输出端分别连接fpga模块输入端;fpga模块第一输出端连接与显示设备相连的显示设备接口;fpga模块第二输出端通过直接数字频率合成器连接与发射极相连的发射信号输出接口;时钟发声电路分别连接低速模数转换器与fpga模块。

8.本实用新型的有益效果在于:本实用新型利用fpga实现雷达信号处理功能,将复杂的高速的信号处理运算集中到一片芯片内实现,有助于降低雷达信号处理器的硬件复杂度,有利于雷达的的低功耗化、小型化,降低了雷达硬件成本。

附图说明

9.图1是现有技术的信号处理装置的电路结构图;

10.图2是雷达系统原理图;

11.图3是本实用新型的信号处理装置的原理图;

12.图4是本实用新型具体实施方式的原理图;

13.图5是基于本实用新型的雷达系统原理图。

具体实施方式

14.下面结合附图对本实用新型作进一步说明:

15.如附图3所示,本实用新型一种小型化x波段雷达信号处理装置,包括高速模数转换器、低速模数转换器、fpga模块、直接数字频率合成器、时钟发声电路;低速模数转换器输入端用于发射功率信号输入;高速模数转换器输入端用于接收机中频信号输入;低速模数转换器输出端、高速模数转换器输出端分别连接fpga模块输入端;fpga模块第一输出端连接与显示设备相连的显示设备接口;fpga模块第二输出端通过直接数字频率合成器连接与发射极相连的发射信号输出接口;时钟发声电路分别连接低速模数转换器与fpga模块。

16.优选的,所述fpga模块采用xc7k325t芯片。

17.优选的,所述高速模数转换器为ad9446芯片。

18.优选的,所述低速模数转换器为ltc2290芯片。

19.优选的,所述接数字频率合成器采用ad9910芯片。

20.优选的,所述时钟发生电路采用ad9516

‑

3芯片。

21.本实用新型装置包括高速模数转换器(adc)芯片、低速模数转换器(adc)芯片、fpga芯片、直接数字频率合成(dds)芯片与时钟发生电路。该装置具有采集和处理雷达回波信号功能,并根据回波信号计算显示模块需要的数据。设置一路低速模数转换器能够在实际应用时采集发射功率包络电平和波形。fpga芯片具有设计灵活、功能强大的优点,将dsp芯片的运算功能和网络接口芯片的功能集中到fpga芯片内部,使用一片集成度高的fpga芯片代替现有方案中的fpga芯片、dsp芯片、网络接口芯片,通过对硬件电路优化,将电路集成到cpci规范3u高度的板卡中。该装置集成波形产生模块,可以直接向发射机提供所需的激励波形。

22.fpga芯片选择xc7k325t芯片,该芯片集成326080个逻辑单元,840个dsp运算单元,支持高速串行接口;高速模数转换器(adc)芯片选择ad9446,该芯片最高采样率为100msps,无杂散动态范围为95dbfs;低速模数转换器(adc)芯片选择ltc2290,该芯片支持最高10msps采样率,12位量化位数,具有低非线性误差特性;fpga芯片集成有数据处理单元与波形产生模块。直接数字频率合成(dds)芯片选用ad9910,该芯片内置14位数模转换器,支持最高1gsps采样率;时钟发生电路选用ad9516

‑

3芯片,该芯片提供多路时钟分配功能,具有低抖动特性和低相位噪声特性,每路输出有独立的分频器。

23.高速模数转换器(adc)芯片的信号输入端与本装置的中频输入接口连接,高速模数转换器(adc)芯片的信号输出端和fpga芯片信号输入端连接,直接数字频率合成(dds)芯片输入端与fpga芯片信号输出端连接,直接数字频率合成(dds)芯片输出端与本装置的发射波形输出接口连接,低速模数转换器(adc)芯片的信号输入端和本装置的发射功率输入

接口连接,低速模数转换器(adc)芯片的输出端和fpga芯片信号输入端连接。fpga直接和本装置的显示设备接口连接。

24.结合具体实施,本装置的工作原理如下:

25.如附图4所示,在本装置具有生成激励波形和采集处理回波两个功能,两个功能在时钟发生电路协同下同步进行。在生成激励波形时,fpga芯片根据当前工作模式,计算频率控制信息发送给直接数字频率合成(dds)芯片,dds芯片根据频率控制信息生成波形信号从发射波形输出接口输出。在采集处理回波时,高速模数转换器(adc)芯片采集模拟中频数据,并量化成数字形式发送给fpga芯片,fpga芯片对中频信号处理和计算得出距离、强度等信息发送给显示装置,同时低速模数转换器(adc)芯片采集功率信息,传输给fpga芯片,由fpga芯片处理后发送给显示装置。

26.本实用新型能够简化雷达系统结构,简化后的雷达系统结构如附图5所示,包括天线、接收机、信号处理装置、显示装置、发射机;天线通过接收机接信号处理装置输入端;信号处理装置与显示装置相连;信号处理装置通过发射机接天线。

27.fpga芯片选择xc7k325t芯片,该芯片集成326080个逻辑单元,840个dsp运算单元,支持高速串行接口。高速模数转换器(adc)芯片选择ad9446,该芯片最高采样率为100msps,无杂散动态范围为95dbfs。低速模数转换器(adc)芯片选择ltc2290,该芯片支持最高10msps采样率,12位量化位数,具有低非线性误差特性。直接数字频率合成(dds)芯片选用ad9910,该芯片内置14位数模转换器,支持最高1gsps采样率。时钟发生电路选用ad9516

‑

3芯片,该芯片提供多路时钟分配功能,具有低抖动特性和低相位噪声特性,每路输出有独立的分频器。

28.本实用新型利用fpga实现雷达信号处理功能,将复杂的高速的信号处理运算集中到一片芯片内实现,有助于降低雷达信号处理器的硬件复杂度,有利于雷达的的低功耗化、小型化,降低了雷达硬件成本。

29.本实用新型的技术方案不限于上述具体实施例的限制,凡是根据本实用新型的技术方案做出的技术变形,均落入本实用新型的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。