时钟信号延迟路径单元和包括其的半导体存储器件

1.相关申请的交叉引用

2.本技术要求于2021年9月6日在韩国知识产权局提交的韩国专利申请no.10-2021-0118258的优先权,该申请的公开内容通过引用整体地并入本文。

技术领域

3.实施例涉及一种时钟信号延迟路径单元和一种包括所述时钟信号延迟路径单元的半导体存储器件。

背景技术:

4.半导体存储器件可以包括延迟锁定环电路。延迟锁定环电路可以包括延迟锁定环和时钟信号延迟路径单元。延迟锁定环可以生成相对于外部时钟信号被锁定延迟的延迟时钟信号。时钟信号延迟路径单元可以通过信号线将延迟时钟信号延迟相同的延迟时间以生成内部时钟信号,并将所述内部时钟信号传输到目标块(例如,数据选通信号驱动器和数据驱动器)。

技术实现要素:

5.一种根据实施例的时钟信号延迟路径单元可以包括:至少一个第一延迟单元,每一个所述第一延迟单元包括:用于延迟并传输时钟信号的第一路由信号线、用于无信号衰减地传输通过所述第一路由信号线传输的所述时钟信号的第一中继器、以及用于延迟并传输从所述第一中继器输出的所述时钟信号的第二路由信号线;第二延迟单元,所述第二延迟单元包括用于使从所述至少一个第一延迟单元提供的所述时钟信号反相以生成反相时钟信号的第一反相电路;以及至少一个第三延迟单元,每一个所述第三延迟单元包括:用于延迟并传输从所述第二延迟单元提供的所述反相时钟信号的第一分支信号线、用于无信号衰减地传输通过所述第一分支信号线传输的所述反相时钟信号的第二中继器、以及用于延迟并传输从所述第二中继器输出的所述反相时钟信号的第二分支信号线,其中所述第一路由信号线、所述第二路由信号线、所述第一分支信号线和所述第二分支信号线均可以是长金属线。

6.一种根据实施例的半导体存储器件可以包括:时钟信号输入缓冲器,所述时钟信号输入缓冲器被配置为缓冲从外部施加的外部时钟信号并且输出缓冲时钟信号;延迟锁定环,所述延迟锁定环被配置为接收所述缓冲时钟信号并且生成相对于所述外部时钟信号被锁定延迟的延迟时钟信号;时钟信号延迟路径单元,所述时钟信号延迟路径单元被配置为使所述延迟时钟信号延迟和反相,以生成n个内部时钟信号、输出数据选通信号和反相输出数据选通信号;存储单元阵列,所述存储单元阵列包括多个存储单元并且输出存储在响应于多个字线选择信号和多个列选择信号而选择的存储单元中的数据;数据读取路径单元,所述数据读取路径单元被配置为接收所述数据并且将所述数据转换成串行数据以生成n条数据;数据输出单元,所述数据输出单元被配置为响应于所述n个内部时钟信号而驱动所述

n条数据;以及数据选通信号输出单元,所述数据选通信号输出单元被配置为驱动所述输出数据选通信号和所述反相输出数据选通信号,其中所述时钟信号延迟路径单元包括n 2个分支延迟单元,每个所述分支延迟单元包括:至少一个第一延迟单元,每一个所述第一延迟单元包括:用于延迟并传输所述延迟时钟信号的第一路由信号线、被配置为无信号衰减地传输通过所述第一路由信号线传输的所述延迟时钟信号的第一中继器、以及用于延迟并传输从所述第一中继器输出的所述延迟时钟信号的第二路由信号线;第二延迟单元,所述第二延迟单元包括被配置为使从所述至少一个第一延迟单元提供的所述延迟时钟信号反相以生成反相延迟时钟信号的第一反相电路;以及至少一个第三延迟单元,每一个所述第三延迟单元包括:用于延迟并传输从所述第二延迟单元提供的所述反相延迟时钟信号的第一分支信号线、被配置为无信号衰减地传输通过所述第一分支信号线传输的所述反相延迟时钟信号的第二中继器、以及用于延迟并传输从所述第二中继器输出的所述反相延迟时钟信号的第二分支信号线,其中所述第一路由信号线、所述第二路由信号线、所述第一分支信号线和所述第二分支信号线均可以是长金属线,并且所述n 2个分支延迟单元可以生成所述n个内部时钟信号、所述输出数据选通信号和所述反相输出数据选通信号。

7.一种根据实施例的半导体存储器件可以包括:读取使能信号输入缓冲器,所述读取使能信号输入缓冲器被配置为缓冲从外部施加的读取使能信号并且输出缓冲的读取使能信号;反相读取使能信号输入缓冲器,所述反相读取使能信号输入缓冲器被配置为缓冲从外部施加的反相读取使能信号并且输出缓冲的反相读取使能信号;读取使能信号延迟路径单元,所述读取使能信号延迟路径单元被配置为使所述缓冲的读取使能信号和所述缓冲的反相读取使能信号延迟和反相以生成n个内部时钟信号、输出数据选通信号和反相输出数据选通信号;存储单元阵列,所述存储单元阵列包括多个存储单元并且输出存储在响应于多个字线选择信号、多个源极线选择信号、多个地选择信号和多个列选择信号而选择的存储单元中的数据;页面缓冲器,所述页面缓冲器被配置为缓冲所述数据以生成读取数据;数据读取路径单元,所述数据读取路径单元被配置为接收所述读取数据并且将所述数据转换为串行数据以生成n条数据;数据输出单元,所述数据输出单元被配置为响应于所述n个内部时钟信号而驱动所述n条数据;以及数据选通信号输出单元,所述数据选通信号输出单元被配置为驱动所述输出数据选通信号和所述反相输出数据选通信号,其中所述读取使能信号延迟路径单元包括n 2个分支延迟单元,每个所述分支延迟单元包括:至少一个第一延迟单元,每一个所述第一延迟单元包括:用于延迟并传输包括所述缓冲的读取使能信号和所述缓冲的反相读取使能信号的读取使能信号对的第一路由信号线对、被配置为无信号衰减地传输通过所述第一路由信号线对传输的所述读取使能信号对的第一中继器、以及用于延迟并传输从所述第一中继器输出的所述读取使能信号对的第二路由信号线对;第二延迟单元,所述第二延迟单元包括被配置为使从所述至少一个第一延迟单元提供的所述读取使能信号对反相并且输出反相读取使能信号对的第一反相电路;以及至少一个第三延迟单元,每一个所述第三延迟单元包括:用于延迟并传输从所述第二延迟单元提供的所述反相读取使能信号对的第一分支信号线对、被配置为无信号衰减地传输通过所述第一分支信号线对传输的所述反相读取使能信号对的第二中继器、以及用于延迟并传输从所述第二中继器输出的所述反相读取使能信号对的第二分支信号线对,其中所述第一路由信号线对、所述第二路由信号线对、所述第一分支信号线对和所述第二分支信号线对均可以是长金属线

对,并且所述n 2个分支延迟单元可以生成所述n个内部时钟信号、所述输出数据选通信号和所述反相输出数据选通信号。

附图说明

8.通过参考附图详细地描述示例实施例,对本领域的技术人员而言特征将变得显而易见,在附图中:

9.图1是示出根据示例实施例的时钟信号延迟路径单元的图。

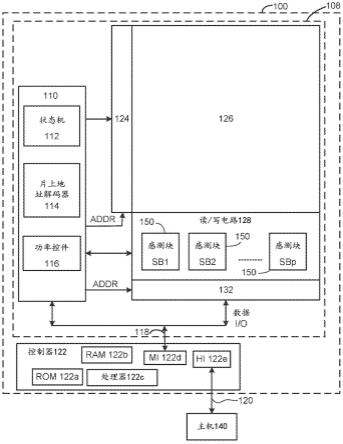

10.图2a和图2b是根据示例实施例的半导体存储器件的框图。

11.图3是示出根据示例实施例的半导体存储器件的布置的图。

12.图4是示出根据示例实施例的外围电路区域的垂直布置的图。

13.图5是示出根据示例实施例的时钟信号延迟路径单元的配置的图。

14.图6是示出根据示例实施例的时钟信号延迟路径单元的配置的图。

15.图7是示出根据示例实施例的时钟信号延迟路径单元的配置的图。

16.图8a和图8b是示出根据示例实施例的中继器的配置的图。

17.图9a和图9b是示出根据示例实施例的反相中继器的配置的图。

18.图10是示出根据示例实施例的中继器的逆变器的配置的图。

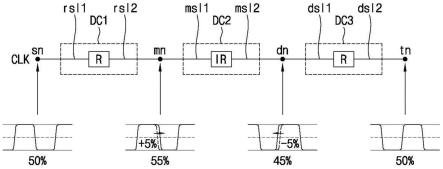

19.图11是用于描述根据示例实施例的时钟信号延迟路径单元的操作的波形图。

20.图12是示出根据示例实施例的占空比校正器的配置的框图。

21.图13是示出根据示例实施例的占空比检测器的配置的框图。

22.图14是示出根据示例实施例的占空比调节器的配置的电路图。

23.图15a和图15b是示出根据示例实施例的分相器和选择器的配置的图。

24.图16是示出根据示例实施例的时钟信号延迟路径单元的图。

25.图17a和图17b是示出根据示例实施例的半导体存储器件的框图。

26.图18a和图18b是示出根据示例实施例的中继器r的配置的图。

27.图19a和图19b是示出根据示例实施例的反相中继器的配置的图。

28.图20是示出根据示例实施例的反相电流模式逻辑差分放大器的配置的图。

具体实施方式

29.图1是示出根据示例实施例的时钟信号延迟路径单元的图。如下将参考图1描述时钟信号延迟路径单元的配置和操作。

30.时钟信号延迟路径单元可以包括第一延迟单元dc1、第二延迟单元dc2和第三延迟单元dc3。

31.第一延迟单元dc1可以包括延迟并传输时钟信号clk的第一路由信号线rsl1、无信号衰减地传输通过第一路由(root)信号线rsl1传输的时钟信号的中继器r、以及延迟并传输从中继器r输出的时钟信号的第二路由信号线rsl2。

32.第一路由信号线rsl1和第二路由信号线rsl2均可以是长金属线。

33.通过第一延迟单元dc1传输的时钟信号clk的占空比可以根据工艺、电压和温度(pvt)的变化而变化。例如,尽管施加到起始节点sn的时钟信号clk的占空比是50%,但是当时钟信号clk通过第一延迟单元dc1时占空比可以增加5%,因此在中间节点mn处生成的时

钟信号clk的占空比可以达到55%。

34.第二延迟单元dc2可以包括:第一中间信号线msl1,其延迟并传输从第一延迟单元dc1提供的时钟信号clk;反相中继器ir,其使通过第一中间信号线msl1传输的时钟信号clk反相以生成反相时钟信号并且无信号衰减地传输该反相时钟信号;以及第二中间信号线msl2,其延迟并传输从反相中继器ir输出的反相时钟信号。

35.反相中继器ir可以包括串联连接的反相电路(未示出)和中继器r(未示出)。在这种情况下,反相电路使从第一延迟单元dc1提供的时钟信号clk反相以生成反相时钟信号,中继器r无信号衰减地传输该反相时钟信号。

36.在示例实施例中,可以将第二延迟单元dc2实现为反相电路(未示出)。例如,第二延迟单元dc2可以不包括作为长金属线的第一中间信号线msl1和第二中间信号线msl2以及中继器r。

37.第二延迟单元dc2可以使具有因第一延迟单元dc1而增加的占空比的时钟信号clk的相位反相。因此,从第二延迟单元dc2输出的反相时钟信号的占空比可以变化。例如,当占空比为55%的时钟信号clk的相位被第二延迟单元dc2反相时,反相时钟信号的占空比可以变为45%。因此,可以在分支节点dn处减小反相时钟信号的占空比。

38.第三延迟单元dc3可以包括:第一分支信号线dsl1,其延迟并传输从第二延迟单元dc2提供的反相时钟信号;中继器r,其无信号衰减地传输通过第一分支信号线dsl1提供的反相时钟信号;以及第二分支信号线dsl2,其延迟并传输从中继器r输出的反相时钟信号。

39.第一分支信号线dsl1和第二分支信号线dsl2均可以是长金属线。

40.如在第一延迟单元dc1中一样,通过第三延迟单元dc3传输的反相时钟信号的占空比可以由于pvt的变化而变化。例如,尽管施加到分支节点dn的反相时钟信号的占空比是45%,但是当反相时钟信号通过第三延迟单元dc3时占空比可以增加5%,因此反相时钟信号在目标节点处可以达到50%。

41.在根据示例实施例的时钟信号延迟路径单元中,即使时钟信号clk的占空比由于pvt的变化而由第一延迟单元dc1和第二延迟单元dc2增加或减小,但是由于时钟信号clk的相位被反相,因此仍可以使通过时钟信号延迟路径单元传输的时钟信号clk的占空比维持恒定。也就是说,输入到时钟信号延迟路径单元的时钟信号clk的占空比可以与从时钟信号延迟路径单元输出的时钟信号clk的占空比基本上相同。例如,当输入到时钟信号延迟路径单元的时钟信号clk的占空比是50%时,从时钟信号延迟路径单元输出的时钟信号clk的占空比可以是50%。如图1所示,即使时钟信号clk的占空比通过第一延迟单元dc1和第三延迟单元dc3增加了预定百分比(例如,5%),也可以通过经第二延迟单元dc2使时钟信号clk反相来校正时钟信号clk的占空比,使得从第三延迟单元dc3输出的时钟信号clk的占空比变为期望的占空比(例如,50%)。

42.尽管图1示出了第一延迟单元dc1和第三延迟单元dc3中的每一者包括单个中继器r,但是这仅仅是示例,并且例如,第一延迟单元dc1和第三延迟单元dc3中的每一者可以包括多个中继器。在这种情况下,包括在第一延迟单元dc1中的中继器的数目可以等于包括在第三延迟单元dc3中的中继器的数目。

43.另外,尽管图1图示了占空比由时钟信号延迟路径部分的延迟单元增加,但是即使当占空比由延迟单元减小,也可以通过使时钟信号clk反相来校正时钟信号clk的占空比。

44.在示例实施例中,每个中继器r可以包括串联连接的偶数个反相电路。

45.在示例实施例中,长金属线可以被实现为使得长金属线的长度大于构成中继器r的反相电路之间的信号线的长度。根据示例实施例,当反相中继器ir被实现为包括串联连接的反相电路和中继器时,反相电路与中继器之间的信号线的长度可以小于长金属线的长度。

46.在图1中,由于在目标节点tn处生成的反相时钟信号的相位具有时钟信号clk的反相相位,所以可以向起始节点之前的级添加用于使时钟信号clk的相位反相的反相电路,或者可以向目标节点tn之后的级(stage)添加用于使反相时钟信号的相位反相的反相电路,以便恢复时钟信号clk的相位。

47.图2a和图2b是根据示例实施例的半导体存储器件的框图。

48.参考图2a和图2b,半导体存储器件100可以包括时钟信号端子2、命令和地址端子4、时钟信号输入缓冲器10、命令和地址生成器12、模式设置寄存器14、时延(latency)控制器16、延迟锁定环电路18、行译码器20、列译码器22、存储单元阵列24、数据读取路径单元26、数据写入路径单元28、数据输出单元30、数据输入单元32、数据选通信号输出单元34、数据选通信号输入单元36、数据端子38-1至38-n、数据选通信号端子40-1和反相数据选通信号端子40-2。

49.延迟锁定环电路18可以包括延迟锁定环18-2和时钟信号延迟路径单元18-4。

50.数据输出单元30可以包括n个数据输出驱动器(dod)30-1至30-n。

51.数据输入单元32可以包括n个数据输入驱动器(did)32-1至30-n。

52.数据选通信号输出单元34可以包括数据选通信号输出驱动器(dqsod)34-1和反相数据选通信号输出驱动器(dqsbod)34-2。

53.数据选通信号输入单元36可以包括数据选通信号输入驱动器(dqsid)36-1和反相数据选通信号输入驱动器(dqsbid)36-2。

54.如下将描述图2a和图2b所示的每个框的功能。

55.时钟信号端子2可以接收外部时钟信号eclk。命令和地址端子4可以接收命令和地址ca。

56.时钟信号输入缓冲器10可以缓冲外部时钟信号eclk,并且输出缓冲的时钟信号clk。

57.命令和地址生成器12可以响应于外部时钟信号eclk而对包括在命令和地址ca中的命令信号进行译码,以生成激活命令act、写入命令wr、读取命令rd和模式设置命令mrs。另外,命令和地址生成器12可以接收包括在命令和地址ca中的地址信号,以连同激活命令act一起生成行地址radd,连同写入命令wr或读取命令rd一起生成列地址cadd,并且连同模式设置命令mrs一起生成模式设置代码opc。

58.模式设置寄存器14可以响应于模式设置命令mrs而存储模式设置代码opc,并且设置读取时延rl和突发长度bl。

59.时延控制器16可以响应于时延时钟信号latclk而接收读取命令rd,并且生成时延控制信号la,该时延控制信号la在与读取时延rl相对应的时钟周期数之后被激活,并且在与突发长度bl相对应的时钟周期数之后被去激活。

60.延迟锁定环18-2可以接收缓冲的时钟信号clk,生成相对于外部时钟信号eclk被

锁定延迟的延迟时钟信号dclk,并且另外地生成时延时钟信号latclk。

61.时钟信号延迟路径单元18-4可以传输延迟时钟信号dclk,以生成输出数据选通信号dqso、反相输出数据选通信号dqsob、以及锁定到外部时钟信号eclk的n个内部时钟信号ick1至ickn。根据示例实施例,时钟信号延迟路径单元18-4可以包括n 2个分支延迟单元。时钟信号延迟路径单元18-4可以校正延迟时钟信号dclk的占空比的变化,该变化可能是由于用于传输延迟时钟信号dclk的信号线中的pvt的变化而发生的。例如,即使延迟时钟信号dclk的占空比由于信号线中的pvt的变化而增加(或减小),时钟信号延迟路径单元18-4也可以通过使延迟时钟信号dclk的相位在信号线的中点处反相,来减小(或增加)延迟时钟信号dclk的占空比,从而校正占空比。因此,由时钟信号延迟路径单元18-4生成的输出数据选通信号dqso、反相输出数据选通信号dqsob和n个内部时钟信号ick1至ickn的占空比可以得到校正。

62.行译码器20可以通过对行地址radd进行译码来生成多个字线选择信号wl。

63.列译码器22可以通过对列地址cadd进行译码来生成多个列选择信号csl。

64.存储单元阵列24可以包括多个存储单元(未示出),并且可以从响应于多个字线选择信号wl和多个列选择信号csl而选择的存储单元输出读取数据do,或者可以将写入数据di存储在所选择的存储单元中。多个存储单元均可以是动态存储单元,存储单元阵列24可以是动态存储单元阵列,并且半导体存储器件100可以是动态随机存取存储器(dram)器件。

65.数据读取路径单元26可以串行地转换读取数据do,以生成n条输出数据do1至don。可以在时延控制信号la的激活时段期间生成n条输出数据do1至don。例如,当输入8n位的读取数据do时,可以通过1个比特将n条输出数据do1至don输出八次。

66.数据写入路径单元28可以并行地转换n条输入数据di1至din以生成写入数据di。例如,当通过1个比特将n条输入数据di1至din输入八次时,可以生成8n位的写入数据di。

67.数据输出驱动器30-1至30-n分别可以连接到n个数据端子38-1至38-n,并且可以分别响应于内部时钟信号ick1至ickn而驱动n条输出数据do1至don以生成n条数据dq1至dqn。

68.数据输入驱动器32-1至32-n分别可以连接到n个数据端子38-1至38-n,并且可以驱动n条数据dq1至dqn以生成n条输入数据di1至din。

69.数据选通信号输出驱动器34-1可以连接到数据选通信号端子40-1,并且可以驱动输出数据选通信号dqso以生成数据选通信号dqs。反相数据选通信号输出驱动器34-2可以连接到反相数据选通信号端子40-2,并且可以驱动反相输出数据选通信号dqsob以生成反相数据选通信号dqsb。

70.数据选通信号输入驱动器36-1可以连接到数据选通信号端子40-1,并且可以驱动从外部施加的数据选通信号dqs以生成输入数据选通信号dqsi。反相数据选通信号输入驱动器36-2可以连接到反相数据选通信号端子40-2,并且可以驱动从外部施加的反相数据选通信号dqsb以生成反相输入数据选通信号dqsib。

71.图3是示出根据示例实施例的半导体存储器件的布置的图。图4是示出根据示例实施例的外围电路区域的垂直布置的图。

72.参考图3,半导体存储器件100可以包括存储单元阵列区域24-1至24-4和外围电路区域50。

73.参考图2a、图2b和图3,存储单元阵列24可以包括例如四个存储体组(memory bank group)mbg1至mbg4。存储体组mbg1至mbg4可以分别设置在存储单元阵列区域24-1至24-4中。另外,用于存储体组mbg1至mbg4中的每一者的行译码器20和列译码器22可以另外设置在存储单元阵列区域24-1至24-4中的相应存储单元阵列区域中。例如以下外围电路可以设置在外围电路区域50中:时钟信号输入缓冲器10、命令和地址生成器12、模式设置寄存器14、时延控制器16、延迟锁定环电路18、数据读取路径单元26、数据写入路径单元28、数据输出单元30、数据输入单元32、数据选通信号输出单元34、数据选通信号输入单元36、数据端子38-1至38-8、数据选通信号端子40-1以及反相数据选通信号端子40-2。

74.参考图2a至图4,外围电路可以设置在基板52上的电路区域54中。信号线区域56可以设置在电路区域54上。电源线区域58可以设置在信号线区域56上。端子区域60可以设置在电源线区域58上。可以在信号线区域56中布置信号线。可以在电源线区域58中布置电源线。可以在端子区域60中布置数据端子38-1至38-n、数据选通信号端子40-1和反相数据选通信号端子40-2。端子可以是焊盘。

75.图3所示的时钟信号延迟路径单元18-4的信号线的布置是这样的布置:当数据端子38-1至38-8、数据选通信号端子40-1和反相数据选通信号端子40-2相邻地设置时,被施加外部时钟信号eclk的时钟信号端子2被设置为相对地远离数据端子38-1至38-8、数据选通信号端子40-1和反相数据选通信号端40-2,时钟信号输入缓冲器10和延迟锁定环18-2与时钟信号端子2相邻地设置,并且数据输出驱动器30-1至30-8、数据选通信号输出驱动器34-1和反相数据选通信号输出驱动器34-2分别与数据端子38-1至38-n、数据选通信号端子40-1和反相数据选通信号端子40-2相邻地设置。

76.现在将进一步参考图2a至图4描述时钟信号延迟路径单元18-4的信号线的布置。

77.第一节点n1可以是延迟锁定环18-2的输出节点。第二节点n2可以是分支起始节点。第三节点n3和第四节点n4可以是第一分支节点。第五节点n5至第八节点n8可以是第二分支节点。第九节点n9至第十三节点n13可以是第三分支节点。第十四节点n14至第十七节点n17和第二十节点n20至第二十三节点n23可以是数据输出驱动器30-1至30-8的输入节点。第十八节点n18和第十九节点n19可以是数据选通信号输出驱动器34-1和反相数据选通信号输出驱动器34-2的输入节点。第二十四节点n24和第二十五节点n25可以是附加节点。

78.第一节点n1可以对应于图1所示的起始节点sn。第二节点n2可以对应于分支节点dn。第十四节点n14至第二十三节点n23可以对应于目标节点tn。

79.从分支起始节点(第二节点n2)到第一分支节点(第三节点n3和第四节点n4)的第一信号线sl21和sl22可以具有相同的长度和宽度。

80.从第一分支节点(第三节点n3)到第二分支节点(第五节点n5和第六节点n6)的第二信号线sl31和sl32以及从第一分支节点(第四节点n4)到第二分支节点(第七节点n7和第八节点n8)的第二信号线sl33和sl34可以具有相同的长度和宽度。

81.从第二分支节点(第五节点n5、第六节点n6、第七节点n7和第八节点n8)到所对应的第三分支节点((第九节点n9、第十节点n10)、第十一节点n11、(第十二节点n12、第十三节点n13)和第二十四节点n24)的第三信号线(sl41、sl42)、sl44、(sl45、sl46)和sl47可以具有相同的长度和宽度。

82.第三信号线sl43和sl48可以具有与第三信号线sl41的长度相同的长度,也可以不

具有与第三信号线sl41的长度相同的长度。

83.从第三分支节点(第九节点n9、第十节点n10、第十一节点n11、第十二节点n12、第十三节点n13和第二十四节点n24)到所对应的第四分支节点((第十四节点n14、第十五节点n15)、(第十六节点n16、第十七节点n17)、(第十八节点n18、第十九节点n19)、(第二十节点n20、第二十一节点n21)、(第二十二节点n22、第二十三节点n23)和第二十五节点n25)的第四信号线(sl49、sl50)、(sl51、sl52)、(sl53、sl54)、(sl55、sl56)、(sl57、sl58)和sl59可以具有相同的长度和宽度。

84.路由信号线sl1以及第一信号线sl21和sl22至第四信号线sl49至sl59可以设置在信号线区域56中。沿水平方向设置的信号线和沿垂直方向设置的信号线可以设置在信号线区域56的不同层上。尽管在图中路由信号线sl1以及第一信号线sl21和sl22至第四信号线sl49至sl59被连续地布置在第一节点n1至第二十五节点n25之间,但是它们可以通过中继器(未示出)或组件(未示出)连接,并且所述中继器或所述组件可以设置在电路区域54中。

85.如上所述,时钟信号延迟路径单元18-4可以包括两条第一信号线sl21和sl22以及最多2m条第四信号线sl49至sl59,这最多2m条第四信号线sl49至sl59将两个第一分支节点(第三节点n3和第四节点n4)连接到被依次布置以便在树结构中从分支起始节点n2分支m次的最多2m个第四分支节点(第十四节点n14至二十三节点n23和第二十五节点n25)。

86.图5是示出根据示例实施例的时钟信号延迟路径单元的配置的图。

87.参考图1和图5,可以在从第一节点n1到中间节点mn的路由信号线sl11上设置五个中继器r。可以在第一节点n1与中间节点mn之间设置五个第一延迟单元dc1。五个中继器r之间的信号线可以对应于第一路由信号线rsl1或第二路由信号线rsl2,并且可以是长金属线。中继器r可以无信号衰减地传输延迟时钟信号dclk。

88.占空比校正器dcc、多路复用器mux和反相中继器ir可以设置在从中间节点mn起的中间信号线sl12与第二节点n2之间。中间节点mn与第二节点n2之间的配置可以对应于第二延迟单元dc2。

89.占空比校正器dcc可以使用内部时钟信号对ick和ickb来校正从中间节点mn传输的延迟时钟信号dclk的占空比。

90.多路复用器mux响应于选择信号sel,可以选择从中间节点mn传输的延迟时钟信号dclk,或者可以选择从占空比校正器dcc传输的延迟时钟信号dclk。可以通过图2a所示的施加到模式设置寄存器14的模式设置代码opc另外设置选择信号sel。

91.反相中继器ir可以具有其中反相电路(未示出)和中继器r(未示出)串联连接的配置。反相电路可以使从多路复用器mux传输的延迟时钟信号dclk的相位反相,以生成反相延迟时钟信号dclkb,并且中继器r可以无信号衰减地传输反相延迟时钟信号dclkb。在实现方式中,可以采用在中间节点mn与第二节点n2之间不提供中继器r(未示出)的配置。

92.中继器r可以设置在第一信号线sl21和sl22至第四信号线sl49至sl59的每一条信号线上。可以在从第二节点n2到第四分支节点(第十四节点n14)的分支信号线中配置包括四个第三延迟单元dc3的分支延迟单元。可以从第二节点n2到第四分支节点(第十四节点n14至第二十三节点n23)配置十个分支延迟单元。中继器r之间的信号线可以对应于第一分支信号线dsl1或第二分支信号线dsl2并且可以是长金属线。也就是说,第一信号线sl21和sl22中的每一条至第四信号线sl49至sl59中的每一条可以是长金属线。

93.可以在第十四节点n14至第二十三节点n23与数据输出驱动器30-1至30-8、数据选通信号输出驱动器34-1和反相数据选通信号输出驱动器34-2之间另外提供分相器ps和选择器mux。分相器ps和选择器mux可以对内部时钟信号ick1至ick8、数据输出选通信号dqso和反相数据输出选通信号dqsob的相位进行分相或者反相分相,以交替地输出相位差为180度的内部时钟信号对、数据输出选通信号对和反相数据输出选通信号对。

94.中继器r可以连接在第二十四节点n24与第二十五节点n25之间。分相器ps可以连接到第二十五节点n25,并且分相器ps可以通过对内部时钟信号ick9的相位进行分相或者反相分相来生成相位差为180度的另外的内部时钟信号对。

95.图6是示出根据示例实施例的时钟信号延迟路径单元的配置的图。

96.除了图5的配置中的设置在中间节点mn与第二节点n2之间的反相中继器ir被替换为中继器r,并且图5的配置中的连接在第二节点n2、第三节点n3和第四节点n4之间的中继器r被替换为时钟信号延迟路径单元18-4’中的反相中继器ir之外,关于图6描述的示例实施例可以与图5的时钟信号延迟路径单元18-4的示例实施例相同。反相中继器ir可以具有其中反相电路(未示出)和中继器r(未示出)串联连接的配置。

97.参考图6,时钟信号延迟路径单元18-4’可以被配置为紧接在第二节点n2(即,分支起始节点)之后使延迟时钟信号dclk的相位反相,而不是紧接在第二节点n2之前使延迟时钟信号dclk的相位反相。

98.图7是示出根据示例实施例的时钟信号延迟路径单元的配置的图。

99.除了图5的配置中的紧接在中间节点mn之前的中继器r被替换为反相中继器ir,并且图5的配置中的设置在中间节点mn与第二节点n2之间的反相中继器ir被替换为时钟信号延迟路径单元18-4”中的中继器r之外,关于图7描述的示例实施例可以与图5的时钟信号延迟路径单元18-4的配置相同。

100.反相中继器ir可以具有其中反相电路(未示出)和中继器r(未示出)串联连接的配置。

101.参考图7,时钟信号延迟路径单元18-4”可以被配置为紧接在中间节点mn之前使延迟时钟信号dclk的相位反相,而不是紧接在第二节点n2(即,分支起始节点)之前使延迟时钟信号dclk的相位反相。

102.延迟时钟信号dclk的相位由图5至图7的时钟信号延迟路径单元18-4、18-4’和18-4”中的反相中继器ir反相。为了恢复延迟时钟信号dclk的相位,延迟锁定环18-2可以被配置为提前使延迟时钟信号dclk反相,并且将反相延迟时钟信号施加到第一节点n1。作为另一示例,分相器ps可以被配置为使内部时钟信号ick1至ick8、输出数据选通信号dqso和反相输出数据选通信号dqsob反相以执行上述分相操作。

103.在示例实施例中,反相中继器ir可以设置在与时钟信号延迟路径单元18-4、18-4’和18-4”中的位置不同的各种位置处,即,不同于参考图5至图7的以上描述。例如,可以将包括四个中继器r的第一中继器组至包括最多2m个中继器的第m中继器组之一中包括的中继器r配置为反相中继器ir。如果在时钟信号延迟路径单元18-4’和18-4”中在从第一节点n1到第四分支节点(第十四节点n14至第二十三节点n23)的信号线中发生的总占空比的变化是10%,则可以在占空比的变化为5%的位置处提供用于使延迟时钟信号dclk反相的反相中继器ir。

104.在示例实施例中,图5至图7的时钟信号延迟路径单元18-4、18-4’和18-4”中的每一者可以被配置为不仅包括占空比校正器dcc和多路复用器mux。另外,图5至图7的时钟信号延迟路径单元18-4、18-4’和18-4”中的每一者还可以被配置为不仅包括分相器ps和选择器mux。例如,如果图2a和图2b所示的半导体存储器件被配置为以单数据速率(sdr)输出数据而不是以双数据速率(ddr)输出数据,则图5至图7的时钟信号延迟路径单元18-4、18-4’和18-4”中的每一者可以被配置为不仅包括分相器ps和选择器mux。

105.图8a和图8b是示出根据示例实施例的中继器的配置的图。

106.参考图8a,中继器r可以包括串联连接的两个反相电路inv1和inv2。

107.反相电路inv1可以包括单个反相器i。

108.反相电路inv2可以包括并联连接的两个反相器i。反相电路inv2的大小可以为反相电路inv1的两倍。在另一实现方式中,反相电路inv2的大小可以为反相电路inv1的三倍或更多倍。

109.参考图8b,中继器r可以包括串联连接的四个反相电路inv1至inv4。

110.反相电路inv1和反相电路inv2可以具有与参考图8a描述的配置相同的配置。

111.反相电路inv3可以包括并联连接的四个反相器i。反相电路inv3的大小可以为反相电路inv1的四倍。

112.反相电路inv4可以包括并联连接的六个反相器i。反相电路inv4的大小可以为反相电路inv1的六倍。

113.在另一实现方式中,与所示出的不同,反相电路inv1和反相电路inv2可以具有相同的大小,反相电路inv3的大小可以为反相电路inv1的两倍或更多倍,并且反相电路inv4的大小可以为反相电路inv1的三倍或更多倍。

114.如参考图8a和图8b所描述的,中继器r可以包括串联连接的偶数个反相电路,并且可以被配置为使得反相电路的大小与前一级中的反相电路的大小相同或者大于前一级中的反相电路的大小。图8a和图8b所示的中继器r可以驱动延迟时钟信号dclk以生成具有相同相位且没有信号衰减的延迟时钟信号dclk。

115.图9a和图9b是示出根据示例实施例的反相中继器的配置的图。

116.参考图9a,反相中继器ir可以具有向图8a的中继器r的配置添加反相电路inv3的配置。

117.参考图9b,反相中继器ir可以具有向图8b的中继器r的配置添加反相电路inv5的配置。

118.如参考图9a和图9b所描述的,反相中继器ir可以包括串联连接的奇数个反相电路,并且可以被配置为使得反相电路的大小与前一级中的反相电路的大小相同或者大于前一级中的反相电路的大小。

119.图9a和图9b所示的反相中继器ir可以驱动延迟时钟信号dclk以生成具有相反相位的反相延迟时钟信号dclkb。

120.根据示例实施例,图8a至图9b所示的每一个中继器r和每一个反相中继器ir的反相电路之间的信号线的长度可以小于图5、图6和图7所示的中继器r之间的信号线的长度。

121.图10是示出根据示例实施例的中继器的逆变器的配置的图。

122.参考图10,反相器i可以包括pmos晶体管p(具有连接到电源电压vdd的源极、连接

到输入节点in的栅极和连接到输出节点on的漏极)和nmos晶体管n(具有连接到地电压的源极、耦接到输入节点in的栅极和耦接到输出节点on的漏极)。反相器i可以使施加到输入节点in的信号反相,并且通过输出节点on输出反相信号。

123.图11是用于描述根据示例实施例的时钟信号延迟路径单元的操作的波形图。

124.参考图5至图11,可以在第一节点n1处生成占空比为50%的延迟时钟信号dclk。

125.延迟时钟信号dclk可以通过连接在第一节点n1与中间节点mn之间的路由信号线sl1和连接到路由信号线sl1的中继器r来传输。此时,通过反相器i的nmos晶体管n的信号传输速率可能由于pvt的变化而变得低于通过其pmos晶体管p的信号传输速率,所述反相器i构成与路由信号线sl1连接的中继器r。因此,延迟时钟信号dclk从“高”电平到“低”电平的转变可以被延迟,并且因此可以在中间节点mn处生成占空比大于50%的延迟时钟信号dclk。例如,每当延迟时钟信号dclk通过中继器r时占空比可以逐渐增加,以在中间节点mn处达到55%。

126.可以通过多路复用器mux传输中间节点mn的延迟时钟信号dclk。当从中间节点mn通过多路复用器mux或者通过占空比校正器dcc和多路复用器mux传输延迟时钟信号dclk时,因为信号线短,所以可以忽略由于pvt变化导致的占空比变化。因此,从中间节点mn通过多路复用器mux或者通过占空比校正器dcc和多路复用器mux传输的延迟时钟信号dclk的相位通过反相中继器ir被反相,因此可以在第二节点n2处生成占空比为45%的反相延迟时钟信号dclkb。

127.可以经由中继器r通过从第二节点n2到第四分支节点(第十四节点n14至第二十三节点n23)的分支信号线传输反相延迟时钟信号dclkb。此时,通过反相器i的nmos晶体管n的信号传输速率可能由于pvt的变化而变得低于通过其pmos晶体管p的信号传输速率,所述反相器i构成存在于从第二节点n2到第四分支节点(第十四节点n14至第二十三节点n23)的第一信号线至第四信号线上的中继器r。因此,在第二节点n2处的占空比为45%的反相延迟时钟信号dclkb从“高”电平到“低”电平的转变被延迟,并且因此可以在第四分支节点(第十四节点n14至第二十三节点n23)中的每一个处生成占空比为50%的反相延迟时钟信号dclkb。

128.另外地,分相器ps和选择器mux可以使第四分支节点(第十四节点n14至第二十三节点n23)处的占空比为50%的反相延迟时钟信号dclkb的相位反相,以生成占空比为50%的内部时钟信号ick1至ick8、输出数据选通信号dqso和反相输出数据选通信号dqsob。例如,当连接到第十四节点n14至第二十三节点n23的分相器ps和选择器mux的输出节点是n14’至n23’时,可以在输出节点n14’至n23’处生成占空比为50%的内部时钟信号ick1至ick8、输出数据选通信号dqso和反相输出数据选通信号dqsob。

129.图12是示出根据示例实施例的占空比校正器的配置的框图。如下将描述图12所示的每个框的功能。

130.占空比校正器(dcc)可以包括占空比检测器70和占空比调节器72。

131.占空比检测器70可以生成第一泵浦电压和第二泵浦电压(例如,通过响应于具有180度相位差的内部时钟信号ick和ickb而执行泵浦操作),将第一泵浦电压与第二泵浦电压进行比较以生成比较输出信号,以及通过根据比较输出信号执行向上计数或向下计数操作来生成代码code(具有预定位数)和反转代码codeb(具有预定位数)。

132.占空比调节器72可以响应于代码code和反转代码codeb,调节中间节点mn的延迟

时钟信号dclk的上升转变的斜率和下降转变的斜率,以控制延迟时钟信号dclk的占空比。

133.图13是示出根据示例实施例的占空比检测器的配置的框图。如下将描述图13所示的每个框的功能。

134.占空比检测器70可以包括电荷泵70-2、比较器70-4和计数器70-6。

135.电荷泵70-2可以通过响应于内部时钟信号ick而执行泵浦操作来生成第一泵浦电压cp1,以及通过响应于反相内部时钟信号ickb而执行泵浦操作来生成第二泵浦电压cp2。

136.比较器70-4可以将第一泵浦电压cp1与第二泵浦电压cp2进行比较,以生成比较输出信号cout。

137.计数器70-6可以通过响应于比较输出信号cout而执行向上计数或向下计数操作来生成代码code(具有预定位数)和反转代码codeb(具有预定位数)。

138.图14是示出根据示例实施例的占空比调节器的配置的电路图。

139.参考图14,占空比调节器72可以包括串联连接的第一调节器72-2和第二调节器72-4。

140.第一调节器72-2和第二调节器72-4均可以包括并联连接的i 1个反相器,即,第一反相器i1和i个第二反相器i21至i2i。

141.第一反相器i1可以包括:连接在电源电压vdd与第一输出节点on1或第二输出节点on2之间的第一pmos晶体管p11,以及连接在第一输出节点on1或第二输出节点on2与地电压之间的第一nmos晶体管n11。

142.第二反相器i21至i2i中的每一者可以包括:串联连接在电源电压vdd与第一输出节点on1或第二输出节点on2之间的第二pmos晶体管p21、

…

、或pi1和第三pmos晶体管p22、

…

、或pi2,以及串联连接在第一输出节点on1或第二输出节点on2与地电压之间的第三nmos晶体管n22、...、或ni2和第二nmos晶体管n21、...、或ni1。

143.第一调节器72-2的第一反相器i1可以使中间节点mn的延迟时钟信号dclk反相并且向第一输出节点on1输出相位与延迟时钟信号dclk的相位相反的反相时钟信号ina。

144.第一调节器72-2的第二反相器i21至i2i中的每一者可以响应于中间节点mn的延迟时钟信号dclk以及i位代码code中的对应位c1、...、或ci,调节反相时钟信号ina的上升转变的斜率或下降转变的斜率,以控制反相时钟信号ina的占空比。

145.第二调节器72-4的第一反相器i1可以使反相时钟信号ina反相并且向第二输出节点on2输出相位与延迟时钟信号dclk的相位相同的时钟信号inb。

146.第二调节器72-4的第二反相器i21至i2i中的每一者可以响应于反相时钟信号ina以及i位反转代码codeb中的对应位c1b、...、或cib,调节时钟信号inb的上升转变的斜率或下降转变的斜率,以控制时钟信号inb的占空比。

147.图15a和图15b是示出根据示例实施例的分相器和选择器的配置的图。

148.参考图15a,分相器ps可以包括第三反相器i3至第十反相器i10。

149.第三反相器i3至第七反相器i7可以接收第十四节点n14的反相延迟时钟信号dclkb,使其反相,并且输出相位与反相延迟时钟信号dclkb的相位相反的时钟信号ck。

150.第三反相器i3至第五反相器i5和第八反相器i8至第十反相器i10可以接收反相延迟时钟信号dclkb,并且输出相位与反相延迟时钟信号dclkb的相位相同的反相时钟信号ckb。

151.选择器mux可以接收时钟信号ck和反相时钟信号ckb,响应于反相时钟信号ckb选择时钟信号ck,并且响应于时钟信号ck选择反相时钟信号ckb。

152.参考图15b,分相器ps’可以包括第三反相器i3至第九反相器i9。

153.第三反相器i3至第六反相器i6可以接收第十四节点n14的反相延迟时钟信号dclkb,使其反相,并且输出相位与反相延迟时钟信号dclkb的相位相同的反相时钟信号ckb。

154.第三反相器i3、第四反相器i4和第七反相器i7至第九反相器i9可以使反相延迟时钟信号dclkb反相并且输出相位与反相延迟时钟信号dclkb的相位相反的时钟信号ck。

155.选择器mux可以接收反相时钟信号ckb和时钟信号ck,响应于时钟信号ck选择反相时钟信号ckb,并且响应于反相时钟信号ckb选择时钟信号ck。

156.图16是示出根据示例实施例的时钟信号延迟路径单元的图。

157.时钟信号延迟路径单元可以包括第一延迟单元dc1’、第二延迟单元dc2’和第三延迟单元dc3’。

158.除了所有节点(即,起始节点sn、中间节点mn、分支节点dn和目标节点tn)都是成对(即,起始节点对sn1和sn2、中间节点对mn1和mn2、分支节点对dn1和dn2以及目标节点对tn1和tn2)提供的,所有信号线(即,第一路由信号线rsl1、第二路由信号线rsl2、第一中间信号线msl1、第二中间信号线msl2、第一分支信号线dsl1和第二分支信号线dsl2)都是成对(即,第一路由信号线对rslp1、第二路由信号线对rslp2、第一中间信号线对mslp1、第二中间信号线对mslp2、第一分支信号线对dslp1和第二分支信号线对dslp2)提供的,并且传输时钟信号对clk和clkb代替时钟信号clk之外,图16所示的时钟信号延迟路径单元可以与图1所示的时钟信号延迟路径单元相同。

159.可以通过参考图1的时钟信号延迟路径单元的操作容易地理解图16所示的时钟信号延迟路径单元的操作。

160.图17a和图17b是示出根据示例实施例的半导体存储器件200的框图。如下将描述图17a和图17b所示的每个框。

161.半导体存储器件200可以包括控制信号端子110-2、读取使能信号端子110-4、反相读取使能信号端子110-6、读取使能信号缓冲器(reb)112-2、反相读取使能信号缓冲器(rebb)112-4、控制逻辑单元114、电压发生器116、行译码器118、列译码器120、存储单元阵列122、读取使能信号延迟路径单元124、页面缓冲器126、数据写入路径单元128、数据读取路径单元130、数据输出单元132、数据输入单元134、数据选通信号输入单元136、数据选通信号输出单元138、数据端子140-1至140-n、数据选通信号端子142-1和反相数据选通信号端子142-2。

162.数据输出单元132可以包括n个数据输出驱动器(dod)132-1至132-n。

163.数据输入单元134可以包括n个数据输入驱动器(did)134-1至134-n。

164.数据选通信号输入单元136可以包括数据选通信号输入驱动器(dqsid)136-2和反相数据选通信号输入驱动器(dqsibd)136-4。

165.数据选通信号输出单元138可以包括数据选通信号输出驱动器(dqsod)138-2和反相数据选通信号输出驱动器(dqsobd)138-4。

166.控制信号端子110-2可以接收控制信号con(例如,命令使能信号ce、写入使能信号

we、命令锁存使能信号cle和地址锁存使能信号ale(未示出))。

167.读取使能信号端子110-4可以接收读取使能信号re。

168.反相读取使能信号端子110-6可以接收反相读取使能信号reb。

169.读取使能信号缓冲器(reb)112-2可以缓冲读取使能信号re,并且输出缓冲的读取使能信号reb。

170.反相读取使能信号缓冲器(rebb)112-4可以缓冲反相读取使能信号reb,并且输出缓冲的反相读取使能信号rebb。

171.控制逻辑单元114可以响应于控制信号con、缓冲的读取使能信号reb和缓冲的反相读取使能信号rebb,而生成编程命令pgm和读取命令rd。控制逻辑单元114可以响应于命令锁存使能信号cle和写入使能信号we而接收命令com,并且可以响应于地址锁存使能信号ale和写入使能信号we而接收地址add,或者可以响应于地址锁存使能信号ale、缓冲的读取使能信号reb和缓冲的反相读取使能信号rebb而接收地址add。

172.电压发生器116可以接收电源电压vdd和地电压vss,响应于编程命令pgm而生成用于编程操作的驱动电压dv,以及响应于读取命令rd而生成用于读取操作的驱动电压dv。

173.行译码器118可以响应于编程命令pgm而接收用于编程操作的驱动电压dv,并且对行地址radd进行译码以驱动多个字线选择信号wl、多个源极线选择信号ssl和多个地选择信号gsl,或者可以响应于读取命令rd而接收用于读取操作的驱动电压dv,并且对行地址radd进行译码以驱动多个字线选择信号wl、多个源极线选择信号ssl和多个地选择信号gsl。

174.列译码器120可以接收列地址cadd并对其进行译码以生成多个列选择信号csl。

175.存储单元阵列122可以包括多个存储单元。存储单元阵列122可以响应于编程命令pgm而将编程数据pd编程到存储单元(由多个字线选择信号wl、多个源极线选择信号ssl、多个地选择信号gsl和多个列选择信号csl选择的)中,并且可以响应于读取命令rd而从所选择的存储单元输出读取数据rd。多个存储单元可以是闪速存储单元,存储单元阵列122可以是闪速存储单元阵列,并且半导体存储器件200可以是闪速存储器件。

176.读取使能信号延迟路径单元124可以响应于读取命令rd,而通过信号线对来传输缓冲的读取使能信号reb和缓冲的反相读取使能信号rebb,以生成输出数据选通信号dqso、反相输出数据选通信号dqsob和n个内部时钟信号ick1至ickn。

177.读取使能信号延迟路径单元124可以校正缓冲的读取使能信号reb的占空比和缓冲的反相读取使能信号rebb的占空比,这些占空比可能由于传输缓冲的读取使能信号reb和缓冲的反相读取使能信号rebb的信号线对中的pvt的变化而发生改变。例如,即使在信号线对中缓冲的读取使能信号reb的占空比和缓冲的反相读取使能信号rebb的占空比由于pvt的变化而增大(或减小),读取使能信号延迟路径单元124也可以减小(或增大)缓冲的读取使能信号reb的占空比和缓冲的反相读取使能信号rebb的占空比,以通过在信号线对的中点处使缓冲的读取使能信号reb的相位和缓冲的反相读取使能信号rebb的相位反相来校正占空比。因此,可以校正从读取使能信号延迟路径单元124生成的输出数据选通信号dqso、反相输出数据选通信号dqsob和n个内部时钟信号ick1至ickn的占空比。

178.页面缓冲器126可以响应于编程命令pgm而缓冲写入数据di以将其作为编程数据pd输出,并且可以响应于读取命令rd而缓冲读取数据rd以将其作为读取数据do输出。

179.数据写入路径单元128可以响应于编程命令pgm而将输入数据di转换成并行数据,以输出写入数据di。

180.数据读取路径单元130可以响应于读取命令rd而将读取数据do转换成串行数据,以输出输出数据do。

181.数据输出驱动器132-1至132-n可以分别连接到n个数据端子140-1至140-n,并且可以驱动n条输出数据do1至don以生成n条数据dq1至dqn。

182.数据输入驱动器134-1至134-n分别可以连接到n个数据端子140-1至140-n,并且可以驱动n条数据dq1至dqn以生成n条输入数据di1至din。

183.数据选通信号输入驱动器136-2、反相数据选通信号输入驱动器136-4、数据选通信号输出驱动器138-2和反相数据选通信号输出驱动器138-4可以分别执行与参考图2b描述的数据选通信号输入驱动器36-1、反相数据选通信号输入驱动器36-2、数据选通信号输出驱动器34-1和反相数据选通信号输出驱动器34-2的功能相同的功能。

184.图17a和图17b所示的半导体存储器件200的读取使能信号缓冲器112-2的输出节点和反相读取使能信号缓冲器112-4的反相输出节点可以分别对应于图16所示的起始节点对sn1和sn2。图17a和图17b所示的半导体存储器件200的读取使能信号延迟路径单元124与参考图5至图7描述的半导体存储器件100(其中每条信号线是单条信号线)的时钟信号延迟路径单元18-4、18-4’和18-4”的不同之处可以在于如图16所示那样可以成对地提供信号线。

185.类似地,读取使能信号延迟路径单元124与参考图5至图7描述的半导体存储器件100(其中第一节点n1和第四分支节点(第十四节点n14至第二十三节点至n23)中的每一个节点是单个节点)的时钟信号延迟路径单元18-4、18-4’和18-4”的不同之处可以在于如图16所示那样可以成对地提供节点。

186.如图16所示,缓冲的读取使能信号reb的相位和缓冲的反相读取使能信号rebb的相位由反相中继器ir反相。为了恢复缓冲的读取使能信号reb的相位和缓冲的反相读取使能信号rebb的相位,可以以交叉方式将缓冲的读取使能信号reb和缓冲的反相读取使能信号rebb施加到第一节点对。

187.作为另一示例,可以在成对的第四分支节点(第十四节点n14至二十三节点n23)、数据输出驱动器134-1至134-n、数据选通信号输出驱动器136-2和反相数据选通信号输出驱动器136-4之间设置选择器。选择器可以被配置为交替地输出内部时钟信号对、数据输出选通信号对和反相数据输出选通信号对当中的一组反相内部时钟信号、反相数据输出选通信号和数据输出选通信号以及一组内部时钟信号、数据输出选通信号和反相数据输出选通信号。

188.图18a和图18b是示出根据示例实施例的中继器r的配置的图。

189.图18a和图18b对应于传输图17a和图17b所示的缓冲的读取使能信号reb和缓冲的反相读取使能信号rebb的情况。

190.参考图18a,中继器r可以包括串联连接的两个反相电路inv1和inv2。

191.反相电路inv1可以包括单个反相放大器cml。

192.反相电路inv2可以包括并联连接的两个反相放大器cml。

193.反相放大器cml可以是反相电流模式逻辑差分放大器。

194.反相电路inv2的大小可以为反相电路inv1的两倍。在另一实现方式中,与所示出的不同,反相电路inv2的大小可以与反相电路inv1相同或为反相电路inv1三倍或更多倍。

195.参考图18b,中继器r可以包括串联连接的四个反相电路inv1至inv4。

196.反相电路inv1和反相电路inv2可以具有与参考图18a描述的配置相同的配置。

197.反相电路inv3可以包括并联连接的三个反相放大器cml。反相电路inv3的大小可以为反相电路inv1的三倍。

198.反相电路inv4可以包括并联连接的四个反相放大器cml。反相电路inv4的大小可以为反相电路inv1的四倍。

199.反相放大器cml可以是反相电流模式逻辑差分放大器。

200.在另一实现方式中,与所示出的不同,反相电路inv1和反相电路inv2具有相同的大小,反相电路inv3的大小可以为反相电路inv1的两倍或更多倍,并且反相电路inv4的大小可以为反相电路inv1的三倍或更多倍。

201.如参考图18a和图18b所描述的,中继器r可以包括串联连接的偶数个反相电路,并且可以被配置为使得反相电路的大小与前一级中的反相电路的大小相同或者大于前一级中的反相电路的大小

202.图19a和图19b是示出根据示例实施例的反相中继器的配置的图。

203.参考图19a,除了图19a的反相中继器ir的反相电路inv1的输出信号线对和反相电路inv2的输入信号线对交叉耦接之外,反相中继器ir可以具有与图18a所示的中继器r的配置相同的配置。

204.参考图19b,除了图19b的反相中继器ir的反相电路inv2的输出信号线对和反相电路inv3的输入信号线对交叉耦接之外,反相中继器ir可以具有与图18b所示的中继器r的配置相同的配置。

205.在另一实现方式中,与所示出的不同,反相中继器ir可以通过交叉耦接图19b的反相电路inv1的输出信号线对和反相电路inv2的输入信号线对来配置。

206.如参考图19a和图19b所描述的,反相中继器ir可以包括串联连接的偶数个反相电路,并且可以通过将前一级中的反相电路的输出信号线对交叉耦接到(在两个依次连接的反相电路之间)后一级中的反相电路的输入信号线对来配置。因此,反相中继器ir可以使输入信号的相位反相。此外,反相中继器ir可以被配置为使得后一级中的反相电路的大小与前一级中的反相电路的大小相同或者大于前一级中的反相电路的大小。

207.图20是示出根据示例实施例的反相电流模式逻辑差分放大器的配置的图。

208.参考图20,反相电流模式逻辑差分放大器cml可以包括第一电阻器r1(连接在电源电压vdd与反相输出节点onb之间)、第二电阻器r2(连接在电源电压vdd与输出节点on之间)、第一nmos晶体管n1(具有连接到反相输出节点onb的漏极、连接到输入节点in的栅极和连接到中间节点mn的源极)、第二nmos晶体管n2(具有连接到输出节点on的漏极、连接到反相输入节点inb的栅极和连接到中间节点mn的源极)、以及第三nmos晶体管n3(具有连接到中间节点mn的漏极、被施加偏置电压vbias的栅极和连接到地电压的源极)。

209.当第三nmos晶体管n3响应于偏置电压vbias而被导通时,可以启用反相电流模式逻辑差分放大器cml。

210.当反相电流模式逻辑差分放大器cml被启用并且施加到输入节点in的输入信号的

电压电平高于施加到反相输入节点inb的反相输入信号的电压电平时,流过第一nmos晶体管n1的电流大于流过第二nmos晶体管n2的电流,因此反相输出节点onb的电平变得低于输出节点on的电平。也就是说,可以生成处于“低”电平的反相输出信号和处于“高”电平的输出信号。

211.另一方面,当反相电流模式逻辑差分放大器cml被启用并且施加到输入节点in的输入信号的电压电平低于施加到反相输入节点inb的反相输入信号的电压电平时,可以生成处于“低”电平的输出信号和处于“高”电平的反相输出信号。

212.尽管未示出,但是根据示例实施例的时钟信号延迟路径单元可以用于使数据选通信号对(数据选通信号dqs和反相数据选通信号dqsb)延迟并且无信号衰减地传输该数据选通信号对。

213.通过总结和回故,时钟信号延迟路径单元可以包括信号线上的中继器以便无信号衰减地传输延迟时钟信号,所述信号衰减可能是由从延迟锁定环(其生成延迟时钟信号)的输出节点(即,信号源)到目标块的信号线的长长度而产生的。

214.如上所述,实施例可以提供一种被配置为校正信号线中的时钟信号的占空比的变化(例如,由于工艺、电压和温度的变化而导致的)的时钟信号延迟路径单元,以及一种包括所述时钟信号延迟路径单元的半导体存储器件。

215.实施例可以提供一种被配置为通过在信号线中发生的总占空比的变化(例如,由于工艺、电压和温度的变化而导致的)减半的位置处使时钟信号的相位反相来校正时钟信号的占空比的时钟信号延迟路径单元。因此,可以提高包括该时钟信号延迟路径单元的半导体存储器件的操作的可靠性。

216.已在本文中公开了示例实施例,并且尽管采用了特定术语,但是它们仅在通用和描述性意义上被使用和解释,而不用于限制的目的。在一些情况下,如从提交本技术时起将对本领域的普通技术人员而言显而易见的,除非另外具体地指示,否则结合特定实施例描述的特征、特性和/或元素可以单独使用,也可以与结合其他实施例描述的特征、特性和/或元素相结合地使用。因此,本领域的技术人员将理解,在不脱离如所附权利要求中阐述的本发明的精神和范围的情况下,可以做出形式和细节上的各种改变。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。