技术特征:

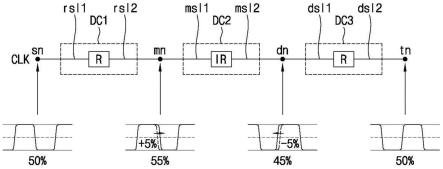

1.一种时钟信号延迟路径单元,包括:至少一个第一延迟单元,每一个所述第一延迟单元包括:用于延迟并传输时钟信号的第一路由信号线、用于无信号衰减地传输通过所述第一路由信号线传输的所述时钟信号的第一中继器、以及用于延迟并传输从所述第一中继器输出的所述时钟信号的第二路由信号线;第二延迟单元,所述第二延迟单元包括用于使从所述至少一个第一延迟单元提供的所述时钟信号反相以生成反相时钟信号的第一反相电路;以及至少一个第三延迟单元,每一个所述第三延迟单元包括用于延迟并传输从所述第二延迟单元提供的所述反相时钟信号的第一分支信号线、用于无信号衰减地传输通过所述第一分支信号线传输的所述反相时钟信号的第二中继器、以及用于延迟并传输从所述第二中继器输出的所述反相时钟信号的第二分支信号线,其中,所述第一路由信号线、所述第二路由信号线、所述第一分支信号线和所述第二分支信号线均是长金属线。2.根据权利要求1所述的时钟信号延迟路径单元,其中,所述至少一个第一延迟单元中的每一个中包括的第一中继器的数目等于所述至少一个第三延迟单元中的每一个中包括的第二中继器的数目。3.根据权利要求1所述的时钟信号延迟路径单元,其中,所述第二延迟单元还包括:第一中间信号线,所述第一中间信号线用于延迟从所述至少一个第一延迟单元提供的所述时钟信号,并且将延迟的所述时钟信号传输到所述第一反相电路;第三中继器,所述第三中继器被配置为无信号衰减地传输从所述第一反相电路输出的所述反相时钟信号;以及第二中间信号线,所述第二中间信号线用于延迟从所述第三中继器输出的所述反相时钟信号,其中,所述第一中间信号线和所述第二中间信号线均是长金属线。4.根据权利要求3所述的时钟信号延迟路径单元,其中:所述第三中继器包括串联连接的偶数个第二反相电路,并且所述第一中间信号线和所述第二中间信号线中的每一者的长度大于所述第一反相电路与所述第三中继器之间的信号线的长度或者大于串联连接的所述偶数个第二反相电路之间的信号线的长度。5.根据权利要求4所述的时钟信号延迟路径单元,其中,所述第一反相电路与所述第二反相电路均包括至少一个反相器。6.根据权利要求1所述的时钟信号延迟路径单元,其中:所述第一中继器包括串联连接的偶数个第三反相电路,所述第二中继器包括串联连接的偶数个第四反相电路,并且所述第一路由信号线和所述第二路由信号线中的每一者的长度大于所述第三反相电路之间的信号线的长度,或者所述第一分支信号线和所述第二分支信号线中的每一者的长度大于所述第四反相电路之间的信号线的长度。7.根据权利要求6所述的时钟信号延迟路径单元,其中,所述第三反相电路和所述第四反相电路均包括至少一个反相器。

8.根据权利要求1所述的时钟信号延迟路径单元,还包括:第五反相电路,所述第五反相电路被配置为:在将所述时钟信号施加到所述至少一个第一延迟单元之前,对所述时钟信号进行反相;或第六反相电路,所述第六反相电路被配置为使从所述至少一个第三延迟单元提供的所述反相时钟信号反相。9.根据权利要求1所述的时钟信号延迟路径单元,其中:所述第一路由信号线、所述第二路由信号线、所述第一分支信号线和所述第二分支信号线分别被设置为第一路由信号线对、第二路由信号线对、第一分支信号线对和第二分支信号线对,所述第一中继器连接在所述第一路由信号线对与所述第二路由信号线对之间,并且被配置为无信号衰减地传输包括所述时钟信号的时钟信号对,所述第一反相电路被配置为使所述时钟信号对反相以生成包括所述反相时钟信号的反相时钟信号对,所述第二中继器连接在所述第一分支信号线对与所述第二分支信号线对之间,并且被配置为无信号衰减地传输所述反相时钟信号对,并且所述第一路由信号线对、所述第二路由信号线对、所述第一分支信号线对和所述第二分支信号线对均是长金属线对。10.根据权利要求9所述的时钟信号延迟路径单元,其中,包括在所述至少一个第一延迟单元中的第一中继器的数目等于包括在所述第二延迟单元中的第二中继器的数目。11.根据权利要求9所述的时钟信号延迟路径单元,其中,所述第二延迟单元还包括:第一中间信号线对,所述第一中间信号线对用于延迟从所述至少一个第一延迟单元提供的所述时钟信号对,并且将延迟的所述时钟信号对传输到所述第一反相电路;第三中继器,所述第三中继器被配置为无信号衰减地传输从所述第一反相电路输出的所述反相时钟信号对;以及第二中间信号线对,所述第二中间信号线对用于延迟从所述第三中继器输出的所述反相时钟信号对,其中,所述第一中间信号线对和所述第二中间信号线对均是长金属线对。12.根据权利要求11所述的时钟信号延迟路径单元,其中:所述第三中继器包括串联连接的偶数个第二反相电路,所述第一中间信号线对和所述第二中间信号线对中的每一者的长度大于所述第一反相电路与所述第三中继器之间的信号线对的长度或者大于串联连接的所述偶数个第二反相电路之间的信号线对的长度。13.根据权利要求12所述的时钟信号延迟路径单元,其中:所述第一反相电路包括偶数个第一反相放大器,所述第二反相电路包括偶数个第二反相放大器,并且在所述第一反相放大器当中,一个所述第一反相放大器的输出信号线对和另一个所述第一反相放大器的输入信号线对交叉耦接。14.根据权利要求9所述的时钟信号延迟路径单元,其中:所述第一中继器包括串联连接的偶数个第三反相电路,

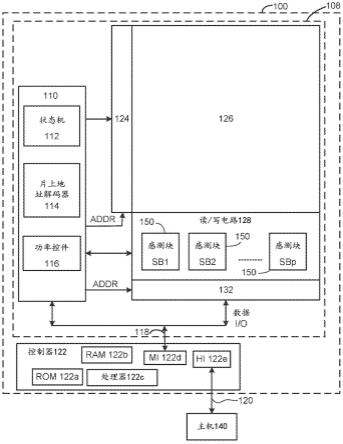

所述第二中继器包括串联连接的偶数个第四反相电路,所述第一路由信号线对和所述第二路由信号线对中的每一者的长度大于所述第三反相电路之间的信号线对的长度,并且所述第一分支信号线对和所述第二分支信号线对中的每一者的长度大于所述第四反相电路之间的信号线对的长度。15.根据权利要求14所述的时钟信号延迟路径单元,其中,所述第三反相电路和所述第四反相电路均包括至少一个反相放大器。16.一种半导体存储器件,包括:时钟信号输入缓冲器,所述时钟信号输入缓冲器被配置为缓冲从外部施加的外部时钟信号,并且输出缓冲时钟信号;延迟锁定环,所述延迟锁定环被配置为接收所述缓冲时钟信号,并且生成相对于所述外部时钟信号被锁定延迟的延迟时钟信号;时钟信号延迟路径单元,所述时钟信号延迟路径单元被配置为使所述延迟时钟信号延迟和反相,以生成n个内部时钟信号、输出数据选通信号和反相输出数据选通信号;存储单元阵列,所述存储单元阵列包括多个存储单元,并且输出存储在响应于多个字线选择信号和多个列选择信号而被选择的存储单元中的数据;数据读取路径单元,所述数据读取路径单元被配置为接收所述数据,并且将所述数据转换成串行数据以生成n条数据;数据输出单元,所述数据输出单元被配置为响应于所述n个内部时钟信号而驱动所述n条数据;以及数据选通信号输出单元,所述数据选通信号输出单元被配置为驱动所述输出数据选通信号和所述反相输出数据选通信号,其中:所述时钟信号延迟路径单元包括n 2个分支延迟单元,每个所述分支延迟单元包括:至少一个第一延迟单元,每一个所述第一延迟单元包括:用于延迟并传输所述延迟时钟信号的第一路由信号线、被配置为无信号衰减地传输通过所述第一路由信号线传输的所述延迟时钟信号的第一中继器、以及用于延迟并传输从所述第一中继器输出的所述延迟时钟信号的第二路由信号线;第二延迟单元,所述第二延迟单元包括被配置为使从所述至少一个第一延迟单元提供的所述延迟时钟信号反相以生成反相延迟时钟信号的第一反相电路;以及至少一个第三延迟单元,每一个所述第三延迟单元包括:用于延迟并传输从所述第二延迟单元提供的所述反相延迟时钟信号的第一分支信号线、被配置为无信号衰减地传输通过所述第一分支信号线传输的所述反相延迟时钟信号的第二中继器、以及用于延迟并传输从所述第二中继器输出的所述反相延迟时钟信号的第二分支信号线,其中,所述第一路由信号线、所述第二路由信号线、所述第一分支信号线和所述第二分支信号线均是长金属线,并且所述n 2个分支延迟单元生成所述n个内部时钟信号、所述输出数据选通信号和所述反相输出数据选通信号。17.根据权利要求16所述的半导体存储器件,其中,所述至少一个第一延迟单元中的每一个中包括的第一中继器的数目等于所述至少一个第三延迟单元中的每一个中包括的第

二中继器的数目。18.根据权利要求16所述的半导体存储器件,其中,所述n 2个分支延迟单元中的所有的所述第一分支信号线和所述第二分支信号线具有相同的长度。19.根据权利要求16所述的半导体存储器件,其中,所述第二延迟单元还包括:第一中间信号线,所述第一中间信号线用于延迟从所述至少一个第一延迟单元提供的所述延迟时钟信号,并且将延迟的所述延迟时钟信号传输到所述第一反相电路;第三中继器,所述第三中继器被配置为无信号衰减地传输从所述第一反相电路输出的所述反相延迟时钟信号;以及第二中间信号线,所述第二中间信号线用于延迟从所述第三中继器输出的所述反相延迟时钟信号,其中,所述第一中间信号线和所述第二中间信号线均是长金属线。20.根据权利要求16所述的半导体存储器件,其中,所述第三中继器包括串联连接的偶数个第二反相电路,并且所述第一中间信号线和所述第二中间信号线中的每一者的长度大于所述第一反相电路与所述第三中继器之间的信号线的长度或者大于串联连接的所述偶数个第二反相电路之间的信号线的长度。21.根据权利要求16所述的半导体存储器件,其中,所述第一中继器包括串联连接的偶数个第三反相电路,所述第二中继器包括串联连接的偶数个第四反相电路,所述第一路由信号线和所述第二路由信号线中的每一者的长度大于所述第三反相电路之间的信号线的长度,或者所述第一分支信号线和所述第二分支信号线中的每一者的长度大于所述第四反相电路之间的信号线的长度。22.根据权利要求16所述的半导体存储器件,还包括第五反相电路或第六反相电路,所述第五反相电路被配置为将所述延迟时钟信号施加到所述至少一个第一延迟单元之前,对所述延迟时钟信号进行反相,所述第六反相电路被配置为使从所述至少一个第三延迟单元提供的所述反相延迟时钟信号反相。23.根据权利要求16所述的半导体存储器件,还包括分别连接到所述n 2个分支延迟单元的n 2个分相器和选择器,其中,所述n 2个分相器和选择器对所述n个内部时钟信号进行反相分相以及对所述输出数据选通信号和所述反相输出数据选通信号进行反相分相,以将反相分相后的所述n个内部时钟信号输出到所述数据输出单元,并且将反相分相后的所述输出数据选通信号及反相分相后的所述反相输出数据选通信号输出到所述数据选通信号输出单元。24.根据权利要求23所述的半导体存储器件,其中,所述时钟信号延迟路径单元还包括:至少一个附加第三延迟单元,每一个所述附加第三延迟单元包括用于延迟从所述第二延迟单元提供的所述反相延迟时钟信号的第三分支信号线和第四分支信号线,以及连接在所述第三分支信号线与所述第四分支信号线之间并且被配置为无信号衰减地传输所述反相延迟时钟信号的第四中继器;分相器,所述分相器被配置为对从所述至少一个附加第三延迟单元提供的附加内部时

钟信号进行反相分相以生成附加内部时钟信号对;占空比校正器,所述占空比校正器被配置为使用所述附加内部时钟信号对来附加地校正从所述至少一个第一延迟单元提供的所述反相时钟信号的占空比;以及选择器,所述选择器被配置为响应于选择信号而选择所述占空比校正器或所述附加第三延迟单元。25.一种半导体存储器件,包括:读取使能信号输入缓冲器,所述读取使能信号输入缓冲器被配置为缓冲从外部施加的读取使能信号,并且输出缓冲的读取使能信号;反相读取使能信号输入缓冲器,所述反相读取使能信号输入缓冲器被配置为缓冲从外部施加的反相读取使能信号,并且输出缓冲的反相读取使能信号;读取使能信号延迟路径单元,所述读取使能信号延迟路径单元被配置为:使所述缓冲的读取使能信号和所述缓冲的反相读取使能信号延迟和反相,以生成n个内部时钟信号、输出数据选通信号和反相输出数据选通信号;存储单元阵列,所述存储单元阵列包括多个存储单元并且输出存储在响应于多个字线选择信号、多个源极线选择信号、多个地选择信号和多个列选择信号而被选择的存储单元中的数据;页面缓冲器,所述页面缓冲器被配置为缓冲所述数据以生成读取数据;数据读取路径单元,所述数据读取路径单元被配置为接收所述读取数据,并且将所述读取数据转换成串行数据以生成n条数据;数据输出单元,所述数据输出单元被配置为响应于所述n个内部时钟信号而驱动所述n条数据;以及数据选通信号输出单元,所述数据选通信号输出单元被配置为驱动所述输出数据选通信号和所述反相输出数据选通信号,其中:所述读取使能信号延迟路径单元包括n 2个分支延迟单元,每个所述分支延迟单元包括:至少一个第一延迟单元,每一个所述第一延迟单元包括:用于延迟并传输包括所述缓冲的读取使能信号和所述缓冲的反相读取使能信号的读取使能信号对的第一路由信号线对、被配置为无信号衰减地传输通过所述第一路由信号线对传输的所述读取使能信号对的第一中继器、以及用于延迟并传输从所述第一中继器输出的所述读取使能信号对的第二路由信号线对;第二延迟单元,所述第二延迟单元包括被配置为使从所述至少一个第一延迟单元提供的所述读取使能信号对反相并且输出反相读取使能信号对的第一反相电路;以及至少一个第三延迟单元,每一个所述第三延迟单元包括:用于延迟并传输从所述第二延迟单元提供的所述反相读取使能信号对的第一分支信号线对、被配置为无信号衰减地传输通过所述第一分支信号线对传输的所述反相读取使能信号对的第二中继器、以及用于延迟并传输从所述第二中继器输出的所述反相读取使能信号对的第二分支信号线对,其中,所述第一路由信号线对、所述第二路由信号线对、所述第一分支信号线对和所述第二分支信号线对均是长金属线对,并且所述n 2个分支延迟单元生成所述n个内部时钟信号、所述输出数据选通信号和所述反

相输出数据选通信号。

技术总结

提供一种时钟信号延迟路径单元和包括其的半导体存储器件。时钟信号延迟路径单元包括:第一延迟单元,包括:用于延迟并传输时钟信号的第一路由信号线、用于无信号衰减地传输通过第一路由信号线传输的时钟信号的第一中继器、以及用于延迟并传输从第一中继器输出的时钟信号的第二路由信号线;第二延迟单元,包括被配置为使从第一延迟单元提供的时钟信号反相以生成反相时钟信号的第一反相电路;以及第三延迟单元,包括:用于延迟并传输从第二延迟单元提供的反相时钟信号的第一分支信号线、用于传输通过第一分支信号线传输的反相时钟信号的第二中继器、以及用于延迟并传输从第二中继器输出的反相时钟信号的第二分支信号线。继器输出的反相时钟信号的第二分支信号线。继器输出的反相时钟信号的第二分支信号线。

技术研发人员:李民揆 赵英喆 朴胜振 崔荣暾 崔桢焕

受保护的技术使用者:三星电子株式会社

技术研发日:2022.06.06

技术公布日:2023/3/10

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。