地址锁存器、地址控制电路和半导体装置

1.相关申请的交叉引用

2.本技术要求于2021年9月7日提交至韩国知识产权局的韩国申请第10-2021-0119099号的优先权,其整体通过引用并入本文。

技术领域

3.各种实施方式大体涉及半导体电路,并且更具体地,涉及地址锁存器、地址控制电路和包括地址控制电路的半导体装置。

背景技术:

4.作为半导体装置的示例的半导体存储装置可以包括地址控制电路,该地址控制电路被配置为处理从外部提供的地址信号。地址控制电路可以包括用于支持半导体存储装置的各种操作模式的读取操作和写入操作的各种电路结构。随着地址控制电路的结构变得复杂,在地址处理的过程中会出现布局裕量变小和延迟变大的问题。

技术实现要素:

5.在一个实施例中,一种地址锁存器可以包括第一地址处理单元和第二地址处理单元。第一地址处理单元可以被配置为基于读取命令和写入命令来锁存外部地址信号,以通过输出节点输出第一锁存的信号。第二地址处理单元可以被配置为基于突发长度被设置为第一值的突发长度的读取命令来锁存外部地址信号,以及被配置为基于内部读取命令通过输出节点输出第二锁存的信号。

6.在一个实施例中,一种地址控制电路可以包括读取/写入组合地址锁存器、管道寄存器和解码器。读取/写入组合地址锁存器可以被配置为:根据读取命令或写入命令来锁存从半导体装置的外部输入的外部地址信号,以通过第一输出线输出第一锁存的信号,以及被配置为:根据内部读取命令,通过第一输出线输出根据突发长度被设置为第一值的读取命令来锁存的第二锁存的信号。管道寄存器可以被配置为:基于多个输入/输出控制信号,将在半导体装置的写入操作期间通过第一输出线输出的信号储存在其中,以及被配置为:通过与第一输出线耦接的第二输出线输出所储存的信号。解码器可以被配置为:对通过第二输出线输出的信号进行解码,以产生存储体组地址、存储体地址和列地址中的至少一个。

7.在一个实施例中,一种半导体装置可以包括存储区、数据输入/输出电路、地址控制电路和地址解码器。存储区可以包括多个存储单元,多个存储单元被划分为多个存储体。数据输入/输出电路可以耦接到存储区并且可以被配置为与存储区或外部设备交换数据。地址控制电路可以被配置为:根据读取命令或写入命令来锁存从外部设备输入的外部地址信号,以通过第一输出线输出第一锁存的信号,被配置为:根据突发长度设置为第一值的读取命令来锁存外部地址信号,以根据内部读取命令通过第一输出线输出第二锁存的信号,以及被配置为:对通过第一输出线输出的信号进行解码,以产生存储体组地址、存储体地址和列地址。地址解码器可以被配置为对存储体组地址、存储体地址和列地址进行解码,以基

于解码的结果来访问存储区。

附图说明

8.图1是示出根据一个实施例的半导体装置的结构的图。

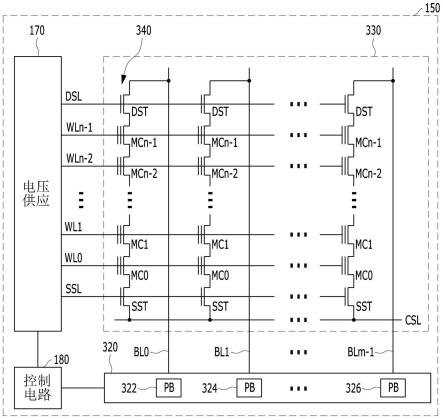

9.图2是示出图1的存储区的结构的图。

10.图3是示出根据一个实施例的地址控制电路的结构的图。

11.图4是示出根据一个实施例的对于各个操作模式的读取操作的时序图。

12.图5是示出根据一个实施例的地址控制电路的结构的图。

13.图6是示出图5的读取/写入组合地址锁存器的结构的图。

14.图7是示出根据一个实施例的对于各个操作模式的读取操作的时序图。

具体实施方式

15.根据实施例,可以提供一种地址锁存器、地址控制电路和包括地址控制电路的半导体装置,该地址控制电路能够减少在地址处理过程中的延迟并增加布局裕量。

16.在下文中,将参考附图来描述本公开的示例性实施例。

17.图1是示出根据一个实施例的半导体装置100的结构的图。

18.参考图1,半导体装置100可以包括存储区101、地址解码器102、数据输入/输出电路104和控制电路105。

19.存储区101可以包括多个存储单元,每个存储单元包括易失性存储器和非易失性存储器中的至少一个。易失性存储器可以包括静态随机存取存储器(静态ram:sram)、动态ram(dram)和同步dram(sdram)。非易失性存储器可以包括只读存储器(rom)、可编程rom(prom)、电可擦除可编程rom(eeprom)、电可编程rom(eprom)、闪速存储器、相变ram(pram)、磁性ram(mram)、电阻式ram(rram)、铁电ram(fram)等。在半导体装置100的读取操作期间,可以从存储区101中读出数据。在半导体装置100的写入操作期间,可以将从外部设备提供的数据储存到存储区101中。存储区101的存储单元可以被划分为多个单元存储区,例如多个存储体。例如,可以将多个存储体划分为用于半导体装置100的读取操作和写入操作的存储体组。

20.地址解码器102可以耦接到控制电路105和存储区101。地址解码器102可以对从控制电路105提供的地址信号进行解码并且可以根据解码的结果来访问存储区101。从控制电路105提供的地址信号可以包括行地址信号和列地址信号。行地址信号可以包括存储体组地址、存储体地址等。

21.数据输入/输出电路104可以耦接到存储区101。数据输入/输出电路104可以与外部设备或半导体装置100的内部电路交换数据。数据输入/输出电路104可以包括数据输入缓冲器、数据输出缓冲器、数据输入/输出焊盘等。

22.控制电路105可以耦接到存储区101、地址解码器102和数据输入/输出电路104。控制电路105可以执行与半导体装置100的读取操作、写入操作和地址处理有关的控制操作。控制电路105可以通过命令/地址引脚ca从外部设备接收命令和外部地址。控制电路105可以包括地址控制电路。地址控制电路可以控制用于半导体装置100的各个操作模式中的读取操作和写入操作的地址信号。地址控制电路可以针对半导体装置100的各个操作模式中

的读取操作和写入操作以预定时序锁存地址信号。通过命令/地址引脚ca,命令和外部地址信号可以以预定时序顺序地输入。

23.图2是示出图1的存储区101的配置的图。

24.参考图2,存储区101可以包括多个单单元存储块,例如多个存储体bk。半导体装置100可以以组为单位划分多个存储体bk。半导体装置100可以将多个存储体bk划分为多个存储体组bg0至bg3。多个存储体组bg0至bg3中的每一个可以包括多个存储体bk,例如四个存储体bk。

25.半导体存储装置应支持各种操作模式。例如,半导体存储装置的操作模式可以包括8存储体模式、16存储体模式和存储体组模式。例如,在对应于第五代低功耗双倍数据速率(lpddr5)的存储体组模式中,可以以非常短的时间间隔(即被称为“列到列短延迟”的时间间隔tccd_s)对不同的存储体组连续执行读取/写入操作。在存储体组模式中,即使当以时间间隔tccd_s对不同的存储体组a和b执行被设置为默认值(例如

‘

16’)的突发长度(bl)的读取操作时,也可以保证以时间间隔tccd_s来操作不同存储体组a和b的时序裕量。在这里,在本公开中,默认值被示例性地设置为

‘

16’。但是,默认值可以改变。然而,在存储体组模式中,当以时间间隔tccd_s对存储体组a和b执行具有被设置为默认值的整数倍(例如

‘

32’,其是默认值

‘

16’的两倍)的突发长度的读取操作时,时序裕量可能不足以以时间间隔tccd_s来操作存储体组a和b。因此,可以首先对存储体组a执行bl16读取操作,该bl16(即,设置为

‘

16’的突发长度)对应于bl32(即,设置为

‘

32’的突发长度)的第一半部分。然后,在时间间隔tccd_s之后,可以操作存储体组b。之后,可以在随后的时间间隔tccd_s期间对存储体组a执行bl16读取操作,该bl16对应于bl32的第二半部分。根据实施例,半导体装置100可以被配置为:对于存储体组模式中的bl32读取操作,在针对存储体组b的读取操作的时间间隔期间,保持存储体组a的地址不变。

26.在下文中,bl16的读取命令和针对bl16的读取命令的读取操作分别被称为bl16读取命令和bl16读取操作。此外,bl32的读取命令和针对bl32的读取命令的读取操作分别被称为bl32读取命令和bl32读取操作。与响应于bl32读取命令而要执行的bl32读取操作的第一半部分相对应的bl16读取操作被称为第一bl32读取操作。与响应于bl32读取命令而要执行的bl32读取操作的第二半部分相对应的bl16读取操作被称为第二bl32读取操作。

27.图3是示出根据实施例的地址控制电路105-1的配置的图。

28.参考图3,地址控制电路105-1可以包括在参考图1描述的控制电路105中。

29.地址控制电路105-1可以包括第一地址锁存器211、第二地址锁存器212、第一管道寄存器221、第二管道寄存器222、第一解码器231、第二解码器232、多路复用器241、第一输入/输出控制电路250和第二输入/输出控制电路260。第一地址锁存器211、第二地址锁存器212、第一管道寄存器221、第二管道寄存器222、第一解码器231、第二解码器232、多路复用器241、第一输入/输出控制电路250和第二输入/输出控制电路260中的每一个可以通过接收时钟信号(未示出)来操作。

30.根据写入命令信号wtf,第一地址锁存器211可以锁存外部地址信号ca《0:5》以产生第一写入地址锁存信号ba_wr_pre《0:3》和byac_wr_pre《0:5》。在第一写入地址锁存信号ba_wr_pre《0:3》和byac_wr_pre《0:5》之中,第一写入存储体地址锁存信号ba_wr_pre《0:3》可以被用作用于在半导体装置100的写入操作期间选择多个存储体bk(如图2所示)的存储

体地址。在第一写入地址锁存信号ba_wr_pre《0:3》和byac_wr_pre《0:5》之中,第一写入列地址锁存信号byac_wr_pre《0:5》可以被用作用于在半导体装置100的写入操作期间访问由第一写入存储体地址锁存信号ba_wr_pre《0:3》选择的存储体的列的列地址。

31.根据读取命令信号rdtf,第二地址锁存器212可以锁存外部地址信号ca《0:5》以产生第一读取地址锁存信号ba_rd_pre《0:3》和byac_rd_pre《0:5》。在第一读取地址锁存信号ba_rd_pre《0:3》和byac_rd_pre《0:5》之中,第一读取存储体地址锁存信号ba_rd_pre《0:3》可以被用作用于在半导体装置100的读取操作期间选择多个存储体bk(如图2所示)的存储体地址。在第一读取地址锁存信号ba_rd_pre《0:3》和byac_rd_pre《0:5》之中,第一读取列地址锁存信号byac_rd_pre《0:5》可以被用作用于在半导体装置100的读取操作期间访问由第一读取存储体地址锁存信号ba_rd_pre《0:3》选择的存储体的列的列地址。

32.第一管道寄存器221可以基于多个输入/输出控制信号255将第一写入地址锁存信号ba_wr_pre《0:3》和byac_wr_pre《0:5》储存在其中,并且可以将所储存的信号输出作为第二写入地址锁存信号ba_wr《0:3》和byac_wr《0:5》。第二写入地址锁存信号ba_wr《0:3》和byac_wr《0:5》可以被划分为第二写入存储体地址锁存信号ba_wr《0:3》和第二写入列地址锁存信号byac_wr《0:5》。

33.第二管道寄存器222可以基于多个输入/输出控制信号265将第一读取地址锁存信号ba_rd_pre《0:3》和byac_rd_pre《0:5》储存在其中,并且可以将所储存的信号输出作为第二读取地址锁存信号ba_rd《0:3》和byac_rd《0:5》。第二读取地址锁存信号ba_rd《0:3》和byac_rd《0:5》可以被划分为第二读取存储体地址锁存信号ba_rd《0:3》和第二读取列地址锁存信号byac_rd《0:5》。

34.第一解码器231可以对第二写入存储体地址锁存信号ba_wr《0:3》进行解码以产生第三地址锁存信号addlatp_bg0、addlatp_bg1、addlatp_bg2、addlatp_bg3和cbanktb《0:3》。第三地址锁存信号addlatp_bg0、addlatp_bg1、addlatp_bg2、addlatp_bg3和cbanktb《0:3》可以被划分为第三存储体组地址锁存信号addlatp_bg0、addlatp_bg1、addlatp_bg2和addlatp_bg3以及第三存储体地址锁存信号cbanktb《0:3》。

35.第一解码器231可以对第二写入存储体地址锁存信号ba_wr《0:3》的部分比特位(例如,ba_wr《0:1》)进行解码,以产生第三存储体组地址锁存信号addlatp_bg0、addlatp_bg1、addlatp_bg2和addlatp_bg3,并且可以对第二写入存储体地址锁存信号ba_wr《0:3》的其余比特位(例如,ba_wr《2:3》)进行解码,以产生第三存储体地址锁存信号cbanktb《0:3》。

36.第二解码器232可以对第二读取存储体地址锁存信号ba_rd《0:3》进行解码,以产生第三地址锁存信号addlatp_bg0、addlatp_bg1、addlatp_bg2、addlatp_bg3和cbanktb《0:3》。

37.第二解码器232可以对第二读取存储体地址锁存信号ba_rd《0:3》的部分比特位(例如,ba_rd《0:1》)进行解码,以产生第三存储体组地址锁存信号addlatp_bg0、addlatp_bg1、addlatp_bg2和addlatp_bg3,并且可以对第二读取存储体地址锁存信号ba_rd《0:3》的其余比特位(例如,ba_rd《2:3》)进行解码,以产生第三存储体地址锁存信号cbanktb《0:3》。

38.在半导体装置100的写入操作期间,多路复用器241可以对从第一解码器231输出的第三存储体组地址锁存信号addlatp_bg0、addlatp_bg1、addlatp_bg2和addlatp_bg3以及第三存储体地址锁存信号cbanktb《0:3》进行选择和输出,并且可以将第二写入列地址锁

存信号byac_wr《0:5》输出作为第三列地址锁存信号byac《0:5》。

39.在半导体装置100的读取操作期间,多路复用器241可以对从第二解码器232输出的第三存储体组地址锁存信号addlatp_bg0、addlatp_bg1、addlatp_bg2和addlatp_bg3以及第三存储体地址锁存信号cbanktb《0:3》进行选择和输出,并且可以将第二读取列地址锁存信号byac_rd《0:5》输出作为第三列地址锁存信号byac《0:5》。

40.在半导体装置100的写入操作期间,第一输入/输出控制电路250可以产生多个输入/输出控制信号255以满足预定条件。第一输入/输出控制电路250可以根据写入命令信号wtf或/和参考该写入命令信号wtf产生的至少单个信号来产生多个输入/输出控制信号255。

41.第一输入/输出控制电路250可以包括多个计数器251至254。第一计数器(pin计数器)251可以产生用于控制第一写入存储体地址锁存信号ba_wr_pre《0:3》的输入定时的控制信号。第二计数器(pout计数器)252可以产生用于控制第一写入存储体地址锁存信号ba_wr_pre《0:3》的输出定时的控制信号。第三计数器(pin计数器)253可以产生用于控制第一写入列地址锁存信号byac_wr_pre《0:5》的输入定时的控制信号。第四计数器(pout计数器)254可以产生用于控制第一写入列地址锁存信号byac_wr_pre《0:5》的输出定时的控制信号。

42.在半导体装置100的读取操作期间,第二输入/输出控制电路260可以产生多个输入/输出控制信号265以满足预定条件。第二输入/输出控制电路260可以根据读取命令信号rdtf或/和参考该读取命令信号rdtf产生的至少单个信号来产生多个输入/输出控制信号265。

43.第二输入/输出控制电路260可以包括多个计数器261至264。第一计数器(pin计数器)261可以产生用于控制第一读取存储体地址锁存信号ba_rd_pre《0:3》的输入定时的控制信号。第二计数器(pout计数器)262可以产生用于控制第一读取存储体地址锁存信号ba_rd_pre《0:3》的输出定时的控制信号。第三计数器(pin计数器)263可以产生用于控制第一读取列地址锁存信号byac_rd_pre《0:5》的输入定时的控制信号。第四计数器(pout计数器)264可以产生用于控制第一读取列地址锁存信号byac_rd_pre《0:5》的输出定时的控制信号。

44.图4是示出根据一个实施例的各个操作模式的读取操作的时序图。

45.在下文中,通过参考图3和图4进行描述,将公开针对16存储体模式和存储体组模式(bg模式)的地址控制电路105-1的操作。

46.在16存储体模式中,可以参考时钟信号clk通过命令/地址引脚顺序地输入命令cmd和外部地址信号ca《0:5》。例如,可以在第一定时t0输入命令cmd。然后,可以参考第一定时t0在第二时钟信号的单个周期时间间隔dsel期间输入外部地址信号ca《0:5》。

47.当在第一定时t0输入bl32读取命令rd32和外部地址信号ca《0:5》时,地址控制电路105-1可以产生第三存储体地址锁存信号cbanktb《0:3》和第三列地址锁存信号byac《0:5》。

48.根据第三存储体地址锁存信号cbanktb《0:1》,可以选择第一存储体。

49.可以基于第三存储体地址锁存信号cbanktb《0:1》和第三列地址锁存信号byac《0:5》对第一存储体执行第一bl32读取操作。

50.在第二定时t1,可以在半导体装置100内部产生针对响应于bl32读取命令rd32而要对第一存储体执行的第二bl32读取操作的内部读取命令ird32。

51.根据内部读取命令ird32,第三存储体地址锁存信号cbanktb《0:3》的值可以保持不变,并且第三列地址锁存信号byac《0:5》的值可以改变。根据第三存储体地址锁存信号cbanktb《0:3》和改变后的第三列地址锁存信号byac《0:5》,可以对第一存储体执行第二bl32读取操作。

52.当在第三定时t2输入另一bl32读取命令rd32和外部地址信号ca《0:5》时,地址控制电路105-1可以产生第三存储体地址锁存信号cbanktb《0:3》和第三列地址锁存信号byac《0:5》。

53.根据第三存储体地址锁存信号cbanktb《0:1》,可以选择第二存储体。

54.可以基于第三存储体地址锁存信号cbanktb《0:1》和第三列地址锁存信号byac《0:5》来对第二存储体执行第一bl32读取操作。

55.在第四定时t3,可以在半导体装置100内部产生针对响应于bl32读取命令rd32而要对第二存储体执行的第二bl32读取操作的内部读取命令ird32。

56.根据内部读取命令ird32,第三存储体地址锁存信号cbanktb《0:3》的值可以保持不变,并且第三列地址锁存信号byac《0:5》的值可以改变。根据第三存储体地址锁存信号cbanktb《0:3》和改变后的第三列地址锁存信号byac《0:5》,可以对第二存储体执行第二bl32读取操作。

57.在存储体组模式中,可以在第一定时t0输入命令cmd。然后,可以参考第一定时t0在第二时钟信号的单个周期时间间隔dsel期间输入外部地址信号ca《0:5》。

58.当在第一定时t0输入bl32读取命令rd32和外部地址信号ca《0:5》时,地址控制电路105-1可以产生第三存储体组地址锁存信号addlatp_bg0、addlatp_bg1、addlatp_bg2和addlatp_bg3、第三存储体地址锁存信号cbanktb《0:1》以及第三列地址锁存信号byac《0:5》。

59.根据第三存储体组地址锁存信号addlatp_bg0、addlatp_bg1、addlatp_bg2和addlatp_bg3以及第三存储体地址锁存信号cbanktb《0:1》,可以选择第一存储体组bg0内的存储体。

60.根据第三存储体地址锁存信号cbanktb《0:1》和第三列地址锁存信号byac《0:5》,可以对第一存储体组bg0的存储体执行第一bl32读取操作。

61.当在第二定时t1输入另一bl32读取命令rd32和外部地址信号ca《0:5》时,地址控制电路105-1可以产生第三存储体组地址锁存信号addlatp_bg0、addlatp_bg1、addlatp_bg2和addlatp_bg3以及第三存储体地址锁存信号cbanktb《0:1》。

62.根据第三存储体组地址锁存信号addlatp_bg0、addlatp_bg1、addlatp_bg2和addlatp_bg3以及第三存储体地址锁存信号cbanktb《0:1》,可以选择第二存储体组bg1内的存储体。

63.根据对应于在第二定时t1输入的bl32读取命令rd32并且用于第二存储体组bg1的第一读取地址锁存信号ba_rd_pre《0:3》和byac_rd_pre《0:5》,第三存储体地址锁存信号cbanktb《0:1》和第三列地址锁存信号byac《0:5》的值可以改变。根据改变后的第三存储体地址锁存信号cbanktb《0:1》和改变后的第三列地址锁存信号byac《0:5》,可以对第二存储

体组bg1的存储体执行第一bl32读取操作。

64.当在第二定时t1没有输出针对另一存储体组的bl32读取命令rd32的情况下,如上所述,时序裕量可能不足以参考bl32以时间间隔tccd_s来操作第一存储体组和第二存储体组。因此,在第二定时t1与第三定时t2之间的对应时间间隔期间可能不需要执行读取操作,这可以被称为非操作时间间隔或“冒泡(bubble)”。在第二定时t1与第三定时t2之间的时间间隔期间,对应于在第一定时t0输入的bl32读取命令rd32并用于第一存储体组bg0的第一读取地址锁存信号ba_rd_pre《0:3》和byac_rd_pre《0:5》可以被储存在第二管道寄存器222(如图3所示)中,并且可以保持不变,以便对第一存储体组bg0的存储体执行第二bl32读取操作。这将在后面描述。

65.在第三定时t2,可以在半导体装置100内部产生针对响应于bl32读取命令rd32而要对第一存储体组bg0的存储体执行的第二bl32读取操作的内部读取命令ird32。

66.与用于第一存储体组bg0的bl32读取命令rd32相对应的第一读取地址锁存信号ba_rd_pre《0:3》和byac_rd_pre《0:5》可以被储存在第二管道寄存器222中并且可以保持不变。因此,在第二定时t1针对第二存储体组bg1改变的第三存储体地址锁存信号cbanktb《0:1》和第三列地址锁存信号byac《0:5》的值可能会在第三定时t2基于内部读取命令ird32针对第一存储体组bg0而再次改变。根据针对第一存储体组bg0再次改变的第三存储体地址锁存信号cbanktb《0:1》和第三列地址锁存信号byac《0:5》,可以对第一存储体组bg0的存储体执行第二bl32读取操作。

67.在第四定时t3,可以在半导体装置100内部产生针对响应于bl32读取命令rd32而要对第二存储体组bg1的存储体执行的第二bl32读取操作的内部读取命令ird32。

68.与用于第二存储体组bg1的bl32读取命令rd32相对应的第一读取地址锁存信号ba_rd_pre《0:3》和byac_rd_pre《0:5》可以被储存在第二管道寄存器222中并且可以保持不变。因此,在第三定时t2针对第一存储体组bg0改变的第三存储体地址锁存信号cbanktb《0:1》和第三列地址锁存信号byac《0:5》的值可能会在第四定时t3基于内部读取命令ird32针对第二存储体组bg1而再次改变。根据针对第二存储体组bg1再次改变的第三存储体地址锁存信号cbanktb《0:1》和第三列地址锁存信号byac《0:5》,可以对第二存储体组bg1的存储体执行第二bl32读取操作。

69.在与16存储体模式不同的存储体组模式中的bl32读取操作期间,可能不会连续地执行第一bl32读取操作和第二bl32读取操作。也就是说,可以首先对一个存储体组执行第一bl32读取操作,然后,在对另一存储体组执行读取操作的时间间隔或者“冒泡”之后,可以对上述一个存储体组执行第二bl32读取操作。因此,为了储存第一bl32读取操作中所使用的第一读取地址锁存信号ba_rd_pre《0:3》和byac_rd_pre《0:5》并且为了在第二bl32读取操作中使用所储存的第一读取地址锁存信号ba_rd_pre《0:3》和byac_rd_pre《0:5》,可以提供如图3所示的地址控制电路105-1以独立地锁存用于读取操作和写入操作各自的地址。

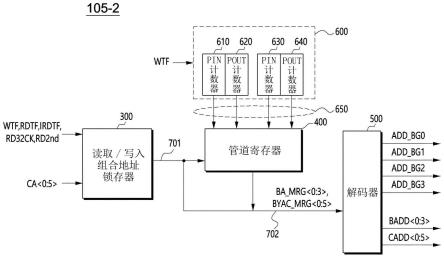

70.图5是示出根据一个实施例的地址控制电路105-2的配置的图。

71.参考图5,地址控制电路105-2可以包括在参考图1描述的控制电路105中。

72.地址控制电路105-2可以包括读取/写入组合地址锁存器300、管道寄存器400、解码器500和输入/输出控制电路600。读取/写入组合地址锁存器300、管道寄存器400、解码器500和输入/输出控制电路600中的每一个可以通过接收时钟信号(未示出)来操作。

73.读取/写入组合地址锁存器300可以基于半导体装置100的读取命令或写入命令来通过第一信号路径锁存外部地址信号ca《0:5》,以通过输出节点输出锁存的信号。在bl32读取操作期间,读取/写入组合地址锁存器300可以基于内部读取命令通过第二信号路径锁存外部地址信号ca《0:5》,以通过第一输出线701输出锁存的信号。第一输出线701可以耦接到管道寄存器400。耦接到第一输出线701的第二输出线702可以耦接到解码器500。

74.根据读取命令信号rdtf、写入命令信号wtf、内部读取命令信号irdtf、第一读取定时信号rd32ck和第二读取定时信号rd2nd,读取/写入组合地址锁存器300可以锁存外部地址信号ca《0:5》,以产生第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》。读取/写入组合地址锁存器300可以将第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》提供到管道寄存器400和解码器500。

75.第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》可以被划分为第一组合存储体地址锁存信号ba_mrg《0:3》和第一组合列地址锁存信号byac_mrg《0:5》。第一组合存储体地址锁存信号ba_mrg《0:3》可以被用作用于选择多个存储体bk(图2所示)的存储体地址。第一组合列地址锁存信号byac_mrg《0:5》可以被用作用于访问由第一组合存储体地址锁存信号ba_mrg《0:3》选择的存储体的列的列地址。

76.当读取命令信号rdtf和写入命令信号wtf中的任何一个被使能时,读取/写入组合地址锁存器300可以锁存外部地址信号ca《0:5》并且可以输出锁存的信号作为第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》。读取/写入组合地址锁存器300可以根据第一读取定时信号rd32ck锁存外部地址信号ca《0:5》以产生第一锁存信号。读取/写入组合地址锁存器300可以根据第二读取定时信号rd2nd锁存第一锁存信号以产生第二锁存信号。读取/写入组合地址锁存器300可以根据内部读取命令信号irdtf来输出第二锁存信号作为第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》。

77.管道寄存器400可以基于多个输入/输出控制信号650通过第一输出线701将与半导体装置100的写入操作相对应的第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》储存在其中,并且可以通过第二输出线702输出所储存的信号作为第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》。

78.解码器500可以通过第二输出线702接收第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》,并且对第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》进行解码以产生第二组合地址锁存信号add_bg0、add_bg1、add_bg2、add_bg3、badd《0:3》和cadd《0:5》。第二组合地址锁存信号add_bg0、add_bg1、add_bg2、add_bg3、badd《0:3》和cadd《0:5》可以被划分为第二组合存储体组地址锁存信号add_bg0、add_bg1、add_bg2和add_bg3、第二组合存储体地址锁存信号badd《0:3》以及第二组合列地址锁存信号cadd《0:5》。

79.解码器500可以对第一组合存储体地址锁存信号ba_mrg《0:3》的部分比特位(例如,ba_mrg《0:1》)进行解码,以产生第二组合存储体组地址锁存信号add_bg0、add_bg1、add_bg2和add_bg3,并且可以对第一组合存储体地址锁存信号ba_mrg《0:3》的其余比特位(例如,ba_mrg《2:3》)进行解码,以产生第二组合存储体地址锁存信号badd《0:3》。解码器500可以输出第一组合列地址锁存信号byac_mrg《0:5》作为第二组合列地址锁存信号cadd《0:5》。

80.在半导体装置100的写入操作期间,输入/输出控制电路600可以产生多个输入/输

出控制信号650以满足预定条件。输入/输出控制电路600可以根据参考写入命令信号wtf而产生的至少单个信号来产生多个输入/输出控制信号650。

81.在半导体装置100的读取操作期间,输入/输出控制电路600可以控制多个输入/输出控制信号650的值使得从读取/写入组合地址锁存器300输出的第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》不被输入到管道寄存器400。因此,管道寄存器400可以在半导体装置100的写入操作期间操作,而在半导体装置100的读取操作期间可以不操作。

82.输入/输出控制电路600可以包括多个计数器610至640。第一计数器(pin计数器)610可以产生用于控制第一组合存储体地址锁存信号ba_mrg《0:3》的输入定时的控制信号。第二计数器(pout计数器)620可以产生用于控制第一组合存储体地址锁存信号ba_mrg《0:3》的输出定时的控制信号。第三计数器(pin计数器)630可以产生用于控制第一组合列地址锁存信号byac_mrg《0:5》的输入定时的控制信号。第四计数器(pout计数器)640可以产生用于控制第一组合列地址锁存信号byac_mrg《0:5》的输出定时的控制信号。

83.图6是示出图5的读取/写入组合地址锁存器300的配置的图。

84.参考图6,读取/写入组合地址锁存器300可以包括第一地址处理单元310和第二地址处理单元320。第一地址处理单元310可以作为第一信号路径来操作,且第二地址处理单元320可以作为第二信号路径来操作。

85.根据读取/写入命令信号wt_rd和反相读取/写入命令信号wtb_rdb,第一地址处理单元310可以锁存外部地址信号ca《0:5》并且可以通过输出节点313来输出锁存的信号作为第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》。

86.第一地址处理单元310可以包括多个锁存器311和多个逻辑门312。多个锁存器311可以基于反相读取/写入命令信号wtb_rdb来锁存外部地址信号ca《0:5》。多个逻辑门312可以基于读取/写入命令信号wt_rd和反相读取/写入命令信号wtb_rdb通过输出节点313来输出由多个锁存器311锁存的信号作为第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》。

87.第二地址处理单元320可以根据由第一地址处理单元310锁存的外部地址信号ca《0:5》、第一读取定时信号rd32ck和第二读取定时信号rd2nd执行控制,以基于内部读取命令信号irdtf通过输出节点313产生第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》。

88.第二地址处理单元320可以根据第一读取定时信号rd32ck锁存由第一地址处理单元310锁存的外部地址信号ca《0:5》,以产生第一锁存信号latb1。第二地址处理单元320可以根据第二读取定时信号rd2nd锁存第一锁存信号latb1,以产生第二锁存信号latb2。第二地址处理单元320可以根据内部读取命令信号irdtf和反相内部读取命令信号irdtfb通过输出节点313来输出第二锁存信号latb2作为第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》。

89.第二地址处理单元320可以包括多个第一锁存器321、多个第二锁存器322和多个逻辑门323。多个第一锁存器321可以根据第一读取定时信号rd32ck锁存由第一地址处理单元310锁存的外部地址信号ca《0:5》,以产生第一锁存信号latb1。多个第二锁存器322可以基于第二读取定时信号rd2nd锁存第一锁存信号latb1,以产生第二锁存信号latb2。多个逻辑门323可以基于内部读取命令信号irdtf和反相内部读取命令信号irdtfb通过输出节点313来输出第二锁存信号latb2作为第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》。

90.反相内部读取命令信号irdtfb、反相读取/写入命令信号wtb_rdb和读取/写入命令信号wt_rd可以从如图1所示的控制电路105产生,或者可以从与地址处理以外的读取/写入操作相关的电路块产生。此外,反相内部读取命令信号irdtfb、反相读取/写入命令信号wtb_rdb和读取/写入命令信号wt_rd可以从地址控制电路105-2产生。

91.读取/写入组合地址锁存器300还可以包括控制逻辑330,该控制逻辑330被配置为产生反相内部读取命令信号irdtfb、反相读取/写入命令信号wtb_rdb和读取/写入命令信号wt_rd。控制逻辑330可以包括多个逻辑门331至333。第一逻辑门331可以对写入命令信号wtf和读取命令信号rdtf执行或非运算,以产生反相读取/写入命令信号wtb_rdb。第二逻辑门332可以对写入命令信号wtf和读取命令信号rdtf执行或运算,以产生读取/写入命令信号wt_rd。第三逻辑门333可以接收内部读取命令信号irdtf以产生反相内部读取命令信号irdtfb。

92.图7是示出根据一个实施例的各个操作模式的读取操作的时序图。

93.在下文中,通过参考图5至图7描述,将公开地址控制电路105-2的操作。

94.在半导体装置100以存储体组模式操作并且bl32读取命令和bl16读取命令被连续输入的实例1“case 1”中,可以在bl32读取命令rd32和外部地址信号ca《0:5》被输入之后预定时间后产生读取命令信号rdtf。

95.可以由读取命令信号rdtf产生反相读取/写入命令信号wtb_rdb,并且可以基于反相读取/写入命令信号wtb_rdb锁存外部地址信号ca《0:5》。

96.基于读取/写入命令信号wt_rd和反相读取/写入命令信号wtb_rdb,可以将锁存的外部地址信号ca《0:5》输出作为第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》。

97.可以由解码器500对第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》进行解码,以产生第二组合存储体地址锁存信号badd《0:3》和第二组合列地址锁存信号cadd《0:5》。

98.根据第二组合存储体地址锁存信号badd《0:3》和第二组合列地址锁存信号cadd《0:5》,可以对存储体组x(“bg x”)的存储体执行第一bl32读取操作。

99.然后,可以在bl16读取命令rd16和外部地址信号ca《0:5》被输入之后预定时间后产生读取命令信号rdtf。

100.可以由读取命令信号rdtf产生反相读取/写入命令信号wtb_rdb,并且可以基于反相读取/写入命令信号wtb_rdb锁存外部地址信号ca《0:5》,以将锁存的外部地址信号ca《0:5》输出作为第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》。

101.可以由解码器500对第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》进行解码,以产生第二组合存储体地址锁存信号badd《0:3》和第二组合列地址锁存信号cadd《0:5》。

102.根据第二组合存储体地址锁存信号badd《0:3》和第二组合列地址锁存信号cadd《0:5》,可以对存储体组y(“bg y”)的存储体执行bl16读取操作。

103.在对应于存储体组x(“bg x”)的bl32读取命令rd32被输入之后,可以分别产生预定次数的第一读取定时信号rd32ck和第二读取定时信号rd2nd。

104.第一读取定时信号rd32ck可以在bl32读取命令rd32被输入之后时间2tck后产生。tck对应于时钟信号clk的1个周期的时间。第二读取定时信号rd2nd可以通过对第一读取定

时信号rd32ck和内部读取命令信号irdtf进行或非运算而产生。

105.可以基于第一读取定时信号rd32ck来产生第一锁存信号latb1。可以根据第二读取定时信号rd2nd来产生第二锁存信号latb2。

106.当正在对存储体组y(“bg y”)执行bl16读取操作时,与用于存储体组x(“bg x”)的bl32读取命令rd32相对应的第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》(即第二锁存信号latb2)可以被储存在第二地址处理单元320中,并且可以保持不变,以便对存储体组x(“bg x”)的存储体执行第二bl32读取操作。

107.在对存储体组y(“bg y”)的存储体的bl16读取操作之后,可以在半导体装置100内部产生针对响应于bl32读取命令rd32而要对存储体组x(“bg x”)的存储体执行的第二bl32读取操作的内部读取命令ird32。可以基于内部读取命令ird32来产生内部读取命令信号irdtf。

108.可以基于内部读取命令信号irdtf和反相内部读取命令信号irdtfb输出第二锁存信号latb2作为第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》。

109.可以由解码器500对第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》进行解码,以产生第二组合存储体地址锁存信号badd《0:3》和第二组合列地址锁存信号cadd《0:5》。

110.根据第二组合存储体地址锁存信号badd《0:3》和第二组合列地址锁存信号cadd《0:5》,可以对存储体组x(“bg x”)的存储体执行第二bl32读取操作。

111.在半导体装置100以存储体组模式操作并且bl32读取命令被连续输入的实例2“case 2”中,可以响应于bl32读取命令rd32对存储体组z(“bg z”)执行第一bl32读取操作。

112.然后,响应于另一bl32读取命令rd32,可以对存储体组a(“bg a”)执行第一bl32读取操作。

113.当响应于针对存储体组a(“bg a”)的bl32读取命令rd32而正在对存储体组a(“bg a”)执行第一bl32读取操作时,与针对存储体组z(“bg z”)的bl32读取命令rd32相对应的第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》(即第二锁存信号latb2)可以被储存在第二地址处理单元320中,并且可以保持不变,以便对存储体组z(“bg z”)的存储体执行第二bl32读取操作。

114.在针对bl32读取命令rd32对存储体组a(“bg a”)执行的第一bl32读取操作之后,可以在半导体装置100内部产生针对响应于bl32读取命令rd32而要对存储体组z(“bg z”)的存储体执行的第二bl32读取操作的内部读取命令ird32。

115.根据针对存储体组z(“bg z”)的内部读取命令ird32,可以对存储体组z(“bg z”)执行第二bl32读取操作。

116.在响应于针对存储体组z(“bg z”)的内部读取命令ird32而正在对存储体组z(“bg z”)执行第二bl32读取操作的情况下,与针对存储体组a(“bg a”)的bl32读取命令rd32相对应的第一组合地址锁存信号ba_mrg《0:3》和byac_mrg《0:5》(即第二锁存信号latb2)可以被储存在第二地址处理单元320中,并且可以保持不变,以便对存储体组a(“bg a”)的存储体执行第二bl32读取操作。

117.在针对内部读取命令ird32对存储体组z(“bg z”)执行的第二bl32读取操作之后,可以在半导体装置100内部产生针对响应于bl32读取命令rd32而要对存储体组a(“bg a”)

的存储体执行的第二bl32读取操作的内部读取命令ird32。

118.根据针对存储体组a(“bg a”)的内部读取命令ird32,可以对存储体组a(“bg a”)执行第二bl32读取操作。

119.根据一个实施例,地址控制电路105-2可以在对存储体组2执行第一bl32读取操作的时间间隔或被称为“冒泡”的时间间隔期间,将执行了第一bl32读取操作的存储体组1的地址储存到读取/写入组合地址锁存器300中,并且可以在对存储体组1执行第二bl32读取操作之前输出所储存的地址。因此,当与图3的实施例相比时,地址控制电路105-2可以由简化的电路结构来配置,如图5所示,即由单个读取/写入组合地址锁存器300、单个管道寄存器400和单个解码器500配置。

120.尽管上面已经描述了某些实施例,但是本领域技术人员将理解,所描述的实施例仅作为示例。因此,地址锁存器、地址控制电路和包括地址控制电路的半导体装置不应基于所描述的实施例来限制。相反,本文中描述的地址锁存器、地址控制电路和包括地址控制电路的半导体装置应当仅根据结合以上描述和附图的所附权利要求来限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。