低成本晶片级封装件和硅

1.相关申请

2.本技术要求于2021年7月27日提交的美国临时专利申请第63/203,539号的优先权,该申请的内容通过引用整体并入。

技术领域

3.本公开涉及用于形成晶片级封装件的技术,并且具体地涉及形成具有使用激光直接结构形成的再分布层的晶片级封装件,以使得能够形成包含多个互连集成电路管芯的紧凑封装件。

背景技术:

4.集成电路管芯被封装以保护管芯免受操作环境的影响,并提供管芯与利用管芯的电子装置之间的电接口。传统上,管芯封装技术不同于晶片级处理中使用的半导体制造技术。然而,近年来,诸如晶片级芯片级封装(wlcsp)的晶片级处理技术已经开始用于构建管芯封装。

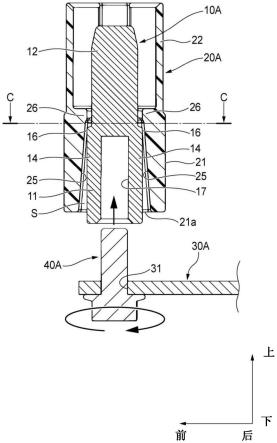

5.图1是包括通过形成在第一集成电路管芯9上的相应再分布层与第二集成电路管芯8连接的第一集成电路管芯9的已知封装件10的截面图。

6.更详细地,第一集成电路管芯9具有被示出为暴露的后侧和其上形成有焊盘12a和12b的前侧,焊盘12a和12b提供到第一集成电路管芯9内的内部电路的连接。钝化层13设置在第一集成电路管芯9的前侧,并且阻焊层15形成在钝化层13上。形成在钝化层13和阻焊层15内的第一再分布层包括分别连接至焊盘12a和12b的互连件14a和14d,以及连接至第一集成电路管芯9的前侧上的未示出的焊盘的互连件14b、14c、27a和27b。焊球16a-16d分别连接至互连件14a-14d。

7.第二集成电路管芯8具有被示出为由包封层23包封的后侧和其上形成有焊盘19a和19b的前侧,焊盘19a和19b提供到第二集成电路管芯8内的内部电路的连接。钝化层20设置在第二集成电路管芯8的前侧,并且阻焊层22形成在钝化层20上。形成在钝化层20和阻焊层22内的第二再分布层包括分别连接至焊盘19a和19b的互连件21a和21b。焊球17a和17b将第一集成电路管芯9的互连件27a和27b连接至第二集成电路管芯8的互连件21a和21b。包封层23包封第二集成电路管芯8的边缘侧和前表面,并将其与第一集成电路管芯9的阻焊剂15密封。

8.根据诸如图1中的现有技术的晶片级处理技术形成的晶片级封装具有若干限制。例如,形成高密度、大尺寸和高引脚计数的晶片级封装件的成本可能高于期望,特别是当要使用扇出布置时。此外,利用多个集成电路管芯的晶片级封装件可能难以形成,并且使用焊球连接不同管芯可能消耗不期望的空间量。

9.因此,需要进一步发展。

技术实现要素:

10.本文公开了一种从晶片形成晶片级封装件的方法,包括:将第二集成电路的后侧粘性地附接至包括多个第一集成电路的晶片的前侧,使得暴露第一集成电路的前侧上的焊盘和第二集成电路的前侧上的焊盘;在第一集成电路和第二集成电路的前侧上以及第二集成电路的边缘上形成激光直接结构化(lds)可活化层;活化lds可活化层的一部分以在lds可活化层内形成结构化区域的期望图案,该lds可活化层内的结构化区域的期望图案中的一些从第二集成电路的前侧上的焊盘延伸到第一集成电路的前侧上的焊盘;对结构化区域的期望图案进行金属化以在lds可活化层内形成导电区域,所形成的导电区域中的一些将第一集成电路的焊盘电连接至第二集成电路的焊盘;并且对晶片进行切单从而形成多个晶片级封装件,每个晶片级封装件包含第一集成电路中的一个和第二集成电路中的一个。

11.可以将焊球附接至所形成的导电区域中的期望导电区域,使得附接至第一集成电路的前侧上的所形成的导电区域的焊球中的一些电连接至第二集成电路的前侧上的焊盘。

12.可以在切单之前在第一集成电路的后侧上形成涂层。

13.可以在lds可活化层上形成阻焊层。

14.无源元件可以附接至形成在第一集成电路上的导电区域中的期望导电区域,该导电区域电连接至第二集成电路的前侧上的期望焊盘,以及在无源元件上形成模制层。

15.可以在第一集成电路上形成模制层,在模制层的底侧上形成焊盘,并且可以在模制层中形成过孔,该过孔将形成在第一集成电路上的导电区域中的期望导电区域电连接至形成在模制层的底侧上的焊盘,该导电区域电连接至第一集成电路的前侧上的焊盘。

16.可以在第一集成电路上形成模制层,可以在模制层的底侧上形成焊盘,并且可以形成将模制层的底侧上的焊盘连接至第二集成电路的前侧上的期望焊盘的互连件。

17.芯片可以使用焊球附接至形成在第一集成电路上的导电区域中的期望导电区域,使得芯片的焊盘面向导电区域中的期望导电区域,并且在芯片上形成模制层。

18.本文还公开了一种晶片级封装,包括:第一集成电路管芯,其前侧具有多个焊盘;第二集成电路管芯,其前侧具有多个焊盘,其中,粘合剂层将第二集成电路管芯的后侧粘附至第一集成电路管芯的前侧;树脂层,包围第二集成电路管芯的边缘侧和第二集成电路管芯的前侧,并包围第一集成电路管芯的前侧,其中,树脂层包括可活化催化剂材料;阻焊层,其后侧与树脂层的前表面接触;以及再分布层。该再分布层包括:树脂层的第一活化和金属化部分,其与第二集成电路管芯的前侧上的多个焊盘相邻;树脂层的第二活化和金属化部分,其与第一集成电路管芯的前侧上的多个焊盘相邻;以及树脂层的第三活化和金属化部分,其从树脂层的第一活化和金属化部分中的给定部分沿着第二集成电路管芯的边缘侧向下且跨第一集成电路管芯的前侧上的树脂层的部分延伸,从而在第二集成电路管芯的前侧上的多个焊盘中的给定焊盘与第一集成电路管芯的前侧上的树脂层上的位置之间提供电连接。

19.树脂层的第四活化和金属化部分可以将树脂层的第一活化和金属化部分中的某些部分电连接至树脂层的第二活化和金属化部分中的某些部分,从而将第二集成电路管芯的前侧上的某些焊盘电连接至第一集成电路管芯的前侧上的某些焊盘。

20.树脂层的第四活化和金属化部分可以在第一集成电路管芯的前侧上。树脂层的第五活化和金属化部分可以将第一活化和金属化部分中的一个电连接至树脂层的第四活化

和金属化部分。

21.无源元件可以电连接至树脂层的第四活化和金属化部分。

22.模制层可以包封无源元件。

23.模制层可以包封第一集成电路管芯的一部分和树脂层的第二活化和金属化部分中的一个。可以在模制层上形成焊盘。过孔可以从形成在模制层上的焊盘延伸穿过模制层,以接触树脂层的第二活化和金属化部分中的一个,从而将形成在模制层上的焊盘电连接至树脂层的第二活化和金属化部分中的一个。

24.芯片可以连接至第一集成电路管芯的前侧上的树脂层的第三活化和金属化部分中的一个。

25.模制层可以包封芯片。

附图说明

26.图1是使用现有技术形成的晶片级封装件的截面图。

27.图2a至图2b是使用本文所述的技术形成的第一晶片级封装件的截面图。

28.图3至图11示出了制造图2a的第一晶片级封装件所涉及的一系列步骤。

29.图12是使用本文所述的技术形成的第二晶片级封装件的截面图。

30.图13至图19示出了制造图12的第二晶片级封装件所涉及的一系列步骤。

31.图20是使用本文所述的技术形成的第三晶片级封装件的截面图。

具体实施方式

32.以下公开使得本领域技术人员能够制造和使用本文公开的主题。在不脱离本公开的精神和范围的情况下,本文描述的一般原理可以应用于除上述详细描述的实施例和应用之外的实施例和应用。本公开并非旨在限于所示的实施例,而是要符合与本文公开或暗示的原理和特征一致的最宽泛范围。

33.在以下公开中,对元件“连接”的引用可以指示那些组件电连接,并且可以直接电连接以及物理连接。

34.首先参考图2a,现在描述第一晶片级封装件10'。第一晶片级封装件10'包括:第一集成电路管芯11,其前侧具有焊盘12a和12b并且其后侧具有涂层31;以及第二集成电路管芯18,其前侧具有焊盘19a-19b并且其后侧面向第一集成电路管芯11的前侧。粘合层30将第二集成电路管芯18的后侧附接至第一集成电路管芯11的前侧。因此,注意,第一集成电路管芯11的焊盘12a和12b不面向第二集成电路管芯18的焊盘19a-19b。

35.树脂层13'设置在第一集成电路管芯11的前侧上和跨前侧、第二集成电路管芯18的边缘侧上和上方、以及第二集成电路管芯18的前侧上和跨前侧。阻焊层15'设置在树脂层13'上和跨树脂层13'。

36.再分布层(rdl)形成在树脂层13'内和树脂层13'上,并被阻焊层15'覆盖。rdl包括分别连接至焊盘12a和12b的互连件41a和41d,以及分别连接至焊盘19c和19d的互连件41e和41f。rdl还包括互连件41b和41c,该互连件41b和41c从焊盘19a和19b跨第二管芯18的前面上的树脂层13'的部分、沿着第二管芯18的边缘侧上的树脂层13'的部分向下并且跨集成电路管芯11的前面上的树脂层13'的部分延伸。在一些实例中,互连件41b或41c可以将焊盘

19a或19c连接至第一集成电路管芯11上的相应焊盘,例如图2b所示,其中,互连件41b将焊盘19a连接至第一集成电路管芯11上的焊盘12c。

37.焊球16a和16d分别连接至互连件41a和41d。焊球16b和16c分别连接至互连件41b和41c在第一集成电路管芯11的前面跨树脂层13'延伸的部分。焊球16e和16f分别连接至互连件41e和41f。

38.这里要注意的是,互连件41a-41f不是通过常规技术形成的。如下文将详细说明的,互连件41a-41f是通过活化树脂层13'的期望区域(并在活化期望区域和经由钻孔形成的孔的壁之前对适当区域进行钻孔)并且然后电镀活化区域形成的,该树脂层13'包含可活化催化剂。

39.现在参考图3至图11的系列附图来描述第一晶片级封装件10'的形成。首先参考图3,单个进入晶片5具有形成在其中的集成电路管芯位置7;示出了两个这样的集成电路管芯位置7,但是应该理解,可以存在任何数量的这样的集成电路管芯位置7。每个集成电路管芯位置7具有形成在其前侧上的焊盘12a和12b。

40.如图4所示,在每个集成电路管芯位置7的前侧上形成粘合层30,并且然后将集成电路18的后侧附接至粘合层30,使得集成电路18的后侧附接至集成电路管芯位置7的前侧。集成电路18分别具有形成在其前侧上的焊盘19a-19d。

41.如图5所示,共形沉积物,例如,通过喷涂,由在集成电路管芯位置7和集成电路管芯18'的组合结构上的激光直接结构化(lds)可比树脂13'制成。具体地,lds兼容树脂13'喷涂在集成电路管芯位置7和集成电路管芯18的前侧的暴露部分上,并且被喷涂在集成电路18的侧面上。lds兼容树脂被注入或嵌入激光活化的催化剂或颗粒,当受到某些激光辐射(诸如红外(ir)激光辐射)时,这些催化剂或颗粒被活化或暴露以形成结构化区域。然后可以经由金属化将这些结构化区域变为导电区域。

42.例如,lds树脂层13'可以具有嵌入其中的诸如氧化铜铬尖晶石、硫酸铜、磷酸氢氧化铜或罗丹酸铜的颗粒。然后固化模制层13'。

43.接下来,如图6所示,通过激光钻孔形成穿过lds树脂层13'的过孔腔71a-71b和72a-72d,并且通过活化或暴露过孔腔71a-71b和72a-72d的壁中的催化剂,使用激光在lds树脂层13'中形成结构化区域的期望图案。

44.结构化区域是指lds树脂层13'中由于将激光施加到lds树脂层13'的相关部分而使催化剂活化或暴露的区域。如下所述,结构化区域可以被金属化以形成导电区域。例如,激光活化可以施加到过孔腔71a-71b和72a-72d的壁以构造那些壁。

45.此后,如图7所示,执行金属化处理以对过孔腔71a-71b和72a-72d进行金属化,并形成连接到它们并跨lds树脂层13'延伸的迹线,从而形成互连件41a-41f。该金属化处理可以包括铜无电镀沉积,其中,适当的湿化学浴与lds树脂层13'内的暴露的铬颗粒反应,以在lds树脂层13'上的结构化区域的图案上产生薄(例如,厚度为5μm)的铜图案。该薄的铜图案可以通过电沉积加厚以达到适当形成互连件41a-41f的期望厚度(例如,10μm)。

46.接下来,如图8所示,在lds树脂层13'和互连件41a-41f上形成阻焊层15。然后,如图9所示,焊球16a-16d连接至互连件41a-41d,并且焊球16e-16f连接至互连件41e-41f。然后,如图10所示,涂层31施加到集成电路管芯位置7的后侧,并且然后,如图11所示,晶片被切单为集成电路管芯11以形成晶片级封装件10a'和10b'。

47.首先参考图12,现在描述第二晶片级封装件10”。第二晶片级封装件10”包括:第一集成电路管芯11,其前侧具有焊盘12a和12b并且其后侧具有涂层31;以及第二集成电路管芯18,其前侧具有焊盘19a-19b并且其后侧面向第一集成电路管芯11的前侧。粘合层30将第二集成电路管芯18的后侧附接至第一集成电路管芯11的前侧。因此,注意,第一集成电路管芯11的焊盘12a和12b不面向第二集成电路管芯18的焊盘19a-19b。

48.树脂层13'设置在前集成电路管芯11的前侧上和跨前侧、第二集成电路管芯18的边缘侧上和上方、以及第二集成电路管芯18的前侧上和跨前侧。阻焊层15'设置在树脂层13'上和跨树脂层13'。

49.再分布层(rdl)形成在树脂层13'内和树脂层13'上,并被阻焊层15'覆盖。rdl包括分别连接至焊盘12a和12b的互连件41a和41d,以及分别连接至焊盘19c和19d的互连件41e和41f。rdl包括互连件41b和41c,该互连件41b和41c从焊盘19a和19b跨第二管芯18的前面上的树脂层13'的部分、沿着第二管芯18的边缘侧上的树脂层13'的部分向下并且跨集成电路管芯11的前面上的树脂层13'的部分延伸。

50.焊球35a和35b连接至互连件41c和41d,并且连接至芯片40上的焊盘,芯片40的前侧面向第一集成电路管芯11的前侧。模制层44包封芯片40,并且沿着第二集成电路管芯18的一侧并跨第一集成电路管芯15的前表面的一部分延伸。

51.诸如电容器的无源元件45连接至互连件41b。过孔46连接至互连件41a。模制层44包封无源元件45,并沿着第二集成电路管芯18的另一侧并跨第一集成电路管芯11的前表面的另一部分延伸。

52.注意,阻焊剂14还跨模制层44延伸,并在模制层44的两侧夹持模制层44。焊盘33a在阻焊剂14中处于与互连线41a相对的图示位置并连接至过孔46,并且焊球16a连接至焊盘33a。焊盘和互连件33b在阻焊剂14中从互连件41e延伸到与无源元件45和互连件41b相对的图示位置,并且焊球16b连接至焊盘33b。焊盘和互连件33c在阻焊剂14中从互连件41f延伸到与芯片40和互连件41c相对的图示位置,并且焊球16c连接至焊盘33c。焊盘33d在与互连件41d相对的阻焊剂14中,并且焊球16d连接至焊盘33d。

53.这里要注意的是,互连件41a-41f不是通过钻孔和填充形成的。互连件41a-41f是通过活化树脂层13'的期望区域(并在活化期望区域和经由钻孔形成的孔的壁之前对适当区域进行钻孔)并且然后电镀活化区域形成的,该树脂层13'包含可活化催化剂。还应注意的是,阻焊剂15内的焊盘33a、焊盘和互连件33b、焊盘和互连件33c和焊盘33d以及过孔46是通过常规技术而不是使用lds技术形成的。

54.第二晶片级封装件10”的形成开始与第一晶片级封装件10'相同,如上面参考图3至图8所述。现在另外参考图13至图19来描述第二晶片级封装件10”的形成的剩余部分。在lds树脂层13'和互连件41a-41f上形成阻焊剂层16之后,无源元件45附接至互连件41b,如图13所示。另外,此时芯片40连接至互连件41c和41d。

55.接下来,如图14所示,在阻焊剂15、无源元件45和芯片40上沉积模制层44。然后,如图15所示,使用常规技术在模制层44中形成过孔46,该过孔46从模制层44的前面延伸以到达互连件41a。

56.焊盘33a在与互连件41a相对的图示位置上形成在阻焊剂14中并连接至过孔46,并且焊球16a使用常规技术连接至焊盘33a。

57.焊盘和互连件33b被形成为在阻焊剂14中从互连件41e延伸到与无源元件45和互连件41b相对的图示位置,并且焊球16b使用常规技术连接至焊盘33b。焊盘和互连件33c被形成为在阻焊剂14中从互连件41f延伸到与芯片40和互连件41c相对的图示位置,并且焊球16c使用常规技术连接至焊盘33c。焊盘33d形成在与互连件41d相对的阻焊剂14中,并且焊球16d也使用常规技术连接至焊盘33d。

58.然后,如图16所示,在模制层44上形成阻焊剂15的附加部分,并在模制层44中钻孔76a-76d。此后,如图17所示,焊球16a-16d连接至焊盘和互连件33a-33d,并且如图18所示,涂层31被施加到集成电路管芯位置7的后侧,并且然后如图19所示,集成电路被切单为集成电路管芯10a”和10b”。

59.应当理解,以上给出的实施例是当使用lds技术时可能的可能性的示例。图20的封装件10”中示出了另一示例,其与图2a中的封装件10'相同,除了这里在集成电路管芯位置7的后侧沉积另一阻焊层51,并在其上形成焊盘52a-52d。连接器53a和53b延伸穿过集成电路管芯位置7以在阻焊层51和13中的组件之间提供互连。

60.尽管已经针对有限数量的实施例描述了本公开,但是受益于本公开的本领域技术人员将理解,可以设想不脱离本文公开的本公开的范围的其他实施例。因此,本公开的范围仅受所附权利要求的限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。