半导体装置及其制造方法

1.相关申请的交叉引用

2.本技术要求2021年7月27日提交于韩国知识产权局的韩国专利申请no.10-2021-0098390的优先权,其内容以引用方式整体并入本文。

技术领域

3.本公开涉及半导体装置及其制造方法,更具体地,涉及一种包括氧化物半导体材料的半导体装置及其制造方法。

背景技术:

4.随着半导体装置变得更加高度集成,控制半导体装置的泄漏电流特性可能重要。为了减小半导体装置的泄漏电流,已研究了包含氧化物半导体材料(例如,铟镓锌氧化物(igzo))的沟道层。氧化物半导体材料具有与硅(si)相似的导通电流并且还具有高带隙能量,从而具有优异的泄漏电流特性。

5.氧化物半导体材料可根据沉积方法或后处理方法具有各种类型的结晶度,并且可基于结晶度具有各种电特性和稳定性。在这方面,需要能够控制氧化物半导体材料的结晶度的技术来针对特定电气设计目标或要求高效地配置包括氧化物半导体材料的沟道层。

技术实现要素:

6.本公开的各方面提供了一种具有改进的性能和可靠性的半导体装置。

7.本公开的各方面还提供了一种制造具有改进的性能和可靠性的半导体装置的方法。

8.本公开的各方面不限于上面提及的那些,本领域技术人员将从以下描述清楚地理解本文中未总结的本公开的附加方面。

9.根据本发明构思的一方面,提供了一种半导体装置,其包括:导线,其在基板上在第一方向上延伸;第一氧化物半导体层,其在导线上且包括包含第一金属元素的第一结晶氧化物半导体材料;第二氧化物半导体层,其在导线上与第一氧化物半导体层物理接触并连接到导线;栅电极,其在第二氧化物半导体层的侧部在与第一方向交叉的第二方向上延伸;以及电容器结构,其在第二氧化物半导体层和栅电极上连接到第二氧化物半导体层,其中,第二氧化物半导体层包括包含第一金属元素以及不同于第一金属元素的第二金属元素和第三金属元素的第二结晶氧化物半导体材料。

10.根据本发明构思的一方面,提供了一种半导体装置,其包括:导线,其在基板上在第一方向上延伸;下氧化物层,其在导线的侧部且在基板上;第一氧化物半导体层,其在导线上且包括包含第一金属元素的第一结晶氧化物半导体材料;隔离绝缘层,其在导线和下氧化物层上且包括在与第一方向交叉的第二方向上延伸的沟道沟槽,下氧化物层的至少一部分和第一氧化物半导体层的至少一部分在沟道沟槽中的隔离绝缘层外面;第二氧化物半导体层,其沿着沟道沟槽的至少一部分延伸,并且与下氧化物层和第一氧化物半导体层物

理接触,第二氧化物半导体层连接到导线;第一栅电极,其在第二氧化物半导体层上在沟道沟槽内在第二方向上延伸;以及电容器结构,其在隔离绝缘层上连接到第二氧化物半导体层,其中,第二氧化物半导体层包括包含第一金属元素以及不同于第一金属元素的第二金属元素和第三金属元素的第二结晶氧化物半导体材料。

11.根据本发明构思的一方面,提供了一种半导体装置,其包括:基板;第一氧化物半导体层,其在基板上且包括包含第一金属元素的第一结晶氧化物半导体材料;第二氧化物半导体层,其在第一氧化物半导体层上且包括包含第一金属元素以及不同于第一金属元素的第二金属元素和第三金属元素的第二结晶氧化物半导体材料;以及栅电极,其在第二氧化物半导体层上,其中,在远离第二氧化物半导体层的方向上,第一氧化物半导体层中的第三金属元素的浓度降低速率大于第一氧化物半导体层中的第一金属元素的浓度降低速率。

附图说明

12.通过参照附图详细描述本发明构思的示例实施例,本发明构思的以上和其它方面和特征将变得更清楚,在附图中:

13.图1是示出根据一些实施例的半导体装置的示例截面图。图2是示出图1的第一氧化物半导体层和第二氧化物半导体层的示例曲线图。

14.图3是示出根据一些实施例的半导体装置的示例布局图。图4是沿着图3的线a-a截取的截面图。图5是沿着图3的线b-b截取的截面图。

15.图6是示出根据一些实施例的半导体装置的另一示例布局图。图7是沿着图6的线c1-c1截取的截面图。图8是沿着图6的线d1-d1截取的截面图。

16.图9至图11是示出根据一些实施例的半导体装置的各种示例截面图。

17.图12是示出根据一些实施例的半导体装置的另一示例布局图。图13是沿着图12的线c2-c2截取的截面图。图14是沿着图12的线d2-d2截取的截面图。

18.图15至图17是示出根据一些实施例的半导体装置的各种示例截面图。

19.图18是示出根据一些实施例的半导体装置的另一示例布局图。图19是沿着图18的线c3-c3截取的截面图。图20是沿着图18的线d3-d3截取的截面图。

20.图21至图23是示出根据一些实施例的半导体装置的各种示例截面图。

21.图24至图27是示出根据一些实施例的半导体装置的制造方法的中间操作的示图。

22.图28至图30是示出根据一些实施例的半导体装置的制造方法的中间操作的示图。

23.图31至图33是示出根据一些实施例的半导体装置的制造方法的中间操作的示图。

具体实施方式

24.以下,将参照附图详细描述本发明构思的实施例。相同的标号用于附图中的相同构成元件,并且省略其重复描述。将理解,尽管本文中可使用术语第一、第二等来描述各种元件,但这些元件不应受这些术语限制。这些术语仅用于将一个元件与另一元件相区分。因此,例如,在不脱离本发明构思的教导的情况下,下面讨论的第一元件、第一组件或第一区段可被称为第二元件、第二组件或第二区段。如本文所使用的,术语“和/或”包括一个或多个相关所列项的任何和所有组合。要注意的是,尽管没有相对于其具体地描述,关于一个实施例描述的方面可被并入不同的实施例中。即,所有实施例和/或任何实施例的特征可按任

何方式和/或组合来组合。

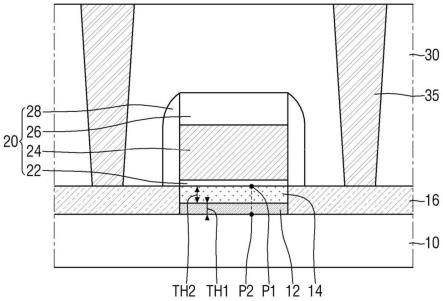

25.图1是示出根据一些实施例的半导体装置的示例截面图。图2是示出图1的第一氧化物半导体层和第二氧化物半导体层的示例曲线图。

26.尽管图1仅示出包括平面沟道区的平面fet作为根据一些实施例的半导体装置的示例,但是将理解,本发明构思的实施例不限于该示例。作为另一示例,根据一些实施例,半导体装置可包括鳍型晶体管(鳍fet)、隧穿晶体管(隧穿fet)、包括纳米线或纳米片的晶体管、竖直fet(vfet)、互补fet(cfet)和/或三维(3d)晶体管。在其它实施例中,半导体装置可包括双极结型晶体管、横向双扩散晶体管(ldmos)等。

27.参照图1和图2,根据一些实施例,半导体装置包括第一基板10、第一氧化物半导体层12、第二氧化物半导体层14、源极/漏极区16、栅极结构20、层间绝缘层30以及源极/漏极接触件35。

28.第一基板10可以是体硅基板或绝缘体上硅(soi)基板。另外地,第一基板10可以是硅基板,或者可包括其它材料,诸如硅锗、绝缘体上硅锗(sgoi)、锑化铟、碲铅化合物、砷化铟、磷化铟、砷化镓和/或锑化镓。另外地,第一基板10可以是形成在基底基板上的外延层。

29.第一氧化物半导体层12可形成在第一基板10上。例如,第一氧化物半导体层12可沿着第一基板10的上表面的一部分延伸。第一氧化物半导体层12可包括具有结晶度的第一结晶氧化物半导体材料。例如,第一结晶氧化物半导体材料可包括多晶结构、尖晶石晶体结构和/或c轴取向结晶结构(caac)。

30.在一些实施例中,第一结晶氧化物半导体材料可包括包含第一金属元素的二元或三元氧化物半导体材料,或者包含彼此不同的第一金属元素和第二金属元素的三元氧化物半导体材料。二元或三元氧化物半导体材料可以是但不限于锌氧化物(zno、zn

x

o)、镓氧化物(gao、ga

x

o)、锡氧化物(tio、ti

x

o)、锌氮氧化物(znon、zn

x

oyn)、铟锌氧化物(izo、in

x

znyo)、镓锌氧化物(gzo、ga

x

znyo)、锡锌氧化物(tzo、sn

x

znyo)和/或锡镓氧化物(tgo、sn

x

gayo)中的一种。

31.第二氧化物半导体层14可形成在第一氧化物半导体层12上。例如,第二氧化物半导体层14可沿着第一氧化物半导体层12的上表面延伸。第二氧化物半导体层14可与第一氧化物半导体层12物理接触。如本文所使用的,当元件被称为与另一元件“直接接触”时,其指示不存在介于它们之间的其它元件。第二氧化物半导体层14可包括具有结晶度的第二结晶氧化物半导体材料。例如,第二结晶氧化物半导体材料可包括多晶结构、尖晶石晶体结构和/或c轴取向结晶结构(caac)。

32.在一些实施例中,第二结晶氧化物半导体材料可包括包含第一金属元素和第二金属元素以及不同于第一金属元素和第二金属元素的第三金属元素的四元氧化物半导体材料。例如,四元氧化物半导体材料可以是但不限于铟镓锌氧化物(igzo、in

x

gayznzo,)、铟镓硅氧化物(igso、in

x

gaysizo)、铟锡锌氧化物(itzo、in

x

snyznzo)、铟锡镓氧化物(itgo、in

x

snygazo)、锆锌锡氧化物(zzto、zr

x

znysnzo)、铪铟锌氧化物(hizo、hf

x

inyznzo)、镓锌锡氧化物(gzto、ga

x

znysnzo)、铝锌锡氧化物(azto、al

x

znysnzo)和镱镓锌氧化物(ygzo、yb

x

gayznzo)中的一种或多种。

33.例如,第一金属元素可以是镓(ga),第二金属元素可以是锌(zn),第三金属元素可以是铟。在这种情况下,第一结晶氧化物半导体材料可包括例如多晶gzo和/或尖晶石gzo。

第二结晶氧化物半导体材料可包括例如多晶igzo、尖晶石igzo和/或c轴取向结晶(caac)igzo。

34.由于第二氧化物半导体层14形成在第一氧化物半导体层12上,所以第二氧化物半导体层14通常可具有高结晶度。在这种情况下,结晶度意指包含结晶部分的材料的结晶部分的质量(或体积)与包含结晶部分的材料的总质量(或体积)之比。例如,包含第一金属元素(或第一金属元素和第二金属元素)的第一氧化物半导体层12可在沉积包含第一金属元素至第三金属元素的第二氧化物半导体层14的处理中用作种子层,以改进第二氧化物半导体层14的结晶度。这将参照图24至图27更详细地描述。

35.第一氧化物半导体层12和第二氧化物半导体层14中的每一个可具有大于硅的带隙能量。例如,第一氧化物半导体层12和第二氧化物半导体层14中的每一个可具有约1.5ev至5.6ev的带隙能量。例如,第一氧化物半导体层12和第二氧化物半导体层14中的每一个可在具有约2.0ev至4.0ev的带隙能量时具有最优沟道性能。

36.例如,第一氧化物半导体层12的厚度th1和第二氧化物半导体层14的厚度th2可分别为约0.1nm至约50nm。在一些实施例中,第一氧化物半导体层12的厚度th1和第二氧化物半导体层14的厚度th2可分别为约0.1nm至约10nm。在一些实施例中,第二氧化物半导体层14的厚度th2可大于第一氧化物半导体层12的厚度th1。例如,第一氧化物半导体层12的厚度th1可为约0.1nm至约10nm,第二氧化物半导体层14的厚度th2可大于0.1nm至10nm的厚度。

37.尽管第一氧化物半导体层12的宽度和第二氧化物半导体层14的宽度被示出为彼此相同,但这仅是示例。在其它实施例中,第二氧化物半导体层14的宽度可大于或等于第一氧化物半导体层12的宽度。

38.第一氧化物半导体层12中的第三金属元素的浓度可随第三金属元素距第二氧化物半导体层14的距离增加而降低。例如,如图2所示,第一氧化物半导体层12中的第三金属元素(例如,铟(in))的浓度可随第三金属元素距第二氧化物半导体层14的距离增加而降低。这可能是因为第二氧化物半导体层14的第三金属元素扩散到第一氧化物半导体层12中。作为参考,图2示出在将第二氧化物半导体层14的上表面上的一个点p1与第一氧化物半导体层12的下表面上的一个点p2连接的扫描线中镓(ga)或锌(zn)和铟(in)的示意性浓度。

39.在远离第二氧化物半导体层14的方向上,第一氧化物半导体层12中的第三金属元素(例如,铟(in))的浓度降低速率可大于第一氧化物半导体层12中的第一金属元素或第二金属元素(例如,镓(ga)或锌(zn))的浓度降低速率。例如,第一氧化物半导体层12中的第一金属元素或第二金属元素(例如,镓(ga)或锌(zn))的浓度可在远离第二氧化物半导体层14的方向上维持基本上均匀。

40.在图2中,尽管第二氧化物半导体层14中的第三金属元素(例如,铟(in))的浓度仅被示出为大于第二氧化物半导体层14中的第一金属元素或第二金属元素(例如,镓(ga)或锌(zn))的浓度,但这仅是示例。另外,尽管第一氧化物半导体层12中的第一金属元素或第二金属元素(例如,镓(ga)或锌(zn))的浓度仅被示出为小于第二氧化物半导体层14中的第一金属元素或第二金属元素(例如,镓(ga)或锌(zn))的浓度,但这也是示例。

41.栅极结构20可形成在第二氧化物半导体层14上。例如,栅极结构20可沿着第二氧化物半导体层14的上表面延伸。在一些实施例中,栅极结构20可包括第一栅极介电层22、第

一栅电极24、第一栅极封盖图案26和栅极间隔件28。

42.第一栅极介电层22可沉积在第二氧化物半导体层14上。第一栅极介电层22可插置在第二氧化物半导体层14和第一栅电极24之间。例如,第一栅极介电层22可包括氧化硅、氮氧化硅、氮化硅和/或具有大于氧化硅的介电常数的高介电常数(高k)材料。高k材料可包括但不限于氧化铪。

43.第一栅电极24可沉积在第一栅极介电层22上。第一栅电极24可包括导电材料,例如ti、ta、w、al、co或其组合,但实施例不限于此。例如,第一栅电极24可包括非金属的硅和/或硅锗。

44.尽管第一栅电极24被示出为单层,但本发明构思的实施例不限于此。在其它实施例中,第一栅电极24可通过沉积多种导电材料来形成。例如,第一栅电极24可包括用于调节功函数的功函数控制层以及用于填充由功函数控制层形成的空间的填充导电层。例如,功函数控制层可包括tin、tan、tic、tac、tialc或其组合。例如,填充导电层可包括w和/或al。在一些实施例中,第一栅电极24可通过置换工艺来形成,但实施例不限于此。

45.第一栅极封盖图案26可在第一栅电极24的上表面上并至少部分地覆盖第一栅电极24的上表面。第一栅极封盖图案26可包括但不限于氧化硅、氮化硅、氮氧化硅或其组合。

46.尽管第一栅极介电层22的宽度、第一栅电极24的宽度和第一栅极封盖图案26的宽度被示出为与第一氧化物半导体层12的宽度和/或第二氧化物半导体层14的宽度相同,但这仅是示例。作为另一示例,第一栅极介电层22的宽度、第一栅电极24的宽度和第一栅极封盖图案26的宽度可大于或小于第一氧化物半导体层12的宽度和/或第二氧化物半导体层14的宽度。

47.栅极间隔件28可在第一栅电极24的侧部并至少部分地覆盖第一栅电极24的侧部。例如,栅极间隔件28可沿着第一栅极介电层22的侧部、第一栅电极24的侧部和第一栅极封盖图案26的侧部延伸。栅极间隔件28可包括但不限于氧化硅、氮化硅、氮氧化硅或其组合。

48.源极/漏极区16可在第一栅电极24的侧部形成在第一基板10上。另外,源极/漏极区16可连接到第二氧化物半导体层14。例如,源极/漏极区16可形成在第一氧化物半导体层12的侧部和第二氧化物半导体层14的侧部。因此,第二氧化物半导体层14可用作包括第一栅电极24的晶体管的沟道层。在一些实施例中,源极/漏极区16可包括形成在第一基板10上的外延层。

49.当根据一些实施例的半导体装置是pfet时,源极/漏极区16可包括p型杂质或用于减少或防止p型杂质的扩散的杂质。例如,源极/漏极区16可包括b、c、in、ga和al或其组合。当根据一些实施例的半导体装置是nfet时,源极/漏极区16可包括n型杂质或用于减少或防止n型杂质的扩散的杂质。例如,源极/漏极区16可包括p、sb、as或其组合。

50.层间绝缘层30可在源极/漏极区16和栅极结构20上并至少部分地覆盖源极/漏极区16和栅极结构20。例如,层间绝缘层30可包括氧化硅、氮化硅、氮氧化硅和/或具有小于氧化硅的介电常数的低k材料。低k材料可包括但不限于可流动氧化物(fox)、torene si lazene(tosz)、未掺杂石英玻璃(usg)、硼硅玻璃(bsg)、磷硅玻璃(psg)、硼磷硅玻璃(bpsg)、等离子体增强原硅酸四乙酯(peteos)、氟硅酸盐玻璃(fsg)、碳掺杂氧化硅(cdo)、干凝胶、气凝胶、非晶氟化碳、有机硅酸盐玻璃(osg)、聚对二甲苯、双苯并环丁烯(bcb)、silk、聚酰亚胺、多孔聚合材料或其组合。

51.源极/漏极接触件35可连接到源极/漏极区16。例如,源极/漏极接触件35可通过穿过层间绝缘层30来连接到源极/漏极区16。源极/漏极接触件35可包括但不限于导电材料,例如金属、导电金属氮化物、导电金属碳氮化物、导电金属碳化物、金属硅化物、掺杂半导体材料、导电金属氮氧化物、导电金属氧化物和/或二维(2d)材料。

52.为了减小半导体装置的泄漏电流,已研究了包含氧化物半导体材料(例如,igzo)的沟道层。氧化物半导体材料可具有与硅(si)类似的导通电流并且还可具有高带隙能量,从而具有优异的泄漏电流特性。然而,具有低结晶度的氧化物半导体材料可能对半导体装置的电特性和稳定性的劣化负责。例如,在沉积四元氧化物半导体材料(例如,igzo)的处理中,可能生成多个晶界,这可能导致四元氧化物半导体材料具有相对低的结晶度。另外,由于在这种四元氧化物半导体材料(例如,igzo)中的初始沉积步骤中形成的非晶区域,可能难以生成特定厚度(例如,几nm或更小)的结晶度。

53.然而,在根据一些实施例的半导体装置中,第二氧化物半导体层14可形成在第一氧化物半导体层12上以具有高结晶度。详细地,如上所述,包含第一金属元素(或第一金属元素和第二金属元素)的第一氧化物半导体层12可在沉积包含第一金属元素至第三金属元素的第二氧化物半导体层14的处理中用作种子层,从而改进第二氧化物半导体层14的结晶度。因此,可提供具有改进的性能和可靠性的半导体装置。

54.图3是示出根据一些实施例的半导体装置的示例布局图。图4是沿着图3的线a-a截取的截面图。图5是沿着图3的线b-b截取的截面图。为了描述方便,与参照图1和图2描述的那些重复的部分将简要描述或省略。

55.参照图3至图5,根据一些实施例的半导体装置可包括第二基板100、元件隔离层110、基础绝缘层120、第一导线130(bl)、直接接触件dc、间隔件结构140、第一氧化物半导体层12、第二氧化物半导体层14、第二栅电极160(wl)、第二栅极介电层162、接触结构bc和lp以及第一电容器结构190。

56.第二基板100可以是沉积有基底基板和外延层的结构,但实施例不限于此。第二基板100可以是硅基板、砷化镓基板、硅锗基板和/或绝缘体上半导体(soi)基板。以下描述作为示例将基于第二基板100是硅基板。

57.第二基板100可包括有源区ar。有源区ar可为彼此平行延伸的多个条的形式。另外,多个有源区ar之一的中心可被设置为与另一有源区ar的远端相邻。在一些实施例中,有源区ar可形成为斜条形状。例如,如图3所示,有源区ar可为在第一方向y1和第二方向x1延伸的平面上在不同于第一方向y1和第二方向x1的第三方向上延伸的条的形式。第二方向x1和第三方向之间的锐角可为例如60

°

,但实施例不限于此。

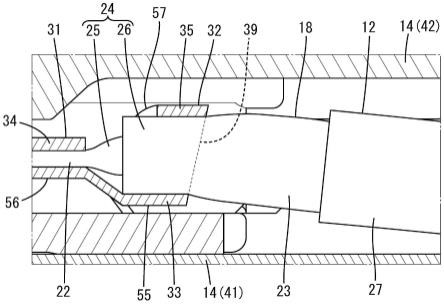

58.有源区ar可包括杂质,并且因此可用作源极/漏极区。在一些实施例中,有源区ar的第一部分(例如,中心部分)可通过直接接触件dc连接到第一导线130,有源区ar的第二部分(例如,两端)可通过接触结构bc和lp连接到第一电容器结构190。

59.元件隔离层110可限定多个有源区ar。尽管图5和图7示出元件隔离层110的侧部有斜度,但这仅是工艺特征,实施例不限于此。

60.元件隔离层110可包括但不限于氧化硅、氮化硅和/或氮氧化硅。元件隔离层110可以是由一种绝缘材料制成的单层,或者可以是由各种绝缘材料的组合制成的多层。

61.基础绝缘层120可形成在第二基板100和元件隔离层110上。在一些实施例中,基础

绝缘层120可在未形成接触结构bc和lp的区域中沿着第二基板100的上表面和元件隔离层110的上表面延伸。

62.基础绝缘层120可为单层结构,但在其它实施例中,可如图所示为多层结构。例如,基础绝缘层120可包括顺序地沉积在第二基板100上的第一绝缘层122、第二绝缘层124和第三绝缘层126。第一绝缘层122可包括例如氧化硅。第二绝缘层124可包括蚀刻选择比不同于第一绝缘层122的材料。例如,第二绝缘层124可包括氮化硅。第三绝缘层126可包括介电常数小于第二绝缘层124的材料。例如,第三绝缘层126可包括氧化硅。

63.第一导线130可形成在第二基板100、元件隔离层110和基础绝缘层120上。第一导线130可跨过有源区ar和第二栅电极160在第一方向y1上纵向延伸。例如,第一导线130可与有源区ar倾斜地交叉,并且可与第二栅电极160垂直地交叉。多条第一导线130可彼此间隔开并且沿着第二方向x1以大致恒定的间隔布置。每条第一导线130可连接到有源区ar,并且因此可用作根据一些实施例的半导体装置的位线bl。

64.在一些实施例中,第一导线130可包括顺序地沉积在第二基板100上的第一子导电图案132、第二子导电图案134和第三子导电图案136。第一子导电图案132、第二子导电图案134和第三子导电图案136中的每一个可包括例如多晶硅、tin、tisin、钨、硅化钨或其组合,但实施例不限于此。例如,第一子导电图案132可包括多晶硅,第二子导电图案134可包括tisin,第三子导电图案136可包括钨。

65.在一些实施例中,第一位线封盖图案138和第二位线封盖图案139可顺序地形成在第一导线130上。第一位线封盖图案138和第二位线封盖图案139可沿着第一导线130的上表面延伸。第一位线封盖图案138和第二位线封盖图案139可包括但不限于氮化硅。

66.直接接触件dc可形成在第二基板100和元件隔离层110上。直接接触件dc可通过穿过基础绝缘层120将第二基板100的有源区ar连接到第一导线130。例如,第二基板100可包括第一接触沟槽ct1。第一接触沟槽ct1可通过穿过基础绝缘层120来暴露有源区ar的第一部分(例如,中心部分)。直接接触件dc可形成在第一接触沟槽ct1中以将有源区ar的第一部分连接到第一导线130。

67.在一些实施例中,第一接触沟槽ct1的一部分可与元件隔离层110的一部分交叠。因此,第一接触沟槽ct1可暴露元件隔离层110的一部分以及有源区ar的一部分。

68.在一些实施例中,直接接触件dc的宽度可小于第一接触沟槽ct1的宽度。例如,直接接触件dc可仅与第二基板100的通过第一接触沟槽ct1暴露的部分接触。在一些实施例中,第一导线130的宽度也可小于第一接触沟槽ct1的宽度。例如,第一导线130的宽度可与直接接触件dc的宽度相同。

69.直接接触件dc可包括导电材料。因此,第一导线130可电连接到第二基板100的有源区ar。有源区ar的连接到直接接触件dc的第一部分(例如,中心部分)可用作包括第二栅电极160的半导体装置的第一源极/漏极区。

70.在一些实施例中,直接接触件dc可包括与第一子导电图案132相同的材料。例如,直接接触件dc可包括多晶硅,但这仅是示例。根据制造工艺,直接接触件dc可包括与第一子导电图案132不同的材料。

71.间隔件结构140可形成在第一导线130的侧部。间隔件结构140可沿着第一导线130的侧部延伸。例如,间隔件结构140可在第一方向y1上纵向延伸。在一些实施例中,间隔件结

构140可包括第一间隔件141、第二间隔件142、第三间隔件143、第四间隔件144和第五间隔件145。

72.第一间隔件141可沿着第一导线130的侧部延伸。例如,第一间隔件141可沿着第一导线130的侧部、第一位线封盖图案138的侧部和第二位线封盖图案139的侧部延伸。在形成有第一接触沟槽ct1的区域中,第一间隔件141可沿着第一导线130的侧部、直接接触件dc的侧部和第一接触沟槽ct1延伸。在一些实施例中,第一间隔件141可与第一导线130和直接接触件dc物理接触。在未形成第一接触沟槽ct1的区域中,第一间隔件141可沿着第一导线130的侧部和基础绝缘层120的上表面延伸。

73.第二间隔件142可形成在第一接触沟槽ct1中的第一间隔件141上。例如,第二间隔件142可沿着第一接触沟槽ct1中的第一间隔件141的轮廓延伸。

74.第三间隔件143可形成在第一接触沟槽ct1中的第二间隔件142上。第三间隔件143可至少部分地填充第一接触沟槽ct1的在形成第一间隔件141和第二间隔件142之后剩余的区域。

75.第四间隔件144可形成在第二间隔件142和第三间隔件143上。第四间隔件144可沿着第一导线130的侧部的至少一部分延伸。例如,第四间隔件144可沿着第一间隔件141的未形成第二间隔件142的侧部延伸。

76.第五间隔件145可形成在第三间隔件143上。第五间隔件145可沿着第一导线130的侧部的至少一部分延伸。例如,第五间隔件145可沿着第四间隔件144的侧部延伸。在一些实施例中,第五间隔件145的下表面可形成为低于第四间隔件144的下表面。例如,第五间隔件145的下部可嵌入第三间隔件143中。

77.第一间隔件141、第二间隔件142、第三间隔件143、第四间隔件144和第五间隔件145中的每一个可包括氧化硅、氮氧化硅、氮化硅或其组合。例如,第一间隔件141可包括氮化硅,第二间隔件142可包括氧化硅,第三间隔件143可包括氮化硅,第四间隔件144可包括氧化硅,第五间隔件145可包括氮化硅。

78.在一些实施例中,间隔件结构140可包括空气间隔件140a。空气间隔件140a可由空气或间隙形成。由于空气间隔件140a具有小于氧化硅的介电常数,所以可有效地减小根据一些实施例的半导体装置的寄生电容。例如,第四间隔件144可以是空气间隔件。

79.第二栅电极160可形成在第二基板100和隔离层110上。第二栅电极160可跨过有源区ar和第一导线130在第二方向x1上纵向延伸。例如,第二栅电极160可与有源区ar倾斜交叉,并且可与第一导线130垂直交叉。多个第二栅电极160可彼此间隔开并且沿着第一方向y1以大致恒定的间隔布置。第二栅电极160中的每一个可插置在直接接触件dc和掩埋接触件bc之间以用作根据一些实施例的半导体装置的字线wl。

80.在一些实施例中,第二栅电极160可包括顺序地沉积在第二基板100上的第四子导电图案164和第五子导电图案166。第四子导电图案164和第五子导电图案166中的每一个可包括但不限于金属、多晶硅或其组合。

81.第二栅极介电层162可插置在第二基板100和第二栅电极160之间。第二栅极介电层162可包括但不限于例如氧化硅、氮氧化硅、氮化硅和/或介电常数大于氧化硅的高介电常数(高k)材料。

82.在一些实施例中,第二栅极封盖图案168可形成在第二栅电极160上。第二栅极封

盖图案168可包括但不限于氮化硅。

83.第一氧化物半导体层12和第二氧化物半导体层14可顺序地沉积在第二基板100和元件隔离层110上。第二栅极介电层162和第二栅电极160可顺序地沉积在第二氧化物半导体层14上。因此,第二氧化物半导体层14可用作包括第二栅电极160的晶体管的沟道层。

84.根据一些实施例的半导体装置可以是包括掩埋沟道晶体管(bcat)的半导体存储器装置。掩埋沟道晶体管可指栅电极(例如,第二栅电极160)嵌入在第二基板100中的结构。例如,第二基板100可包括在第二方向x1上延伸的栅极沟槽wt。在一些实施例中,栅极沟槽wt可形成在第二基板100和元件隔离层110中。第一氧化物半导体层12和第二氧化物半导体层14可沿着栅极沟槽wt的轮廓适形延伸。第二栅极介电层162和第二栅电极160可在第二氧化物半导体层14上至少部分地填充栅极沟槽wt的一部分。第二栅极封盖图案168可在第二氧化物半导体层14上至少部分地填充栅极沟槽wt的另一部分。在这些实施例中,第二栅电极160的上表面可低于第二基板100的上表面。

85.尽管第一氧化物半导体层12的最上表面和第二氧化物半导体层14的最上表面被示出为设置在第二基板100的上表面和共面表面上,但这仅是示例。作为另一示例,第一氧化物半导体层12和第二氧化物半导体层14可沿着栅极沟槽wt的一部分的轮廓适形延伸。

86.接触结构bc和lp可形成在第二基板100和元件隔离层110上。接触结构bc和lp可通过穿过基础绝缘层120将第二基板100的有源区ar连接到第一电容器结构190。在一些实施例中,接触结构bc和lp可包括掩埋接触件bc和着陆焊盘lp。

87.掩埋接触件bc可通过穿过基础绝缘层120将第二基板100的有源区ar与着陆焊盘lp连接。例如,第二基板100可包括第二接触沟槽ct2。第二接触沟槽ct2可通过穿过基础绝缘层120暴露有源区ar的第二部分(例如,两端)。掩埋接触件bc可形成在第二接触沟槽ct2中以将有源区ar的第二部分连接到着陆焊盘lp。

88.在一些实施例中,第二接触沟槽ct2的一部分可与元件隔离层110的一部分交叠。因此,第二接触沟槽ct2可暴露元件隔离层110的一部分以及有源区ar的一部分。

89.掩埋接触件bc可形成在间隔件结构140的侧部。掩埋接触件bc可通过间隔件结构140与第一导线130间隔开。在一些实施例中,掩埋接触件bc的上表面可低于第二位线封盖图案139的上表面。

90.掩埋接触件bc可形成彼此间隔开的多个隔离区域。例如,如图3所示,多个掩埋接触件bc可插置在多条第一导线130之间以及多个第二栅电极160之间。在一些实施例中,多个掩埋接触件bc可布置成矩阵形式。

91.掩埋接触件bc可包括导电材料。因此,掩埋接触件bc可电连接到第二基板100的有源区ar。有源区ar的连接到掩埋接触件bc的第二部分(例如,两端)可用作包括第二栅电极160的半导体装置的第二源极/漏极区。掩埋接触件bc可包括例如多晶硅,但实施例不限于此。

92.着陆焊盘lp可形成在掩埋接触件bc上。着陆焊盘lp可被设置为与掩埋接触件bc交叠。在这种情况下,交叠意指在垂直于第二基板100的上表面的第一竖直方向z1上交叠。着陆焊盘lp可连接到掩埋接触件bc的上表面以将有源区ar连接到第一电容器结构190。

93.在一些实施例中,着陆焊盘lp可被设置为与掩埋接触件bc的一部分和第一导线130的一部分交叠。例如,着陆焊盘lp可与掩埋接触件bc的一部分和第二位线封盖图案139

的一部分交叠。在一些实施例中,着陆焊盘lp的上表面可高于第二位线封盖图案139的上表面。在这种情况下,着陆焊盘lp可至少部分地覆盖第二位线封盖图案139的上表面的一部分。

94.着陆焊盘lp可形成彼此间隔开的多个隔离区域。例如,如图3所示,可形成用于限定多个着陆焊盘lp的焊盘沟槽pt。在一些实施例中,焊盘沟槽pt的一部分可暴露第二位线封盖图案139的一部分。例如,焊盘沟槽pt的下表面可低于第二位线封盖图案139的上表面。在这种情况下,多个着陆焊盘lp可通过第二位线封盖图案139和焊盘沟槽pt彼此分离。在一些实施例中,多个着陆焊盘lp可布置成蜂窝形式。

95.着陆焊盘lp可包括导电材料。因此,着陆焊盘lp可电连接到掩埋接触件bc。着陆焊盘lp可包括但不限于钨(w)。

96.在一些实施例中,第一上绝缘层180可形成为至少部分地填充焊盘沟槽pt。第一上绝缘层180可形成在着陆焊盘lp和第二位线封盖图案139上。因此,第一上绝缘层180可限定用于形成多个隔离区域的着陆焊盘lp。

97.第一上绝缘层180可包括绝缘材料。因此,多个着陆焊盘lp可彼此电分离。第一上绝缘层180可包括例如氧化硅、氮化硅、氮氧化硅和/或介电常数小于氧化硅的低k材料,但不限于此。

98.第一电容器结构190可设置在第一上绝缘层180和接触结构bc和lp上。第一电容器结构190可连接到接触结构bc和lp的上表面。例如,第一上绝缘层180可被图案化以暴露着陆焊盘lp的上表面的至少一部分。第一电容器结构190可连接到着陆焊盘lp的上表面的通过第一上绝缘层180暴露的部分。因此,第一电容器结构190可通过接触结构bc和lp电连接到有源区ar的第二部分(例如,两端)。可使用第一导线130和第二栅电极160来控制第一电容器结构190存储数据。

99.第一电容器结构190可包括第一下电极192、第一电容器介电层194和第一上电极196。第一电容器结构190可使用在第一下电极192和第一上电极196之间生成的电位差在第一电容器介电层194中存储电荷。

100.第一下电极192可连接到接触结构bc和lp。例如,第一下电极192可连接到着陆焊盘lp的上表面的通过第一上绝缘层180暴露的部分。在图4和图5中,第一下电极192仅以在第一竖直方向z1上从着陆焊盘lp的上表面延伸的柱形式示出,但这仅是示例。作为另一示例,第一下电极192可为在第一竖直方向z1上从着陆焊盘lp的上表面延伸的圆柱形式。在一些实施例中,多个第一下电极192可布置成蜂窝形式。

101.第一电容器介电层194可形成在第一下电极192上。在一些实施例中,第一电容器介电层194可沿着第一下电极192的侧部和上表面以及第一上绝缘层180的上表面的轮廓适形延伸。

102.第一上电极196可形成在第一电容器介电层194上。尽管图4和图5示出第一上电极196至少部分地填充彼此相邻的第一下电极192之间的区域,但这仅是示例。作为另一示例,第一上电极196可沿着第一电容器介电层194的轮廓适形延伸。

103.图6是示出根据一些实施例的半导体装置的另一示例布局图。图7是沿着图6的线c1-c1截取的截面图。图8是沿着图6的线d1-d1截取的截面图。为了描述方便,与参照图1和图2描述的那些重复的部分将简要描述或省略。

104.参照图6至图8,根据一些实施例的半导体装置包括第三基板200、第二导线220(bl)、下接触层230、第一氧化物半导体层12、隔离绝缘层215、第二氧化物半导体层14、第三栅极介电层240、栅极线250(wl)、上接触层270和第二电容器结构290。

105.第三基板200可以是沉积有基底基板和外延层的结构,但实施例不限于此。第三基板200可以是硅基板、砷化镓基板、硅锗基板和/或绝缘体上半导体(soi)基板。以下描述作为示例将基于第三基板200是硅基板。

106.第二导线220可形成在第三基板200上。例如,第一下绝缘层210可形成在第三基板200上。第二导线220可设置在第一下绝缘层210上。第二导线220可在第四方向y2上纵向延伸。多条第二导线220可在第四方向y2上延伸,并且可在与第四方向y2交叉的第五方向x2上以大致恒定的间隔彼此间隔开。第一下绝缘层210可形成为至少部分地填充第二导线220之间的空间。在一些实施例中,第一下绝缘层210的上表面可设置在与第二导线220的上表面相同的水平高度处。第二导线220可用作根据一些实施例的半导体存储器装置的位线bl。

107.第二导线220可包括掺杂多晶硅、金属、导电金属氮化物、导电金属硅化物、导电金属氧化物或其组合。例如,第二导线220可包括但不限于掺杂多晶硅、al、cu、ti、ta、ru、w、mo、pt、ni、co、tin、tan、wn、nbn、tial、tialn、tisi、tisin、tasi、tasin、rutin、nisi、cosi、iro

x

、ruo

x

或其组合。在其它实施例中,第二导线220可包括二维半导体材料。二维半导体材料可包括石墨烯、碳纳米管或其组合。第二导线220可包括上述导电材料的单层或多层。

108.下接触层230可形成在第二导线220上。例如,下接触层230可沿着第二导线220的上表面延伸。下接触层230可将第二导线220与第二氧化物半导体层14连接。下接触层230可包括但不限于导电材料,例如金属、导电金属氮化物、导电金属碳氮化物、导电金属碳化物、金属硅化物、掺杂半导体材料、导电金属氮氧化物和/或二维(2d)材料。例如,下接触层230可包括氧化铟锡(ito)。

109.第一氧化物半导体层12可形成在第二导线220上。例如,第一氧化物半导体层12可沿着第二导线220的上表面延伸。在一些实施例中,第一氧化物半导体层12可设置在与下接触层230相同的水平高度处。例如,如图7所示,下接触层230可形成在第二导线220的上表面的一部分上,第一氧化物半导体层12可形成在第二导线220的上表面的另一部分上。

110.在一些实施例中,第一氧化物半导体层12可将第二导线220连接到第二氧化物半导体层14。在一些实施例中,第一氧化物半导体层12可在第五方向x2上纵向延伸。如图8所示,第一氧化物半导体层12可连接到沿着第五方向x2布置的多条第二导线220。

111.隔离绝缘层215可形成在第二导线220上。例如,隔离绝缘层215可形成在下接触层230上。隔离绝缘层215可包括在第五方向x2上纵向延伸的沟道沟槽215t。在一些实施例中,隔离绝缘层215可形成在第五方向x2上延伸并通过沟道沟槽215t彼此间隔开的多个绝缘图案。沟道沟槽215t可暴露下接触层230的至少一部分和第一氧化物半导体层12的至少一部分。例如,沟道沟槽215t可暴露下接触层230的上表面和第一氧化物半导体层12的上表面。

112.隔离绝缘层215可包括例如氧化硅、氮氧化硅、氮化硅和/或介电常数小于氧化硅的低k材料,但实施例不限于此.

113.第二氧化物半导体层14可形成在第二导线220上。第二氧化物半导体层14可形成在沟道沟槽215t中。例如,第二氧化物半导体层14可沿着沟道沟槽215t的侧部和下表面延伸。第二氧化物半导体层14可(电)连接到第二导线220,并且可与第一氧化物半导体层12

(物理)接触。例如,沿着沟道沟槽215t的下表面延伸的第二氧化物半导体层14可与下接触层230的上表面和第一氧化物半导体层12的上表面物理接触。

114.根据一些实施例的半导体装置可以是包括竖直沟道晶体管(vct)的半导体存储器装置。竖直沟道晶体管可指沟道层(例如,第二氧化物半导体层14)的沟道长度在垂直于第三基板200的上表面的第二竖直方向z2上延伸的结构。例如,第二氧化物半导体层14可包括沿着水平方向(例如,第四方向y2)和与第五方向x2交叉的第二竖直方向z2布置的第一源极/漏极区和第二源极/漏极区。例如,第二氧化物半导体层14的下部可用作第一源极/漏极区,第二氧化物半导体层14的上部可用作第二源极/漏极区。第二氧化物半导体层14的介于第一源极/漏极区和第二源极/漏极区之间的区域可用作沟道区。

115.在一些实施例中,彼此间隔开的多个第二氧化物半导体层14可形成在第二导线220上。多个第二氧化物半导体层14可通过在第四方向y2和第五方向x2上彼此间隔开以矩阵形式布置。在一些实施例中,在第五方向x2上延伸的第一氧化物半导体层12可与沿着第五方向x2布置的多个第二氧化物半导体层14物理接触。

116.第三栅极介电层240可形成在沟道沟槽215t中的第二氧化物半导体层14上。第三栅极介电层240可插置在第二氧化物半导体层14和栅极线250之间。例如,第三栅极介电层240可沿着第二氧化物半导体层14的内侧和上表面延伸。第三栅极介电层240可包括例如氧化硅、氮氧化硅、氮化硅和/或介电常数大于氧化硅的高k材料,但实施例不限于此。

117.栅极线250可形成在沟道沟槽215t中的第三栅极介电层240上。栅极线250可在第五方向x2上纵向延伸。栅极线250可包括掺杂多晶硅、金属、导电金属氮化物、导电金属硅化物、导电金属氧化物或其组合。例如,栅极线250可包括但不限于掺杂多晶硅、al、cu、ti、ta、ru、w、mo、pt、ni、co、tin、tan、wn、nbn、tial、tialn、tisi、tisin、tasi、tasin、rutin、nisi、cosi、iro

x

、ruo

x

或其组合。

118.在一些实施例中,栅极线250可包括在一个沟道沟槽215t中面向彼此的第三栅电极250a和第四栅电极250b。第三栅电极250a和第四栅电极250b可在第四方向y2上彼此间隔开并且在第五方向x2上纵向延伸。在这种情况下,可实现每第二氧化物半导体层14设置两个晶体管的结构。例如,第三栅电极250a可用作根据一些实施例的半导体装置的第一字线,第四栅电极250b可用作根据一些实施例的半导体装置的第二字线。

119.在一些实施例中,第一屏障绝缘层262和间隙填充绝缘层264可形成在第三栅电极250a和第四栅电极250b之间。第三栅电极250a和第四栅电极250b可通过第一屏障绝缘层262和间隙填充绝缘层264彼此分离。例如,第一屏障绝缘层262可沿着第三栅电极250a的内侧、第二氧化物半导体层14的上表面和第四栅电极250b的内侧延伸。间隙填充绝缘层264可形成在第一屏障绝缘层262上以至少部分地填充第三栅电极250a和第四栅电极250b之间的区域。

120.第一屏障绝缘层262和间隙填充绝缘层264中的每一个可包括但不限于氧化硅、氮氧化硅、氮化硅或其组合。例如,第一屏障绝缘层262可包括氮化硅,间隙填充绝缘层264可包括氧化硅。

121.在一些实施例中,第三栅极封盖图案266可形成在栅极线250上。例如,第三栅极封盖图案266可至少部分地覆盖栅极线250的上表面、第一屏障绝缘层262的上表面和间隙填充绝缘层264的上表面。第三栅极封盖图案266可包括但不限于氮化硅。

122.上接触层270可形成在第二氧化物半导体层14上。例如,上接触层270可连接到第二氧化物半导体层14的上表面。上接触层270可将第二氧化物半导体层14连接到第二电容器结构290。上接触层270可包括但不限于导电材料,例如金属、导电金属氮化物、导电金属碳氮化物、导电金属碳化物、金属硅化物、掺杂半导体材料、导电金属氮氧化物和/或二维(2d)材料。

123.在一些实施例中,可每第二氧化物半导体层14形成两个上接触层270。例如,第二氧化物半导体层14的与第三栅电极250a相邻的上部可连接到一个上接触层270,第二氧化物半导体层14的与第四栅电极250b相邻的上部可连接到另一上接触层270。

124.第二电容器结构290可形成在隔离绝缘层215和上接触层270上。第二电容器结构290可连接到上接触层270的上表面。可使用第二导线220和栅极线250来控制第二电容器结构290存储数据。

125.第二电容器结构290可包括第二下电极292、第二电容器介电层294和第二上电极296。第二电容器结构290可使用在第二下电极292和第二上电极296之间生成的电位差在第二电容器介电层294中存储电荷。

126.第二下电极292可连接到上接触层270。在图7和图8中,第二下电极292仅以在第二竖直方向z2上从上接触层270的上表面延伸的柱形式示出,但这仅是示例。作为另一示例,第二下电极292可为在第二竖直方向z2上从上接触层270的上表面延伸的圆柱形式。在一些实施例中,多个第二下电极292可布置成矩阵形式。

127.第二电容器介电层294可形成在第二下电极292上。在一些实施例中,第二电容器介电层294可沿着第二下电极292的侧部和上表面以及隔离绝缘层215的上表面适形延伸。

128.第二上电极296可形成在第二电容器介电层294上。在图7和图8中,第二上电极296被示出为至少部分地填充彼此相邻的第二下电极292之间的区域,但这仅是示例。在其它实施例中,第二上电极296可沿着第二电容器介电层294的轮廓适形延伸。

129.图9至图11是示出根据一些实施例的半导体装置的各种示例截面图。为了描述方便,与参照图1、图2和图6至图8描述的那些重复的部分将简要描述或省略。

130.参照图9,在根据一些实施例的半导体装置中,第二氧化物半导体层14包括面向彼此的第一沟道部分14a和第二沟道部分14b。

131.第一沟道部分14a和第二沟道部分14b可在第四方向y2上彼此间隔开。例如,第一沟道部分14a可沿着沟道沟槽215t的一侧延伸,第二沟道部分14b可沿着沟道沟槽215t的另一侧延伸。

132.在一些实施例中,第一沟道部分14a和第二沟道部分14b可通过第一屏障绝缘层262和间隙填充绝缘层264彼此分离。例如,第一屏障绝缘层262的最下表面可形成为等于或低于第二氧化物半导体层14的最下表面。结果,第二氧化物半导体层14可被切割以形成第一沟道部分14a和第二沟道部分14b。

133.参照图10,在根据一些实施例的半导体装置中,多个第一氧化物半导体层12沿着第五方向x2布置。

134.沿着第五方向x2布置的多个第一氧化物半导体层12可通过第二下绝缘层212彼此间隔开。在一些实施例中,多个第一氧化物半导体层12可对应于沿着第五方向x2布置的多个第二氧化物半导体层14和多条第二导线220。在这种情况下,每个第一氧化物半导体层12

可将一条第二导线220连接到一个第二氧化物半导体层14。

135.参照图11,在根据一些实施例的半导体装置中,第二氧化物半导体层14的至少一部分与下氧化物层216物理接触。

136.下氧化物层216可形成在第一下绝缘层210上。例如,下氧化物层216可至少部分地覆盖第二导线220的侧部。在一些实施例中,下氧化物层216可至少部分地覆盖第二导线220的侧部和第一氧化物半导体层12的侧部。第二氧化物半导体层14可与下氧化物层216的上表面物理接触。

137.下氧化物层216可包括氧化物。例如,下氧化物层216可包括氧化硅。当第二氧化物半导体层14与下氧化物层216物理接触时,下氧化物层216的氧原子可扩散到第二氧化物半导体层14中。结果,第二氧化物半导体层14的第二结晶氧化物半导体材料可固化,并且可向半导体装置提供改进的性能和可靠性。

138.在一些实施例中,第二屏障绝缘层214可插置在第二导线220和下氧化物层216之间。第二屏障绝缘层214可至少部分地覆盖第二导线220的侧部。第二屏障绝缘层214可减少或防止下氧化物层216的氧原子扩散到第二导线220中。例如,第二屏障绝缘层214可包括但不限于氮化硅。

139.图12是示出根据一些实施例的半导体装置的另一示例布局图。图13是沿着图12的线c2-c2截取的截面图。图14是沿着图12的线d2-d2截取的截面图。为了描述方便,与参照图1、图2和图6至图8描述的那些重复的部分将简要描述或省略。

140.参照图12至图14,在根据一些实施例的半导体装置中,第二氧化物半导体层14与第一氧化物半导体层12的侧部物理接触。

141.例如,如图13所示,第一氧化物半导体层12可形成在下接触层230的上表面的一部分上,第二氧化物半导体层14可形成在下接触层230的上表面的另一部分上。另外,沟道沟槽215t可暴露下接触层230的上表面和第一氧化物半导体层12的侧部。结果,第二氧化物半导体层14可与下接触层230的上表面和第一氧化物半导体层12的侧部物理接触。

142.在一些实施例中,下接触层230可至少部分地覆盖第二导线220的上表面和第一下绝缘层210的上表面。如图14所示,下接触层230可连接到沿着第五方向x2布置的多条第二导线220。下接触层230可连接到在第四方向y2和第五方向x2上彼此间隔开的多个第二氧化物半导体层14。

143.图15至图17是示出根据一些实施例的半导体装置的各种示例截面图。为了描述方便,与参照图1、图2和图6至图14描述的那些重复的部分将简要描述或省略。

144.参照图15,在根据一些实施例的半导体装置中,第二氧化物半导体层14包括面向彼此的第一沟道部分14a和第二沟道部分14b。由于第二氧化物半导体层14与上面参照图9描述的类似,所以将省略其详细描述。

145.参照图16,在根据一些实施例的半导体装置中,多个下接触层230沿着第五方向x2布置。

146.沿着第五方向x2布置的多个下接触层230可通过第二下绝缘层212彼此间隔开。在一些实施例中,多个下接触层230可对应于沿着第五方向x2布置的多个第二氧化物半导体层14和多条第二导线220。在这种情况下,每个下接触层230可将一条第二导线220连接到沿着第四方向y2布置的多个第二氧化物半导体层14。

147.参照图17,在根据一些实施例的半导体装置中,第二氧化物半导体层14的至少一部分与下氧化物层216物理接触。由于第二氧化物半导体层14与上面参照图11描述的类似,所以将省略其详细描述。

148.图18是示出根据一些实施例的半导体装置的另一示例布局图。图19是沿着图18的线c3-c3截取的截面图。图20是沿着图18的线d3-d3截取的截面图。

149.参照图18至图20,在根据一些实施例的半导体装置中,第一氧化物半导体层12在第四方向y2上纵向延伸。

150.如图18所示,第一氧化物半导体层12可与沿着第四方向y2布置的多个第二氧化物半导体层14物理接触。多个第一氧化物半导体层12可沿着第五方向x2布置。

151.尽管图18和图20示出第一氧化物半导体层12在第二竖直方向z2中不与第二导线220交叠,但这仅是示例。作为另一示例,第一氧化物半导体层12的至少一部分可在第二竖直方向z2上与第二导线220交叠。

152.图21至图23是示出根据一些实施例的半导体装置的各种示例截面图。为了描述方便,与参照图1、图2和图6至图20描述的那些重复的部分将简要描述或省略。

153.参照图21,在根据一些实施例的半导体装置中,第二氧化物半导体层14包括面向彼此的第一沟道部分14a和第二沟道部分14b。由于第二氧化物半导体层14与上面参照图9描述的类似,所以将省略其详细描述。

154.参照图22,在根据一些实施例的半导体装置中,多个下接触层230沿着第五方向x2布置。由于下接触层230与上面参照图16描述的类似,所以将省略其详细描述。

155.参照图23,在根据一些实施例的半导体装置中,第二氧化物半导体层14的至少一部分与下氧化物层216物理接触。由于第二氧化物半导体层14与上面参照图11描述的类似,所以将省略其详细描述。

156.以下,将参照图1至图33描述根据示例实施例的半导体装置的制造方法。

157.图24至图27是示出根据一些实施例的半导体装置的制造方法的中间操作的示图。为了描述方便,与参照图1和图2描述的那些重复的部分将简要描述或省略。

158.参照图24,在第一基板10上形成第一初步氧化物半导体层12a。

159.可通过例如沉积工艺来形成第一初步氧化物半导体层12a。第一初步氧化物半导体层12a可包括包含第一金属元素的二元氧化物半导体材料或三元氧化物半导体材料,或者包含彼此不同的第一金属元素和第二金属元素的三元氧化物半导体材料。二元氧化物半导体材料或三元氧化物半导体材料可以是(但不限于)锌氧化物(zno、zn

x

o)、镓氧化物(gao、ga

x

o)、锡氧化物(tio、ti

x

o)、锌氮氧化物(znon、zn

x

oyn)、铟锌氧化物(izo、in

x

znyo)、镓锌氧化物(gzo、ga

x

znyo)、锡锌氧化物(tzo、sn

x

znyo)和/或锡镓氧化物(tgo、sn

x

gayo)。

160.在一些实施例中,第一初步氧化物半导体层12a可包括非结晶氧化物半导体材料。例如,第一初步氧化物半导体层12a可包括非晶gzo。

161.在一些其它实施例中,第一初步氧化物半导体层12a可包括结晶氧化物半导体材料。例如,第一初步氧化物半导体层12a可包括多晶gzo和/或尖晶石gzo。

162.参照图25,执行第一后处理工艺ht1以形成第一氧化物半导体层12。

163.第一后处理工艺ht1可包括例如退火工艺。在一些实施例中,第一后处理工艺ht1可在约700℃或更低的温度下执行。例如,第一后处理工艺ht1可包括在约200℃至约700℃

的温度下执行的退火工艺。

164.随着执行第一后处理工艺ht1,第一初步氧化物半导体层12a可结晶以形成具有结晶度的第一氧化物半导体层12。例如,第一氧化物半导体层12可包括多晶gzo和/或尖晶石gzo。

165.在一些实施例中,可省略第一后处理工艺ht1。例如,当第一初步氧化物半导体层12a包括结晶氧化物半导体材料时,可省略第一后处理工艺ht1。

166.参照图26,在第一氧化物半导体层12上形成第二初步氧化物半导体层14a。

167.可通过例如沉积工艺来形成第二初步氧化物半导体层14a。第二初步氧化物半导体层14a可包括包含第一金属元素和第二金属元素以及不同于第一金属元素和第二金属元素的第三金属元素的四元氧化物半导体材料。例如,四元氧化物半导体材料可以是(但不限于)铟镓锌氧化物(igzo、in

x

gayznzo,)、铟镓硅氧化物(igso、in

x

gaysizo)、铟锡锌氧化物(itzo、in

x

snyznzo)、铟锡镓氧化物(itgo、in

x

snygazo)、锆锌锡氧化物(zzto、zr

x

znysnzo)、铪铟锌氧化物(hizo、hf

x

inyznzo)、镓锌锡氧化物(gzto、ga

x

znysnzo)、铝锌锡氧化物(azto、al

x

znysnzo)和/或镱镓锌氧化物(ygzo、yb

x

gayznzo)。

168.第二初步氧化物半导体层14a可包括非结晶氧化物半导体材料。例如,第二初步氧化物半导体层14a可包括非晶igzo。

169.参照图27,执行第二后处理工艺ht2以形成第二氧化物半导体层14。

170.第二后处理工艺ht2可包括例如退火工艺。在一些实施例中,第二后处理工艺ht2可在约700℃或更低的温度下执行。例如,第二后处理工艺ht2可包括在约200℃至约700℃的温度下执行的退火工艺。

171.随着执行第二后处理工艺ht2,第二初步氧化物半导体层14a可结晶以形成具有结晶度的第二氧化物半导体层14。例如,第二氧化物半导体层14可包括多晶igzo、尖晶石igzo和/或c轴取向结晶(caac)igzo。

172.随后,参照图1,在第一基板10、第一氧化物半导体层12和第二氧化物半导体层14上形成源极/漏极区16、栅极结构20、层间绝缘层30和源极/漏极接触件35。

173.例如,可在第一氧化物半导体层12和第二氧化物半导体层14上形成第一栅极介电层22、第一栅电极24和第一栅极封盖图案26。随后,可执行使用第一栅极封盖图案26作为蚀刻掩模的蚀刻工艺。结果,可形成被图案化的第一氧化物半导体层12和第二氧化物半导体层14。然后,可形成源极/漏极区16、栅极间隔件28、层间绝缘层30和源极/漏极接触件35。结果,可制造上面参照图1描述的半导体装置。

174.在根据一些实施例的半导体装置的制造方法中,第二氧化物半导体层14可形成在第一氧化物半导体层12上以具有高结晶度。详细地,如上所述,包含第一金属元素(或第一金属元素和第二金属元素)的第一氧化物半导体层12可在沉积包含第一金属元素至第三金属元素的第二氧化物半导体层14的工艺中用作种子层以改进第二氧化物半导体层14的结晶度。因此,可提供一种制造具有改进的性能和可靠性的半导体装置的方法。

175.图28至图30是示出根据一些实施例的半导体装置的制造方法的中间操作的示图。为了描述方便,与参照图1至图5和图24至图27描述的那些重复的部分将简要描述或省略。

176.参照图28,在第二基板100中形成栅极沟槽wt。

177.栅极沟槽wt可在第二方向x1上延伸。在一些实施例中,栅极沟槽wt可形成在第二

基板100和元件隔离层110中。

178.参照图29,在栅极沟槽wt中形成第一氧化物半导体层12和第二氧化物半导体层14。

179.可在栅极沟槽wt中顺序地沉积第一氧化物半导体层12和第二氧化物半导体层14。第一氧化物半导体层12和第二氧化物半导体层14中的每一个可沿着栅极沟槽wt的轮廓适形延伸。由于第一氧化物半导体层12和第二氧化物半导体层14形成为与上面参照图24至图27描述的那些类似,所以将省略其详细描述。

180.参照图30,在栅极沟槽wt中形成第二栅极介电层162和第二栅电极160。

181.可在第二氧化物半导体层14上顺序地沉积第二栅极介电层162和第二栅电极160。第二栅极介电层162和第二栅电极160中的每一个可沿着第二氧化物半导体层14的轮廓适形延伸。

182.在一些实施例中,第二栅极介电层162和第二栅电极160可在第二氧化物半导体层14上至少部分地填充栅极沟槽wt的一部分。第二栅极封盖图案168可在第二氧化物半导体层14上至少部分地填充栅极沟槽wt的另一部分。在这种情况下,第二栅电极160的上表面可低于第二基板100的上表面。

183.在形成第二栅极介电层162、第二栅电极160和第二栅极封盖图案168之后,可执行用于暴露第二基板100的上表面的平坦化工艺。

184.随后,参照图3至图5,在第二基板100和元件隔离层110上形成基础绝缘层120、第一导线130(bl)、直接接触件dc、间隔件结构140、接触结构bc和lp以及第一电容器结构190。因此,可制造参照图3至图5描述的包括掩埋沟道晶体管(bcat)的半导体存储器装置。

185.图31至图33是示出根据一些实施例的半导体装置的制造方法的中间操作的示图。为了描述方便,与参照图1、图2和图6至图27描述的那些重复的部分将简要描述或省略。

186.参照图31,在第三基板200上形成第一下绝缘层210、第二导线220和第一氧化物半导体层12。

187.第一下绝缘层210可形成在第三基板200上。第二导线220可形成在第一下绝缘层210上。多条第二导线220可在第四方向y2上延伸,并且可在与第四方向y2交叉的第五方向x2上以大致恒定的间隔彼此间隔开。第一下绝缘层210可形成为至少部分地填充第二导线220之间的空间。

188.第一氧化物半导体层12可形成在第一下绝缘层210和第二导线220上。由于第一氧化物半导体层12形成为与上面参照图24和图25描述的类似,所以将省略其详细描述。

189.参照图32,形成下接触层230和隔离绝缘层215。

190.例如,可执行用于将第一氧化物半导体层12图案化的蚀刻工艺。随后,可形成用于至少部分地填充图案化的第一氧化物半导体层12之间的空间的下接触层230。下接触层230可连接到第二导线220。

191.随后,可在下接触层230和第一氧化物半导体层12上形成隔离绝缘层215。隔离绝缘层215可包括在第五方向x2上纵向延伸的沟道沟槽215t。沟道沟槽215t可暴露下接触层230的至少一部分和第一氧化物半导体层12的至少一部分。例如,沟道沟槽215t可暴露下接触层230的上表面和第一氧化物半导体层12的上表面。

192.参照图33,在沟道沟槽215t中形成第二氧化物半导体层14。

193.第二氧化物半导体层14可沿着沟道沟槽215t的轮廓适形延伸。结果,可形成与下接触层230和第一氧化物半导体层12物理接触的第二氧化物半导体层14。由于第二氧化物半导体层14形成为与上面参照图26和图27描述的类似,所以将省略其详细描述。

194.随后,参照图6至图8,在第二氧化物半导体层14上形成第三栅极介电层240、栅极线250(wl)、上接触层270和第二电容器结构290。因此,可制造参照图6至图8描述的包括竖直沟道晶体管(vct)的半导体存储器装置。

195.尽管参考本发明构思的实施例具体地示出和描述了本发明构思,但是将理解,在不脱离所附权利要求的精神和范围的情况下,可对其进行各种形式和细节上的改变。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。