技术特征:

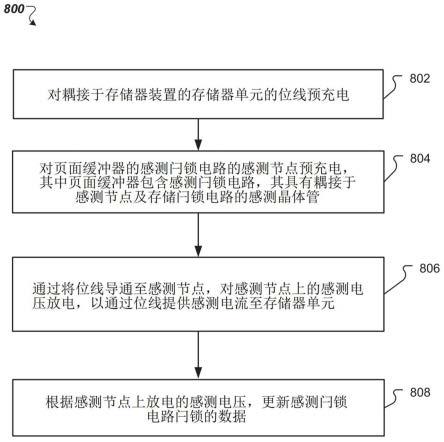

1.一种存储器装置,包含:一存储器阵列,包含多个存储器单元;多个存储器单元线,分别连接至该存储器阵列中这些存储器单元的多条线;一页面缓冲电路,包含耦接至这些存储器单元线的多个页面缓冲器,其中这些页面缓冲器的每一个包含:一感测闩锁电路,包含一感测晶体管,其中该感测晶体管耦接于一感测节点及至少一个感测闩锁单元,该至少一个感测闩锁单元具有耦接于该感测节点的一第一节点及耦接于该感测晶体管的一第二节点;以及一储存闩锁电路,包含至少一个储存闩锁单元,其中至少一个储存闩锁单元包含一第三节点及一第四节点,该第三节点及该第四节点耦接于该感测节点;其中该感测晶体管包含一第一端、一栅极端及一第二端,该第一端耦接于该至少一个感测闩锁单元的该第二节点,该栅极端耦接于该感测节点及该至少一个储存闩锁单元的该第三节点及该第四节点,且该第二端耦接于一接地端。2.根据权利要求1所述的存储器装置,其中每一个该至少一个感测闩锁单元包含:一第一闩锁器,包含一第一反相器;以及一第一闩锁控制电路,耦接于该第一闩锁器及该感测晶体管的该第一端;其中该至少一个储存闩锁单元包含:一第二闩锁器,包含一第二反相器;以及一第二闩锁控制电路,耦接于该第二闩锁器及该感测晶体管的该栅极端。3.根据权利要求2所述的存储器装置,其中该第二闩锁控制电路包含一第一控制晶体管及一第二控制晶体管,其中该第一控制晶体管及该第二控制晶体管的多个源极端耦接于该感测节点及该感测晶体管的该栅极端。4.根据权利要求2所述的存储器装置,其中每一个该至少一个感测闩锁单元还包含一第一耦合电路及该第一闩锁器,该第一耦合电路耦接于该感测节点;其中每一个该至少一个储存闩锁单元还包含一第二耦合电路及该二闩锁器,该第二耦合电路耦接于该感测节点。5.根据权利要求1所述的存储器装置,其中这些页面缓冲器的每一个还包含:一预充电电路,耦接于该感测节点,且用以在一预充电阶段中对该感测节点预充电;以及一位线控制电路,包含一第一控制节点及一第二控制节点,其中该第一控制节点耦接于这些存储器单元的其中一个的一位线,且该第二控制节点耦接于该感测节点;其中该位线控制电路用以:在该预充电阶段中对该位线充电;以及在该预充电阶段后的一放电阶段中,通过导通该感测节点及该位线,使该位线放电,以提供一感测电流至这些存储器单元的其中一个。6.根据权利要求5所述的存储器装置,其中该储存闩锁电路用以:导通该至少一个储存闩锁单元中的一个或多个闩锁控制电路,以更新该至少一个储存闩锁单元中一个或多个闩锁器的一感测结果。7.根据权利要求1所述的存储器装置,其中该感测闩锁电路中的该至少一个感测闩锁

单元的数量及该储存闩锁电路中的该至少一个储存闩锁单元的数量关联于这些存储器单元的一存储器类型。8.根据权利要求1所述的存储器装置,其中该储存闩锁电路并不包含与该感测晶体管实质上相同的晶体管。9.根据权利要求1所述的存储器装置,其中该感测闩锁电路包含实质上与该感测晶体管相同的一个或多个晶体管;其中该感测闩锁电路包含多个感测闩锁单元;以及其中该一个或多个晶体管的数量小于这些感测闩锁单元的数量。10.一种集成电路,包含:一感测闩锁电路,包含:一感测晶体管,耦接于一感测节点;至少一个感测闩锁单元,包含一第一节点及一第二节点,其中该第一节点耦接于该感测节点,该第二节点耦接于该感测晶体管;以及一储存闩锁电路,包含:至少一个储存闩锁单元,包含一第三节点及一第四节点,其中该第三节点及该第四节点耦接于该感测节点;其中该感测晶体管包含:一第一端,耦接于该至少一个感测闩锁单元的该第二节点;一第二端,耦接于一接地端;以及一栅极端,耦接于该感测节点及该至少一个储存闩锁单元的该第三节点及该第四节点。11.根据权利要求10所述的集成电路,其中每一个该至少一个感测闩锁单元包含:一第一闩锁器,包含一第一反相器;以及一第一闩锁控制电路,耦接于该第一闩锁器及该感测晶体管的该第一端;其中该至少一个储存闩锁单元包含:一第二闩锁器,包含一第二反相器;以及一第二闩锁控制电路,耦于该第二闩锁器及该感测晶体管的该栅极端。12.根据权利要求11所述的集成电路,其中每一个该至少一个感测闩锁单元包含:一第一耦合电路,耦接于该感测节点及该第一闩锁器;以及每个该至少一个储存闩锁单元包含:一第二耦合电路,耦接于该感测节点及该第二闩锁器。13.根据权利要求10所述的集成电路,其中该至少一个感测闩锁单元包含多个感测闩锁单元,且这些感测闩锁单元的每一个分别包含一第一节点及一第二节点,其中该第一节点耦接于该感测节点,且该第二节点耦接于该感测晶体管的一漏极端;以及其中该至少一个储存闩锁单元包含多个储存闩锁单元,这些储存闩锁单元的每一个分别包含一第三节点及一第四节点,其中该第三节点耦接于该感测节点,该第四节点耦接于该感测晶体管的该栅极端。14.根据权利要求10所述的集成电路,其中该感测闩锁电路包含至少一个感测晶体管,且该至少一个储存闩锁单元并不包含实质上与该感测晶体管相同的晶体管。

15.根据权利要求10所述的集成电路,其中该感测闩锁电路及该储存闩锁电路用以具备一个等效电容,该等效电容关联于一栅极电容,该栅极电容则关联于该感测晶体管,该等效电容还关联于一个或多个结电容,且该一个或多个结电容关联于该感测闩锁电路及该储存闩锁电路中的多个晶体管。16.根据权利要求10所述的集成电路,还包含:一预充电电路,耦接于该感测节点,且用以在一预充电阶段中对该感测节点预充电;一位线控制电路,包含一第一控制节点及一第二控制节点,其中该第一控制节点耦接于一存储器单元中的一位线,且该第二控制节点耦接于该感测节点;其中该位线控制电路用以:在该预充电阶段中,对该位线进行预充电;以及在该预充电阶段后的一放电阶段中,通过导通该感测节点及该位线,对该感测节点进行放电,以提供一感测电流至该存储器单元。17.根据权利要求16所述的集成电路,其中该感测闩锁电路用以:当该存储器单元储存一0位时,该感测节点上的一感测电压大于一阈值,且该感测晶体管被导通,以将被该至少一个感测闩锁单元所闩锁的一位值改变为0;以及当该存储器单元储存一1位时,该感测节点上的一感测电压小于或等于该阈值,且该感测晶体管被关断,以将被该至少一个感测闩锁单元所闩锁的该位值维持为1;其中该储存闩锁电路用以:导通该至少一个储存闩锁单元中的一个或多个闩锁控制电路,以更新该至少一个储存闩锁单元中一个或多个闩锁器的一感测结果。18.根据权利要求10所述的集成电路,其中该至少一个感测闩锁单元包含一第一类型闩锁器,该至少一个储存闩锁单元包含一第二类型闩锁器,其中该第一类型闩锁器与该第二类型闩锁器不同。19.一种集成电路,包含:一第一闩锁电路,包含一感测晶体管及一个或多个第一闩锁单元,其中该感测晶体管耦接于一感测节点,且该一个或多个第一闩锁单元耦接于该感测晶体管;以及一第二闩锁电路,包含一个或多个第二闩锁单元,其中每一个该一个或多个第二闩锁单元与该一个或多个第一闩锁单元相同;其中该感测晶体管与该第二闩锁电路中的每个晶体管的差异在于,该感测晶体管的一栅极端耦接于该感测节点,且用以作为一栅极电容。20.根据权利要求19所述的集成电路,还包含:一第三电路,用以:在一第一阶段中,分别对该感测节点及一位线预充电,其中该位线耦接于一存储器装置中的一存储器单元,且用以断开与该感测节点的连接;以及在该第一阶段后的一第二阶段中,通过将该感测节点导通至该位线,根据一等效电容对该感测节点的一感测电压放电,以通过该位线在该存储器单元上产生一感测电流,其中该等效电容依据该栅极电容及一个或多个结电容,该栅极电容关联于该感测晶体管,该一个或多个结电容关联于该一个或多个第一闩锁单元及该一个或多个第二闩锁单元中的多个晶体管;

其中该一个或多个结电容中的一整体电容值实质上大于该栅极电容的电容值;其中该第一闩锁电路用以:在该第二阶段后,根据该感测节点上被释放的该感测电压,更新被该第一闩锁电路所闩锁的数据;以及其中该第二闩锁电路用以:导通一个或多个第二晶体管中的至少一个,以将被该第一闩锁电路所闩锁的数据更新至该第二闩锁电路中的至少一个闩锁器。

技术总结

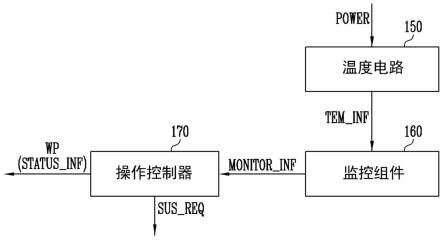

本公开提供了一种存储器装置及集成电路,包含计算机可读介质,用于管理存储器装置中的页面缓冲电路。本公开内容的一方面为存储器装置,包括存储器阵列、耦接于存储器单元的各线的存储器单元线以及具有耦合至存储器单元线的页面缓冲器的页面缓冲电路。每个页面缓冲器包含感测闩锁电路及储存闩锁电路。感测闩锁电路包含耦接于感测节点的感测晶体管及至少一个感测闩锁单元。储存闩锁电路包括至少一个储存闩锁单元,储存闩锁单元具有耦接于感测节点的第三节点和第四节点,以及耦接于感测晶体管的栅极端。感测晶体管的第二端耦接至接地端。感测晶体管的第二端耦接至接地端。感测晶体管的第二端耦接至接地端。

技术研发人员:杨尚辑 高晖曜

受保护的技术使用者:旺宏电子股份有限公司

技术研发日:2022.05.19

技术公布日:2023/2/17

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。