用于dram的刷新管理

背景技术:

1.计算机系统通常使用廉价和高密度的动态随机存取存储器(dram)芯片作为主存储器。当dram芯片中的特定行被激活以进行读取或写入时,与该行相关联的字线被激活,并且沿该行的存储器单元的内容被读取到页面缓冲器中。对该行中的存储器单元的后续读取和写入访问可完全在页面缓冲器内进行,而无需再次访问该行。当数据处理器稍后访问同一存储器存储体中的另一行时,沿该行的存储器单元在可激活另一行之前在预充电操作中复原。

2.现代dram芯片通常使用深亚微米技术存储一至八千兆位(gb)的数据。由于高密度和小特征尺寸,存储器的行在物理上非常靠近其他行,以致于特定行的激活可能通过改变存储器单元电容器上的电荷来扰乱存储在相邻行中的数据。在过去,这些扰乱通常是无害的,因为会周期性地刷新存储器单元。然而,一些存储器访问模式偶尔会导致某些行在下一个刷新循环之前被激活和预充电很多次,以致于相邻行中的存储器单元损坏并反转逻辑状态。在损坏之后,原始数据丢失并且在后续刷新循环中不能复原。随着特征尺寸变得更小,此问题(称为“行锤击(row hammer)”)变得更难缓解,因为引起该问题所需的行激活次数变得更少。

3.解决数据扰乱问题的一种已知技术称为目标行刷新(trr)。为了确保dram行在刷新周期内不被激活太多次,存储器控制器通过设置某些模式寄存器位将dram置于trr模式。控制器然后发布连续的激活和预充电命令到目标行以及两个物理上相邻的行。一旦启用trr模式,就不允许其他模式寄存器命令,直到trr模式完成。trr模式是自清除的,并且模式寄存器位在trr模式完成之后进行设置。虽然trr允许存储器控制器避免在特定时间段内对特定行的过度激活,但它是通过设置模式寄存器进入的,这需要大量的时间,因为在控制器可发布模式寄存器设置命令之前,所有存储体必须处于空闲状态。

附图说明

4.图1以框图形式示出了现有技术中已知的加速处理单元(apu)和存储器系统;

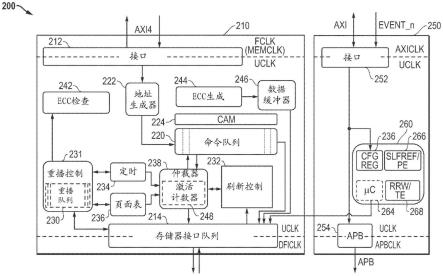

5.图2以框图形式示出了根据一些实施方案的适合于在类似图1的apu的apu中使用的存储器控制器;

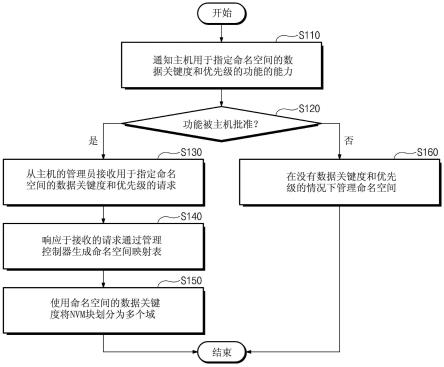

6.图3是根据一些实施方案的用于处理刷新管理的过程的流程图;

7.图4是根据一些实施方案的用于重放命令的过程的流程图;并且

8.图5-图7是根据一些实施方案的例示恢复序列的部分的一系列图示。

9.在以下描述中,在不同附图中使用相同的附图标号指示类似或相同的项。除非另有说明,否则字词“耦接”及其相关联的动词形式包括直接连接和通过本领域已知的方式的间接电连接两者,并且除非另有说明,否则对直接连接的任何描述也意味着使用合适形式的间接电连接的另选实施方案。

具体实施方式

10.存储器控制器包括存储器接口队列、仲裁器、至少一个重放队列、刷新控制电路和重放控制电路。该存储器接口队列包括用于连接到存储通道的输出,该存储通道适于连接到至少一个动态随机存取存储器(dram)。该仲裁器连接到存储器接口队列,用于选择进入的存储器命令并将该存储器命令放置在存储器接口队列中,从而致使该存储器命令通过存储通道来传输。该重放队列存储被放置在存储器接口队列中的存储器访问命令。该刷新控制电路连接到仲裁器并且可操作以监测对通过存储通道发送到存储区域的激活命令的数量进行计数的激活计数器,并且响应于激活计数器高于指定的阈值,向仲裁器发信号通知应发送紧急刷新命令。该重放控制电路检测到指定类型的错误已发生,并且响应于该错误而发起恢复序列,包括从该至少一个重放队列重新传输所选存储器命令。

11.一种方法包括选择性地将存储器命令放置在存储器接口队列中、将存储器命令从存储器接口队列传输到连接到至少一个动态随机存取存储器(dram)的存储通道、以及将所传输的存储器命令的副本存储在重放队列中。该方法对通过存储通道发送到dram的存储区域的激活命令的数量进行计数。响应于激活命令的数量高于指定的阈值,该方法向仲裁器发信号通知应发送紧急刷新命令到该存储区域。响应于检测到指定类型的错误已发生,该方法发起恢复序列,包括从重放队列重新传输所选存储器命令。响应于恢复序列中的指定的错误条件,该方法检查在仲裁器处是否有紧急刷新命令待决,并且如果有,则中断恢复序列并允许发送紧急刷新命令。

12.一种数据处理系统包括:数据处理器;数据织构,该数据织构连接到该数据处理器;以及存储器控制器,该存储器控制器连接到该数据织构以用于履行来自数据处理器的存储器请求。该存储器控制器包括存储器接口队列、仲裁器、至少一个重放队列、刷新控制电路和重放控制电路。该存储器接口队列包括用于连接的存储通道的输出,该存储通道到适于连接到至少一个动态随机存取存储器(dram)。该仲裁器连接到存储器接口队列,用于选择进入的存储器命令并将该存储器命令放置在存储器接口队列中,从而致使该存储器命令通过存储通道来传输。重放队列存储被放置在存储器接口队列中的存储器访问命令。该刷新控制电路连接到仲裁器并且可操作以监测对通过存储通道发送到存储区域的激活命令的数量进行计数的激活计数器,并且响应于激活计数器高于指定的阈值,向仲裁器发信号通知应发送紧急刷新命令。该重放控制电路检测指定类型的错误已发生,并且响应于该错误而发起恢复序列,包括从所述至少一个重放队列重新传输所选存储器命令。

13.图1以框图形式示出了现有技术中已知的加速处理单元(apu)100和存储器系统130。apu 100是适合于用作主机数据处理系统中的处理器的集成电路,并且通常包括中央处理单元(cpu)核心复合体110、图形核心120、一组显示引擎122、存储器管理中心140、数据织构125、一组外围控制器160、一组外围总线控制器170和系统管理单元(smu)180。如普通技术人员将会知道的,apu 100可以不具有每个实施方案中存在的所有这些元素,并且还可具有附加元素包括在其中。此外,apu 100可包括例如系统中的一个或多个集成电路。

14.cpu核心复合体110包括cpu核心112和cpu核心114。在该示例中,cpu核心复合体110包括两个cpu核心,但是在其他实施方案中,cpu核心复合体110可包括任意数量的cpu核心。cpu核心112和114中的每一个核心双向连接到形成控制织构的系统管理网络(smn)和数据织构125,并且能够将存储器访问请求提供到数据织构125。cpu核心112和114中的每一个

核心可以是一体式核心,或者可以进一步是具有共享某些资源诸高速缓存的两个或更多个一体式核心的核心复合体。

15.图形核心120是高性能图形处理单元(gpu),该gpu能够以高度集成和并行方式执行图形操作诸如顶点处理、片段处理、着色、纹理混合等。图形核心120双向连接到smn和数据织构125,并且能够将存储器访问请求提供到数据织构125。就此而言,apu 100可支持其中cpu核心复合体110和图形核心120共享相同存储空间的统一存储器架构,或其中cpu核心复合体110和图形核心120共享存储空间的一部分、同时图形核心120还使用cpu核心复合体110不能访问的私有图形存储器的存储器架构。

16.显示引擎122渲染并光栅化由图形核心120生成的对象以供在监测器上显示。图形内核120和显示引擎122双向连接到公共存储器管理集线器140以用于统一转换为存储器系统130中的适当地址,并且存储器管理集线器140双向连接到数据织构125以用于生成此类存储器访问并且接收从存储器系统返回的读取数据。

17.数据织构125包括用于在任何存储器访问代理和存储器管理集线器140之间路由存储器访问请求和存储器响应的横杆开关。数据织构还包括由基本输入/输出系统(bios)定义的、用于基于系统配置确定存储器访问的目的地的系统存储器映射,以及用于每个虚拟连接的缓冲器。

18.外围控制器160包括通用串行总线(usb)控制器162和串行高级技术附件(sata)接口控制器164,它们中的每一者双向连接到系统集线器166和smn总线。这两个控制器仅仅是可用于apu 100的外围控制器的示例。

19.外围总线控制器170包括系统控制器或“南桥”(sb)172以及外围部件互连高速(pcie)控制器174,它们中的每一者双向连接到输入/输出(i/o)集线器176和smn总线。i/o集线器176也双向连接到系统集线器166和数据织构125。因此,例如,cpu核心可通过数据织构125通过i/o集线器176路由的访问对usb控制器162、sata接口控制器164、sb 172或pcie控制器174中的寄存器进行编程。apu 100的软件和固件存储在系统数据驱动器或系统bios存储器(未示出)中,系统数据驱动器或系统bios存储器可以是多种非易失性存储器类型中的任一种,诸如只读存储器(rom)、闪存电可擦除可编程rom(eeprom)等。通常,bios存储器通过pcie总线访问,并且系统数据驱动器通过sata接口。

20.smu 180是控制apu 100上的资源的操作并使这些资源之间的通信同步的本地控制器。smu 180管理apu 100上的各种处理器的上电定序,并且经由复位、启用和其他信号控制多个芯片外装置。smu 180包括一个或多个时钟源(未示出),诸如锁相环路(pll),以为apu 100的每个部件提供时钟信号。smu 180还管理各种处理器和其他功能块的功率,并且可从cpu核心112和114以及图形核心120接收测量功率消耗值以确定适当的功率状态。

21.在该实施方案中,存储器管理集线器140及其相关联的物理接口(phy)151和152与apu 100集成。存储器管理集线器140包括存储通道141和142以及功率引擎149。存储通道141包括主机接口145、存储通道控制器143和物理接口147。主机接口145通过串行存在检测链路(sdp)将存储通道控制器143双向连接到数据织构125。物理接口147将存储通道控制器143双向连接到phy 151,并且符合ddr phy接口(dfi)规范。存储通道142包括主机接口146、存储通道控制器144和物理接口148。主机接口146通过另一个sdp将存储通道控制器144双向连接到数据织构125。物理接口148将存储通道控制器144双向连接到phy 152,并且符合

dfi规范。功率引擎149通过smn总线双向连接到smu 180,通过apb连接到phy 151和152,并且还双向连接到存储通道控制器143和144。phy 151具有到存储通道131的双向连接。phy 152具有双向连接存储通道133。

22.存储器管理集线器140是具有两个存储通道控制器的存储器控制器的实例化,并且使用共享功率引擎149以将在下面进一步描述的方式控制存储通道控制器143和存储通道控制器144两者的操作。存储通道141和142中的每一个存储通道可连接到现有技术的ddr存储器(诸如ddr版本四(ddr 4)、低功率ddr4(lpddr 4)、图形ddr版本五(gpddr 5))和高带宽存储器(hbm),并且可适于未来存储器技术。这些存储器提供高总线带宽和高速操作。同时,它们还提供低功率模式以节省电池供电应用诸如膝上型计算机的功率,并且还提供内置热监测。

23.存储器系统130包括存储通道131和存储通道133。存储通道131包括连接到ddrx总线132的一组双列直插存储模块(dimm),包括代表性的dimm 134、136和138,它们在该示例中对应于单独存储列。同样,存储通道133包括连接到ddrx总线129的一组dimm,包括代表性的dimm 135、137和139。

24.apu 100作为主机数据处理系统的中央处理单元(cpu)操作并且提供在现代计算机系统可用的各种总线和接口。这些接口包括两个双数据速率(ddrx)存储通道、用于连接到pcie链路的pcie根复合体、用于连接到usb网络的usb控制器以及到sata大容量存储装置的接口。

25.apu 100还实现各种系统监测和功率节省功能。具体地,一个系统监测功能是热监测。例如,如果apu 100变热,则smu 180可降低cpu核心112和114和/或图形核心120的频率和电压。如果apu 100变得过热,则可完全关断apu 100。smu 180还可经由smn总线从外部传感器接收热事件,并且作为响应,smu 180可降低时钟频率和/或电源电压。

26.图2以框图形式示出了适合于在类似于图1的apu的apu中使用的存储器控制器200。存储器控制器200通常包括存储通道控制器210和功率控制器250。存储通道控制器210通常包括接口212、存储器接口队列214、命令队列220、地址生成器222、内容可寻址存储器(cam)224、包括重播队列230的重播控制逻辑231、刷新逻辑块232、定时块234、页面表236、仲裁器238、纠错码(ecc)检查电路242、ecc生成块244和数据缓冲器246。

27.接口212具有通过外部总线到数据织构125的第一双向连接,并且具有输出。在存储器控制器200中,该外部总线与由arm holdings,plc of cambridge,england规定的高级可扩展接口版本四(称为axi4)兼容,但在其他实施方案中可以是其他类型的接口。接口212将存储器访问请求从称为fclk(或memclk)域的第一时钟域转换到存储器控制器200内部的称为uclk域的第二时钟域。类似地,存储器接口队列214提供从uclk域到与dfi接口相关联的dficlk域的存储器访问。

28.地址生成器222解码通过axi4总线从数据织构125接收的存储器访问请求的地址。存储器访问请求包括物理地址空间中以归一化格式表示的访问地址。地址生成器222将归一化地址转换成可用于对存储器系统130中的实际存储器装置进行寻址以及高效地调度相关访问的格式。该格式包括将存储器访问请求与特定存储列、行地址、列地址、存储体地址和存储体组相关联的区域标识符。在启动时,系统bios查询存储器系统130中的存储器装置以确定它们的大小和配置,并且对与地址生成器222相关联的一组配置寄存器进行编程。地

址生成器222使用存储在配置寄存器中的配置来将归一化地址转换成适当格式。命令队列220是从apu 100中的存储器访问代理诸如cpu核心112和114以及图形核心120接收的存储器访问请求的队列。命令队列220存储由地址生成器222解码的地址字段以及允许仲裁器238高效地选择存储器访问的其他地址信息,包括访问类型和服务质量(qos)标识符。cam 224包括实施排序规则诸如写后写(waw)以及写后读(raw)排序规则的信息。

29.纠错码(ecc)生成块244确定要发送到存储器的写入数据的ecc。ecc检查电路242针对传入ecc检查所接收的ecc。

30.重播队列230是用于存储由仲裁器238选取的所选择的存储器访问的临时队列,所选择的存储器访问正在等待响应,诸如地址和命令奇偶响应。重播控制逻辑231访问ecc检查电路242以确定所返回的ecc是正确的还是指示错误。重播控制逻辑231发起并控制恢复序列,其中在这些循环中的一个循环的奇偶或ecc错误的情况下重播访问。所重播的命令放置在存储器接口队列214中。

31.刷新控制逻辑232包括用于各种掉电、刷新和终端电阻(zq)校准循环的状态机,这些循环与从存储器访问代理接收的正常读取和写入存储器访问请求分开生成。例如,如果存储器存储体处于预充电掉电,则必须周期性地唤醒该存储器存储体以运行刷新循环。刷新控制逻辑232周期性地且响应于指定条件而生成刷新命令,以防止由于电荷从dram芯片中的存储器单元的存储电容器泄漏而引起的数据错误。存储区域在一些实施方案中是存储器存储体,并且在其他实施方案中是存储器子存储体,如下文进一步讨论。刷新控制逻辑232还生成刷新命令,这些刷新命令包括刷新(ref)命令和刷新管理(rfm)命令两者,其中rfm命令引导存储器执行刷新功能以减轻行锤击问题,如下文进一步描述。此外,刷新控制逻辑232周期性地校准zq以防止由于系统的热变化而导致的片上终端电阻的失配。

32.仲裁器238双向连接到命令队列220并且是存储通道控制器210的核心。仲裁器238通过智能调度访问来提高效率以提高存储器总线的使用率。仲裁器238使用定时块234通过基于dram定时参数确定命令队列220中的某些访问是否有资格发布来实施正确的定时关系。例如,每个dram在激活命令之间具有最小规定时间,称为“t

rc”。定时块234维持一组计数器,该组计数器基于该定时参数和jedec规范中规定的其他定时参数来确定资格,并且定时块双向连接到重播队列230。页面表236维持关于仲裁器238的存储通道的每个存储体和存储列中的活动页面的状态信息,并且双向连接到重播队列230。仲裁器238包括激活计数器248,在该实施方案中,该激活计数器包括用于每个存储区域的计数器,该计数器对通过存储通道发送到存储区域的激活命令的数量进行计数。仲裁器238双向连接到刷新控制逻辑232以监测刷新命令并引导刷新活动。

33.响应于从接口212接收到写入存储器访问请求,ecc生成块244根据写入数据计算ecc。数据缓冲器246存储所接收的存储器访问请求的写入数据和ecc。当仲裁器238选取对应写入访问以供分派到存储通道时,数据缓冲器将组合写入数据/ecc输出到存储器接口队列214。

34.功率控制器250通常包括到高级可扩展接口版本一(axi)的接口252、高级外围总线(apb)接口254和功率引擎260。接口252具有到smn的第一双向连接,该第一双向连接包括用于接收图2中单独示出的标记为“event_n”的事件信号的输入,以及输出。apb接口254具有连接到接口252的输出的输入,以及用于通过apb连接到phy的输出。功率引擎260具有连

接到接口252的输出的输入,以及连接到存储器接口队列214的输入的输出。功率引擎260包括一组配置寄存器262、微控制器(μc)264、自刷新控制器(slfref/pe)266和可靠读/写定时引擎(rrw/te)268。配置寄存器262通过axi总线编程,并且存储配置信息以控制存储器控制器200中各种块的操作。因此,配置寄存器262具有连接到这些块的输出,这些块在图2中未详细示出。自刷新控制器266是除了由刷新控制逻辑232自动生成刷新之外还允许手动生成刷新的引擎。可靠读/写定时引擎268向存储器或i/o装置提供连续存储器访问流,用于诸如ddr接口最大读取延迟(mrl)训练和回送测试等目的。

35.存储通道控制器210包括允许仲裁器选取存储器访问以供分派到相关联存储通道的电路系统。为了做出期望的仲裁决定,地址生成器222将地址信息解码成预解码信息,预解码信息包括存储器系统中的存储列、行地址、列地址、存储体地址和存储体组,并且命令队列220存储预解码信息。配置寄存器262存储配置信息以确定地址生成器222解码所接收的地址信息的方式。仲裁器238使用所解码的地址信息、由定时块234指示的定时资格信息以及由页面表236指示的活动页面信息来高效地调度存储器访问,同时遵守诸如服务质量(qos)要求等其他标准。例如,仲裁器238实现对访问打开页面的优先,以避免改变存储页面所需的预充电和激活命令的开销,并且通过将对一个存储体的开销访问与对另一个存储体的读和写访问交错来隐藏对一个存储体的开销访问。特别是在正常操作期间,仲裁器238通常保持页面在不同存储体中打开,直到需要对这些页面进行预充电,然后选择不同的页面。在一些实施方案中,仲裁器238至少基于相应命令的目标存储区域的激活计数器248的相应值来确定命令选择的资格。

36.图3是根据一些实施方案的用于处理刷新管理的过程300的流程图。过程300在一些实施方案中由刷新控制逻辑232(图2)执行,并且或者在其他实施方案中由存储器控制器数字逻辑或具有类似功能性的控制器执行。在该实施方案中,刷新控制逻辑232连接到仲裁器238并且可操作以监测激活计数器248,该激活计数器对通过存储通道发送到存储区域的激活命令的数量进行计数,如框302处所示。存储区域在一些实施方案中是存储器存储体,但是在其他实施方案中是存储器子存储体,如下文进一步讨论。对每个存储区域重复过程300。在框304处,如果刷新(ref)命令发布到相应的所监测区域,则过程300通过将计数器递减第一指定量来管理计数器。框304考虑了指向特定存储器存储体的“每存储体”ref命令,以及指向特定存储器存储体中的所有存储体的“所有存储体”ref命令。例如,在一个实施方案中,响应于ref命令被发布到存储器存储体,无论它是每存储体ref还是所有存储体ref,都将存储器存储体的激活计数器递减50。因此,对于所有受影响的存储体,所有存储体ref命令致使多个激活计数器递减。如框306处所示,当rfm命令发布到存储区域时,过程300还通过将计数器递减第二指定量来考虑刷新管理(rfm)命令的发布。例如,在一个实施方案中,响应于rfm命令发布到存储器存储体,将存储器存储体的激活计数器递减100。如将理解的,递减(或递增)的量是示例性的,并且可采用其它值。此外,可动态地改变第一量、每区域或如参考示例性实施方案所描述的每存储体量、和/或第二量(示例性实施方案中的所有存储体量),以反映存储器设备的各种特性-例如,老化、电压、温度等,其可能影响存储器需要刷新的频率。

37.当激活计数器248通过框302、304和306更新时,过程300监测值,如框308-320处所示,除了发布到存储区域的正常ref命令之外,这些框还采取各种刷新管理动作。通常,过程

300用于提供某种类型的刷新命令(ref或rfm),同时优选由刷新控制逻辑232(图2)的周期性刷新功能创建的ref命令。这种优先通过以下方式实现:响应于激活计数器高于中间管理阈限值且低于最大管理阈限值,确定针对存储区域的待决刷新(ref)命令当前是否保持在刷新控制电路处,并且如果不是,则致使刷新管理(rfm)命令被发送到存储区域。如果是,则允许发布待决ref命令,而不发布rfm命令。响应于激活计数器等于或高于最大管理阈限,该过程致使为该存储区域调度rfm命令,并且防止任何新的激活命令被调度到该存储区域,直到rfm命令被调度或者待决ref命令被调度。在不同的实施方案中,使用不同的逻辑过程来实现这一点。

38.在所描绘的过程300中,框308监测激活计数器248的值。如果在框310处,值等于或高于最大管理阈限,则过程300进行到框316,在框316处,过程检查针对存储区域的ref命令是否在仲裁器238处待决。框316检查应用于所考虑的存储体的“每存储体”ref命令和“所有存储体”ref命令。如果任一类型ref命令中覆盖所考虑的存储体的一者待决,则过程进行到框318,在框318处,其发信号通知仲裁器使待决ref命令优先以要求对它进行调度和发布。如果在框316处不存在待决ref命令,则过程300进行到框320,在框320处,过程创建要由仲裁器调度的新rfm命令。在框318或320中的任一个框之后,过程300进行到框322,在框322处,过程防止任何激活命令在仲裁器238处被调度,直到新创建的rfm命令被调度或者待决ref被调度。在一些另选实施方案中,刷新控制电路进一步可操作以响应于在框310处激活计数器248的指定条件诸如超过最大阈限,致使存储区域的刷新速率增加一倍,直到指定条件得到补救。除了或代替在框320处创建rfm命令,可执行这种速率增加。在一些实施方案中,刷新控制逻辑能够配置为包括速率增加。

39.如果在框310处激活计数器248不高于最大管理阈限,则框314检查激活计数器248是否等于或高于中间管理阈限。如果不是,则框315简单地返回到框308以继续监测激活计数器。如果是,则过程300进行到框324,在框324处,过程检查针对存储区域的ref命令是否在仲裁器238处待决。框316检查应用于所考虑的存储体的“每存储体”ref命令和“所有存储体”ref命令。如果任一类型ref命令中覆盖所考虑的存储体的一者待决,则过程进行到框326,在框326处,过程发信号通知仲裁器使待决ref命令优先以要求对它进行调度和发布。如果不是,则过程300进行到框328,在框328处,过程创建要由仲裁器调度的新rfm命令。

40.虽然按次序示出了所描绘的过程框,但是此次序不是限制性的,并且所描绘的逻辑功能性或其逻辑等同物通常由并行操作的各种数字逻辑电路实现。在各种实施方案中,数字逻辑电路以各种方式执行激活计数器监测,诸如通过对激活计数器的变化作出响应或重复地将激活计数器值与中间阈限值和最大阈限值中的一者或两者进行比较。在逻辑功能的每个所描绘分支完成之后,框308处的监测继续。

41.中间管理阈限和最大管理阈限优选地可调整以允许存储器控制器与来自各种制造商的不同dram模块良好合作,对于这些模块,ref命令和rfm命令通常在其实施方式方面有所变化。在一些实施方案中,允许将中间管理阈限和最大管理阈限设置为相同的值以实现监测过程的简化版本。将这两个阈限值设置为相等优选地作用来禁用最大管理阈限逻辑(框310),并且允许实现中间管理阈限比较的逻辑(框314、315、324、326和328)处理计数器超过相等阈限值的情况。由此,此类实施方式用来在存在待决ref命令时优选待决ref命令,而不是创建新rfm命令。这种优先通常提高效率,因为在各种dram模块实施方式中,ref命令

通常比rfm命令更快。

42.在各种实施方案中,针对其监测激活计数器的存储区域是存储器存储体或子存储体。当存储区域是存储器存储体的子存储体时,刷新控制电路可操作以监测存储器存储体的相应多个子存储体的多个激活计数器,并且在存储体级别应用ref命令和rfm命令。此类命令致使存储体内子存储体的所有子存储体激活计数器更新。类似地,所有存储体ref命令致使相应存储列内的所有子存储体的子存储体激活计数器更新。因此,过程300可操作以在多个子存储体的粒度级别监测激活计数器,并且允许或致使ref命令和rfm命令在所选择的存储器存储体的粒度级别发布。刷新控制电路可能够配置为提供存储器存储体或子存储体的激活计数器,刷新管理过程也可调整以考虑存储体或子存储体。

43.图4是根据一些实施方案的用于重放命令的过程的流程图400。在所示实施方案中,所描绘的过程由重放控制逻辑231(图2)管理,但在其它实施方案中,可由实施所描述功能的另一合适的数字逻辑电路管理。该过程开始于框402,在框402处,传出命令的副本被放置在重放队列(230,图2)以被保存直到所述命令被履行而没有错误为止。在框404处,当命令被履行而没有错误时,将其从重放队列中移除。这个将命令放置在重放队列中直到其被履行的序列继续,直到检测到需要恢复序列的错误,如框406所示。

44.框406处的过程检测在dram模块(例如,dimm)中的一者处或在存储通道上是否存在需要恢复序列的错误。当检测到此类错误时,过程从框406前进到框408,在框408处,清除dram模块处的错误。框408包括:如果检测到奇偶错误,则清除存储信道上每个dram模块处的奇偶错误。如果在框406处检测到写入或读取ecc错误,则框408清除写入或读取ecc状态。在一些实施方案中,如果过程不能确定错误类型,则清除两种错误类型的错误,以确保完全清除错误状态。

45.在框410处,存储器控制器在框处重置phy的先进先出(fifo)缓冲区。如果多用途寄存器(mpr)模式当前是活跃的,则在重置之前将其禁用。框410还可包括请求写入信用,如果需要的话。如果mpr模式在恢复序列之前是活跃的,则然后再次启用其,以便将dimm放置在与发生所述错误时其所处于的相同条件下来重放必要的命令。此时,恢复序列已重置并清除了通道和dimm的各个部分。然而,在发送命令以实施恢复序列(这占用命令总线一段时间)之前,该过程处理刷新命令以便避免违反对于ref命令之间的最大时间的限制,并且基于计数激活命令处理可能已经针对特定区域生成的rfm命令。

46.为了处理此类命令,框412处的过程在重新传输恢复序列中的命令之前检查是否有紧急刷新或推迟的刷新命令待决。该实施方案中的紧急刷新命令是由图3的刷新管理过程(诸如在框312、框320和框328处)生成或优先化的ref或rfm命令中的任意者。其它实施方案使用与图3中不同的过程来提供紧急刷新命令。例如,一些实施方案中的紧急刷新命令是响应于激活计数器处对于存储区域(诸如存储体、子存储体或线)的非期望值而生成的ref或rfm命令。另外的实施方案可以不使用激活计数器来生成紧急刷新命令,而是监测由基础的周期性刷新循环创建的刷新条件,并且在需要时插入紧急刷新命令。刷新控制电路包括输出、或标记或类似指示符,其向仲裁器238(图2)和重放控制电路231发信号通知特定刷新命令是紧急的。通常,该信号指示该命令必须在任何进一步的激活命令被发送给受影响的存储区域之前被发送。推迟的刷新命令是待决的ref命令,其被推迟,使得如果恢复循环持续太久,则可能违反存储区域的最大ref到ref间隔。例如,一些ddr标准规定刷新之间的最

大间隔为所定义时间间隔tref1的5倍。

47.如果在框412处存在紧急刷新命令或推迟的刷新命令,则过程在框414处中断恢复序列并且允许仲裁器传输紧急刷新命令和/或推迟的刷新命令。可在该框处传输多个刷新命令以用于不同存储区域。如果在框412处没有紧急刷新命令待决,则过程直接前进到框416以继续恢复序列。

48.接下来,在框418处,过程从重放队列从所选命令开始重放命令。通常,命令按其最初被传输的确切顺序被重放。所重放的命令被放置在存储器接口队列中用于传输给dram。在一些实施方案中,所选命令包括任何读取、写入、和mpr相关命令。随着恢复序列重放命令,在框420处,过程监测错误。如果在恢复序列期间接收到错误消息,则框420处的过程确定该错误是否是会需要重新开始恢复序列的指定类型的。例如,在该实施方案中,命令奇偶错误需要重新开始恢复序列。其它类型的错误也可满足指定条件。如果错误条件不满足指定条件,则框420处的过程返回到框418并且继续重新传输恢复序列中的命令。

49.如果在框420处存在指定的错误状态,则除了在框406处检测到的原始错误之外,其代表第二或另外的错误。这个附加错误导致“递归”恢复序列,其中恢复序列重新开始。在一些情况下,此类重新开始可使刷新管理过程在提供适当刷新命令时滞后。在一些情况下,如果在重放队列中的所有命令被传输之前发生错误,则恢复序列可能必须重新开始多于一次。所描绘的过程每当恢复序列被重新开始时就针对紧急刷新命令和推迟的刷新命令进行检查(框412)。当重放队列中所有命令的传输完成并且命令被履行时,认为恢复序列完成,并且存储器控制器结束恢复序列并且返回到其正常操作状态,其中仲裁器选择要传输的命令。

50.图5-图7是根据一些实施方案例示恢复序列的部分的一系列图示。图5是例示在恢复序列开始之前的示例场景的图示500。仲裁器诸如仲裁器238(图2)从命令队列中选择进入的命令用于放置在存储器接口队列(图5中的“队列”)中。该操作由箭头501描绘,其示出按仲裁器选择的顺序放置在队列中的命令。箭头502描绘所述命令的副本被放置在重放队列中。箭头503描绘通过phy层和存储通道从队列传输到dram模块的命令。

51.图6是示出图5的场景以箭头504继续的图示600,该箭头指示错误消息正指示错误诸如命令奇偶错误或ecc或crc检查错误,指示在通道上已发生了不可校正的错误。这使得恢复序列如上所述开始。然后按照箭头505所描绘的顺序重放来自重放队列的命令,示出了添加到队列的来自重放队列的命令。然后,如箭头506所示,通过通道传输这些命令。

52.图7是示出其中在恢复序列期间已发生指定的错误条件从而需要重新开始恢复序列的稍后场景的图示700。在重新开始时,存在紧急刷新命令要传输,如箭头507所示。在被重新开始的恢复序列中的命令被传输之前,紧急刷新命令被放置在队列中用于传输,如箭头508所示。然后将重放队列中的命令添加到所述队列以用于传输,如箭头509所示。

53.虽然在该实施方案中,紧急刷新命令能够在错误条件需要恢复序列重新开始时被传输,但是在其它实施方案中,对紧急刷新命令的检查(框412,图4)可在过程中的附加点或过程中的其它点处执行。例如,所述检查可发生在恢复序列的开始处,或者如果重放队列大到足以保证进一步的检查,则对于紧急刷新的周期性检查可在恢复序列期间发生,而没有错误条件,如框420的错误条件。

54.图2的存储器控制器200或其任何部分(诸如仲裁器238和刷新控制电路232)可由

呈数据库或可由程序读取并且直接或间接地用于制造集成电路的其他数据结构形式的计算机可访问数据结构描述或表示。例如,该数据结构可以是高级设计语言(hdl)诸如verilog或vhdl中的硬件功能性的行为级描述或寄存器传送级(rtl)描述。描述可由合成工具读取,合成工具可合成描述以产生包括来自合成馆的门列表的网表。网表包括门集,门集也表示包括集成电路的硬件的功能性。然后可以放置和路由网表以产生描述待应用于掩模的几何形状的数据集。然后可以在各种半导体制造步骤中使用掩模以产生集成电路。另选地,计算机可访问存储介质上的数据库可以是网表(具有或不具有合成库)或数据集(根据需要)或图形数据系统(gds)ii数据。

55.虽然已描述了特定实施方案,但是对这些实施方案的各种修改对于本领域技术人员将是显而易见的。例如,存储通道控制器210和/或功率引擎250的内部架构在不同实施方案中可有所变化。存储器控制器200可接口连接到除了ddrx之外的其他类型的存储器,诸如高带宽存储器(hbm)、rambus dram(rdram)等。虽然所示的实施方案示出了对应于单独dimm或simm的每个存储器存储列,但在其他实施方案中,每个模块可支持多个存储列。再其他实施方案可包括其他类型的dram模块或特定模块中未包含的dram,诸如安装到主机母板的dram。因此,所附权利要求书旨在覆盖所公开实施方案的落入所公开实施方案的范围内的所有修改。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。