1.本公开涉及电荷引导式(charge-steering)放大器,尤其涉及以电荷引导式放大器实作的放大电路。

背景技术:

2.图1是现有电荷引导式放大器的电路图。电荷引导式放大器100亦称为动态放大器(dynamic amplifier),主要由晶体管110及晶体管120构成,还包含开关130、开关140、开关150、开关160、电容170、电容180及电容190。各元件的连接方式如图所示。电荷引导式放大器100交替操作于重置阶段(开关130、开关140及开关160导通且开关150不导通,使得电容170及电容180充电且电容190放电)及放大阶段(开关130、开关140及开关160不导通且开关150导通,使得电容170及电容180放电且电容190充电)。电荷引导式放大器100在放大阶段放大差分输入信号vi(从节点n1及节点n2输入),并产生输出信号vo(从节点n3及节点n4输出)。电荷引导式放大器100的操作细节为本技术领域技术人员所熟知,不再赘述。

3.然而,电容170及电容180充放电一次只产生一个输出信号vo(即,能源使用效率不佳),且电荷引导式放大器100只对差分输入信号vi放大一次便产生输出信号vo(即,增益较差,导致节点n3的电压及节点n4的电压不容易区分),因此需要一种放大电路来解决上述问题的至少其中之一。

技术实现要素:

4.鉴于现有技术的不足,本发明的一目的在于提供一种放大电路,以改善现有技术的不足。

5.本发明的一实施例提供一种放大电路,该放大电路具有一第一输出端及一第二输出端,且包含:一第一电荷引导式放大器、一第二电荷引导式放大器、一第一开关以及一第二开关。第一电荷引导式放大器包含一第一输入端、一第二输入端、一第一电容及一第二电容,用来于一第一操作时段放大一第一输入信号。第二电荷引导式放大器包含一第三输入端、一第四输入端、该第一电容及该第二电容,用来于一第二操作时段放大一第二输入信号。第一开关耦接于该第一输出端与一第一目标电压或一第二目标电压之间。第二开关耦接于该第二输出端与该第一目标电压或该第二目标电压之间。该第一电容耦接于该第一输出端与一参考电压之间,而该第二电容耦接于该第二输出端与该参考电压之间。该第一电容及该第二电容于该第一操作时段充电,且该第一电容及该第二电容于该第二操作时段放电。

6.本发明的另一实施例提供一种电荷引导式放大电路,该电荷引导式放大电路具有一第一输入端、一第二输入端、一第三输入端、一第四输入端、一第一输出端及一第二输出端,且包含:一第一晶体管、一第二晶体管、一第三晶体管、一第四晶体管、一第一电容、一第二电容、一第三电容、一第四电容、一第一开关、一第二开关、一第三开关、一第四开关、一第五开关、一第六开关。第一晶体管具有一第一端、一第二端及一第一控制端,其中,该第一控

制端电连接该第一输入端,且该第二端电连接该第一输出端。第二晶体管具有一第三端、一第四端及一第二控制端,其中,该第二控制端电连接该第二输入端,该第四端电连接该第二输出端,且该第三端电连接该第一端。第三晶体管具有一第五端、一第六端及一第三控制端,其中,该第三控制端电连接该第三输入端,且该第六端电连接该第一输出端。第四晶体管具有一第七端、一第八端及一第四控制端,其中,该第四控制端电连接该第四输入端,该第八端电连接该第二输出端,且该第七端电连接该第五端。第一电容耦接于该第一端与一参考电压之间。第二电容耦接于该第五端与该参考电压之间。第三电容耦接于该第一输出端与该参考电压之间。第四电容耦接于该第二输出端与该参考电压之间。第一开关耦接于该第一电容与该第一端之间。第二开关耦接于该第一电容,当该第二开关导通时该第一电容放电。第三开关耦接于该第二电容与该第五端之间。第四开关耦接于该第二电容,当该第四开关导通时该第二电容充电。第五开关用来将该第一输出端耦接至一第一目标电压或一第二目标电压。第六开关用来将该第二输出端耦接至该第一目标电压或该第二目标电压。

7.相较于传统技术,本发明的放大电路具有更大的增益,或是更省电。

8.有关本发明的特征、实作与技术效果,兹配合附图作实施例详细说明如下。

附图说明

9.图1为现有电荷引导式放大器的电路图;

10.图2为本发明放大电路的一实施例的电路图;

11.图3为本发明放大电路的一操作实施例的时序图;

12.图4为本发明放大电路的另一操作实施例的时序图;以及

13.图5为本发明放大电路的另一操作实施例的时序图。

14.符号说明

15.100,201,202:电荷引导式放大器

16.110,120,210,220,230,240:晶体管

17.130,140,150,160,sw1,sw2,sw3,sw4,sw5,sw6:开关

18.170,180,190,c1,c2,c3,c4:电容

19.vi:差分输入信号

20.n1,n2,n3,n4,n5,n6:节点

21.vo:输出信号

22.200:放大电路(电荷引导式放大电路)

23.vip,vin:信号

24.vdd:电源电压

25.nr:中间位置

26.vr1:第一目标电压

27.vr2:第二目标电压

28.ck1,ck2,ck3,ck4:时钟

29.vn5,vn6:电压

30.t1,t2,t3,t4,t5:时间点

具体实施方式

31.以下说明内容的技术用语是参照本技术领域的习惯用语,如本说明书对部分用语有加以说明或定义,该部分用语的解释是以本说明书的说明或定义为准。

32.本发明的公开内容包含放大电路。由于本发明的放大电路所包含的部分元件单独而言可能为已知元件,因此在不影响该装置发明的充分公开及可实施性的前提下,以下说明对于已知元件的细节将予以省略。

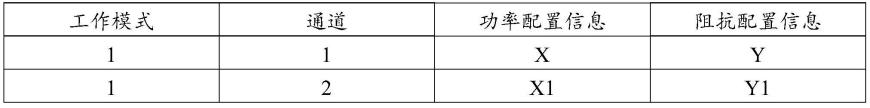

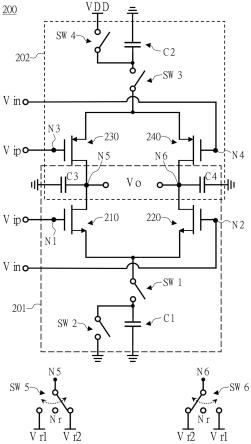

33.图2是本发明放大电路的一实施例的电路图。电荷引导式放大电路200(或简称为放大电路200)包含电荷引导式放大器201及电荷引导式放大器202。电荷引导式放大器201从输入端(即节点n1)及输入端(即节点n2)接收差分输入信号vi(包含信号vip及信号vin),并且从输出端(即节点n5)及输出端(即节点n6)输出输出信号vo。电荷引导式放大器202从输入端(即节点n3)及输入端(即节点n4)接收差分输入信号vi(包含信号vip及信号vin),并且从输出端(即节点n5)及输出端(即节点n6)输出输出信号vo。

34.电荷引导式放大器201包含晶体管210(例如n型金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect transistor,简称nmos晶体管))、晶体管220(例如nmos晶体管)、开关sw1、开关sw2、电容c1、电容c3及电容c4。晶体管210的第一端(例如漏极)耦接或电连接节点n5;晶体管210的第二端(例如源极)耦接或电连接开关sw1;晶体管210的控制端(例如栅极)耦接或电连接节点n1。晶体管220的第一端(例如漏极)耦接或电连接节点n6;晶体管220的第二端(例如源极)耦接或电连接开关sw1及晶体管210的第二端;晶体管220的控制端(例如栅极)耦接或电连接节点n2。开关sw1耦接于电容c1与晶体管210的第二端之间,且开关sw1亦耦接于电容c1与晶体管220的第二端之间。电容c1的第一端耦接或电连接开关sw1,电容c1的第二端耦接或电连接第一参考电压(例如接地)。开关sw2的一端耦接或电连接电容c1的第一端,开关sw2的另一端耦接或电连接第一参考电压。电容c3耦接或电连接于节点n5与第一参考电压之间。电容c4耦接或电连接于节点n6与第一参考电压之间。

35.电荷引导式放大器202包含晶体管230(例如p型金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect transistor,简称pmos晶体管))、晶体管240(例如pmos晶体管)、开关sw3、开关sw4、电容c2、电容c3及电容c4(其中,电容c3及电容c4与电荷引导式放大器201共用)。晶体管230的第一端(例如漏极)耦接或电连接节点n5;晶体管230的第二端(例如源极)耦接或电连接开关sw3;晶体管230的控制端(例如栅极)耦接或电连接节点n3。晶体管240的第一端(例如漏极)耦接或电连接节点n6;晶体管240的第二端(例如源极)耦接或电连接开关sw3及晶体管230的第二端;晶体管240的控制端(例如栅极)耦接或电连接节点n4。开关sw3耦接于电容c2与晶体管230的第二端之间,且开关sw3亦耦接于电容c2与晶体管240的第二端之间。电容c2的第一端耦接或电连接开关sw3,电容c2的第二端耦接或电连接第一参考电压。开关sw4的一端耦接或电连接电容c2的第一端,开关sw4的另一端耦接或电连接第二参考电压(例如电源电压vdd)。第二参考电压大于第一参考电压。

36.放大电路200还包含开关sw5及开关sw6。开关sw5及开关sw6可以导通(即,切换到第一目标电压vr1或第二目标电压vr2)或是不导通(即,切换到中间位置nr)。当开关sw5及开关sw6导通时,开关sw5及开关sw6分别将节点n5及节点n6耦接或电连接第一目标电压vr1或第二目标电压vr2。

37.在一些实施例中,第一目标电压vr1为第二参考电压(例如电源电压vdd)或第二参考电压的一半(例如电源电压vdd的1/2),且第二目标电压vr2为第一参考电压(例如接地)或第二参考电压的一半(例如电源电压vdd的1/2)。换句话说,当节点n5及节点n6耦接或电连接第一目标电压vr1时,电容c3及电容c4的跨压实质上为第二参考电压或第二参考电压的一半;当节点n5及节点n6耦接或电连接第二目标电压vr2时,电容c3及电容c4的跨压实质上为零或第二参考电压的一半。

38.在一些实施例中,开关sw1、开关sw2、开关sw3、开关sw4、开关sw5及开关sw6可以用晶体管实作。

39.图3为本发明放大电路的一操作实施例的时序图,可一并参考图2。在以下的讨论中,开关sw3根据时钟ck1切换(即,导通或不导通):当时钟ck1为第一准位(例如高准位)时,开关sw3不导通;当时钟ck1为第二准位(不等于第一准位,例如低准位)时,开关sw3导通。开关sw1根据时钟ck2切换:当时钟ck2为第一准位时,开关sw1导通;当时钟ck2为第二准位时,开关sw1不导通。电压vn5代表节点n5上的电压,而电压vn6代表节点n6上的电压。

40.当时钟ck3为第一准位时(例如时间点t1与时间点t3之间),放大电路200操作于放大阶段;当时钟ck3为第二准位时(例如时间点t3与时间点t4之间),放大电路200操作于重置阶段。

41.在图3的实施例中,开关sw5及开关sw6导通时将节点n5及节点n6耦接或电连接至第二目标电压vr2,并且开关sw2、开关sw4、开关sw5及开关sw6根据时钟ck3切换:当时钟ck3为第一准位时,开关sw2、开关sw4、开关sw5及开关sw6不导通;当时钟ck3为第二准位时,开关sw2、开关sw4、开关sw5及开关sw6导通。

42.如图3所示,在时间点t1时,时钟ck3从第二准位转换到第一准位(代表重置阶段结束且放大阶段开始),电压vn5及电压vn6为第二目标电压vr2。时钟ck2于时间点t2从第二准位转换到第一准位。放大阶段包含第一操作时段(当时钟ck1为第二准位时)及第二操作时段(当时钟ck2为第一准位时)。第一操作时段实质上等于或略小于从时间点t1到时间点t2的时间,换言之,时钟ck1从第一准位转换到第二准位的时间点可以实质上等于或略晚于时间点t1,而时钟ck1从第二准位转换到第一准位的时间点可以实质上等于或略早于时间点t2。第二操作时段实质上等于或略小于从时间点t2到时间点t3的时间,换言之,时钟ck2从第二准位转换到第一准位的时间点实质上等于时间点t2,而时钟ck2从第一准位转换到第二准位的时间点可以实质上等于或略晚于时间点t3。在时间点t3,时钟ck3从第一准位转换到第二准位(代表放大阶段结束且重置阶段开始)。

43.请一并参考图2及图3。在第一操作时段期间,开关sw3导通且开关sw1不导通,所以晶体管230及晶体管240作用(active)且晶体管210及晶体管220不作用(inactive),使得电容c3与电容c4充电。在第一操作时段期间,晶体管230及晶体管240放大差分输入信号vi,因此电压vn5(例如虚线)及电压vn6(例如实线)之间的差渐渐变大。在第二操作时段期间,开关sw1导通且开关sw3不导通,所以晶体管210及晶体管220作用且晶体管230及晶体管240不作用,使得电容c3与电容c4放电。在第二操作时段期间,晶体管210及晶体管220以时间点t2的电压vn5及电压vn6为基础继续放大差分输入信号vi(与第一操作时段的差分输入信号vi相同),因此可以看到电压vn5及电压vn6之间的差继续变大。换言之,电压vn5及电压vn6之间在时间点t3的差大于电压vn5及电压vn6之间在时间点t2的差。由此可见,经过第二次放

大,电压vn5及电压vn6之间的差变得更大,有利于后级电路(例如比较器)的操作。作为比较,因为现有的电荷引导式放大器100只对差分输入信号做一次放大,所以电荷引导式放大器100针对相同的差分输入信号vi所产生的输出信号vo实施方式至多对应于时间点t2的输出信号vo。也就是说,本公开的放大电路200的增益大于电荷引导式放大器100的增益。

44.请注意,由于差分输入信号vi在时间点t1及时间点t3之间保持不变,即,维持在前一个重置阶段的取样结果(由取样及保持电路(图未示)产生),所以晶体管210、晶体管220、晶体管230及晶体管240在同一个放大阶段(例如时间点t1与时间点t3之间)实质上根据同一个差分输入信号vi进行放大操作。时间点t4与时间点t5之间的差分输入信号vi是时间点t3与时间点t4之间的取样操作的结果。

45.图4为本发明放大电路的另一操作实施例的时序图。图4与图3相似,差别在于在每次的放大阶段中,第二操作时段早于第一操作时段,而且在每次的重置阶段中,开关sw5及开关sw6将节点n5及节点n6耦接或电连接至第一目标电压vr1,而非第二目标电压vr2。因此,电压vn5及电压vn6于放大阶段中先变小(即,电容c3与电容c4放电,例如时间点t1与时间点t2之间)再变大(即,电容c3与电容c4充电,例如时间点t2与时间点t3之间)。与图3的实施例相似,在每个放大阶段差分输入信号vi经过二次放大,使得电压vn5及电压vn6之间的差变得更大,有利于后级电路(例如比较器)的操作。

46.图5为本发明放大电路的另一操作实施例的时序图。在图5的实施例中,开关sw2及开关sw4根据时钟ck3切换:当时钟ck3为第一准位时,开关sw2及开关sw4不导通;当时钟ck3为第二准位时,开关sw2及开关sw4导通。开关sw5及开关sw6根据时钟ck4切换。当时钟ck4为第二准位时(例如时间点t1与时间点t2之间或时间点t3与时间点t4之间),放大电路200操作于放大阶段;当时钟ck4为第一准位时(例如时间点t2与时间点t3之间或时间点t4与时间点t5之间),放大电路200操作于重置阶段。类似地,图5的实施例也包含第一操作时段(当时钟ck1为第一准位时)及第二操作时段(当时钟ck2为第二准位时)。如图5所示,在本实施例中,第一操作时段(对应于第一放大操作)及第二操作时段(对应于第二放大操作)之间间隔重置阶段;换言之,在第一操作时段开始前及在第二操作时段开始前,放大电路200的输出端(即,节点n5与节点n6)上的电压(即电压vn5及电压vn6)会重置,也就是电容c3及电容c4的端电压会重置。

47.如图5所示,时钟ck4在时间点t1及时间点t3从第一准位转换到第二准位,且时钟ck4在时间点t2及时间点t4从第二准位转换到第一准位。

48.第一操作时段实质上等于或略小于从时间点t1到时间点t2的时间,换言之,时钟ck1从第二准位转换到第一准位的时间点可以实质上等于或略晚于时间点t1,而时钟ck1从第一准位转换到第二准位的时间点可以实质上等于或略早于时间点t2。第二操作时段实质上等于或略小于从时间点t3到时间t4的时间,换言之,时钟ck2从第一准位转换到第二准位的时间点实质上等于或略晚于时间点t3,而时钟ck2从第二准位转换到第一准位的时间点可以实质上等于或略早于时间点t4。

49.请参考图2及图5。在第一操作时段(例如时间点t1与时间点t2之间的第一操作时段)期间,开关sw1导通且开关sw3不导通(即,晶体管210及晶体管220作用且晶体管230及晶体管240不作用,电容c3及电容c4放电),晶体管210及晶体管220放大差分输入信号vi,因此电压vn5及电压vn6的差值变大。在第一操作时段后的重置阶段(例如时间点t2与时间点t3

之间),开关sw5及开关sw6将节点n5及节点n6耦接或电连接至第二目标电压vr2。在紧接着的第二操作时段(例如时间点t3与时间点t4之间的第二操作时段)期间,开关sw1不导通且开关sw3导通(即,晶体管210及晶体管220不作用且晶体管230及晶体管240作用,电容c3及电容c4充电),晶体管230及晶体管240放大差分输入信号vi,因此电压vn5及电压vn6的差值变大。在第二操作时段后的重置阶段(例如时间点t4与时间点t5之间),开关sw5及开关sw6将节点n5及节点n6耦接或电连接至第一目标电压vr1。

50.需注意的是,因为取样及保持电路在重置阶段取样,所以在图5的实施例中,放大电路200在第一操作时段及第二操作时段放大不同的差分输入信号vi(即,放大不同次取样的结果,而非同一次取样的结果)。

51.如图5所示,从时间点t1到时间点t5,电容c3及电容c4只被充电一次(约介于时间点t3到时间点t5之间),放大电路200却产生两个放大结果(长时间来看,放大电路200于第一操作时段产生第奇数个放大结果,于第二操作时段产生第偶数个放大结果)。因此,放大电路200相较于现有的电荷引导式放大器100更省电。

52.上述的晶体管也可以用双极性接面型晶体管(bipolar junction transistor,bjt)实作。bjt的射极(emitter)、集极(collector)及基极(base)可以分别对应于mosfet的源极、漏极及栅极,此为本技术领域技术人员所熟知,故不再赘述。

53.请注意,前述附图中,元件的形状、尺寸及比例仅为示意,是供本技术领域技术人员了解本发明之用,非用以限制本发明。

54.虽然本发明的实施例如上所述,然而该些实施例并非用来限定本发明,本技术领域技术人员可依据本发明的明示或隐含的内容对本发明的技术特征施以变化,凡此种种变化均可能属于本发明所寻求的专利保护范围,换言之,本发明的专利保护范围须视本说明书的权利要求所界定者为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。