1.本公开大体上涉及集成电路和集成电路操作,并且确切地说,在一或多个实施例中,本公开涉及电压调节系统、含有电压调节系统的设备以及其在通电期间的操作的方法。

背景技术:

2.集成电路装置横跨广泛范围的电子装置。一种特定类型包含存储器装置,时常简称为存储器。存储器装置通常提供为计算机或其它电子装置中的内部半导体集成电路装置。存在许多不同类型的存储器,包含随机存取存储器(ram)、只读存储器(rom)、动态随机存取存储器(dram)、同步动态随机存取存储器(sdram)和快闪存储器。

3.快闪存储器已发展成用于广泛范围的电子应用的受欢迎的非易失性存储器源。快闪存储器通常使用允许高存储器密度、高可靠性和低功耗的单晶体管存储器单元。通过对电荷存储结构(例如,浮动栅极或电荷陷阱)或其它物理现象(例如,相变或偏振)进行编程,存储器单元的阈值电压(vt)改变决定每一存储器单元的数据状态(例如,数据值)。快闪存储器和其它非易失性存储器的常见用途包含个人计算机、个人数字助理(pda)、数字相机、数字媒体播放器、数字记录器、游戏、电气设备、车辆、无线装置、移动电话和可拆卸式存储器模块,且非易失性存储器的用途在持续扩大。

4.nand快闪存储器是常用类型的快闪存储器装置,如此称谓的原因在于布置基本存储器单元配置的逻辑形式。通常,用于nand快闪存储器的存储器单元阵列被布置成使得阵列中的一行中的每一存储器单元的控制栅极连接在一起以形成存取线,例如字线。阵列中的列包含在一对选择栅极之间(例如,在源极选择晶体管与漏极选择晶体管之间)串联连接在一起的存储器单元串(通常被称为nand串)。每一源极选择晶体管可连接到源极,而每一漏极选择晶体管可连接到数据线,例如列位线。在存储器单元串与源极之间和/或在存储器单元串与数据线之间使用多于一个选择栅极的变型是已知的。

5.电子系统通常使用多个nand装置以实现较大存储能力。由于对电源电流能力的限制,通常必需依序为这些nand装置通电。在nand装置通电时,所述nand装置可产生大电流尖峰。由于为多个nand装置通电的依序性质,共享电源的控制器和其它电路可能已完全可操作,并且大电流尖峰可能不利地影响此类控制器和其它电路的性能或操作。

技术实现要素:

6.描述一种电压调节系统。电压调节系统可包含:电压调节器,其包括输入、输出和在其输入与其输出之间的选择性激活的第一电流路径;以及电压跟踪器,其包括连接到电压调节器的输入的第一输入、被配置成接收控制信号的第二输入、连接到电压调节器的输出的输出,以及连接在电压调节器的输入与电压调节器的输出之间的选择性激活的第二电流路径。电压跟踪器被配置成在控制信号具有第一逻辑电平时响应于电压调节器的输入的电压电平而允许第二电流路径激活。电压跟踪器被配置成在控制信号具有不同于第一逻辑电平的第二逻辑电平时响应于电压调节器的输入的电压电平而禁止第二电流路径激活。

7.描述一种存储器。存储器可包含:电压调节器,其包括输入和输出;选择性激活的第一电流路径,其连接在电压调节器的输入与电压调节器的输出之间;选择性激活的第二电流路径,其连接在电压调节器的输入与电压调节器的输出之间;存储器单元阵列,其连接到电压调节器的输出;以及控制器,其连接到电压调节器的输出。控制器被配置成致使存储器:在电压调节器的输入的电压电平具有第一电压电平时,通过第一电流路径将电压调节器的输出连接到电压调节器的输入;在电压调节器的输入的电压电平具有高于第一电压电平的第二电压电平时,通过第二电流路径将电压调节器的输出连接到电压调节器的输入;维持电压调节器的输出通过电流路径到电压调节器的输入的连接,直到电压调节器的输入的电压电平具有高于第二电压电平的第三电压电平为止;维持电压调节器的输出通过第二电流路径到电压调节器的输入的连接,直到电压调节器的输入的电压电平具有第三电压电平为止;在电压调节器的输入的电压电平具有第三电压电平之后,通过第一电流路径且通过第二电流路径将电压调节器的输出与电压调节器的输入隔离;以及在电压调节器的输出通过第一电流路径且通过第二电流与电压调节器的输入隔离时,调节电压调节器的输出的电压电平。

8.描述一种集成电路装置。集成电路装置可包含:电压调节器,其包括输入和输出;选择性激活的电流路径,其连接在电压调节器的输入与电压调节器的输出之间;以及控制器。控制器被配置成致使集成电路装置:在电压调节器的输入的电压电平具有第一电压电平时,通过电流路径将电压调节器的输出连接到电压调节器的输入;维持电压调节器的输出通过电流路径到电压调节器的输入的连接,直到电压调节器的输入的电压电平具有高于第一电压电平的第二电压电平为止;在电压调节器的输入的电压电平具有第二电压电平之后,通过电流路径将电压调节器的输出与电压调节器的输入隔离;以及在电压调节器的输出通过电流路径与电压调节器的输入隔离时,调节电压调节器的输出的电压电平。

9.描述一种操作集成电路装置的方法。方法可包含:在电压调节器的输入的电压电平具有第一电压电平时,通过电流路径将电压调节器的输出连接到电压调节器的输入;维持电压调节器的输出通过电流路径到电压调节器的输入的连接,直到电压调节器的输入的电压电平具有高于第一电压电平的第二电压电平为止;在电压调节器的输入的电压电平具有第二电压电平之后,通过电流路径将电压调节器的输出与电压调节器的输入隔离;以及在电压调节器的输出通过电流路径与电压调节器的输入隔离时,调节电压调节器的输出的电压电平。

附图说明

10.图1是根据实施例的作为电子系统的部分与处理器通信的存储器的简化框图。

11.图2是根据另一实施例的作为电子系统的部分与主机通信的存储器模块的简化框图。

12.图3是相关技术的电压调节系统的示意框图。

13.图4是相关技术的电压调节器的示意图。

14.图5是相关技术的电压调节的时序图。

15.图6是根据实施例的电压调节系统的示意框图。

16.图7是根据实施例的电压跟踪器的示意图。

17.图8是根据实施例的电压调节的时序图。

18.图9是根据实施例的操作集成电路装置的方法的流程图。

19.图10是根据另一实施例的操作集成电路装置的方法的流程图。

具体实施方式

20.在以下详细描述中,参考附图,所述附图形成详细描述的部分,且在其中借助于说明展示具体实施例。在图式中,在若干视图中相同的参考标号始终描述大体上类似的组件。在不脱离本公开的范围的情况下可利用其它实施例,且可做出结构、逻辑和电改变。因此,不应按限制性意义来看待以下详细描述。

21.除非另外从上下文显而易见,否则如本文中所使用的术语“导电(conductive)”以及其各种相关形式(例如,传导(conduct)、以导电方式(conductively)、传导(conducting)、传导(conduction)、导电性(conductivity)等)是指电学上的导电。类似地,除非另外从上下文显而易见,否则如本文中所使用的术语“连接(connecting)”以及其各种相关形式(例如,connect、connected、connection等)是指通过导电路径的电连接。

22.如本文中所使用,多个动作同时执行将意味着在相应的时间段上执行这些动作中的每一个,并且这些相应的时间段中的每一个与其余的相应的时间段中的每一个部分或完全重叠。换句话说,在至少某一时间段上同时执行那些动作中的每一个的部分。

23.在本文中认识到,即使在值可能预期相等的情况下,工业加工和操作的可变性和精确度仍可能会导致与其预期值的差异。这些可变性和精确度将通常取决于在集成电路装置的制造和操作中利用的技术。因而,如果值预期相等,则认为那些值相等而不考虑其所得值。

24.图1是根据实施例的呈存储器(例如,存储器装置)100形式的第一设备的简化框图,所述第一设备作为呈电子系统形式的第三设备的部分与呈处理器130形式的第二设备通信。电子系统的一些实例包含个人计算机、个人数字助理(pda)、数字相机、数字媒体播放器、数字记录器、游戏、电气设备、车辆、无线装置、移动电话等。处理器130,例如,存储器装置100外部的控制器,可为存储器控制器或另一外部主机装置。

25.存储器装置100包含可逻辑上布置成行和列的存储器单元阵列104。逻辑行中的存储器单元通常连接到同一存取线(统称为字线),而逻辑列中的存储器单元通常选择性地连接到同一数据线(统称为位线)。单个存取线可与存储器单元的多于一个逻辑行相关联且单个数据线可与多于一个逻辑列相关联。存储器单元阵列104的至少部分的存储器单元(图1中未展示)能够经编程为至少两个目标数据状态中的一个。

26.提供行解码电路系统108和列解码电路系统110以对地址信号进行解码。接收地址信号并对其进行解码以存取存储器单元阵列104。存储器装置100还包含输入/输出(i/o)控制电路系统112,其用以管理命令、地址和数据到存储器装置100的输入以及数据和状态信息从存储器装置100的输出。地址寄存器114与i/o控制电路系统112和行解码电路系统108以及列解码电路系统110通信以在解码之前锁存地址信号。命令寄存器124与i/o控制电路系统112和控制逻辑116通信以锁存传入命令。

27.控制器(例如,在存储器装置100内部的控制逻辑116)响应于命令而控制对存储器单元阵列104的存取,并且可产生外部处理器130的状态信息,即,控制逻辑116被配置成对

存储器单元阵列104执行存取操作(例如,感测操作[其可包含读取操作和校验操作]、编程操作和/或擦除操作)。控制逻辑116与行解码电路系统108和列解码电路系统110通信以响应于地址而控制行解码电路系统108和列解码电路系统110。控制逻辑116可包含指令寄存器128,其可表示用于存储计算机可读指令的计算机可用存储器。对于一些实施例,指令寄存器128可表示固件。替代地,指令寄存器128可表示存储器单元阵列104中的存储器单元的分组,例如,预留的存储器单元块。

[0028]

控制逻辑116还可与高速缓存寄存器118通信。高速缓存寄存器118锁存如由控制逻辑116引导的传入或传出数据,以分别在存储器单元阵列104忙碌地写入或读取其它数据时暂时存储数据。在编程操作(例如,写入操作)期间,数据可从高速缓存寄存器118传送到数据寄存器120以用于传递到存储器单元阵列104;接着可从i/o控制电路系统112将新数据锁存在高速缓存寄存器118中。在读取操作期间,可将数据从高速缓存寄存器118传送到i/o控制电路系统112以用于输出到外部处理器130;接着可将新数据从数据寄存器120传送到高速缓存寄存器118。高速缓存寄存器118和/或数据寄存器120可形成存储器装置100的页缓冲器(例如,可形成其部分)。页缓冲器可进一步包含感测装置(图1中未展示)以例如通过感测连接到存储器单元阵列104的存储器单元的数据线的状态来感测所述存储器单元的数据状态。状态寄存器122可与i/o控制电路系统112和控制逻辑116通信以锁存状态信息以用于输出到处理器130。

[0029]

存储器装置100在控制逻辑116处经由控制链路132从处理器130接收控制信号。控制信号可包含芯片启用ce#、命令锁存启用cle、地址锁存启用ale、写入启用we#、读取启用re#和写入保护wp#。取决于存储器装置100的性质,可进一步经由控制链路132接收额外或替代控制信号(未展示)。存储器装置100经由多路复用的输入/输出(i/o)总线134从处理器130接收命令信号(其表示命令)、地址信号(其表示地址)和数据信号(其表示数据)且经由i/o总线134将数据输出到处理器130。

[0030]

举例来说,可经由输入/输出(i/o)总线134的i/o引脚[7:0]在i/o控制电路系统112处接收命令,并且可接着将所述命令写入到命令寄存器124中。可经由输入/输出(i/o)总线134的i/o引脚[7:0]在i/o控制电路系统112处接收地址,并且可接着将所述地址写入到地址寄存器114中。可经由用于8位装置的输入/输出(i/o)引脚[7:0]或用于16位装置的输入/输出(i/o)引脚[15:0]在i/o控制电路系统112处接收数据,并且接着可将所述数据写入到高速缓存寄存器118中。可随后将数据写入到数据寄存器120中以用于对存储器单元阵列104进行编程。对于另一实施例,可省略高速缓存寄存器118,并且可将数据直接写入到数据寄存器120中。还可经由用于8位装置的输入/输出(i/o)引脚[7:0]或用于16位装置的输入/输出(i/o)引脚[15:0]输出数据。虽然可参考i/o引脚,但它们可包含通过外部装置(例如,处理器130)实现到存储器装置100的电连接的任何导电节点,例如常用的导电衬垫或导电凸块。

[0031]

存储器装置100和/或处理器130可从电源136接收电力。电源136可表示用于将电力提供到存储器装置100和/或处理器130的电路系统的任何组合。举例来说,电源136可包含单独电源(例如,电池)、线连接的电源(例如,台式计算机和服务器中常见的开关模式电源或对便携式电子装置常见的ac适配器)或两种的组合。通常使用两个或更多个电压供应节点137从电源136接收电力,所述电压供应节点例如供应电压节点(例如,vcc或vccq)和参

考电位节点(例如,vss或vssq,例如接地或0v)。提供多于两个电压供应节点137对电源136来说不常见。为简单起见,未描绘从电压供应节点137到存储器装置100内的组件的电力分布。

[0032]

所属领域的技术人员应了解,可提供额外的电路系统和信号,并且已简化图1的存储器装置100。应认识到,参考图1描述的各种块组件的功能性可能不必分离到集成电路装置的不同组件或组件部分。举例来说,集成电路装置的单个组件或组件部分可适于执行图1的多于一个块组件的功能性。替代地,可组合集成电路装置的一或多个组件或组件部分,以执行图1的单个块组件的功能性。

[0033]

另外,虽然根据各种信号的接收和输出的流行惯例描述了具体i/o引脚,但应注意,可在各种实施例中使用其它组合或其它数目的i/o引脚(或其它i/o节点结构)。

[0034]

给定处理器130可与一或多个存储器装置100(例如,裸片)通信。图2是根据另一实施例的作为电子系统的部分呈与主机240通信的存储器模块201的形式的设备的简化框图。存储器装置100和处理器130可如参考图1所描述。虽然存储器模块(例如,存储器封装)201描绘为具有四个存储器装置100(例如,裸片),但存储器模块201可具有更少或更多存储器装置100。如本文中所使用,裸片是指个别集成电路装置,其可包含存储器装置100,并且可包含其它集成电路装置。

[0035]

因为处理器130(例如,存储器控制器)在主机240与存储器装置100之间,所以主机240与处理器130之间的通信可涉及与处理器130与存储器装置100之间使用的通信链路不同的通信链路。举例来说,存储器模块201可为固态驱动器(ssd)的嵌入式多媒体存储卡(emmc)。根据现有标准,与emmc的通信可包含用于数据传递的数据链路242(例如,8位链路)、用于命令传递和装置初始化的命令链路244,以及提供用于使数据链路242和命令链路244上的传递同步的时钟信号的时钟链路246。处理器130可自主地处置许多活动,例如错误校正、有缺陷块的管理、耗损均衡和地址翻译。

[0036]

图3是相关技术的电压调节系统300的示意框图。电压调节系统300可为集成电路装置(例如,存储器装置)的组件。电压调节系统300可通过第一电压供应节点1370,例如对应于上部电力轨的供应电压节点(例如,vcc_ext)且通过第二电压供应节点1371,例如对应于下部电力轨的参考电位节点(例如,vss,例如接地或0v)连接到电源136。电压调节系统300可包含连接在上部电力轨与下部电力轨之间的参考电压产生器,例如,带隙电压产生器350,并且可在输出处产生参考电压,例如,带隙参考电压vbgr。带隙电压产生器在所属领域中通常被很好地理解成用于产生通常独立于电源变化、温度改变和电路负载的参考电压,只要供应电压具有足够电压电平以完全产生带隙电压产生器的输出的电压电平即可。带隙参考电压vbgr可提供到电压调节器352的第一输入。电压调节器352的第二输入可连接到第一电压供应节点1370。电压调节器352还可连接到第二电压供应节点1371作为下部电力轨。如下文将更详细地描述,电压调节器可响应于外部供应电压vcc_ext和带隙参考电压vbgr而在其输出处产生内部供应电压vccr。内部供应电压vccr可提供到负载354作为经调节上部电力轨。负载354还可连接到第二电压供应节点1371作为下部电力轨。负载354可表示使用来自电压调节器352的内部供应电压vccr的集成电路装置的电路系统的任何组合。举例来说,负载354可包含存储器100的存储器单元阵列104以及控制器(例如,控制逻辑116)和存储器100的其它组件。电压调节系统300可进一步包含连接在内部供应电压vccr与第二电

压供应节点1371之间的去耦电容器356。通常在电力轨之间使用去耦电容器以缓解电压尖峰。

[0037]

图4是如可与电压调节系统300一起使用的电压调节器352的示意图。一般来说,电压调节器可包含被配置成调节输出电压电平,例如,输出462处的内部供应电压vccr的任何电路,所述输出电压电平低于其输入电压电平(例如,从其下调),例如,在输入460处接收到的电压vcc_ext。输入460可连接到第一供应电压节点1370。内部供应电压vccr的电压电平可响应于在输入464处接收到的参考电压,例如,带隙参考电压vbgr。

[0038]

图4中所描绘的电压调节器352可表示线性电压调节器。电压调节器352可包含运算放大器(op-amp)466,所述运算放大器具有经连接以接收带隙参考电压vbgr的第一输入(例如,反相输入)。运算放大器466可具有经连接以接收分压器470的输出468,例如,反馈电压的第二输入(例如,非反相输入)。如本文中所使用,运算放大器(operational amplifier或op-amp)将指被配置成响应于信号差分而调整(例如,增加或减少)其输出电压电平且在所述信号接近相等时停止调整其输出电压电平的任何电路。

[0039]

分压器470可连接在电压调节器352的输出462与电压节点472之间。电压节点472可表示参考电位,例如vss、接地或0v,并且可连接到第二供应电压节点1371。分压器470在概念上描绘为具有其在顶部电阻rtop与底部电阻rbot之间的输出468。分压器470可为可调整分压器以更改rtop/(rtop rbot)的电阻比率。举例来说,分压器470可用于调整电压调节器352的增益。分压器470的输出468的电压电平可为用于运算放大器466的反馈电压。

[0040]

运算放大器466可具有连接到晶体管(例如,p型场效应晶体管或pfet)476的控制栅极的其输出474。pfet 476可具有连接到输入460以接收外部供应电压vcc_ext的第一源极/漏极(例如,源极),并且可具有连接到输出462的第二源极/漏极(例如,漏极)。pfet 476可充当电阻器,并且可促进将电压调节器352的输出462维持在目标电压电平。

[0041]

图5是相关技术的电压调节的时序图。参考图5,迹线580可表示外部供应电压vcc_ext的电压电平,例如,在电压调节器352的输入460处接收到的电压电平。迹线582可表示内部供应电压vccr的电压电平,例如,电压调节器352的输出462的电压电平。时间t0可表示集成电路装置的通电的起始,例如通过开始使提供到集成电路装置的外部供应电压vcc_ext的电压电平斜升。在时间t0处,外部供应电压vcc_ext可开始从初始电压电平,例如,vss、接地或0v斜升。内部供应电压vccr可保持在初始电压电平,因为pfet 476的源极电压(例如,vcc_ext)与栅极电压(例如,vss)之间的差可保持低于其阈值电压,对于典型pfet,所述阈值电压可为1v。

[0042]

在时间t1处,外部供应电压vcc_ext可达到足以激活pfet 476的电平,例如,约1v,从而导致内部供应电压vccr的电压电平的快速增加。此类快速转变可导致电源的电流需求的尖峰。如所提及,此类电流尖峰可对依赖于同一电源的其它装置的性能或操作不利。内部供应电压vccr的电压电平可继续遵循迹线580的电压电平直到时间t2为止,此时分压器470的输出468处的电压电平可达到其高于在电压调节器352的输入464处发展的带隙参考电压vbgr的电压电平的点。此时,运算放大器466可转变且开始将外部供应电压vcc_ext施加到pfet 476的控制栅极,因此暂停内部供应电压vccr的电压电平的发展。

[0043]

在时间t3处,带隙参考电压vbgr的电压电平可充分发展以变得高于分压器470的输出468处的电压电平。因此,内部供应电压vccr的电压电平可经历电压电平的另一快速

(尽管较小)增加,这可再次导致来自电源的电流需求的尖峰。此时,电压调节器352可变得完全起作用且开始主动调节内部供应电压vccr的电压电平。在时间t4处,外部供应电压vcc_ext可达到稳态值,并且在时间t5处,内部供应电压vccr的电压电平可达到稳态值,例如,电压调节器352的目标电压电平。

[0044]

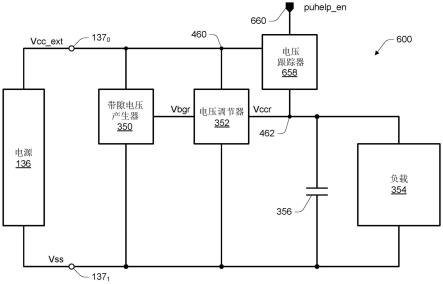

图6是根据实施例的电压调节系统600的示意框图。电压调节系统600可为集成电路装置(例如,存储器装置)的组件。电压调节系统600可通过第一电压供应节点1370,例如对应于上部电力轨的供应电压节点(例如,vcc_ext)且通过第二电压供应节点1371,例如对应于下部电力轨的参考电位节点(例如,vss,例如接地或0v)连接到电源136。电压调节系统600可包含连接在上部电力轨与下部电力轨之间的参考电压产生器,例如,带隙电压产生器350,并且可在输出处产生参考电压,例如,带隙参考电压vbgr。带隙电压产生器在所属领域中通常被很好地理解成用于产生通常独立于电源变化、温度改变和电路负载的参考电压,只要供应电压具有足够电压电平以完全产生带隙电压产生器的输出的电压电平即可。带隙参考电压vbgr可提供到电压调节器352的第一输入。电压调节器352的第二输入可连接到第一电压供应节点1370。电压调节器352还可连接到第二电压供应节点1371作为下部电力轨。如上文已描述,电压调节器可响应于外部供应电压vcc_ext和带隙参考电压vbgr而在其输出处产生内部供应电压vccr。内部供应电压vccr可提供到负载354作为经调节上部电力轨。负载354还可连接到第二电压供应节点1371作为下部电力轨。负载354可表示使用来自电压调节器352的内部供应电压vccr的集成电路装置的电路系统的任何组合。电压调节系统600可进一步包含连接在内部供应电压vccr与第二电压供应节点1371之间的去耦电容器356。通常在电力轨之间使用去耦电容器以缓解电压尖峰。

[0045]

与电压调节系统300相比,电压调节系统600进一步包含电压跟踪器658,所述电压跟踪器具有连接到电压调节器352的输入460的输入,并且具有连接到电压调节器352的输出462的输出。虽然电压调节系统600被描绘为利用与电压调节系统300相同的带隙电压产生器350,但被配置成产生参考电压电平的任何电路系统将适合于与实施例一起使用。类似地,虽然电压调节系统600被描绘为利用与电压调节系统300相同的电压调节器352,但任何电路系统被配置成调节输出电压电平,例如,输出462处的内部供应电压vccr,所述输出电压电平低于其输入电压电平(例如,从其下调),例如,在输入460处接收到的电压vcc_ext。电压跟踪器658进一步包含被配置成接收控制信号puhelp_en的第二输入660。

[0046]

一般来说,电压跟踪器658可被配置成选择性地将电压调节器352的输入460短接(例如,连接)到其输出462。这可准许内部供应电压vccr的电压电平在电压调节器具有足够供应电压电平以主动地调节其输出之前跟踪外部供应电压vcc_ext的电压电平。

[0047]

图7是根据实施例的电压跟踪器658的示意图。电压跟踪器658具有连接在输入460与输出462之间的晶体管(例如,n型场效应晶体管或nfet)690,所述输入和所述输出可分别进一步表示电压跟踪器658的输入和输出。nfet 690可具有负阈值电压以促进紧密跟踪在连接到输入460的第一源极/漏极(例如,漏极)处接收到的外部供应电压vcc_ext,以及在连接到输出462的第二源极漏极(例如,源极)处的所得内部供应电压vccr。虽然可使用正阈值电压nfet,但负阈值电压nfet可促进对外部供应电压vcc_ext的更紧密跟踪。

[0048]

耦合电容器692可具有连接到nfet 690的控制栅极的一个电极和连接到输入460的另一电极。以此方式,外部供应电压vcc_ext可耦合(例如,电容耦合)到nfet 690的控制

栅极。通过负阈值电压,此耦合可将nfet 690维持在激活条件中,而控制栅极以其它方式浮动,因为nfet 690的控制栅极处的电压电平(例如,接近外部供应电压vcc_ext的电压电平)可保持接近且可甚至超过其源极的电压电平(例如,内部供应电压vccr的电压电平)。

[0049]

电压跟踪器658可进一步包含例如通过pfet 696连接在输入460与电压节点698之间的nfet 694,所述电压节点可被配置成接收参考电位,例如,vss、接地或0v。pfet 696的第一源极/漏极(例如,源极)可连接到输入460,并且pfet 696的第二源极/漏极(例如,漏极)可连接到nfet 694的第一源极/漏极(例如,漏极)。nfet 694的第二源极/漏极(例如,源极)可连接到电压节点698。nfet 694可响应于在输入660处接收到的控制信号puhelp_en。如所描绘,输入660连接到第一反相器700的输入。第一反相器700的输出连接到第二反相器702的输入,并且第二反相器702的输出连接到nfet 694的控制栅极。撤销激活nfet 694可响应于外部供应电压vcc_ext的电压电平而允许nfet690激活,而激活nfet 694可响应于外部供应电压vcc_ext的电压电平而禁止nfet 690激活。

[0050]

电压跟踪器658可进一步包含pfet 704,所述pfet具有连接到输入460的第一源极/漏极(例如,源极)和连接到输出462的第二源极/漏极(例如,漏极)。虽然nfet 690可促进在外部供应电压vcc_ext上升到足以操作pfet 704的电平之前紧密跟踪输出462处的外部供应电压vcc_ext,但pfet 704可促进在外部供应电压vcc_ext上升到足以操作pfet 704的电平之后改进跟踪外部供应电压vcc_ext。

[0051]

电压跟踪器658可进一步包含例如通过pfet 708连接在输入460与电压节点698之间的nfet 706。pfet 708的第一源极/漏极(例如,源极)可连接到输入460,并且pfet 708的第二源极/漏极(例如,漏极)可连接到nfet 706的第一源极/漏极(例如,漏极)。nfet 706的第二源极/漏极(例如,源极)可连接到电压节点698。nfet 706可响应于控制信号puhelp_en。如所描绘,控制信号puhelp_en通过输入660连接到第一反相器700的输入,并且第一反相器700的输出连接到nfet 706的控制栅极。激活nfet 706可响应于外部供应电压vcc_ext的电压电平而允许pfet 704激活,而在激活pfet 708时撤销激活nfet 706可响应于外部供应电压vcc_ext的电压电平而禁止pfet 704激活。

[0052]

电压跟踪器658可进一步包含耦合电容器710。耦合电容器710可具有连接到第二反相器702的输入的一个电极和连接到输入460的另一电极。以此方式,外部供应电压vcc_ext可耦合(例如,电容耦合)到第二反相器702的输入以促进在外部供应电压vcc_ext上升到足以可靠地操作第一反相器700的电平之前将其输出维持在逻辑低电平,否则所述第一反相器将驱动第二反相器702的输入。

[0053]

图8是根据实施例的电压调节的时序图。将参考图7的电压跟踪器658描述图8的时序图。参看图8,迹线880可表示外部供应电压vcc_ext的电压电平,例如,在电压调节器352和电压跟踪器658的输入460处接收到的电压电平。迹线882可表示内部供应电压vccr的电压电平,例如,电压调节器352和电压跟踪器658的输出462的电压电平。迹线884可表示到nfet 690的控制栅极的控制栅极电压vg的电压电平。时间t0可表示集成电路装置的通电的起始,例如通过开始使外部供应电压vcc_ext的电压电平斜升。

[0054]

在时间t0处,外部供应电压vcc_ext可开始从初始电压电平,例如,vss、接地或0v斜升。与相关技术的电压调节相比,内部供应电压vccr还可开始从初始电压电平斜升。内部供应电压vccr的增加的速率可滞后于外部供应电压的增加的速率。具体地说,在时间t0处,

控制信号puhelp_en可在参考电位,例如,逻辑低电平。可撤销激活pfet 696和nfet 694。因此,由于耦合电容器692,控制栅极电压vg的电压电平可遵循外部供应电压vcc_ext。这可导致负阈值电压nfet 690的激活,从而允许内部供应电压vccr的电压电平紧密地遵循外部供应电压vcc_ext的电压电平。电容器692的较高电容值可用于使外部供应电压vcc_ext与内部供应电压vccr之间的间隙变窄。应注意,pfet 696,以及pfet 704和708可在t0处撤销激活,因为外部供应电压vcc_ext的电压电平可低于pfet 696、704和708的阈值电压。外部供应电压vcc_ext到反相器702的输入的耦合可用于通过将反相器702的输出驱动到参考电位来撤销激活nfet 694。随着外部供应电压vcc_ext的电压电平增加,nfet 706可激活以将pfet 696和704的控制栅极的电压电平维持在参考电位。

[0055]

在时间t1处,外部供应电压vcc_ext可达到足以激活pfet 704的电平,例如,约1v,从而导致内部供应电压vccr的电压电平的快速增加。此类快速转变可导致电源的电流需求的尖峰。然而,因为内部供应电压vccr已遵循外部供应电压vcc_ext的电压电平,所以增加的量值预期小于相关技术,使得电流需求的尖峰也可能更小。通过具有连接到输出462的其第二源极/漏极的pfet 704,其可辅助nfet 690跟踪外部供应电压vcc_ext的电压电平。因而,可预期内部供应电压vccr的电压电平更紧密地遵循外部供应电压vcc_ext的电压电平。pfet 696还可在时间t1处激活,因此允许控制栅极电压vg也更紧密地跟踪外部供应电压vcc_ext,这可将nfet 690维持处于饱和状态。

[0056]

在时间t2处,控制信号puhelp_en可转变到逻辑高电平(例如,内部供应电压vccr),因此通过反相器700的输出处的逻辑低电平(例如,参考电位)撤销激活nfet 706,并且通过反相器702的输出处的逻辑高电平激活nfet 694。这可导致pfet 708的激活,所述激活可导致pfet 696和704的撤销激活。控制栅极电压vg可进一步返回到参考电位以撤销激活负阈值电压nfet 690。时间t2可对应于低于电压调节器的目标电压电平的外部供应电压vcc_ext的电压电平。时间t2可进一步对应于足够高以将电压调节器的参考电压发展到高于电压调节器的反馈电压电平的电压电平的外部供应电压vcc_ext的电压电平。此时,电压调节器可接管内部供应电压vccr的电压电平的调节,而无如相关技术中所见的电流需求的第二尖峰。此类操作与相关技术相比可进一步促进更快达到内部供应电压vccr的稳态电压电平,并且可想象地在外部供应电压vcc_ext达到其稳态电压电平之前。

[0057]

图9是根据实施例的操作集成电路装置,例如存储器的方法的流程图。方法可表示与集成电路装置,例如存储器的通电相关联的动作。方法可呈例如存储到指令寄存器128的计算机可读指令的形式。此类计算机可读指令可由控制器,例如,控制逻辑116执行,以致使集成电路装置的相关组件执行方法。

[0058]

在901处,在电压调节器的输入的电压电平具有第一电压电平时,电压调节器的输出可通过电流路径连接到电压调节器的输入。举例来说,在外部供应电压vcc_ext具有第一电压电平时,电压调节器352的输出462可通过电压跟踪器658的nfet 690连接到电压调节器352的输入460。第一电压电平可对应于参考电位,或可以其它方式对应于高于nfet 690的阈值电压的电压电平。

[0059]

在903处,可维持电压调节器的输出通过电流路径到电压调节器的输入的连接,直到电压调节器的输入的电压电平具有高于第一电压电平的第二电压电平为止。举例来说,在外部供应电压vcc_ext的电压电平从第一电压电平斜变到第二电压电平时,nfet690可保

持激活。第二电压电平可低于用于电压调节器352的输出462的目标电压电平。

[0060]

在905处,在电压调节器的输入的电压电平具有第二电压电平之后,电压调节器的输出可通过电流路径与电压调节器的输入隔离。举例来说,在外部供应电压vcc_ext的电压电平达到第二电压电平之后,可响应于控制信号puhelp_en而撤销激活电压跟踪器658的nfet 690。应注意,电压调节器可在其输出与输入之间具有不同电流路径,例如,通过电压调节器352的pfet 476。然而,在nfet 690撤销激活时,电压调节器的输出不具有通过电流路径到其输入的连接。因而,即使存在通过某一其它电流路径的连接,它们也通过电流路径隔离。

[0061]

在907处,在电压调节器的输出通过电流路径与电压调节器的输入隔离时,可调节电压调节器的输出的电压电平。举例来说,运算放大器466可响应于来自分压器470的反馈电压而控制pfet 476的控制栅极,例如不同电流路径上的电压电平以选择性地将电压调节器352的输出462连接到其输入460。应注意,在外部供应电压vcc_ext达到第二电压电平之前,运算放大器466可控制pfet 476的控制栅极上的电压电平。然而,虽然输出462通过nfet 690连接到输入460,但电压调节器352不可被认为控制输出462的电压电平。

[0062]

图10是根据另一实施例的操作集成电路装置,例如存储器的方法的流程图。方法可表示与集成电路装置,例如存储器的通电相关联的动作。方法可呈例如存储到指令寄存器128的计算机可读指令的形式。此类计算机可读指令可由控制器,例如,控制逻辑116执行,以致使集成电路装置的相关组件执行方法。

[0063]

在1001处,在电压调节器的输入的电压电平具有第一电压电平时,电压调节器的输出可通过第一电流路径连接到电压调节器的输入。举例来说,在外部供应电压vcc_ext具有第一电压电平时,电压调节器352的输出462可通过电压跟踪器658的nfet 690连接到电压调节器352的输入460。第一电压电平可对应于参考电位,或可以其它方式对应于高于nfet 690的阈值电压的电压电平。

[0064]

在1003处,在电压调节器的输入的电压电平具有高于第一电压电平的第二电压电平时,电压调节器的输出可通过第二电流路径连接到电压调节器的输入。举例来说,在外部供应电压vcc_ext具有第二电压电平时,电压调节器352的输出462可通过电压跟踪器658的pfet 704连接到电压调节器352的输入460。第二电压电平可对应于pfet704的阈值电压。

[0065]

在1005处,可维持电压调节器的输出通过第一电流路径到电压调节器的输入的连接,直到电压调节器的输入的电压电平具有高于第二电压电平的第三电压电平为止。举例来说,在外部供应电压vcc_ext的电压电平从第一电压电平斜变到第三电压电平时,nfet 690可保持激活。第三电压电平可低于用于电压调节器352的输出462的目标电压电平。

[0066]

在1007处,可维持电压调节器的输出通过第二电流路径到电压调节器的输入的连接,直到电压调节器的输入的电压电平具有第三电压电平为止。举例来说,在外部供应电压vcc_ext的电压电平从第二电压电平斜变到第三电压电平时,pfet 704可保持激活。

[0067]

在1009处,在电压调节器的输入的电压电平具有第三电压电平之后,电压调节器的输出可通过第一电流路径且通过第二电流路径与电压调节器的输入隔离。举例来说,在外部供应电压vcc_ext的电压电平达到第三电压电平之后,可响应于控制信号puhelp_en而撤销激活(例如,同时)nfet 690和pfet 704。

[0068]

在1011处,在电压调节器的输出通过第一电流路径且通过第二电流路径与电压调

节器的输入隔离时,可调节电压调节器的输出的电压电平。举例来说,运算放大器466可响应于来自分压器470的反馈电压而控制pfet 476的控制栅极,例如第三电流路径上的电压电平以选择性地将电压调节器352的输出462连接到其输入460。应注意,在外部供应电压vcc_ext达到第三电压电平之前,运算放大器466可控制pfet 476的控制栅极上的电压电平。然而,虽然输出462通过nfet 690和/或pfet 704连接到输入460,但电压调节器352不可被认为控制输出462的电压电平。

[0069]

结论

[0070]

虽然本文中已说明且描述具体实施例,但所属领域的一般技术人员应了解,预计实现相同目的的任何布置可取代所展示的具体实施例。所属领域的一般技术人员将清楚实施例的许多修改。因此,本技术意图涵盖实施例的任何调适或变型。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。