1.本发明涉及压电器件。

背景技术:

2.作为公开压电器件的结构的文献,有国际公开第2017/218299号(专利文献1)。专利文献1中记载的压电器件具备基板和膜片部。基板具有贯通基板的开口部。膜片部由至少一个弹性层、以及夹在上部电极层与下部电极层之间的至少一个压电层形成。膜片部在开口部的上方安装于基板。在靠近开口部的端部的膜片部,通过蚀刻形成有贯通槽。现有技术文献专利文献

3.专利文献1:国际公开第2017/218299号

技术实现要素:

发明要解决的课题

4.在膜片部上下振动时,与通过贯通槽的流体之间的粘性阻力大的情况下,压电器件的激励效率降低。

5.本发明是鉴于上述问题点而完成的,其目的在于,提供一种激励效率高的压电器件。用于解决课题的技术方案

6.基于本发明的压电器件具备基部和层叠部。基部包括一个主面和位于与一个主面相反的一侧的另一个主面,且具有从一个主面贯通至另一个主面的开口部。层叠部层叠在基部的一个主面侧,从上方覆盖开口部。层叠部至少在开口部的上方包括:单晶压电体层、配置在单晶压电体层的上侧的上部电极层、隔着单晶压电体层而与上部电极层的至少一部分相对的下部电极层、在与单晶压电体层之间夹着上部电极层或下部电极层的增强层,且具有作为覆盖开口部的部分的膜片部。在膜片部设置有沿上下方向贯通的贯通槽。单晶压电体层中的贯通槽的宽度随着向下方而变窄。在单晶压电体层和增强层中,位于下侧的层中的贯通槽的最大宽度比位于上侧的层中的贯通槽的最小宽度小。发明的效果

7.根据本发明,能够提高压电器件的激励效率。

附图说明

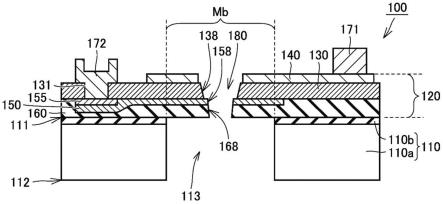

8.图1是本发明的实施方式1涉及的压电器件的俯视图。图2是从ii-ii线箭头方向对图1的压电器件进行观察的剖视图。图3是示出在本发明的实施方式1涉及的压电器件的制造方法中、在单晶压电体层的下表面设置了密接层的状态的剖视图。图4是示出在本发明的实施方式1涉及的压电器件的制造方法中、在密接层和单晶

压电体层的各自的下表面设置了下部电极层的状态的剖视图。图5是示出在本发明的实施方式1涉及的压电器件的制造方法中、在下部电极层和单晶压电体层的各自的下表面设置了增强层的状态的剖视图。图6是示出在本发明的实施方式1涉及的压电器件的制造方法中、使增强层的下表面平坦后的状态的剖视图。图7是示出在本发明的实施方式1涉及的压电器件的制造方法中、拟使基部接合到图6所示的多个层的状态的剖视图。图8是示出在本发明的实施方式1涉及的压电器件的制造方法中、使基部接合于增强层的下表面之后的状态的剖视图。图9是示出在本发明的实施方式1涉及的压电器件的制造方法中、削去单晶压电体层的上表面之后的状态的剖视图。图10是示出在本发明的实施方式1涉及的压电器件的制造方法中、在单晶压电体层的上表面设置了上部电极层的状态的剖视图。图11是示出在本发明的实施方式1涉及的压电器件的制造方法中、在单晶压电体层设置了孔部的状态的剖视图。图12是示出在本发明的实施方式1涉及的压电器件的制造方法中、在单晶压电体层设置了贯通槽的状态的剖视图。图13是示出在本发明的实施方式1涉及的压电器件的制造方法中、以到达增强层的下表面的方式设置了贯通槽的状态的剖视图。图14是示出在本发明的实施方式1涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。图15是示出本发明的实施方式1的第1变形例涉及的压电器件的结构的剖视图。图16是示出本发明的实施方式1的第2变形例涉及的压电器件的结构的剖视图。图17是本发明的实施方式1的第2变形例涉及的压电器件中的膜片部的贯通槽的纵剖面形状的示意图。图18是示出本发明的实施方式1的第3变形例涉及的压电器件的结构的剖视图。图19是本发明的实施方式1的第3变形例涉及的压电器件中的膜片部的贯通槽的纵剖面形状的示意图。图20是本发明的实施方式2涉及的压电器件的剖视图。图21是示出在本发明的实施方式2涉及的压电器件的制造方法中、在下部电极层和单晶压电体层的各自的下表面设置了增强层的状态的剖视图。图22是示出在本发明的实施方式2涉及的压电器件的制造方法中、使增强层的下表面平坦后的状态的剖视图。图23是示出在本发明的实施方式2涉及的压电器件的制造方法中、拟使基部接合到图22所示的多个层的状态的剖视图。图24是示出在本发明的实施方式2涉及的压电器件的制造方法中、使基部接合于增强层的下表面之后的状态的剖视图。图25是示出在本发明的实施方式2涉及的压电器件的制造方法中、削去单晶压电体层的上表面之后的状态的剖视图。

图26是示出在本发明的实施方式2涉及的压电器件的制造方法中、在单晶压电体层的上表面设置了上部电极层的状态的剖视图。图27是示出在本发明的实施方式2涉及的压电器件的制造方法中、在单晶压电体层设置了孔部的状态的剖视图。图28是示出在本发明的实施方式2涉及的压电器件的制造方法中、在单晶压电体层设置了贯通槽的状态的剖视图。图29是示出在本发明的实施方式2涉及的压电器件的制造方法中、以到达增强层的下表面的方式设置了贯通槽的状态的剖视图。图30是示出在本发明的实施方式2涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。图31是示出本发明的实施方式2的第1变形例涉及的压电器件的结构的剖视图。图32是示出本发明的实施方式2的第2变形例涉及的压电器件的结构的剖视图。图33是示出本发明的实施方式2的第3变形例涉及的压电器件的结构的剖视图。图34是本发明的实施方式3涉及的压电器件的剖视图。图35是示出在本发明的实施方式3涉及的压电器件的制造方法中、拟使图6所示的多个层与层叠了追加增强层的基部接合的状态的剖视图。图36是示出在本发明的实施方式3涉及的压电器件的制造方法中、使追加增强层接合于增强层的下表面之后的状态的剖视图。图37是示出在本发明的实施方式3涉及的压电器件的制造方法中、削去单晶压电体层的上表面之后的状态的剖视图。图38是示出在本发明的实施方式3涉及的压电器件的制造方法中、在单晶压电体层的上表面设置了上部电极层的状态的剖视图。图39是示出在本发明的实施方式3涉及的压电器件的制造方法中、在单晶压电体层设置了孔部的状态的剖视图。图40是示出在本发明的实施方式3涉及的压电器件的制造方法中、在单晶压电体层设置了贯通槽的状态的剖视图。图41是示出在本发明的实施方式3涉及的压电器件的制造方法中、以到达增强层的下表面的方式设置了贯通槽的状态的剖视图。图42是示出在本发明的实施方式3涉及的压电器件的制造方法中、以到达追加增强层的下表面的方式设置了贯通槽的状态的剖视图。图43是示出在本发明的实施方式3涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。图44是示出本发明的实施方式3的第1变形例涉及的压电器件的结构的剖视图。图45是示出本发明的实施方式3的第2变形例涉及的压电器件的结构的剖视图。图46是示出本发明的实施方式3的第3变形例涉及的压电器件的结构的剖视图。图47是本发明的实施方式4涉及的压电器件的剖视图。图48是示出在本发明的实施方式4涉及的压电器件的制造方法中、在上部电极层和单晶压电体层的各自的上表面设置了增强层的状态的剖视图。图49是示出在本发明的实施方式4涉及的压电器件的制造方法中、使增强层的上

表面平坦后的状态的剖视图。图50是示出在本发明的实施方式4涉及的压电器件的制造方法中、在单晶压电体层和增强层分别设置了孔部的状态的剖视图。图51是示出在本发明的实施方式4涉及的压电器件的制造方法中、在增强层和上部电极层分别设置了贯通槽的状态的剖视图。图52是示出在本发明的实施方式4涉及的压电器件的制造方法中、以到达下部电极层的下表面的方式设置了贯通槽的状态的剖视图。图53是示出在本发明的实施方式4涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。图54是示出本发明的实施方式4的第1变形例涉及的压电器件的结构的剖视图。图55是示出本发明的实施方式4的第2变形例涉及的压电器件的结构的剖视图。图56是示出本发明的实施方式4的第3变形例涉及的压电器件的结构的剖视图。图57是本发明的实施方式5涉及的压电器件的剖视图。图58是示出在本发明的实施方式5涉及的压电器件的制造方法中、拟使单晶压电体层接合到soi基板的状态的剖视图。图59是示出在本发明的实施方式5涉及的压电器件的制造方法中、削去单晶压电体层的上表面之后的状态的剖视图。图60是示出在本发明的实施方式5涉及的压电器件的制造方法中、在单晶压电体层的上表面设置了上部电极层的状态的剖视图。图61是示出在本发明的实施方式5涉及的压电器件的制造方法中、在单晶压电体层设置了孔部的状态的剖视图。图62是示出在本发明的实施方式5涉及的压电器件的制造方法中、在单晶压电体层设置了贯通槽的状态的剖视图。图63是示出在本发明的实施方式5涉及的压电器件的制造方法中、以到达增强层的下表面的方式设置了贯通槽的状态的剖视图。图64是示出在本发明的实施方式5涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。图65是本发明的实施方式6涉及的压电器件的剖视图。图66是示出在本发明的实施方式6涉及的压电器件的制造方法中、在单晶压电体层的各自的上表面设置了增强层的状态的剖视图。图67是示出在本发明的实施方式6涉及的压电器件的制造方法中、在单晶压电体层和增强层分别设置了孔部的状态的剖视图。图68是示出在本发明的实施方式6涉及的压电器件的制造方法中、在增强层设置了贯通槽的状态的剖视图。图69是示出在本发明的实施方式6涉及的压电器件的制造方法中、以到达下部电极层的下表面的方式设置了贯通槽的状态的剖视图。图70是示出在本发明的实施方式6涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。图71是本发明的实施方式7涉及的压电器件的剖视图。

图72是示出在本发明的实施方式7涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。图73是示出在本发明的实施方式7涉及的压电器件的制造方法中、以从开口部侧到达下部电极层的上表面的方式设置了贯通槽的状态的剖视图。图74是本发明的实施方式7涉及的压电器件中的膜片部的贯通槽的纵剖面形状的示意图。

具体实施方式

9.以下,参照附图对本发明的各实施方式涉及的压电器件进行说明。在以下的实施方式的说明中,对图中的相同或者相应的部分标注相同的附图标记,不再重复其说明。

10.(实施方式1)图1是本发明的实施方式1涉及的压电器件的俯视图。图2是从ii-ii线箭头方向对图1的压电器件进行观察的剖视图。在图1中,用虚线表示压电器件的内部的结构。如图1和图2所示,本发明的实施方式1涉及的压电器件100具备基部110和层叠部120。

11.基部110包含一个主面111和位于与一个主面111相反的一侧的另一个主面112。基部110具有从一个主面111贯通至另一个主面112的开口部113。开口部113被层叠在基部110的一个主面111侧的层叠部120从上方覆盖。

12.在本实施方式中,基部110由本体基部110a和覆盖本体基部110a的上表面的表层基部110b构成。在本实施方式中,本体基部110a由si构成,表层基部110b由sio2构成。但是,构成本体基部110a的材料并不限定于si,构成表层基部110b的材料并不限定于sio2。

13.层叠部120至少在开口部113的上方包括单晶压电体层130、上部电极层140、下部电极层150和增强层160。

14.层叠部120具有作为覆盖开口部113的部分的膜片部mb。从与一个主面111正交的方向观察,膜片部mb是层叠部120中的位于开口部113的开口端部的内侧的部分。在膜片部mb设置有沿上下方向贯通膜片部mb的贯通槽180。

15.单晶压电体层130位于比基部110靠上侧。单晶压电体层130的一部分位于开口部113的上方。单晶压电体层130的上表面和下表面各自是平坦的。

16.单晶压电体层130具有孔部131。孔部131上下贯通单晶压电体层130。在本实施方式中,孔部131位于基部110的一个主面111的上方,而不位于开口部113的上方。

17.单晶压电体层130由钽酸锂或者铌酸锂构成。关于由钽酸锂或者铌酸锂构成的单晶压电体层130,极化状态相同。

18.上部电极层140配置在单晶压电体层130的上侧。上部电极层140的一部分位于开口部113的上方。在本实施方式中,上部电极层140配置在单晶压电体层130的一部分的上侧。上部电极层140例如由al或者pt等金属构成。另外,也可以在上部电极层140与单晶压电体层130之间配置有由ti等构成的密接层。

19.下部电极层150隔着单晶压电体层130而与上部电极层140的至少一部分相对。在本实施方式中,下部电极层150的一部分隔着单晶压电体层130而与上部电极层140的一部分相对。下部电极层150的一部分位于开口部113的上方。

20.下部电极层150的另一部分位于形成在单晶压电体层130的孔部131的下方。在本

实施方式中,下部电极层150的另一部分经由密接层155与单晶压电体层130连接。密接层155从下方覆盖单晶压电体层130的孔部131。另外,未必一定要设置密接层155。在未设置密接层155的情况下,下部电极层150的另一部分从下方直接覆盖孔部131。

21.下部电极层150例如由al或者pt等金属构成。关于密接层155的材料,只要是具有导电性和密接性的材料,就没有特别限定。密接层155例如由ti、cr、ni或者nicr构成。

22.增强层160在与单晶压电体层130之间夹着上部电极层140或者下部电极层150。在本实施方式中,增强层160配置在比单晶压电体层130靠下方处。增强层160在与单晶压电体层130之间夹着下部电极层150。增强层160分别与下部电极层150的下表面、以及单晶压电体层130的下表面中未被下部电极层150覆盖的部分相接。

23.增强层160的一部分位于开口部113的上方。增强层160的一部分覆盖开口部113。未覆盖开口部113的部分的增强层160与基部110相互直接连接。另外,未覆盖开口部113的部分的增强层160与基部110也可以不相互直接连接。未覆盖开口部113的部分的增强层160与基部110可以经由金属层相互连接。

24.在本实施方式中,增强层160由si3n4构成。另外,增强层160的材料并不限定于si3n4,也可以是其他绝缘物。例如,增强层160也可以由具有电绝缘性和绝热性的有机材料构成。

25.如图1和图2所示,压电器件100还包括第一引出布线171和第二引出布线172。第一引出布线171层叠在上部电极层140的一部分的上侧。第二引出布线172层叠在单晶压电体层130的一部分和密接层155的各自的上侧。第二引出布线172在孔部131内经由密接层155层叠在下部电极层150的上侧。

26.这样,层叠部120至少在开口部113的上方包括单晶压电体层130、上部电极层140、下部电极层150和增强层160。

27.在本实施方式中,从与一个主面111正交的方向观察,开口部113的外形为矩形。但是,从与一个主面111正交的方向观察,开口部113的外形不限于矩形,也可以是矩形以外的多边形或者圆形。

28.根据上述结构,通过在上部电极层140与下部电极层150之间施加电压,膜片部mb根据单晶压电体层130的伸缩而上下弯曲振动。

29.如上所述,在膜片部mb设置有沿上下方向贯通膜片部mb的贯通槽180。贯通槽180的宽度在单晶压电体层130和增强层160的各自层中随着向下方而变窄。

30.在单晶压电体层130和增强层160中,位于下侧的层中的贯通槽180的最大宽度比位于上侧的层中的贯通槽的最小宽度小。在本实施方式中,增强层160是位于下侧的层,单晶压电体层130是位于上侧的层。增强层160中的贯通槽180的最大宽度比单晶压电体层130中的贯通槽180的最小宽度小。

31.具体而言,单晶压电体层130具有与贯通槽180相接的端面138。增强层160具有与贯通槽180相接的端面168。夹在单晶压电体层130与增强层160之间的下部电极层150具有端面158。

32.在本实施方式中,端面138为上侧端面,端面168为下侧端面,端面158为中间端面。作为上侧端面的端面138的倾斜角度比作为下侧端面的端面168的倾斜角度小。即,单晶压电体层130中的贯通槽180的最小宽度,是单晶压电体层130的端面138的下端的位置处的贯

通槽180的宽度。增强层160中的贯通槽180的最大宽度,是增强层160的端面168的上端的位置处的贯通槽180的宽度。

33.作为中间端面的端面158位于作为下侧端面的端面168的延长面上,与端面168连续。在作为上侧端面的端面138与作为中间端面的端面158之间形成台阶。作为上侧端面的端面138的下端位于下部电极层150的上表面上。与贯通槽180相邻的、下部电极层150的上表面的一部分露出。

34.如图2所示,贯通槽180的宽度随着从贯通槽180的上端往下端而变窄。另外,贯通槽180的宽度也可以随着从贯通槽180的上端往下端而台阶状地变窄。即,也可以包括随着从贯通槽180的上端往下端而贯通槽180的宽度不变的部分。在本实施方式中,贯通槽180的宽度从上下方向的上部电极层140的上端的位置到下端的位置大致相同。贯通槽180的宽度也可以从上下方向的下部电极层150的上端的位置到下端的位置大致相同。在该情况下,下部电极层150的端面158的倾斜角度为90

°

。

35.贯通槽180在开口部113侧的端部处最窄。即,在上下方向的增强层160的端面168的下端的位置处,贯通槽180最窄。

36.以下,对本发明的实施方式1涉及的压电器件的制造方法进行说明。图3是示出在本发明的实施方式1涉及的压电器件的制造方法中、在单晶压电体层的下表面设置了密接层的状态的剖视图。形成时的单晶压电体层130的厚度比本实施方式涉及的压电器件100中最终包含的单晶压电体层130的厚度厚。

37.如图3所示,通过剥离(lift-off)法、镀敷法或者蚀刻法等,在单晶压电体层130的下表面设置密接层155。

38.图4是示出在本发明的实施方式1涉及的压电器件的制造方法中、在密接层和单晶压电体层的各自的下表面设置了下部电极层的状态的剖视图。如图4所示,通过剥离法、镀敷法或者蚀刻法等,在密接层155的下表面的整个面、以及单晶压电体层的下表面的一部分设置下部电极层150。

39.图5是示出在本发明的实施方式1涉及的压电器件的制造方法中、在下部电极层和单晶压电体层的各自的下表面设置了增强层的状态的剖视图。如图5所示,通过化学气相沉积(cvd,即chemical vapor deposition)法或者物理气相沉积(pvd,即physical vapor deposition)法等,在下部电极层150和单晶压电体层130的各自的下表面设置增强层160。

40.图6是示出在本发明的实施方式1涉及的压电器件的制造方法中、使增强层的下表面平坦后的状态的剖视图。如图6所示,通过化学机械研磨(cmp:chemical mechanical polishing)等使增强层160的下表面平坦。

41.图7是示出在本发明的实施方式1涉及的压电器件的制造方法中、拟使基部接合到图6所示的多个层的状态的剖视图。图8是示出在本发明的实施方式1涉及的压电器件的制造方法中、使基部接合于增强层的下表面之后的状态的剖视图。

42.如图7和图8所示,基部110由本体基部110a和覆盖本体基部110a的上表面的表层基部110b构成。表层基部110b是通过对本体基部110a的上表面进行热氧化而形成的。通过表面活性化接合或者原子扩散接合等,使未形成开口部113的、作为基部110的基板接合于增强层160的下表面。

43.图9是示出在本发明的实施方式1涉及的压电器件的制造方法中、削去单晶压电体

层的上表面之后的状态的剖视图。如图9所示,通过cmp等削去单晶压电体层130的上表面,使单晶压电体层130变为所希望的厚度。另外,也可以在单晶压电体层130的上表面侧预先通过进行离子注入从而形成剥离层。在该情况下,在通过切削或者cmp等削去单晶压电体层130的上表面之前,使剥离层剥离,由此单晶压电体层130的厚度调整变得容易。单晶压电体层130的厚度被调整为可获得电压的施加所引起的单晶压电体层130的所希望的激励。

44.图10是示出在本发明的实施方式1涉及的压电器件的制造方法中、在单晶压电体层的上表面设置了上部电极层的状态的剖视图。如图10所示,通过剥离法、镀敷法或者蚀刻法等,在单晶压电体层130的上表面的一部分设置上部电极层140。

45.图11是示出在本发明的实施方式1涉及的压电器件的制造方法中、在单晶压电体层设置了孔部的状态的剖视图。如图11所示,通过对单晶压电体层130的一部分进行蚀刻,形成孔部131。

46.图12是示出在本发明的实施方式1涉及的压电器件的制造方法中、在单晶压电体层设置了贯通槽的状态的剖视图。如图12所示,通过对单晶压电体层130进行蚀刻,在单晶压电体层130形成贯通槽180。由此,在单晶压电体层130形成与贯通槽180相接的端面138。

47.图13是示出在本发明的实施方式1涉及的压电器件的制造方法中、以到达增强层的下表面的方式设置了贯通槽的状态的剖视图。如图13所示,通过对下部电极层150以及增强层160进行蚀刻,分别在下部电极层150以及增强层160形成贯通槽180。由此,在下部电极层150形成与贯通槽180相接的端面158。在增强层160形成与贯通槽180相接的端面168。

48.图14是示出在本发明的实施方式1涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。如图14所示,从基部110的另一个主面112侧对基部110通过深度反应离子蚀刻等,在基部110形成开口部113。由此,在本实施方式涉及的压电器件100中形成膜片部mb。

49.最后,通过剥离法、镀敷法或者蚀刻法等分别设置第一引出布线171以及第二引出布线172。通过上述工序,可制造如图2所示的本发明的实施方式1涉及的压电器件100。

50.如上所述,在本发明的实施方式1涉及的压电器件100中,贯通槽180的宽度在单晶压电体层130和增强层160的各自层中随着向下方而变窄。在单晶压电体层130和增强层160中,位于下侧的层中的贯通槽180的最大宽度比位于上侧的层中的贯通槽180的最小宽度小。

51.由此,能够减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件100的激励效率。

52.在本实施方式中,能够确保单晶压电体层130所处的部分的贯通槽180的宽度较宽,同时能够使增强层160所处的部分的贯通槽180的宽度较窄。其结果是,能够缓和膜片部mb弯曲振动时作用于单晶压电体层130的应力,从而抑制单晶压电体层130与上部电极层140之间、以及单晶压电体层130与下部电极层150之间的各自的层间剥离的发生。

53.进而,能够使增强层160所处的部分的贯通槽180的宽度较窄,因此能够抑制因贯通槽180的宽度变得过宽而引起压电器件100的特性降低。例如,在压电器件100被用作音响器件的情况下,能够抑制因贯通槽180的宽度变得过宽而引起的声阻抗的降低。

54.在本实施方式涉及的压电器件100中,作为上侧端面的单晶压电体层130的端面138的倾斜角度,比作为下侧端面的增强层160的端面168的倾斜角度小。由此,能够有效地

降低单晶压电体层130的端面138处的粘性阻力。

55.在本实施方式涉及的压电器件100中,单晶压电体层130由钽酸锂或者铌酸锂构成。由此,能够提高压电器件100的压电特性。

56.以下,对本发明的实施方式1涉及的压电器件100的变形例进行说明。图15是示出本发明的实施方式1的第1变形例涉及的压电器件的结构的剖视图。在图15中,以与图2相同的剖面视图进行图示。如图15所示,在本发明的实施方式1的第1变形例涉及的压电器件100a中,作为下侧端面的增强层160的端面168a的倾斜角度,比作为上侧端面的单晶压电体层130的端面138a的倾斜角度小。作为中间端面的下部电极层150的端面158a位于作为下侧端面的端面168a的延长面上,与端面168a连续。由此,能够有效地降低增强层160的端面168a处的粘性阻力。

57.图16是示出本发明的实施方式1的第2变形例涉及的压电器件的结构的剖视图。在图16中,以与图2相同的剖面视图进行图示。如图16所示,在本发明的实施方式1的第2变形例涉及的压电器件100b中,在单晶压电体层130和增强层160中,位于下侧的层中的与贯通槽180相接的下侧端面、和位于上侧的层中的与贯通槽180相接的上侧端面,经由上部电极层140或者下部电极层150中的与贯通槽180相接的中间端面而连续。

58.在本变形例中,作为下侧端面的增强层160的端面168和作为上侧端面的单晶压电体层130的端面138b,经由作为中间端面的下部电极层150的端面158而连续。

59.如图16所示,在单晶压电体层130和增强层160中,位于上侧的层中的贯通槽180的最大宽度为du,位于上侧的层中的贯通槽180的最小宽度为dm1,位于下侧的层中的贯通槽180的最小宽度为db。上侧端面的倾斜角度比下侧端面的倾斜角度小。满足du>dm1>db的关系。

60.图17是本发明的实施方式1的第2变形例涉及的压电器件中的膜片部的贯通槽的纵剖面形状的示意图。如图17所示,通过使上侧端面的倾斜角度比下侧端面的倾斜角度小,能够减小对从上侧浸入贯通槽180的流体f1的粘性阻力。

61.由此,能够有效地减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件100b的激励效率。进而,能够缓和向单晶压电体层130与下部电极层150之间的应力集中,从而抑制单晶压电体层130与下部电极层150之间的层间剥离的发生。

62.图18是示出本发明的实施方式1的第3变形例涉及的压电器件的结构的剖视图。在图18中,以与图2相同的剖面视图进行图示。如图18所示,在本发明的实施方式1的第3变形例涉及的压电器件100c中,作为下侧端面的增强层160的端面168a的倾斜角度,比作为上侧端面的单晶压电体层130的端面138c的倾斜角度小。由此,能够有效地降低增强层160的端面168a处的粘性阻力。

63.此外,作为下侧端面的增强层160的端面168a和作为上侧端面的单晶压电体层130的端面138c,经由作为中间端面的下部电极层150的端面158a而连续。

64.如图18所示,在单晶压电体层130和增强层160中,位于上侧的层中的贯通槽180的最大宽度为du,位于上侧的层中的贯通槽180的最小宽度为dm2,位于下侧的层中的贯通槽180的最小宽度为db。下侧端面的倾斜角度比上侧端面的倾斜角度小。满足du>dm2>db的关系。

65.图19是本发明的实施方式1的第3变形例涉及的压电器件中的膜片部的贯通槽的纵剖面形状的示意图。如图19所示,通过使下侧端面的倾斜角度比上侧端面的倾斜角度小,能够减小对从下侧浸入贯通槽180的流体f2的粘性阻力。

66.由此,能够有效地减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件100c的激励效率。进而,能够缓和向单晶压电体层130与下部电极层150之间的应力集中,从而抑制单晶压电体层130与下部电极层150之间的层间剥离的发生。

67.如图17以及图19所示,在将位于上侧的层中的贯通槽180的最大宽度du、以及位于下侧的层中的贯通槽180的最小宽度db分别固定在一定的尺寸的情况下,满足dm1<dm2的关系。即,通过调整上侧端面的倾斜角度和下侧端面的倾斜角度,能够在维持贯通槽180的上下方向的两端的尺寸的同时控制贯通槽180的纵剖面的轮廓。从加工上的制约以及抑制异物向贯通槽180内的浸入的观点出发考虑,贯通槽180的上下方向的两端的尺寸的自由度小。因此,通过在维持贯通槽180的上下方向的两端的尺寸的同时分别调整上侧端面的倾斜角度以及下侧端面的倾斜角度,能够抑制异物向贯通槽180内的浸入,同时使与贯通槽180内的流体之间的粘性阻力具有所希望的分布。

68.(实施方式2)以下,参照附图对本发明的实施方式2涉及的压电器件进行说明。本发明的实施方式2涉及的压电器件的基部和增强层的结构与本发明的实施方式1涉及的压电器件100不同,因此对于与本发明的实施方式1涉及的压电器件100相同的结构,不再重复说明。

69.图20是本发明的实施方式2涉及的压电器件的剖视图。在图20中,以与图2相同的剖面视图进行图示。如图20所示,本发明的实施方式2涉及的压电器件200具备基部110和层叠部220。

70.在本实施方式中,基部110仅由本体基部110a构成。基部110的开口部113被层叠在基部110的一个主面111侧的层叠部220从上方覆盖。

71.本体基部110a由sio2构成。但是,构成本体基部110a的材料并不限定于sio2。

72.层叠部220至少在开口部113的上方包括单晶压电体层130、上部电极层140、下部电极层150和增强层260。

73.层叠部220具有作为覆盖开口部113的部分的膜片部mb。从与一个主面111正交的方向观察,膜片部mb是层叠部220中的位于开口部113的开口端部的内侧的部分。在膜片部mb设置有沿上下方向贯通膜片部mb的贯通槽180。

74.增强层260在与单晶压电体层130之间夹着下部电极层150。增强层260的一部分位于开口部113的上方。在增强层260的下表面形成有与基部110的开口部113连通的开口部263。开口部263位于开口部113的上方,具有上底面261。开口部263的上底面261构成膜片部mb的下表面。

75.在本实施方式中,增强层260由sio2构成。增强层260的材料并不限定于sio2,只要是绝缘物即可。例如,增强层260也可以由具有电绝缘性和绝热性的有机材料构成。

76.这样,层叠部220至少在开口部113的上方包括单晶压电体层130、上部电极层140、下部电极层150和增强层260。

77.如上所述,在膜片部mb设置有沿上下方向贯通膜片部mb的贯通槽180。贯通槽180

的宽度在单晶压电体层130和增强层260的各自层中随着向下方而变窄。

78.在单晶压电体层130和增强层260中,位于下侧的层中的贯通槽180的最大宽度比位于上侧的层中的贯通槽的最小宽度小。在本实施方式中,增强层260是位于下侧的层,单晶压电体层130是位于上侧的层。增强层260中的贯通槽180的最大宽度比单晶压电体层130中的贯通槽180的最小宽度小。

79.具体而言,单晶压电体层130具有与贯通槽180相接的端面138。增强层260具有与贯通槽180相接的端面268。夹在单晶压电体层130与增强层260之间的下部电极层150具有端面158。

80.在本实施方式中,端面138为上侧端面,端面268为下侧端面,端面158为中间端面。作为上侧端面的端面138的倾斜角度比作为下侧端面的端面268的倾斜角度小。即,单晶压电体层130中的贯通槽180的最小宽度,是单晶压电体层130的端面138的下端的位置处的贯通槽180的宽度。增强层260中的贯通槽180的最大宽度,是增强层260的端面268的上端的位置处的贯通槽180的宽度。作为中间端面的端面158位于作为下侧端面的端面268的延长面上,与端面268连续。

81.贯通槽180在开口部113侧的端部处最窄。即,在上下方向的增强层260的端面268的下端的位置处,贯通槽180最窄。

82.以下,对本发明的实施方式2涉及的压电器件的制造方法进行说明。图21是示出在本发明的实施方式2涉及的压电器件的制造方法中、在下部电极层和单晶压电体层的各自的下表面设置了增强层的状态的剖视图。首先,与本发明的实施方式1涉及的压电器件100的制造方法相同地,在单晶压电体层130的下侧分别设置密接层155和下部电极层150。接着,如图21所示,通过cvd法或者pvd法等,在下部电极层150和单晶压电体层130的各自的下表面设置增强层260。

83.图22是示出在本发明的实施方式2涉及的压电器件的制造方法中、使增强层的下表面变平坦后的状态的剖视图。如图22所示,通过cmp等使增强层260的下表面平坦。

84.图23是示出在本发明的实施方式2涉及的压电器件的制造方法中、拟使基部接合到图22所示的多个层的状态的剖视图。图24是示出在本发明的实施方式2涉及的压电器件的制造方法中、使基部接合于增强层的下表面的状态的剖视图。

85.如图23和图24所示,通过表面活性化接合或者原子扩散接合等,使未形成开口部113的、作为基部110的基板接合于增强层260的下表面。

86.图25是示出在本发明的实施方式2涉及的压电器件的制造方法中、削去单晶压电体层的上表面之后的状态的剖视图。如图25所示,通过cmp等削去单晶压电体层130的上表面,使单晶压电体层130变为所希望的厚度。

87.图26是示出在本发明的实施方式2涉及的压电器件的制造方法中、在单晶压电体层的上表面设置了上部电极层的状态的剖视图。如图26所示,通过剥离法、镀敷法或者蚀刻法等,在单晶压电体层130的上表面的一部分设置上部电极层140。

88.图27是示出在本发明的实施方式2涉及的压电器件的制造方法中、在单晶压电体层设置了孔部的状态的剖视图。如图27所示,通过对单晶压电体层130的一部分进行蚀刻,形成孔部131。

89.图28是示出在本发明的实施方式2涉及的压电器件的制造方法中、在单晶压电体

层设置了贯通槽的状态的剖视图。如图28所示,通过对单晶压电体层130进行蚀刻,在单晶压电体层130形成贯通槽180。由此,在单晶压电体层130形成与贯通槽180相接的端面138。

90.图29是示出在本发明的实施方式2涉及的压电器件的制造方法中、以到达增强层的下表面的方式设置了贯通槽的状态的剖视图。如图29所示,通过对下部电极层150以及增强层260进行蚀刻,分别在下部电极层150以及增强层260形成贯通槽180。由此,在下部电极层150形成与贯通槽180相接的端面158。在增强层260形成与贯通槽180相接的端面268。

91.图30是示出在本发明的实施方式2涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。如图30所示,通过从基部110的另一个主面112侧进行深度反应离子蚀刻等,在基部110形成开口部113,在增强层260形成开口部263。由此,在本实施方式涉及的压电器件200中形成膜片部mb。

92.最后,通过剥离法、镀敷法或者蚀刻法等分别设置第一引出布线171以及第二引出布线172。通过上述工序,可制造如图20所示的本发明的实施方式2涉及的压电器件200。

93.如上所述,在本发明的实施方式2涉及的压电器件200中,贯通槽180的宽度在单晶压电体层130和增强层260的各自层中随着向下方而变窄。在单晶压电体层130和增强层260中,位于下侧的层中的贯通槽180的最大宽度比位于上侧的层中的贯通槽180的最小宽度小。

94.由此,能够减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件200的激励效率。

95.在本实施方式涉及的压电器件200中,作为上侧端面的单晶压电体层130的端面138的倾斜角度,比作为下侧端面的增强层260的端面168的倾斜角度小。由此,能够有效地降低单晶压电体层130的端面138处的粘性阻力。

96.以下,对本发明的实施方式2涉及的压电器件200的变形例进行说明。图31是示出本发明的实施方式2的第1变形例涉及的压电器件的结构的剖视图。在图31中,以与图20相同的剖面视图进行图示。如图31所示,在本发明的实施方式2的第1变形例涉及的压电器件200a中,作为下侧端面的增强层260的端面268a的倾斜角度,比作为上侧端面的单晶压电体层130的端面138a的倾斜角度小。作为中间端面的下部电极层150的端面158a位于作为下侧端面的端面268a的延长面上,与端面268a连续。由此,能够有效地降低增强层260的端面268a处的粘性阻力。

97.图32是示出本发明的实施方式2的第2变形例涉及的压电器件的结构的剖视图。在图32中,以与图20相同的剖面视图进行图示。如图32所示,在本发明的实施方式2的第2变形例涉及的压电器件200b中,在单晶压电体层130和增强层260中,位于下侧的层中的与贯通槽180相接的下侧端面、和位于上侧的层中的与贯通槽180相接的上侧端面,经由上部电极层140或者下部电极层150中的与贯通槽180相接的中间端面而连续。

98.在本变形例中,作为下侧端面的增强层260的端面268和作为上侧端面的单晶压电体层130的端面138b经由作为中间端面的下部电极层150的端面158而连续。

99.由此,能够有效地减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件200b的激励效率。进而,能够缓和向单晶压电体层130与下部电极层150之间的应力集中,从而抑制单晶压电体层130与下部电极层150之间的层间剥离的发生。

100.图33是示出本发明的实施方式2的第3变形例涉及的压电器件的结构的剖视图。在图33中,以与图20相同的剖面视图进行图示。如图33所示,在本发明的实施方式2的第3变形例涉及的压电器件200c中,作为下侧端面的增强层260的端面268a的倾斜角度比作为上侧端面的单晶压电体层130的端面138c的倾斜角度小。由此,能够有效地降低增强层260的端面268a处的粘性阻力。

101.此外,作为下侧端面的增强层260的端面268a和作为上侧端面的单晶压电体层130的端面138c,经由作为中间端面的下部电极层150的端面158a而连续。

102.由此,能够有效地减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件200c的激励效率。进而,能够缓和向单晶压电体层130与下部电极层150之间的应力集中,从而抑制单晶压电体层130与下部电极层150之间的层间剥离的发生。

103.(实施方式3)以下,参照附图对本发明的实施方式3涉及的压电器件进行说明。本发明的实施方式3涉及的压电器件与本发明的实施方式1涉及的压电器件100的不同点在于,具备多个增强层,因此对于与本发明的实施方式1涉及的压电器件100相同的结构,不再重复说明。

104.图34是本发明的实施方式3涉及的压电器件的剖视图。在图34中,以与图2相同的剖面视图进行图示。如图34所示,本发明的实施方式3涉及的压电器件300具备基部110和层叠部320。

105.层叠部320至少在开口部113的上方包括单晶压电体层130、上部电极层140、下部电极层150、增强层160和追加增强层390。在本实施方式中,增强层由增强层160和追加增强层390这两层构成。

106.层叠部320具有作为覆盖开口部113的部分的膜片部mb。从与一个主面111正交的方向观察,膜片部mb是层叠部320中的位于开口部113的开口端部的内侧的部分。在膜片部mb设置有沿上下方向贯通膜片部mb的贯通槽180。

107.追加增强层390以从下方覆盖增强层160的方式层叠。在本实施方式中,追加增强层390设置为与增强层160的下表面相接。追加增强层390的下表面的一部分与基部110的一个主面111相接。

108.追加增强层390的一部分位于开口部113的上方。追加增强层390的一部分覆盖开口部113。未覆盖开口部113的部分的追加增强层390与基部110相互直接连接。另外,未覆盖开口部113的部分的追加增强层390与基部110也可以不相互直接连接。未覆盖开口部113的部分的追加增强层390与基部110可以经由金属层相互连接。

109.在本实施方式中,追加增强层390由si构成。基部110和追加增强层390为soi(silicon on insulator)基板。另外,追加增强层390的材料并不限定于si,也可以是绝缘物。例如,追加增强层390也可以由具有电绝缘性和绝热性的有机材料构成。

110.这样,层叠部320至少在开口部113的上方包括单晶压电体层130、上部电极层140、下部电极层150、增强层160和追加增强层390。

111.如上所述,在膜片部mb设置有沿上下方向贯通膜片部mb的贯通槽180。贯通槽180的宽度在单晶压电体层130和增强层的各自层中随着向下方而变窄。

112.在单晶压电体层130和增强层中,位于下侧的层中的贯通槽180的最大宽度比位于

上侧的层中的贯通槽的最小宽度小。在本实施方式中,增强层是位于下侧的层,单晶压电体层130是位于上侧的层。增强层中的贯通槽180的最大宽度比单晶压电体层130中的贯通槽180的最小宽度小。

113.具体而言,追加增强层390具有与贯通槽180相接的端面398。在本实施方式中,端面138为上侧端面,端面168和端面398分别为下侧端面,端面158为中间端面。作为上侧端面的端面138的倾斜角度,比作为下侧端面的端面168和端面398的各自的倾斜角度小。倾斜角度按照端面398、端面168、端面138的顺序减小。即,单晶压电体层130中的贯通槽180的最小宽度是单晶压电体层130的端面138的下端的位置处的贯通槽180的宽度。增强层中的贯通槽180的最大宽度是增强层160的端面168的上端的位置处的贯通槽180的宽度。

114.增强层160的端面168的倾斜角度比追加增强层390的端面398的倾斜角度小。在增强层160的端面168与追加增强层390的端面398之间形成台阶。增强层160的端面168的下端位于追加增强层390的上表面上。与贯通槽180相邻的、追加增强层390的上表面的一部分露出。

115.贯通槽180在开口部113侧的端部处最窄。即,在上下方向的追加增强层390的端面398的下端的位置处,贯通槽180最窄。

116.以下,对本发明的实施方式3涉及的压电器件的制造方法进行说明。图35是示出在本发明的实施方式3涉及的压电器件的制造方法中、拟使图6所示的多个层与层叠了追加增强层的基部接合的状态的剖视图。图36是示出在本发明的实施方式3涉及的压电器件的制造方法中、使追加增强层接合于增强层的下表面之后的状态的剖视图。

117.首先,与本发明的实施方式1涉及的压电器件100的制造方法相同地,在单晶压电体层130的下侧分别设置密接层155和下部电极层150。进而,在下部电极层150和单晶压电体层130的各自的下表面设置增强层160,使增强层160的下表面平坦。

118.接着,如图35所示,通过表面活性化接合或者原子扩散接合等,使追加增强层390接合于基部110的一个主面111。

119.如图35和图36所示,通过表面活性化接合或者原子扩散接合等,使作为接合了追加增强层390的基部110的基板接合于增强层160的下表面。

120.图37是示出在本发明的实施方式3涉及的压电器件的制造方法中、削去单晶压电体层的上表面之后的状态的剖视图。如图37所示,通过cmp等削去单晶压电体层130的上表面,使单晶压电体层130变为所希望的厚度。

121.图38是示出在本发明的实施方式3涉及的压电器件的制造方法中、在单晶压电体层的上表面设置了上部电极层的状态的剖视图。如图38所示,通过剥离法、镀敷法或者蚀刻法等,在单晶压电体层130的上表面的一部分设置上部电极层140。

122.图39是示出在本发明的实施方式3涉及的压电器件的制造方法中、在单晶压电体层设置了孔部的状态的剖视图。如图39所示,通过对单晶压电体层130的一部分进行蚀刻,形成孔部131。

123.图40是示出在本发明的实施方式3涉及的压电器件的制造方法中、在单晶压电体层设置了贯通槽的状态的剖视图。如图40所示,通过对单晶压电体层130进行蚀刻,在单晶压电体层130形成贯通槽180。由此,在单晶压电体层130形成与贯通槽180相接的端面138。

124.图41是示出在本发明的实施方式3涉及的压电器件的制造方法中、以到达增强层的下表面的方式设置了贯通槽的状态的剖视图。如图41所示,通过对下部电极层150以及增强层160进行蚀刻,分别在下部电极层150以及增强层160形成贯通槽180。由此,在下部电极层150形成与贯通槽180相接的端面158。在增强层160形成与贯通槽180相接的端面168。

125.图42是示出在本发明的实施方式3涉及的压电器件的制造方法中、以到达追加增强层的下表面的方式设置了贯通槽的状态的剖视图。如图42所示,通过对追加增强层390进行蚀刻,在追加增强层390形成贯通槽180。由此,在追加增强层390形成与贯通槽180相接的端面398。

126.图43是示出在本发明的实施方式3涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。如图43所示,通过从基部110的另一个主面112侧进行深度反应离子蚀刻等,在基部110形成开口部113。由此,在本实施方式涉及的压电器件300中形成膜片部mb。

127.最后,通过剥离法、镀敷法或者蚀刻法等分别设置第一引出布线171以及第二引出布线172。通过上述工序,可制造如图34所示的本发明的实施方式3涉及的压电器件300。

128.如上所述,在本发明的实施方式3涉及的压电器件300中,贯通槽180的宽度在单晶压电体层130和增强层的各自层中随着向下方而变窄。在单晶压电体层130和增强层中,位于下侧的层中的贯通槽180的最大宽度比位于上侧的层中的贯通槽180的最小宽度小。

129.由此,能够减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件300的激励效率。

130.在本实施方式涉及的压电器件300中,作为上侧端面的单晶压电体层130的端面138的倾斜角度,比作为下侧端面的增强层160的端面168和追加增强层390的端面398的各自的倾斜角度小。由此,能够有效地降低单晶压电体层130的端面138处的粘性阻力。

131.以下,对本发明的实施方式3涉及的压电器件300的变形例进行说明。图44是示出本发明的实施方式3的第1变形例涉及的压电器件的结构的剖视图。在图44中,以与图34相同的剖面视图进行图示。如图44所示,在本发明的实施方式3的第1变形例涉及的压电器件300a中,作为下侧端面的增强层160的端面168a和追加增强层390的端面398a的各自的倾斜角度,比作为上侧端面的单晶压电体层130的端面138a的倾斜角度小。倾斜角度按照端面138a、端面168a、端面398a的顺序减小。作为中间端面的下部电极层150的端面158a位于作为下侧端面的端面168a的延长面上,与端面168a连续。由此,能够有效地降低增强层160的端面168a和追加增强层390的端面398a各自处的粘性阻力。

132.图45是示出本发明的实施方式3的第2变形例涉及的压电器件的结构的剖视图。在图45中,以与图34相同的剖面视图进行图示。如图45所示,在本发明的实施方式3的第2变形例涉及的压电器件300b中,作为上侧端面的单晶压电体层130的端面138b的倾斜角度,比作为下侧端面的增强层160的端面168b和追加增强层390的端面398的各自的倾斜角度小。倾斜角度按照端面398、端面168b、端面138b的顺序减小。在单晶压电体层130和增强层中,位于下侧的层中的与贯通槽180相接的下侧端面、和位于上侧的层中的与贯通槽180相接的上侧端面,经由上部电极层140或者下部电极层150中的与贯通槽180相接的中间端面而连续。

133.在本变形例中,作为下侧端面的增强层160的端面168b和作为上侧端面的单晶压电体层130的端面138b,经由作为中间端面的下部电极层150的端面158b而连续。

134.由此,能够有效地减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘

性阻力,从而提高压电器件300b的激励效率。进而,能够缓和向单晶压电体层130与下部电极层150之间的应力集中,从而抑制单晶压电体层130与下部电极层150之间的层间剥离的发生。

135.图46是示出本发明的实施方式3的第3变形例涉及的压电器件的结构的剖视图。在图46中,以与图34相同的剖面视图进行图示。如图46所示,在本发明的实施方式3的第3变形例涉及的压电器件300c中,作为下侧端面的增强层160的端面168c和追加增强层390的端面398a的各自的倾斜角度,比作为上侧端面的单晶压电体层130的端面138c的倾斜角度小。倾斜角度按照端面138c、端面168c、端面398a的顺序减小。由此,能够有效地降低增强层160的端面168c和追加增强层390的端面398a各自处的粘性阻力。

136.此外,作为下侧端面的增强层160的端面168c和作为上侧端面的单晶压电体层130的端面138c,经由作为中间端面的下部电极层150的端面158c而连续。

137.由此,能够有效地减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件300c的激励效率。进而,能够缓和向单晶压电体层130与下部电极层150之间的应力集中,从而抑制单晶压电体层130与下部电极层150之间的层间剥离的发生。

138.(实施方式4)以下,参照附图对本发明的实施方式4涉及的压电器件进行说明。本发明的实施方式4涉及的压电器件与本发明的实施方式1涉及的压电器件100的不同主要在于基部和增强层的结构,因此对于与本发明的实施方式1涉及的压电器件100相同的结构,不再重复说明。

139.图47是本发明的实施方式4涉及的压电器件的剖视图。在图47中,以与图2相同的剖面视图进行图示。如图47所示,本发明的实施方式4涉及的压电器件400具备基部110和层叠部420。

140.在本实施方式中,基部110仅由本体基部110a构成。基部110的开口部113被层叠在基部110的一个主面111侧的层叠部420从上方覆盖。

141.层叠部420至少在开口部113的上方包括单晶压电体层130、上部电极层140、下部电极层150和增强层460。层叠部420还包括中间层490。

142.层叠部420具有作为覆盖开口部113的部分的膜片部mb。从与一个主面111正交的方向观察,膜片部mb是层叠部420中的位于开口部113的开口端部的内侧的部分。在膜片部mb设置有沿上下方向贯通膜片部mb的贯通槽180。

143.增强层460在与单晶压电体层130之间夹着上部电极层140。增强层460的一部分位于开口部113的上方。

144.在本实施方式中,增强层460由si3n4构成。增强层460的材料并不限定于si3n4,也可以是其他绝缘物。例如,增强层460也可以由具有电绝缘性和绝热性的有机材料构成。在增强层460由电阻率低的si构成的情况下,可以不设置上部电极层140而使增强层460作为上部电极层发挥功能。

145.这样,层叠部420至少在开口部113的上方包括单晶压电体层130、上部电极层140、下部电极层150和增强层460。

146.中间层490在与单晶压电体层130之间夹着下部电极层150。在中间层490的下表面形成有与基部110的开口部113连通的开口部493。开口部493位于开口部113的上方。通过开

口部493,下部电极层150的下表面的一部分露出。通过开口部493露出的下部电极层150的下表面的一部分构成膜片部mb的下表面。

147.中间层490由sio2构成。中间层490的材料并不限定于sio2,只要是绝缘物即可。例如,中间层490也可以由具有电绝缘性和绝热性的有机材料构成。

148.如上所述,在膜片部mb设置有沿上下方向贯通膜片部mb的贯通槽180。贯通槽180的宽度在单晶压电体层130和增强层460的各自层中随着向下方而变窄。

149.在单晶压电体层130和增强层460中,位于下侧的层中的贯通槽180的最大宽度比位于上侧的层中的贯通槽的最小宽度小。在本实施方式中,单晶压电体层130是位于下侧的层,增强层460是位于上侧的层。单晶压电体层130中的贯通槽180的最大宽度比增强层460中的贯通槽180的最小宽度小。

150.具体而言,单晶压电体层130具有与贯通槽180相接的端面138。增强层460具有与贯通槽180相接的端面468。夹在单晶压电体层130与增强层460之间的上部电极层140具有端面148。

151.在本实施方式中,端面468为上侧端面,端面138为下侧端面,端面148为中间端面。作为上侧端面的端面468的倾斜角度,比作为下侧端面的端面138的倾斜角度小。即,单晶压电体层130中的贯通槽180的最小宽度,是单晶压电体层130的端面138的下端的位置处的贯通槽180的宽度。增强层460中的贯通槽180的最大宽度,是增强层460的端面468的上端的位置处的贯通槽180的宽度。作为中间端面的端面148位于作为上侧端面的端面468的延长面上,与端面468连续。

152.贯通槽180在开口部113侧的端部处最窄。即,在上下方向的下部电极层150的端面158的下端的位置处,贯通槽180最窄。

153.以下,对本发明的实施方式4涉及的压电器件的制造方法进行说明。图48是示出在本发明的实施方式4涉及的压电器件的制造方法中、在上部电极层和单晶压电体层的各自的上表面设置了增强层的状态的剖视图。首先,在截至本发明的实施方式2涉及的压电器件200的制造方法中的图26所示的工序中,除了形成中间层490来代替增强层260这一点之外,本发明的实施方式4涉及的压电器件的制造方法与本发明的实施方式2涉及的压电器件200的制造方法相同。

154.接着,如图48所示,通过cvd法或者pvd法等,在上部电极层140和单晶压电体层130的各自的上表面设置增强层460。

155.图49是示出在本发明的实施方式4涉及的压电器件的制造方法中、使增强层的上表面变平坦后的状态的剖视图。如图49所示,通过cmp等使增强层460的上表面平坦。

156.图50是示出在本发明的实施方式4涉及的压电器件的制造方法中、在单晶压电体层和增强层分别设置了孔部的状态的剖视图。如图50所示,通过对单晶压电体层130和增强层460的各自的一部分进行蚀刻,在单晶压电体层130形成孔部131,在增强层460分别形成孔部461和孔部462。

157.图51是示出在本发明的实施方式4涉及的压电器件的制造方法中、在增强层和上部电极层分别设置了贯通槽的状态的剖视图。如图51所示,通过对增强层460和上部电极层140进行蚀刻,分别在增强层460和上部电极层140形成贯通槽180。由此,在增强层460形成与贯通槽180相接的端面468。在上部电极层140形成与贯通槽180相接的端面148。

158.图52是示出在本发明的实施方式4涉及的压电器件的制造方法中、以到达下部电极层的下表面的方式设置了贯通槽的状态的剖视图。如图52所示,通过对单晶压电体层130和下部电极层150进行蚀刻,分别在单晶压电体层130和下部电极层150形成贯通槽180。由此,在单晶压电体层130形成与贯通槽180相接的端面138。在下部电极层150形成与贯通槽180相接的端面158。

159.图53是示出在本发明的实施方式4涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。如图53所示,通过从基部110的另一个主面112侧进行深度反应离子蚀刻等,在基部110形成开口部113,在中间层490形成开口部493。由此,在本实施方式涉及的压电器件400中形成膜片部mb。

160.最后,通过剥离法、镀敷法或者蚀刻法等分别设置第一引出布线171以及第二引出布线172。通过上述工序,制造如图47所示的本发明的实施方式4涉及的压电器件400。

161.如上所述,在本发明的实施方式4涉及的压电器件400中,贯通槽180的宽度在单晶压电体层130和增强层460的各自层中随着向下方而变窄。在单晶压电体层130和增强层460中,位于下侧的层中的贯通槽180的最大宽度比位于上侧的层中的贯通槽180的最小宽度小。

162.由此,能够减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件400的激励效率。

163.在本实施方式涉及的压电器件400中,作为上侧端面的增强层460的端面468的倾斜角度,比作为下侧端面的单晶压电体层130的端面138的倾斜角度小。由此,能够有效地降低增强层460的端面468处的粘性阻力。

164.以下,对本发明的实施方式4涉及的压电器件400的变形例进行说明。图54是示出本发明的实施方式4的第1变形例涉及的压电器件的结构的剖视图。在图54中,以与图47相同的剖面视图进行图示。

165.如图54所示,在本发明的实施方式4的第1变形例涉及的压电器件400a中,作为下侧端面的单晶压电体层130的端面138a的倾斜角度,比作为上侧端面的增强层460的端面468a的倾斜角度小。作为中间端面的上部电极层140的端面148a位于作为上侧端面的端面468a的延长面上,与端面468a连续。下部电极层150的端面158a位于作为下侧端面的端面138a的延长面上,与端面138a连续。由此,能够有效地降低单晶压电体层130的端面138a处的粘性阻力。

166.图55是示出本发明的实施方式4的第2变形例涉及的压电器件的结构的剖视图。在图55中,以与图47相同的剖面视图进行图示。如图55所示,在本发明的实施方式4的第2变形例涉及的压电器件400b中,在单晶压电体层130和增强层460中,位于下侧的层中的与贯通槽180相接的下侧端面、和位于上侧的层中的与贯通槽180相接的上侧端面,经由上部电极层140或者下部电极层150中的与贯通槽180相接的中间端面而连续。

167.在本变形例中,作为下侧端面的单晶压电体层130的端面138和作为上侧端面的增强层460的端面468b,经由作为中间端面的上部电极层140的端面148b而连续。

168.由此,能够有效地减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件400b的激励效率。进而,能够缓和向单晶压电体层130与上部电极层140之间的应力集中,从而抑制单晶压电体层130与上部电极层140之间的层间剥离的

发生。

169.图56是示出本发明的实施方式4的第3变形例涉及的压电器件的结构的剖视图。在图56中,以与图47相同的剖面视图进行图示。如图56所示,在本发明的实施方式4的第3变形例涉及的压电器件400c中,作为下侧端面的单晶压电体层130的端面138c的倾斜角度,比作为上侧端面的增强层460的端面468c的倾斜角度小。由此,能够有效地降低单晶压电体层130的端面138c处的粘性阻力。

170.此外,作为下侧端面的单晶压电体层130的端面138c和作为上侧端面的增强层460的端面468c,经由作为中间端面的上部电极层140的端面148c而连续。下部电极层150的端面158c位于作为下侧端面的端面138c的延长面上,与端面138c连续。

171.由此,能够有效地减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件400c的激励效率。进而,能够缓和向单晶压电体层130与上部电极层140之间的应力集中,从而抑制单晶压电体层130与上部电极层140之间的层间剥离的发生。

172.(实施方式5)以下,参照附图对本发明的实施方式5涉及的压电器件进行说明。本发明的实施方式5涉及的压电器件与本发明的实施方式1涉及的压电器件100的不同点在于,增强层兼作下部电极层,因此对于与本发明的实施方式1涉及的压电器件100相同的结构,不再重复说明。

173.图57是本发明的实施方式5涉及的压电器件的剖视图。在图57中,以与图2相同的剖面视图进行图示。如图57所示,本发明的实施方式5涉及的压电器件500具备基部110和层叠部520。

174.层叠部520至少在开口部113的上方包括单晶压电体层130、上部电极层140和增强层560。

175.层叠部520具有作为覆盖开口部113的部分的膜片部mb。从与一个主面111正交的方向观察,膜片部mb是层叠部520中的位于开口部113的开口端部的内侧的部分。在膜片部mb设置有沿上下方向贯通膜片部mb的贯通槽180。

176.上部电极层140与单晶压电体层130相邻配置。上部电极层140配置在单晶压电体层130的上侧。

177.增强层560隔着单晶压电体层130而与上部电极层140的至少一部分相对。增强层560与单晶压电体层130的下表面相邻。

178.增强层560的一部分位于开口部113的上方。增强层560的一部分覆盖开口部113。未覆盖开口部113的部分的增强层560与基部110相互直接连接。另外,未覆盖开口部113的部分的增强层560与基部110也可以不相互直接连接。未覆盖开口部113的部分的增强层560与基部110可以经由金属层相互连接。

179.增强层560由si构成。基部110和增强层560为soi基板。增强层560的材料不限定于si,只要是具有导电性的材料即可。

180.贯通槽180的宽度在单晶压电体层130和增强层560的各自层中随着向下方而变窄。在单晶压电体层130和增强层560中,位于下侧的层中的贯通槽180的最大宽度比位于上侧的层中的贯通槽的最小宽度小。在本实施方式中,增强层560是位于下侧的层,单晶压电

体层130是位于上侧的层。增强层560中的贯通槽180的最大宽度比单晶压电体层130中的贯通槽180的最小宽度小。

181.增强层560具有与贯通槽180相接的端面568。在本实施方式中,端面138为上侧端面,端面568为下侧端面。作为上侧端面的端面138的倾斜角度,比作为下侧端面的端面568的倾斜角度小。另外,也可以是作为下侧端面的端面568的倾斜角度比作为上侧端面的端面138的倾斜角度小。

182.单晶压电体层130中的贯通槽180的最小宽度,是单晶压电体层130的端面138的下端的位置处的贯通槽180的宽度。增强层560中的贯通槽180的最大宽度,是增强层560的端面568的上端的位置处的贯通槽180的宽度。如图57所示,贯通槽180的宽度随着从贯通槽180的上端往下端而变窄。

183.贯通槽180在开口部113侧的端部处最窄。即,在上下方向的增强层560的端面568的下端的位置处,贯通槽180最窄。

184.以下,对本发明的实施方式5涉及的压电器件的制造方法进行说明。图58是示出在本发明的实施方式5涉及的压电器件的制造方法中、拟使单晶压电体层接合到soi基板的状态的剖视图。如图58所示,通过表面活性化接合或者原子扩散接合等,使soi基板接合于单晶压电体层130的下表面。

185.图59是示出在本发明的实施方式5涉及的压电器件的制造方法中、削去单晶压电体层的上表面之后的状态的剖视图。如图9所示,通过cmp等削去单晶压电体层130的上表面,使单晶压电体层130变为所希望的厚度。另外,也可以在单晶压电体层130的上表面侧预先通过进行离子注入从而形成剥离层。在该情况下,在通过切削或者cmp等削去单晶压电体层130的上表面之前,使剥离层剥离,由此单晶压电体层130的厚度调整变得容易。单晶压电体层130的厚度被调整为可获得电压的施加所引起的单晶压电体层130的所希望的激励。

186.图60是示出在本发明的实施方式5涉及的压电器件的制造方法中、在单晶压电体层的上表面设置了上部电极层的状态的剖视图。如图60所示,通过剥离法、镀敷法或者蚀刻法等,在单晶压电体层130的上表面的一部分设置上部电极层140。

187.图61是示出在本发明的实施方式5涉及的压电器件的制造方法中、在单晶压电体层设置了孔部的状态的剖视图。如图61所示,通过对单晶压电体层130的一部分进行蚀刻,形成孔部131。

188.图62是示出在本发明的实施方式5涉及的压电器件的制造方法中、在单晶压电体层设置了贯通槽的状态的剖视图。如图62所示,通过对单晶压电体层130进行蚀刻,在单晶压电体层130形成贯通槽180。由此,在单晶压电体层130形成与贯通槽180相接的端面138。

189.图63是示出在本发明的实施方式5涉及的压电器件的制造方法中、以到达增强层的下表面的方式设置了贯通槽的状态的剖视图。如图63所示,通过对增强层560进行蚀刻,在增强层560形成贯通槽180。由此,在增强层560形成与贯通槽180相接的端面568。

190.图64是示出在本发明的实施方式5涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。如图64所示,从基部110的另一个主面112侧对基部110通过深度反应离子蚀刻等,在基部110形成开口部113。由此,在本实施方式涉及的压电器件500中形成膜片部mb。

191.最后,通过剥离法、镀敷法或者蚀刻法等分别设置第一引出布线171以及第二引出

布线172。通过上述工序,制造如图57所示的本发明的实施方式5涉及的压电器件500。

192.如上所述,在本发明的实施方式5涉及的压电器件500中,贯通槽180的宽度在单晶压电体层130和增强层560的各自层中随着向下方而变窄。在单晶压电体层130和增强层560中,位于下侧的层中的贯通槽180的最大宽度比位于上侧的层中的贯通槽180的最小宽度小。

193.由此,能够减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件200的激励效率。

194.在本实施方式涉及的压电器件500中,作为上侧端面的单晶压电体层130的端面138的倾斜角度,比作为下侧端面的增强层560的端面568的倾斜角度小。由此,能够有效地降低单晶压电体层130的端面138处的粘性阻力。此外,通过使增强层560作为下部电极层发挥功能,能够简化压电器件500的结构。

195.(实施方式6)以下,参照附图对本发明的实施方式6涉及的压电器件进行说明。本发明的实施方式6涉及的压电器件与本发明的实施方式4涉及的压电器件400的不同点在于,增强层兼作上部电极层,因此对于与本发明的实施方式4涉及的压电器件400相同的结构,不再重复说明。

196.图65是本发明的实施方式6涉及的压电器件的剖视图。在图65中,以与图2相同的剖面视图进行图示。如图65所示,本发明的实施方式6涉及的压电器件600具备基部110和层叠部620。

197.在本实施方式中,基部110仅由本体基部110a构成。基部110的开口部113被层叠在基部110的一个主面111侧的层叠部620从上方覆盖。

198.层叠部620至少在开口部113的上方包括单晶压电体层130、下部电极层150和增强层660。层叠部620还包括中间层490。

199.层叠部620具有作为覆盖开口部113的部分的膜片部mb。从与一个主面111正交的方向观察,膜片部mb是层叠部620中的位于开口部113的开口端部的内侧的部分。在膜片部mb设置有沿上下方向贯通膜片部mb的贯通槽180。

200.下部电极层150与单晶压电体层130相邻配置。下部电极层150配置在单晶压电体层130的下侧。

201.增强层660隔着单晶压电体层130而与下部电极层150的至少一部分相对。增强层660与单晶压电体层130的上表面相邻。增强层660的一部分位于开口部113的上方。增强层660的一部分覆盖开口部113。

202.增强层660由si构成。增强层660的材料不限定于si,只要是具有导电性的材料即可。

203.贯通槽180的宽度在单晶压电体层130和增强层660的各自层中随着向下方而变窄。在单晶压电体层130和增强层660中,位于下侧的层中的贯通槽180的最大宽度比位于上侧的层中的贯通槽的最小宽度小。在本实施方式中,单晶压电体层130是位于下侧的层,增强层660是位于上侧的层。单晶压电体层130中的贯通槽180的最大宽度比增强层660中的贯通槽180的最小宽度小。

204.增强层660具有与贯通槽180相接的端面668。在本实施方式中,端面668为上侧端

面,端面138为下侧端面。作为上侧端面的端面668的倾斜角度,比作为下侧端面的端面138的倾斜角度小。另外,也可以是作为下侧端面的端面138的倾斜角度比作为上侧端面的端面668的倾斜角度小。

205.单晶压电体层130中的贯通槽180的最小宽度,是单晶压电体层130的端面138的下端的位置处的贯通槽180的宽度。增强层660中的贯通槽180的最大宽度,是增强层660的端面668的上端的位置处的贯通槽180的宽度。如图65所示,贯通槽180的宽度随着从贯通槽180的上端往下端而变窄。

206.贯通槽180在开口部113侧的端部处最窄。即,在上下方向的下部电极层150的端面158的下端的位置处,贯通槽180最窄。

207.以下,对本发明的实施方式6涉及的压电器件的制造方法进行说明。图66是示出在本发明的实施方式6涉及的压电器件的制造方法中、在单晶压电体层的各自的上表面设置了增强层的状态的剖视图。首先,在截至本发明的实施方式2涉及的压电器件200的制造方法中的图25所示的工序中,除了形成中间层490来代替增强层260这一点之外,本发明的实施方式6涉及的压电器件的制造方法与本发明的实施方式2涉及的压电器件200的制造方法相同。

208.接着,如图66所示,通过cvd法或者pvd法等,在单晶压电体层130的上表面设置增强层660。

209.图67是示出在本发明的实施方式6涉及的压电器件的制造方法中、在单晶压电体层和增强层分别设置了孔部的状态的剖视图。如图67所示,通过对单晶压电体层130和增强层660的各自的一部分进行蚀刻,在单晶压电体层130形成孔部131,在增强层660形成孔部661。

210.图68是示出在本发明的实施方式6涉及的压电器件的制造方法中、在增强层设置了贯通槽的状态的剖视图。如图68所示,通过对增强层660进行蚀刻,在增强层660形成贯通槽180。由此,在增强层660形成与贯通槽180相接的端面668。

211.图69是示出在本发明的实施方式6涉及的压电器件的制造方法中、以到达下部电极层的下表面的方式设置了贯通槽的状态的剖视图。如图69所示,通过对单晶压电体层130和下部电极层150进行蚀刻,分别在单晶压电体层130和下部电极层150形成贯通槽180。由此,在单晶压电体层130形成与贯通槽180相接的端面138。在下部电极层150形成与贯通槽180相接的端面158。

212.图70是示出在本发明的实施方式6涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。如图70所示,通过从基部110的另一个主面112侧进行深度反应离子蚀刻等,在基部110形成开口部113,在中间层490形成开口部493。由此,在本实施方式涉及的压电器件600中形成膜片部mb。

213.最后,通过剥离法、镀敷法或者蚀刻法等分别设置第一引出布线171以及第二引出布线172。通过上述工序,可制造如图65所示的本发明的实施方式6涉及的压电器件600。

214.如上所述,在本发明的实施方式6涉及的压电器件600中,贯通槽180的宽度在单晶压电体层130和增强层660的各自层中随着向下方而变窄。在单晶压电体层130和增强层660中,位于下侧的层中的贯通槽180的最大宽度比位于上侧的层中的贯通槽180的最小宽度小。

215.由此,能够减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件600的激励效率。

216.在本实施方式涉及的压电器件600中,作为上侧端面的增强层660的端面668的倾斜角度,比作为下侧端面的单晶压电体层130的端面138的倾斜角度小。由此,能够有效地降低增强层660的端面668处的粘性阻力。此外,通过使增强层660作为上部电极层发挥功能,能够简化压电器件600的结构。

217.(实施方式7)以下,参照附图对本发明的实施方式7涉及的压电器件进行说明。本发明的实施方式7涉及的压电器件与本发明的实施方式1涉及的压电器件100的不同点在于,增强层中的贯通槽的宽度随着向下方而变宽,因此对于与本发明的实施方式1涉及的压电器件100相同的结构,不再重复说明。

218.图71是本发明的实施方式7涉及的压电器件的剖视图。在图71中,以与图2相同的剖面视图进行图示。如图71所示,本发明的实施方式7涉及的压电器件700具备基部110和层叠部120。

219.在本实施方式中,单晶压电体层130中的贯通槽180的宽度随着向下方而变窄。增强层160中的贯通槽180的宽度随着向下方而变宽。

220.在单晶压电体层130和增强层160中,位于下侧的层中的贯通槽180的最大宽度比位于上侧的层中的贯通槽的最小宽度小。在本实施方式中,增强层160是位于下侧的层,单晶压电体层130是位于上侧的层。增强层160中的贯通槽180的最大宽度比单晶压电体层130中的贯通槽180的最小宽度小。

221.贯通槽180在下部电极层150处最窄。具体而言,在上下方向的下部电极层150的端面158的上端的位置处,贯通槽180最窄。

222.以下,对本发明的实施方式7涉及的压电器件的制造方法进行说明。图72是示出在本发明的实施方式7涉及的压电器件的制造方法中、形成了开口部的状态的剖视图。首先,在截至本发明的实施方式1涉及的压电器件100的制造方法中的图12所示的工序中,本发明的实施方式7涉及的压电器件的制造方法与本发明的实施方式1涉及的压电器件100的制造方法相同。

223.如图72所示,从基部110的另一个主面112侧对基部110通过深度反应离子蚀刻等,在基部110形成开口部113。由此,在本实施方式涉及的压电器件700中形成膜片部mb。

224.图73是示出在本发明的实施方式7涉及的压电器件的制造方法中、以从开口部侧到达下部电极层的上表面的方式设置了贯通槽的状态的剖视图。如图73所示,通过从开口部113侧对下部电极层150以及增强层160进行蚀刻,分别在下部电极层150以及增强层160形成贯通槽180。由此,在下部电极层150形成与贯通槽180相接的端面158。在增强层160形成与贯通槽180相接的端面168。

225.如图73所示,在单晶压电体层130和增强层160中,位于上侧的层中的贯通槽180的最大宽度为du,位于上侧的层中的贯通槽180的最小宽度为dm3,位于下侧的层中的贯通槽180的最大宽度为db。满足du>dm3>db的关系。下部电极层150中的贯通槽180的最小宽度为dm4。满足db>dm4的关系。

226.最后,通过剥离法、镀敷法或者蚀刻法等分别设置第一引出布线171以及第二引出

布线172。通过上述工序,可制造如图73所示的本发明的实施方式7涉及的压电器件700。

227.图74是本发明的实施方式7涉及的压电器件中的膜片部的贯通槽的纵剖面形状的示意图。如图74所示,通过满足du>dm3>db>dm4的关系,能够分别减小对从上侧浸入贯通槽180的流体f1的粘性阻力、以及对从下侧浸入贯通槽180的流体f2的粘性阻力。

228.由此,能够有效地减小膜片部mb上下振动时的与通过贯通槽180的流体之间的粘性阻力,从而提高压电器件700的激励效率。

229.在上述实施方式的说明中,也可以将能够组合的结构相互组合。

230.应认为本次公开的实施方式在所有方面均为例示而不是限制性的。本发明的范围不是由上述的说明示出,而是由权利要求书示出,其意图包含与权利要求书等同的含义以及范围内的所有变更。附图标记说明

231.100、100a、100b、100c、200、200a、200b、200c、300、300a、300b、300c、400、400a、400b、400c、500、600、700:压电器件,110:基部,110a:本体基部,110b:表层基部,111:一个主面,112:另一个主面,113、263、493:开口部,120、220、320、420、520、620:层叠部,130:单晶压电体层,131、461、462、661:孔部,138、138a、138b、138c、148、148a、148b、148c、158、158a、158b、158c、168、168a、168b、168c、268、268a、398、398a、468、468a、468b、468c、568、668:端面,140:上部电极层,150:下部电极层,155:密接层,160、260、460、560、660:增强层,171:第一引出布线,172:第二引出布线,180:贯通槽,261:上底面,390:追加增强层,490:中间层,mb:膜片部。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。