1.本公开涉及具有经调谐温度相依性的定时电路。

背景技术:

2.定时电路在电子装置或系统中用于控制各种操作的定时。一个实例是在存储器装置中用于控制定时以感测存储于存储器装置的每个存储器单元中的数据位的状态的定时电路。此类定时电路可能将时间延迟引入到数字控制信号。已知时间延迟对包含定时电路的装置或系统的操作温度具有相依性。装置或系统中接收且使用定时电路的输出的目标电路也可能具有温度相依特性。装置或系统中的不同电路的此类温度相依性需要恰当地协调。需要在装置或系统的操作期间经历的温度变化中将装置或系统的每个重要定时信号或参数(例如,时间延迟)保持在其容差或合乎需要的范围内。

附图说明

3.在未必按比例绘制的图中,相似标号在不同视图中可描述类似组件。各图通过举例而非限制性地大体上说明本文件中所论述的各种实施例。

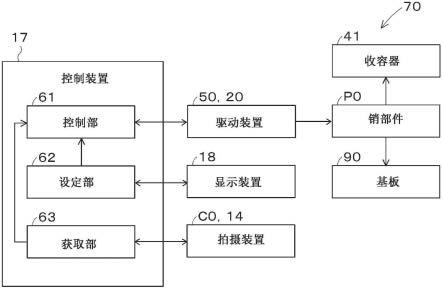

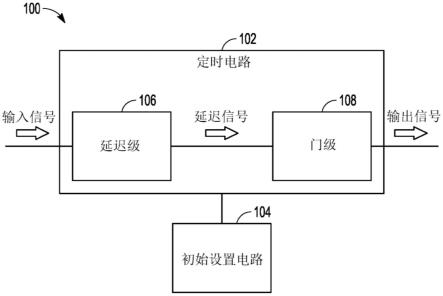

4.图1是说明用于为定时信号提供可调谐温度相依性的系统的实施例的框图。

5.图2是说明例如图1的定时电路等定时电路的信号的实例的图。

6.图3是说明例如图1的定时电路等定时电路的概念的实例的电路图。

7.图4是说明例如图1的定时电路等定时电路中的延迟信号的实例的图。

8.图5是说明图4的延迟信号的时间常数的实例的图。

9.图6是图3的定时电路中的门级的特性的实例的图示,包含说明门级的两个实例的电路图和展示对应于这两个实例的逻辑阈值的图。

10.图7是说明对应于图6的两个实例的图3的定时电路的时间延迟实例的图。

11.图8是说明例如图1的定时电路等定时电路的实施例的电路图。

12.图9是说明例如图1的定时电路等定时电路的另一实施例的电路图。

13.图10是说明例如图1的初始设置电路等初始设置电路的实施例的框图。

14.图11是说明用于为定时信号提供经调谐温度相依性的方法的实施例的流程图。

15.图12是说明用于调谐定时信号的温度相依性以例如提供图11的经调谐温度相依性的方法的实施例的流程图。

16.图13是说明包含用于提供各自具有可调谐温度相依性的定时信号的系统的电子装置的实施例的框图。

17.图14是说明用于生成示例性定时信号的图13的系统的部分的实施例的框图。

18.图15是说明用于生成示例性定时信号的图13的系统的部分的另一实施例的框图。

19.图16是说明图15的系统部分中的各种信号的定时的实施例的定时图。

具体实施方式

20.在以下详细描述中,参考了形成本文一部分的附图,且在附图中以图示方式展示其中可实践本发明的具体实施例。充分详细地描述了这些实施例以使得所属领域的技术人员能够实践本发明,且应理解,可组合实施例,或可利用其它实施例,且可在不脱离本发明的精神和范围的情况下进行结构、逻辑和电气变化。本公开中对“一”、“一个”或“各种”实施例的参考未必是对同一实施例的参考,且此类参考会考虑多于一个实施例。以下详细描述提供实例,且本发明的范围由所附权利要求书和其法定等同物限定。

21.本文件尤其论述一种定时电路,其提供具有准确的时间延迟的数字信号,且可经调谐以在预期温度变化中基本上遵循其目标电路的时间延迟。目标电路可包含使用定时电路的输出的电路,例如使用控制感测的定时的信号的存储器电路。在混合信号电路中,例如存储器电路中的感测裕度等重要时间间隔可具有正温度系数(时间间隔随温度增加而增加)或负温度系数(时间间隔随温度增加而减少)。当延迟电路和目标电路的时间间隔具有基本上匹配的温度系数时,可实现控制系统(例如,包含存储器装置的电路系统)的操作的定时参数。

22.本发明主题可提供一种定时电路,所述定时电路可在制造包含所述定时电路的装置期间针对所需或合乎需要的温度相依性进行调整,由此消除在装置的制造后操作期间调整温度相依性的需要。所述定时电路可包含延迟级和门级。所述门级具有可变逻辑阈值,所述可变逻辑阈值可在制造期间针对所要温度系数进行设置。通过至少调整逻辑阈值,定时电路可经调谐以为其输入信号与其输出信号之间的延迟提供合乎需要的温度系数。可指定此温度相依性,以允许对控制装置或系统中的各种信号和操作的定时的参数进行优化。

23.延迟级可包含向信号提供延迟且可放置在门级之前或之后的任何电路。延迟级可以是可调整的,以允许对定时电路的输入信号与输出信号之间的总体延迟的额外控制,包含对总体延迟的温度系数的控制。

24.在各种实施例中,定时电路可包含电阻-电容(rc)延迟级,随后是具有可变逻辑阈值的门级。rc延迟级产生具有时间常数(τ)的斜变电压信号,所述时间常数是电阻和电容的乘积(τ=rc),其可在制造期间通过调整电阻(r)和/或电容(c)进行设置。时间常数和逻辑阈值各自具有温度系数。通过调整定时常数和逻辑阈值,定时电路可经调谐为在其输入信号与其输出信号之间的延迟提供合乎需要的温度系数。

25.尽管rc延迟级在本文件中作为实例被具体论述,但各种实施例可使用任何类型的延迟电路作为延迟级。延迟级的另一实例包含一或多个门(例如,一或多个反相器)。可确定门的数目以在延迟级的输入信号与输出信号之间提供所要延迟。所述延迟级可具有可变延迟,所述可变延迟可在制造期间通过针对所要延迟选择要永久包含的门数目来进行设置。

26.许多形式的存储器装置可能会表现出某种形式的温度相依性,这是由于可随温度而变的一或多个功能所致。举例来说,一些存储器(在一些实例中为易失性存储器)可能响应于温度的改变而经历保持时间和/或编程时间的差异。在各种形式的存储器装置中,可能需要调整各种电压,例如读取和/或写入电压,以便补偿由温度变化引起的物理变化。通常,存储器装置可包含相对复杂的系统以监测和响应于温度而修改操作参数。仅作为非限制性实例,此类存储器装置可包含易失性和非易失性存储器两者。易失性存储器需要电力来维持其数据,且包含各种形式的随机存取存储器(ram),例如动态随机存取存储器(dram)、同

步动态随机存取存储器(sdram)、静态ram(sram)等。非易失性存储器可在未被供电时保持所存储数据,且可包含一或多种存储技术,例如快闪存储器(例如,nand或nor快闪)、电可擦除可编程rom(eeprom)、铁电ram(feram)、可擦除可编程rom(eprom)、电阻可变存储器,例如相变随机存取存储器(pcram)、电阻式随机存取存储器(rram)、磁阻式随机存取存储器(mram),或3d xpoint

tm

存储器等。

27.作为一个说明性实例,存储器装置中的ras(行地址选通)定时可包含具有各种温度系数的延迟。本发明主题可允许针对此类延迟设置适当温度系数。温度系数可在装置制造过程中针对装置的既定操作的测试阶段期间通过熔丝微调来校准。在装置的操作期间不需要制造后校准。

28.图1是说明用于为定时信号提供可调谐温度相依性的系统100的实施例的框图。系统100可包含定时电路102和初始设置电路104。定时电路100可接收输入信号且通过将时间延迟应用于所述输入信号而产生输出信号。定时电路102可包含延迟级106和门级108。延迟级106可通过将延迟引入到输入信号而产生延迟信号。门级108可接收延迟信号且使用所述延迟信号和逻辑阈值产生输出信号。门级108还可接收阈值设置信号且根据所述阈值设置信号来设置逻辑阈值的初始值。初始设置电路104可提供阈值设置信号且允许调谐阈值设置信号以用于为时间延迟提供指定温度相依性。

29.在一个实施例中,延迟级106通过将rc延迟引入到输入信号而产生延迟信号。延迟级106可接收延迟设置信号且根据所述延迟设置信号来设置时间常数的初始值。时间常数(τ)是rc延迟的量度(且也可称为rc延迟)。初始设置电路104可提供阈值设置信号和延迟设置信号,且允许阈值设置信号和延迟设置信号被调谐以为时间延迟提供指定温度相依性。这允许对时间延迟的温度相依性进行“2维调谐”(即,调谐时间常数和逻辑阈值)。延迟级106可经调谐以通过调整延迟设置信号来为时间常数提供正时间相依性或负时间相依性。门级108可经调谐以通过调整阈值设置信号来为逻辑阈值提供正时间相依性或负时间相依性。因此,系统100可经调谐以通过调整阈值设置信号和/或延迟设置信号来为时间延迟提供负温度相依性或正温度相依性。

30.在一个实施例中,初始设置电路104允许例如在包含系统100的电子装置的制造的测试模式期间通过熔丝微调来调整阈值设置信号和延迟设置信号。熔丝微调可指在此期间低电阻路径永久断开以例如断开电路中的电连接的过程。举例来说,数字输入可包含多个位线,每个位线使用熔丝连接到二进制电压电平,其方式允许将位永久地设置为二进制电平之一,使得可通过选择性地微调(熔断)熔丝来将数字输入设置成合乎需要的值。在各种实施例中,“熔丝”可包含非易失性寄存器,例如用于存储器装置的内部设置的存储器装置(例如,dram装置)内部的非易失性寄存器。阈值设置信号和延迟设置信号可各自为二进制代码,其中每个位在“熔丝微调”期间设置成“0”或“1”且存储在非易失性寄存器中。

31.图2是说明包含延迟级和门级的定时电路(例如,定时电路102)的信号的实例的图。此图展示分别对应于如图1中所展示的定时电路102的输入信号、延迟信号和输出信号的输入信号、延迟信号和输出信号。当输入信号改变其逻辑电平(如所展示从“0”到“1”)时,延迟信号利用时间常数τ=rc改变其逻辑电平,其中r和c是提供时间常数的延迟级的电阻和电容。当延迟信号越过(如所展示超过)门级的逻辑阈值时,输出改变其逻辑电平(如所展示从“0”到“1”)。时间常数和逻辑阈值确定时间延迟,所述时间延迟是输出信号响应于输入

信号中的逻辑电平变化而改变输出信号的逻辑电平所花费的时间。

32.图3是说明定时电路302的实例的电路图。定时电路302可表示展示例如定时电路102等定时电路如何工作的概念的实例。图2中所说明的输入信号、延迟信号和输出信号还分别对应于图3中所说明的定时电路302的输入信号、延迟信号和输出信号。

33.定时电路302可接收输入信号且通过将时间延迟应用于所述输入信号而产生输出信号。在各种实施例中,定时电路302用在包含接收所述输出信号的目标电路(例如,图13中展示的目标电路1352)的电子装置或系统中,且用于使用所述输出信号控制所述装置或系统的操作的定时。定时电路302具有可调谐的温度系数。也就是说,输出信号的时间延迟具有温度系数,且定时电路302经配置以允许所述温度系数被转动。在一个实施例中,定时电路302经配置以在装置或系统的制造期间例如通过熔丝微调来调谐以为时间延迟提供所述温度系数。在此文件中,定时电路的温度系数、输出信号的温度系数和时间延迟的温度系数是指同一温度系数,其为时间延迟的温度相依性的量度。时间延迟是要使用定时电路控制的参数。

34.定时电路302包含延迟级306,所述延迟级通过将rc延迟引入到输入信号而产生延迟信号。可通过时间常数τ=rc测量rc延迟,其中r表示对时间常数有贡献的延迟级306的电阻,且c表示对时间常数有贡献的延迟级306的电容。在各种实施例中,延迟级30可包含任何类型的rc延迟电路(包含但不限于本文件中的实例),所述rc延迟电路是产生延迟信号的电路,其中总电阻r和总电容c提供时间常数τ=rc。此时间常数(其也可称为rc延迟)可称作延迟级或延迟信号的时间常数(或rc延迟)。延迟级306接收延迟设置信号(例如,由初始设置电路104产生的延迟设置信号),且通过根据所述延迟设置信号调整电阻r或电容c中的至少一者来设置时间常数τ的初始值。在一个实施例中,通过使用可电子微调的电阻器可调整电阻r。尽管无源电阻器具有正温度系数,但如果期望具有负温度系数的电阻,则可使用有源(半导体型)电阻器。在一个实施例中,电容c可通过使用可电子微调的电容器调整,所述电容器可包含延迟级中的电容器和/或晶体管的电容。在各种实施例中,电阻r和电容c中的至少一者是可调整的,使得时间常数τ具有随电阻r和/或电容c的定时系数而变的温度系数。

35.图4是说明例如定时电路306等定时电路中的延迟信号的实例的图。此图展示在两个不同温度下的延迟信号的上升部分。差异引起不同温度下的输出信号的时间延迟的差异。

36.图5是说明图4的延迟信号的时间常数的实例的图。在所说明的实例中,时间常数具有正温度系数。

37.延迟级306可具有正温度相依性(例如,因为使用了简单的电阻器)或负温度相依性(例如,当使用半导体型电阻器时)。然而,因为以电子方式调整电阻和/或电容方面的实际限制,难以针对合乎需要的目标校准时间常数的温度相依性。另一方面,可针对宽范围的正和负温度相依性调整门级308的逻辑阈值,从而允许针对合乎需要的温度相依性(例如,基本上匹配目标电路中的一或多个信号的温度相依性)来校准输出信号中的时间延迟。

38.返回参考图3,门级308从延迟级306接收延迟信号且使用所述延迟信号和逻辑阈值产生输出信号。门级308响应于延迟信号越过逻辑阈值而将输出信号切换到不同逻辑电平(例如,响应于延迟信号超过逻辑阈值而将输出信号从“0”切换到“1”,如图2中所说明)。门级308包含阈值设置电路系统,所述阈值设置电路系统接收阈值设置信号(例如,由初始

设置电路104产生的阈值设置信号)且根据所述阈值设置信号将逻辑阈值设置成初始值。

39.在各种实施例中,可针对指定过程设置逻辑阈值的初始值,使得定时电路302在指定过程期间具有适当的温度相依性。所述过程可包含使用定时电路302的输出信号控制的目标电路的操作。所述适当的温度相依性可以是针对所述过程确定的目标温度相依性,以例如确保由温度变化产生的时间间隔中的误差在针对所述过程指定的容差范围内。可通过定时电路302的输出信号的温度系数将基本上匹配的温度系数来测量或指定目标温度相依性。在此文件中,“基本上匹配”可意指实际值匹配结果,所述值匹配受包含但不限于数字控制中的分辨率和制造容差内的误差等因素限制。

40.图6是门级308的特性的实例的图示,包含说明门级的两个实例(展示为门级608a和608b)的电路图和展示对应于所述两个实例的逻辑阈值的图。图6展示不同的逻辑阈值可由不同的晶体管特性产生。所说明的实例展示逻辑阈值,所述逻辑阈值具有正温度系数(“情况1”,对应于门级608a),和具有负温度系数的逻辑阈值(“情况2”,对应于门级608b)。

41.图7是说明对应于图6的两个实例的定时电路308的时间延迟实例的图。时间延迟具有由图5中展示的时间常数的温度系数和图6中展示的逻辑阈值的温度系数产生的温度系数(即,总体效应)。在各种实施例中,定时电路302的时间延迟的温度系数(其也可称为定时电路302的输出信号的温度系数或定时电路302的温度系数)可通过设置时间常数的初始值和逻辑阈值的初始值来调谐。此类2维校准提供可用于调谐时间延迟的温度系数的广泛范围的温度系数值。

42.图8是说明定时电路802的实施例的电路图,所述定时电路可表示定时电路102的实施方案的实例,其中延迟级806具有可调谐时间常数且门级808具有固定逻辑阈值。在所说明实施例中,延迟级806包含可电子微调的电容器,所述可电子微调的电容器的电容可使用延迟设置信号trimc《4:0》调整,所述延迟设置信号是允许选择电容的32个值的5位二进制代码。在一个实施例中,通过在制造包含定时电路802的电子装置或系统期间在测试模式下进行熔丝微调来设置trimc《4:0》。

43.在所说明的实施例中,定时电路802的时间延迟的温度系数可通过调整trimc《4:0》调谐,且因此受到可电子微调的电容器的可调整范围限制。在另一实施例中,延迟级806中的电阻器可以是可电子微调的电阻器。电阻器可以是用于通过无源电阻器不可实现的温度相依性的半导体型电阻器。在各种实施例中,延迟级806可包含可电子微调的电容器和/或可电子微调的电阻器以为延迟信号提供可针对正或负温度系数调谐的时间常数。

44.门级808具有固定逻辑阈值且因此具有固定温度相依性。因此,定时电路802的温度相依性的总体可调谐范围受到延迟级806的由可电子微调的电容器和/或可电子微调的电阻器提供的可调谐范围限制。此总可调谐范围可通过使门级的逻辑阈值可调谐而基本上扩展,如下文参考图9所论述。

45.图9是说明定时电路902的实施例的电路图,所述定时电路可表示定时电路102的实施方案的实例,其中延迟级806具有可调谐时间常数且门级908具有可调谐逻辑阈值。因此,定时电路902具有与定时电路802相同的延迟级,但具有提供对时间延迟的温度系数的更宽范围的控制的不同门级。

46.在所说明的实施例中,门级908包含阈值设置电路系统910,所述阈值设置电路系统包含可使用阈值设置信号trimd《3:0》来数字控制的上拉和下拉晶体管,所述阈值设置信

号是允许选择逻辑阈值的16个值的4位二进制代码。定时电路902的时间延迟的温度系数可通过调整trimc《4:0》和/或trimd《3:0》调谐。在另一实施例中,延迟级806可以是不具有可调谐时间常数的固定电路,且定时电路902的时间延迟的温度系数可通过单独调整trimd《3:0》来调谐。在一个实施例中,通过在制造包含定时电路902的电子装置或系统期间在测试模式下进行熔丝微调来设置trimc《4:0》和trimd《3:0》。

47.在各种实施例中,延迟设置信号可具有提供对延迟级806的时间常数的控制的合乎需要的分辨率和范围的任何数目个位,且阈值设置信号可具有提供对门级908的逻辑阈值的控制的合乎需要的分辨率和范围的任何数目的位。对时间常数的控制的合乎需要的分辨率和范围以及对逻辑阈值的控制的合乎需要的分辨率和范围取决于对定时电路902的输出信号中的时间延迟的温度系数的控制的合乎需要的分辨率和范围。

48.图10是说明可表示初始设置电路104的实例的初始设置电路1004的实施例的框图。在所说明的实施例中,初始设置电路1004包含一或多个延迟设置熔丝1012和一或多个阈值设置熔丝1014。在各种实施例中,取决于对延迟设置信号和阈值设置信号中的每一者的需要,初始设置电路1004可包含一或多个延迟设置熔丝1012和/或一或多个阈值设置熔丝1014。初始设置电路1004可将延迟设置信号和/或阈值设置信号提供到定时电路,例如定时电路102(包含但不限于在此文件中论述的其各种实例)。

49.延迟设置熔丝1012可提供延迟设置信号且允许调谐延迟设置信号以为延迟级106(包含但不限于在此文件中论述的其各种实例)的时间常数提供所要温度系数。在各种实施例中,延迟设置信号是通过在包含初始设置电路1004和接收二进制代码的定时电路的装置的制造期间进行熔丝微调而针对所要温度系数调整的二进制代码。在一个实施例中,延迟设置熔丝1012各自为非易失性寄存器,且熔丝微调是指确定二进制代码的值且将确定的值存储在非易失性寄存器中的过程。在各种实施例中,延迟设置信号可以是n位二进制信号(提供时间常数可设置成的2n个初始值)。

50.阈值设置熔丝1014可提供阈值设置信号且允许调谐阈值设置信号以为门级108(包含但不限于在此文件中论述的其各种实例)的逻辑阈值提供所要温度系数。在各种实施例中,阈值设置信号是通过在包含初始设置电路1004和接收二进制代码的定时电路的装置的制造期间进行熔丝微调而针对所要温度系数调整的二进制代码。在一个实施例中,阈值设置熔丝1014各自为非易失性寄存器,且熔丝微调是指确定二进制代码的值且将确定的值存储在非易失性寄存器中的过程。在各种实施例中,阈值设置信号可以是m位二进制信号(提供逻辑阈值可设置成的2m个初始值)。

51.图11是说明用于为定时信号提供经调谐温度相依性的方法1120的实施例的流程图。在一个实施例中,方法1120由定时电路(例如定时电路102(包含但不限于在此文件中论述的其各种实例))执行,所述定时电路可以是还包含接收且使用定时电路的输出的目标电路的电子装置或系统的部分。

52.在1121处,根据阈值设置信号设置逻辑阈值的初始值,和/或根据延迟设置信号设置rc时间常数(τ=rc)的初始值。各种实施例将逻辑阈值和时间常数两者用于产生定时信号,其中逻辑阈值或时间常数中的至少一者可通过调整初始值来调谐。定时信号的实例是还展示时间常数和逻辑阈值的图2中说明的输出信号。

53.在1122处,接收输入信号。在各种实施例中,输入信号是二进制信号,例如图2中所

说明的输入信号。

54.在1123处,通过将rc延迟引入到输入信号来产生延迟信号。所述时间常数是rc延迟的量度。在各种实施例中,延迟信号响应于输入信号从“0”变化到“1”而以时间常数上升,例如图2中所说明的延迟信号。

55.在1124处,使用延迟信号和逻辑阈值产生输出信号。在各种实施例中,响应于输入信号通过时间延迟改变其逻辑电平,输出信号改变其逻辑电平,例如图2中所说明的输出信号和时间延迟。时间延迟(以及因此输出信号)具有可影响例如目标电路的操作的温度相依性。温度相依性可例如使用下文论述的方法通过根据指定温度相依性设定逻辑阈值的初始值和/或时间常数的初始值来调谐。

56.图12是说明用于针对使用方法1120产生的具有方法1120中的经调谐温度相依性的时间延迟(以及因此输出信号)来调谐温度相依性的方法1230的实施例的流程图。

57.在1231处,确定目标温度系数。在各种实施例中,可针对接收且使用输出信号的目标电路的过程确定目标温度系数。

58.在1232处,针对(输入信号与输出信号之间的)时间延迟的温度系数指定温度相依性,以基本上匹配目标温度系数。举例来说,温度相依性可指定为具有基于目标电路的过程的性能要求可接受的容差范围的时间延迟的温度系数。

59.在1233处,阈值设置信号和/或延迟设置信号经调谐以为时间延迟提供指定温度相依性。在各种实施例中,阈值设置信号和/或延迟设置信号在制造电子装置期间在测试模式下进行调谐。调谐过程可包含熔丝微调,使得阈值设置信号和/或延迟设置信号由于调谐过程而被永久设置,且不需要制造后调整。“熔丝微调”可指确定用于阈值设置信号和/或延迟设置信号的二进制代码以及在测试模式下将确定的代码存储于一或多个非易失性寄存器中。在各种实施例中,定时电路经配置以允许通过调谐阈值设置信号和/或延迟设置信号而从负温度系数和正温度系数选择用于时间延迟的温度系数。时间延迟的温度系数是定时电路的总体温度系数,所述总体温度系数是逻辑阈值的温度系数和/或延迟信号的温度系数(其中任一者或两者是可调谐的)的函数。

60.图13是说明包含用于提供各自具有可调谐温度相依性的定时信号的系统1300的电子装置1350的实施例的框图。系统1300可表示系统100的实施例,其中多个定时电路1302各自耦合到多个初始设置电路1304中的一者。定时电路1302(1302-1、1302-2、

…

1302-n)可各自表示定时电路102的实例(包含但不限于在此文件中论述的其各种实例)。初始设置电路1304(1304-1、1304-2、

…

1304-n)可各自表示初始设置电路104的实例(包含但不限于在此文件中论述的其各种实例)。因此,系统1300的实例包含多个系统100(包含但不限于在此文件中论述的其各种实例)。

61.电子装置1350包含定时电路1302、初始设置电路1304、目标电路1352和存储器单元1354。在各种实施例中,电子装置1350包含需要用于适当操作的重要定时信号的微电子装置,例如dram或feram装置,其中存储器单元1353包含dram或feram单元和任选地非易失性寄存器(例如,用于存储阈值设置信号和/或延迟设置信号)。

62.目标电路1352可从定时电路1302接收输出信号且使用输出信号控制电子装置1350的操作。目标电路1352具有目标电路温度系数,所述目标电路温度系数可经确定以用于指定定时电路1302的时间延迟的温度系数(例如,在方法1230的1231处)。在各种实施例

中,例如通过执行方法1230,在制造电子装置1350期间调谐定时电路1302的时间延迟的温度系数。随后,当电子装置1350用于其预期应用时,定时电路1302例如通过执行方法1120而操作。虽然图13展示并联布置的定时电路1302,但在各种实施例中,取决于所需的定时信号,定时电路1302可并联和/或串联连接。

63.图14和15各自是说明用于当电子装置1350为例如dram或feram装置等存储器装置时生成地址解码定时信号、字线(wl)启用定时信号和感测定时信号的系统1300的部分的实施例的框图。在图14中所说明的实施例中,定时电路1302-1、1302-2和1203-3串联连接以分别响应于定时命令而控制地址解码定时信号的起始时间、地址解码信号的起始与wl启用定时信号之间的延迟以及wl启用定时信号与感测定时信号之间的延迟。图15中所说明的实施例提供替代实施例,其中单个定时电路1302-1用于产生相同定时信号。

64.图16是展示图15中所说明的实施例中的各种信号的定时图。在图15中所说明的实施例中,响应于定时命令,定时电路1302-1生成一连串脉冲n1。脉冲计数器1560接收n1且对脉冲数目进行计数且生成表示计数的数目的代码(代码)。比较器1562比较代码与多个阈值代码,且在代码超过每个阈值代码时生成定时信号。在所说明的实施例中,比较器1562-1将代码与第一阈值(代码1)进行比较且当代码超过第一阈值时生成地址解码定时信号,比较器1562-2将代码与第二阈值(代码2)进行比较且当代码超过第二阈值时生成wl启用定时信号,且s比较器1562-3将代码与第三阈值(代码3)进行比较且当代码超过第二阈值时生成感测定时信号。如图16中作为实例所说明,第一、第二和第三阈值代码分别为4、8和d。

65.本发明主题的一些非限制性实例(实例1到22)提供如下:

66.在实例1中,一种用于在电子装置中为定时信号提供可调谐温度相依性的系统可包含定时电路和初始设置电路。所述定时电路可经配置以接收输入信号且通过将时间延迟应用于所述输入信号而产生输出信号,且可包含延迟级和门级。所述延迟级可经配置以通过将延迟引入到输入信号而产生延迟信号。所述门级可经配置以接收所述延迟信号和阈值设置信号,以使用所述延迟信号和逻辑阈值产生所述输出信号且根据所述阈值设置信号设置所述逻辑阈值的初始值。所述初始设置电路可经配置以提供所述阈值设置信号且允许调谐所述阈值设置信号以用于为时间延迟提供指定温度相依性。

67.在实例2中,实例1的主题可任选地经配置以使得所述延迟级经配置以通过将电阻-电容(rc)延迟引入到所述输入信号来产生所述延迟信号、接收延迟设置信号以及根据所述延迟设置信号设置时间常数的初始值,所述时间常数是rc延迟的量度,且所述初始设置电路另外经配置以提供所述阈值设置信号和所述延迟设置信号且允许调谐所述阈值设置信号和延迟设置信号以用于为时间延迟提供指定温度相依性。

68.在实例3中,实例2的主题可任选地经配置以使得定时电路经配置以可调谐以用于通过调谐所述阈值设置信号或所述延迟设置信号中的至少一者而为时间延迟提供负温度相依性。

69.在实例4中,实例2的主题可任选地经配置以使得定时电路经配置以可调谐以用于通过调谐所述阈值设置信号或所述延迟设置信号中的至少一者而为时间延迟提供正温度相依性。

70.在实例5中,实例2到4中的任一者或任何组合的主题可任选地经配置以使得初始设置电路另外经配置以允许通过熔丝微调来调谐阈值设置信号和延迟设置信号。

71.在实例6中,实例5的主题可任选地经配置以使得初始设置电路包含经配置以产生所述阈值设置信号的一或多个阈值设置熔丝,所述一或多个阈值设置熔丝各自包含非易失性寄存器。

72.在实例7中,实例5和6的任一者或任何组合的主题可任选地经配置以使得初始设置电路包含一或多个延迟设置熔丝以产生所述延迟设置信号,所述一或多个延迟设置熔丝各自为非易失性寄存器。

73.在实例8中,一种微电子装置可包含定时电路、目标电路和初始设置电路。所述定时电路可经配置以接收输入信号且通过将时间延迟应用于所述输入信号而产生输出信号,且可包含延迟级和门级。所述延迟级可经配置以通过将延迟引入到输入信号而产生延迟信号。所述门级可接收延迟信号且使用所述延迟信号和逻辑阈值产生输出信号。所述门级可包含阈值设置电路,所述阈值设置电路经配置以接收阈值设置信号且根据阈值设置输入来设置所述逻辑阈值的初始值。所述目标电路可经配置以接收所述输出信号且使用所述输出信号控制所述微电子装置的操作。所述目标电路具有目标电路温度系数。所述初始设置电路可经配置以提供阈值设置信号。所述定时电路和所述初始设置电路可经配置以允许调谐所述阈值设置信号以用于为时间延迟提供基本上匹配所述目标电路温度系数的定时电路温度系数。

74.在实例9中,实例8的主题可任选地经配置以使得所述延迟级经配置以通过将电阻-电容(rc)延迟引入到所述输入信号来产生所述延迟信号、接收延迟设置信号以及根据所述延迟设置信号设置时间常数的初始值,所述时间常数是rc延迟的量度,且所述初始设置电路另外经配置以提供所述延迟设置信号且允许调谐所述阈值设置信号和延迟设置信号以用于为时间延迟提供定时电路温度系数。

75.在实例10中,实例8和9的任一者或任何组合的主题可任选地经配置以另外包含经配置以存储数据的存储器单元。

76.在实例11中,实例10的主题可任选地经配置以使得存储器单元包含动态随机存取存储器(dram)单元。

77.在实例12中,实例10的主题可任选地经配置以使得存储器单元包含铁电随机存取存储器(feram)单元。

78.在实施例13中,实例9到13中任一者或任何组合的主题可任选地经配置以使得所述初始设置电路包含非易失性寄存器,所述非易失性寄存器经配置以允许在微电子装置的制造期间在测试模式下设置阈值设置信号和延迟设置信号且存储设置的阈值设置信号和设置的延迟设置信号以用于微电子装置的制造后操作。

79.在实例14中,实例8到13中的任一者或任何组合的主题可任选地经配置以使得门级包含阈值设置电路系统,所述阈值设置电路系统包含上拉和下拉晶体管且经配置以根据阈值设置信号设置逻辑阈值。

80.在实例15中,提供一种用于在电子装置中为定时信号提供可调谐温度相依性的方法。所述方法可包含:接收输入信号;通过将延迟引入到所述输入信号来产生延迟信号;以及响应于所述延迟信号越过逻辑阈值而产生切换到不同逻辑电平的输出信号。所述输出信号以某一时间延迟跟随所述输入信号。所述方法还可包含根据阈值设置信号设置逻辑阈值的初始值以及调谐所述阈值设置信号以为时间延迟提供指定温度相依性。

81.在实施例16中,引入实施例15中存在的延迟的主题可任选地包含引入电阻-电容(rc)延迟,且实施例15的主题可另外包含:使用包含电阻和电容的rc延迟电路来提供所述rc延迟以提供作为rc延迟的量度的时间常数,所述电阻或电容中的至少一者是可调整的;根据延迟设置信号设置所述时间常数的初始值;以及调谐所述阈值设置信号和所述延迟设置信号以为时间延迟提供指定温度相依性。

82.在实例17中,实例16的主题可任选地另外包含在制造电子装置期间在测试模式下调谐阈值设置信号和延迟设置信号以及将阈值设置信号和延迟设置信号中的每一者永久地设置成经调谐值以用于所述电子装置的制造后操作。

83.在实例18中,在实例16和17中的任一者或任何组合中存在的调谐阈值设置信号和延迟设置信号的主题可任选地包含:调谐阈值设置信号和延迟设置信号包括熔丝微调。

84.在实例19中,实例18中存在的调谐阈值设置信号和延迟设置信号的主题可任选地包含在测试模式下确定要存储于电子装置中的非易失性寄存器中的数据。

85.在实例20中,在实例16到19中的任一者或任何组合中存在的调谐阈值设置信号和延迟设置信号以为时间延迟提供指定温度相依性的主题可任选地包含从可通过调谐阈值设置信号和延迟设置信号获得的负温度系数和正温度系数中选择时间延迟的温度系数。

86.在实例21中,实例16到20中的任一者或任何组合的主题可任选地另外包含针对接收输出信号的目标电路的过程确定目标温度系数以及指定时间延迟的温度系数的温度相依性以基本上匹配目标温度系数。所述目标电路是所述电子装置的部分。

87.在实例22中,实例15到21中的任一者或任何组合的主题可任选地另外包含使用输出信号控制存储器装置中的感测定时。所述存储器装置是所述电子装置或所述电子装置的部分。

88.以上详细描述包含对附图的参考,所述附图形成详细描述的部分。各图以说明方式展示其中可实践本发明的具体实施例。这些实施例在本文中也称作“实例”。此类实例可包含除了所展示或描述的那些元件之外的元件。然而,本发明人还预期其中仅提供所展示或描述的那些元件的实例。此外,本发明人还预期使用相对于特定实例(或其一或多个方面)或相对于本文展示或描述的其它实例(或其一或多个方面)而展示或描述的那些元件的任何组合或排列的实例(或其一或多个方面)。

89.将理解,当某一元件被称作在另一元件“上”、“连接到”另一元件或与另一元件“耦合”时,所述元件可直接在另一元件上、与另一元件直接连接或耦合,或可存在居间元件。相比而言,当某一元件被称为“直接在另一元件上”、“直接连接到另一元件”或“与另一元件直接耦合”时,不存在居间元件或层。如果两个元件在图中展示为被线连接,则除非另外指明,否则所述两个元件可耦合或直接耦合。

90.以上描述旨在进行说明而非限制。举例来说,上文所描述的实例(或其一或多个方面)可彼此组合使用。例如所属领域的技术人员在查阅以上描述后可使用其它实施例。提供摘要以符合37 c.f.r.

§

1.72(b),从而允许阅读者快速确认技术公开内容的本质。在理解所述摘要将不用于解释或限制权利要求书的范围或意义的情况下提交所述摘要。另外,在以上具体实施方式中,可将各种特征分组在一起以简化本公开。此情况不应解释为期望未要求的公开特征对任何权利要求来说是必不可少的。实际上,发明主题可在于比特定公开实施例的所有特征要少。因此,特此将所附权利要求书并入到具体实施方式中,其中每一权利

要求作为单独实施例而独立存在,且经考虑此类实施例可以各种组合或排列彼此组合。本发明的范围应参考所附权利要求书以及此类权利要求被赋予的等同物的完整范围而确定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。