1.本发明涉及闪存芯片领域,特别涉及一种芯片堆叠封装结构及闪存。

背景技术:

2.当前闪存芯片的堆叠主要采用单排堆叠,io接口以8位/1通道,或16位/2通道为主。这种堆叠方式因为厚度的原因,容量上会受到限制,同时io数量有限,单芯片的读写速度也没有优势。

技术实现要素:

3.本发明的主要目的是提出一种芯片堆叠封装结构及闪存,旨在解决现有的单排堆叠的闪存芯片容量受高度限制的问题。

4.为实现上述目的,本发明提出一种芯片堆叠封装结构,该芯片堆叠封装结构包括基板以及设置在所述基板上的单元芯片,所述基板包括多个信号通道接口,每两个所述单元芯片堆叠设置形成一个芯片对,每个所述芯片对分别与所述基板电连接,并通过信号线分别与一个所述信号通道接口连接;

5.所述芯片堆叠封装结构包括至少两个芯片对,各所述芯片对独立设置在所述基板上;

6.或者,所述芯片对堆叠设置在所述基板上并形成一个芯片组,所述芯片堆叠封装结构包括至少两个芯片组。

7.在一些实施例中,所述芯片堆叠封装结构包括沿所述基板的长度方向并排设置的两个芯片组,每个所述芯片组包括至少两个层叠设置的所述芯片对,每个所述芯片组中的单元芯片自所述基板的表面依次向上堆叠设置。

8.在一些实施例中,所述芯片组中的单元芯片自下至上,依次向所述基板的一侧偏移堆叠,以露出单元芯片的另一侧的上表面;所述芯片组中的单元芯片的所述另一侧的上表面通过导线与基板电连接。

9.在一些实施例中,两个所述芯片组的偏移方向相反,所述基板上对应每个所述芯片组的所述信号通道接口与电源接口位于相应所述芯片组的同侧。

10.在一些实施例中,两个所述芯片组背向彼此偏移,所述电源接口和所述信号通道接口设于所述基板的中心。

11.在一些实施例中,每个所述芯片组分别包括两个芯片对,同一芯片组中的芯片对并行传输数据。

12.在一些实施例中,至少一个所述芯片组还包括设置在两个芯片对之间的垫层,所述垫层为fow垫层。

13.在一些实施例中,所述垫层的偏移方向与其下方的单元芯片的偏移方向相反。

14.在一些实施例中,所述芯片堆叠封装结构包括沿所述基板的宽度方向并排设置的多列芯片组,每列芯片组包括两个所述芯片组,所述基板的宽度方向相邻的两个芯片组上

的单元芯片的偏移方向相同。

15.本发明还提出一种闪存,包括上述的芯片堆叠封装结构。

16.本发明通过在单个封装体内将单元芯片进行多排列并存,每一排再多层堆叠的方式实现单芯片大容量,同时在封装体上采用多io并行传输的方式,实现更快的接口传输速度。

附图说明

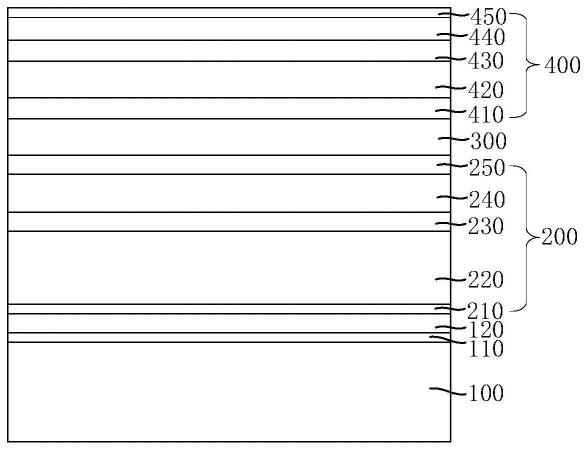

17.图1为本发明芯片堆叠封装结构一实施例的结构示意图;

18.图2为本发明芯片堆叠封装结构另一实施例的结构示意图;

19.图3为本发明芯片堆叠封装结构另一实施例的结构示意图;

20.图4为本发明芯片堆叠封装结构另一实施例的结构示意图;

21.图5为图4实施例中堆叠封装结构的侧视图。

22.本发明目的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

23.下面将结合本发明实施例中的附图,对本发明实施例中的方案进行清楚完整的描述,显然,所描述的实施例仅是本发明中的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

24.需要说明,本发明实施例中所有方向性指示,诸如上、下、左、右、前、后

……

仅用于解释在某一特定姿态,即如附图所示下各部件之间的相对位置关系、运动情况等,如果该特定姿态发生改变时,则该方向性指示也相应地随之改变。

25.还需要说明的是,当元件被称为“固定于”或“设置于”另一个元件上时,它可以直接在另一个元件上或者可能同时存在居中元件。当一个元件被称为是“连接”另一个元件,它可以是直接连接另一个元件或者可能同时存在居中元件。

26.另外,在本发明中涉及“第一”、“第二”等的描述仅用于描述目的,而不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。另外,各个实施例之间的技术方案可以相互结合,但是必须是以本领域普通技术人员能够实现为基础,当技术方案的结合出现相互矛盾或无法实现时应当认为这种技术方案的结合不存在,也不在本发明要求的保护范围之内。

27.本发明还提出一种芯片堆叠封装结构,参照图1至图5,该芯片堆叠封装结构包括基板10以及设置在所述基板10上的至少两个芯片组;所述基板10包括多个信号通道接口,所述芯片组包括至少一个芯片对,所述芯片对由两个单元芯片20堆叠而成;每个所述芯片对分别与所述基板10电连接,并通过信号线分别与一个所述信号通道接口连接。

28.在本实施例中,芯片的堆叠封装结构包括两种方式,其中的一种为在基板10上设置多个单独的芯片对,各芯片对的其中一个单元芯片20贴在基板10上,各芯片组与信号通道接口通过信号线电连接,实现多个芯片对的并行传输信号。每个芯片对的单元芯片20与基板10上的电源接口通过打线电连接。此种封装结构适用于厚度较薄,尺寸较大的芯片规

格。上述芯片对通常设置偶数个,可以在基板10上设置芯片对阵列。

29.另一种封装结构是,在一个芯片组中将多个芯片对进行堆叠,在基板10上设置多个芯片组,每个芯片组最底层的单元芯片20贴合基板10,各芯片对之间并行传输数据。此种封装方式为了控制芯片的厚度,在水平方向设置多个芯片组,使闪存具备更大的数据容量。

30.本发明通过在单个封装体内将单元芯片20进行多排列并存,每一排再多层堆叠的方式实现单芯片大容量。同时在封装体上采用多io并行传输的方式,实现更快的接口传输速度。

31.在一些实施例中,参照图1和图2,所述芯片堆叠封装结构包括沿所述基板10的长度方向并排设置的两个芯片组,每个所述芯片组包括至少两个层叠设置的所述芯片对,每个所述芯片组中的单元芯片20自所述基板10的表面依次向上堆叠设置。

32.在一些实施例中,参照图1和图2,所述芯片组中的单元芯片20自下至上,依次向所述基板10的一侧偏移堆叠,以露出单元芯片20的另一侧的上表面;所述芯片组中的单元芯片20的所述另一侧的上表面通过导线与基板10电连接。

33.在本实施例中,所述芯片堆叠封装结构包括并排设置的两个芯片组,两所述芯片组分别为第一芯片组和第二芯片组,所述芯片组中的单元芯片20自所述基板10的表面依次向上堆叠设置。所述第一芯片组中的单元芯片20自下至上,依次向一侧偏移堆叠,以形成第一偏移侧;所述第一芯片组中的单元芯片20远离所述第一偏移侧的一端通过所述导线与基板10电连接;所述第二芯片组中的单元芯片20自下至上,依次向一侧偏移堆叠,以形成第二偏移侧;所述第二芯片组中的单元芯片20远离所述第二偏移侧的一端通过所述导线与基板10电连接。

34.在一些实施例中,参照图1和图2,两个所述芯片组的偏移方向相反,所述基板10上对应每个所述芯片组的所述信号通道接口与电源接口位于相应所述芯片组的同侧。在本实施例中,第一芯片组和第二芯片组并排设置,第一芯片组位于第二芯片组的左侧,第一芯片组向右偏移,第二芯片组向左偏移。基板10上与第一芯片组对应的信号通道接口以及电源接口位于第一芯片组的左侧;对应的,基板10上与第二芯片组对应的信号通道接口以及电源接口位于第二芯片组的右侧,上述芯片组与信号通道接口以及电源接口通过打线连接。

35.在一些实施例中,参照图1和图2,两个所述芯片组背向彼此偏移,所述电源接口和所述信号通道接口设于所述基板10的中心。在本实施例中,可设置8个单元芯片20,即die1-die8。其中,die1-die4构成一个芯片组,die5-die8构成另一个芯片组,二者并排设置,die1-die4位于die5-die8的左侧。die1-die4中的单元芯片20自下至上向左偏移;die5-die8中的单元芯片20自下至上向右偏移;由此上述信号通道接口和电源接口位于两个芯片组之间,并处于基板10的中心。

36.在一些实施例中,参照图1至图2,每个所述芯片组分别包括两个芯片对,同一芯片组中的芯片对并行传输数据。其中die1和die2与信号通道接口电连接,die1和die2作为第一通道的连接芯片,die3和die4也与信号通道接口电连接,die3和die4作为第三通道的连接芯片。die1/2与die3/4可并行传输数据。其中die5和die6连接第二通道,die7和die8连接第四通道。

37.在本实施例中,一个die上有8根数据线,这8数据线就组成一个与数据线连接的信号通道;如果现在有两个通道,但是有4个die,那么一个通道就使用两个die,这两个die数

据线相连。其中8根数据线与信号线组成一个通道,另外8根数据线与信号线组成一个通道,这两个通道互不干扰,可以一起传输数据。

38.在一些实施例中,参照图3,至少一个所述芯片组还包括设置在两个芯片对之间的垫层,所述垫层为fow垫层。所述第一芯片组还包括设置在两个芯片对之间的第一垫层,所述第二芯片组还包括设置在两个芯片对之间的第二垫层,所述第一垫层和第二垫层为fow垫层。所述第一垫层的偏移方向与第一偏移方向相反,所述第二垫层的偏移方向与第二偏移方向相反。例如,第一垫层与上方的单元芯片20对齐,即第一垫层与上方的单元芯片20可以不相对于第一垫层偏移。

39.在本实施例中,fow(film on wire)工艺,是指可以把线埋起来。相对图2左边的堆叠的方式来说,第三层die可以不用往后阶梯堆叠,而是用fow把第二层的线埋起来,第三层贴在fow上,由此第三层第四层不会导致封装尺寸变大。

40.在一些实施例中,所述芯片堆叠封装结构包括沿所述基板10的宽度方向并排设置的多列芯片组,每列芯片组包括两个所述芯片组,所述基板10的宽度方向相邻的两个芯片组上的单元芯片20的偏移方向相同。

41.在本实施例中,参照图4和图5,所述芯片堆叠封装结构包括四个芯片对,各所述芯片对呈阵列设置在所述基板10上。四个芯片对呈两行两列排布,die1和die2连接第一通道,die3和die4连接第三通道,die5和die6连接第二通道;die7和die8连接第四通道。也可以是更多列,不限于4个,每列设置2个芯片对,横向两个芯片对中单元的偏移一致,纵向的两个相反。

42.本发明还提出一种闪存,包括上述的芯片堆叠封装结构。本发明通过在单个封装体内将单元芯片20进行多排列并存,每一排再多层堆叠的方式实现单芯片大容量。同时在封装体上采用多io并行传输的方式,实现更快的接口传输速度。

43.以上所述的仅为本发明的部分或优选实施例,无论是文字还是附图都不能因此限制本发明保护的范围,凡是在与本发明一个整体的构思下,利用本发明说明书及附图内容所作的等效结构变换,或直接/间接运用在其他相关的技术领域均包括在本发明保护的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。