金属镀覆的玻璃通孔的钝化材料和方法

1.相关申请

2.本技术是2020年6月10日提交的美国申请no.16/897,788的继续申请。上述申请的全部教导通过引用并入本文。

背景技术:

3.玻璃,例如熔融sio2,是适用于高频电气技术的有前景的基板材料。这些技术包括例如毫米波器件,例如射频(rf)集成电路(ic)和微机电系统(mems)。玻璃作为基板材料是有利的,因为它与硅(si)、陶瓷和有机层压板等常规基板材料相比具有独特的优势。玻璃不仅提供卓越的rf性能(例如,在超高频和极高频(shf和ehf)下的高电气隔离、低插入损耗(insertion loss)以及低损耗正切(loss tangent)),而且提供优异的尺寸和热稳定性(例如,可调节的热膨胀系数(cte)、有效的防潮层以及非常薄的ic和mems封装)。

4.对于2.5维(2.5d)和3维(3d)ic和mems,电信号可通过称为硅通孔(tsv)的垂直导电路径传输,该路径完全穿过一个或多个单独的基板和/或中介层(interposer)以互连多个ic芯片。这种平面外电连接也可以在硅酸盐玻璃基板中实现,方法是钻一个横截面直径相对于深度变化(例如,1-100μm)的通孔(through-hole via),从而形成通过硅酸盐玻璃基板的沙漏形通孔。

5.沙漏形孔可以例如使用激光加工技术来构造。图1a示出了在硅酸盐玻璃基板104中形成的示例玻璃通孔(tgv)102的横截面视图。在tgv 102的最窄点106处,直径可以为约10μm,尽管该最窄点106处的直径可以小至1μm且大至100μm。tgv外表面直径108可以为约50μm,尽管外表面直径108可以小至1μm且大至100μm。硅酸盐玻璃基板104的厚度110可以为约300μm,尽管厚度110可以小至100μm且大至1000μm。

6.tgv 102的内表面112可以使用本领域已知的一种或多种常规电镀技术涂覆有一层或多层金属,以形成金属镀覆或金属填充的tgv。如图1b中所示的示例tgv所示,这些金属层可以包括薄的粘附层120(例如,钛(ti))、设置在粘附层120上的金属种子层122以及设置在种子层(seed layer)122上的金属镀层124。金属镀层124可以包括导电材料,例如铜(cu)或铝(al)。

7.沿着水平导电路径(例如,包含金(au)的图案化金属化层)布线的电信号可以电联接到金属填充的tgv。在制造过程中,金属镀覆的tgv的金属镀层124可暴露于以高浓度氧气(o2)为特征的环境条件。金属镀层124的一些原子可沿着设置在金属镀层124上的图案化金属化层的晶界扩散并遇到o2。o2可容易地与暴露的非惰性金属原子例如与cu在高于100℃的温度下反应,产生不稳定的金属氧化物副产物,例如氧化铜(cuo或cu2o)。由此产生的金属氧化物副产物可能会降低相关器件的性能、可靠性、寿命和封装完整性。图2a和2b中所示的扫描电子显微照片(sem)呈现了在au表面204上产生的主要由cuo或cu2o组成的这种微米和纳米级颗粒206。由于cu原子通过图案化金属化层的扩散,颗粒206在tgv 202附近的区域产生。

8.为了防止图2a和2b中所示的金属镀层124的原子扩散以及由此产生的污染,可以

在金属镀层124和图案化金属化层之间设置阻挡层。由于硅通孔的物理尺寸较小(相对于tgv),用常规技术配置这种阻挡层是可行的。例如,硅基制造技术可使用诸如氮化钛(tin)或氮化钽(tan)等扩散阻挡层(diffusion barrier),其使用化学气相沉积(cvd)或物理气相沉积(pvd)或原子层沉积(ald)工艺来沉积。这种tin或tan阻挡层(barrier)通常非常薄(小于10nm),但薄度不是问题,因为缩放的tsv的尺寸相对较小(例如,直径小于5μm)。

9.然而,由于tgv的尺寸相对较大,使用这种常规技术完全配置这种阻挡层可能存在问题。例如,使用常规制造技术(例如pvd)在与本文所述的大尺寸沙漏形tgv相关的3d拓扑结构上放置阻挡膜可导致不完整的阻挡密封。这种不完整的密封可允许原子从金属镀层扩散到图案化金属化层。

技术实现要素:

10.本文所述的实施方式涉及与金属化玻璃通孔(tgv)相关的钝化(或阻挡)层及其制造方法。理想地,设置在tgv的金属镀层和外部金属化层之间的中间层可以用作金属镀层的原子迁移到外部金属化层的阻挡层。例如,图3中所示的金属镀层124和外部金属化层304之间的中间层302可用于防止来自金属镀层的原子扩散到外部金属化层304。沙漏形tgv的3d拓扑结构和大空间尺寸(相对于tsv)对在tgv内建立完整的阻挡层造成了障碍。本领域已知的薄膜沉积技术(例如pvd)通常产生保形膜,但这种薄保形膜沉积技术可能导致3d类型的不完全填充,例如图1a、图1b和图3中所示的大尺寸沙漏形tgv。3d拓扑结构中未被阻挡膜覆盖的任何区域都可为金属扩散提供路径。

11.根据所述实施方式,氧化物基和氮化物基薄膜,例如二氧化硅(sio2)和氮化钛(tin),可以有效地用作扩散阻挡层以阻挡金属扩散和随后的o2相互作用。这种阻挡层可以用常规沉积技术(例如cvd、pvd和ald)沉积在金属化tgv基板的表面上,并用标准光刻和蚀刻工艺进行图案化。

12.在一个方面,本发明可以是在形成于玻璃基板中的金属化玻璃通孔(tgv)上设置阻挡膜的方法,该方法包括使用原子层沉积(ald)工序在金属化tgv的金属镀层上建立金属氮化物膜,以及在金属氮化物膜上形成导电金属化层。导电金属化层可以电联接到金属氮化物膜。

13.该方法还可以包括将导电金属氮化物膜配制成包含氮化钛(tin)。该方法还可以包括将外部金属化层电联接到导电金属氮化物膜。该方法还可以包括在导电金属氮化物膜上沉积一个或多个导电涂层(conductive coatings)。一个或多个导电涂层包含tiw和/或au。

14.在另一方面,本发明可以是在形成于玻璃基板中的金属化玻璃通孔(tgv)上设置阻挡膜的方法,该方法包括使用物理气相沉积(pvd)工序(i)在金属化tgv的金属镀层上和(ii)在tgv周围的至少部分玻璃上建立金属膜。该方法还可以包括使用化学气相沉积(cvd)工序在金属膜上建立电绝缘膜。电绝缘膜可以与金属镀层完全重叠并且与金属膜部分重叠。该方法还可以包括使用pvd工序在绝缘膜上和在金属膜上形成导电金属化层。导电金属化层可以电联接到金属膜。

15.该方法还可以包括将导电金属膜制备成包含钛钨(tiw)。该方法还可以包括将绝缘膜制备成包含二氧化硅(sio2)。该方法还可以包括对绝缘膜进行图案化以形成扩散阻挡

补片(diffusion barrier patch),该扩散阻挡补片至少覆盖导电金属膜的铺在tgv上面的区域。该方法还可以包括对绝缘膜进行延伸,使得扩散阻挡补片覆盖tgv周围的至少部分玻璃。

16.该方法还可以包括将外部金属化层电联接到导电金属膜。该方法还可以包括在导电金属氮化物膜上沉积一个或多个导电涂层。一个或多个导电涂层包含tiw和/或au。

17.在另一方面,本发明可以是在玻璃基板中形成的玻璃通孔(tgv),其包括在tgv中形成的金属镀层。tgv可以具有通过玻璃基板的三维(3d)拓扑结构和保形地覆盖3d拓扑结构的金属镀层。tgv还可以包括设置在金属镀层上的阻挡层和设置在阻挡层上的导电金属化层。导电金属化层可以通过阻挡层电联接到金属镀层。

18.阻挡层还可以包括设置在金属镀层上的金属氮化物膜,金属氮化物层电联接到导电金属化层。金属氮化物膜可以是氮化钛(tin)。

19.阻挡层还可以包括(i)设置在金属镀层上和tgv周围的至少部分玻璃上的金属膜,以及(ii)设置在金属膜上的电绝缘膜。电绝缘膜可以与金属镀层完全重叠并且与金属膜部分重叠。金属膜可以电联接到导电金属化层。金属膜可以是钛钨(tiw),电绝缘膜可以是二氧化硅(sio2)。tgv还可以包括在导电金属化层上的一个或多个导电涂层。一个或多个导电涂层可以包含tiw和/或au。

附图说明

20.从以下示例实施方式的更具体描述中,前述内容将显而易见,如附图所示,其中类似的参考字符在不同视图中指代相同的部分。附图不必按比例绘制,而是将重点放在例示性实施方式上。

21.图1a示出了在硅酸盐玻璃基板中形成的示例玻璃通孔(tgv)的横截面视图。

22.图1b示出了图1a的tgv,其具有薄的粘附层、设置在粘附层上的金属种子层和设置在种子层上的金属镀层。

23.图2a和2b示出了扫描电子显微照片(sem),其描绘了tgv的au表面上的微米和纳米级颗粒。

24.图3示出了在玻璃基板的顶表面和/或底表面上沉积有金属膜的示例tgv。

25.图4示出了本发明的tgv上配置的钝化层的一个实施方式。

26.图5示出了本发明的tgv上配置的钝化层的另一个实施方式。

27.图6a和6b示出了用本发明的钝化层制造的tgv的示例。

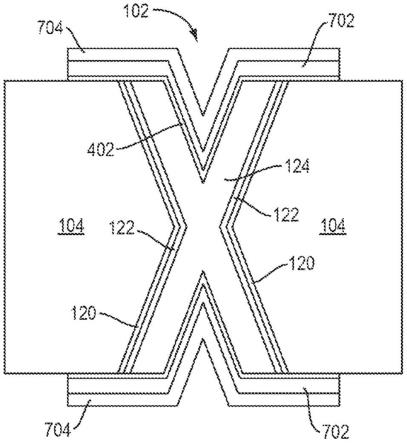

28.图7示出了图4的钝化tgv的实施方式,其具有用作导电互连路径和/或ic和mems封装中使用的密封环的附加金属涂层。

29.图8示出了图5的钝化tgv的实施方式,其具有用作导电互连路径和/或ic和mems封装中使用的密封环的附加金属涂层。

具体实施方式

30.示例实施方式的描述如下。

31.本文引用的所有专利、公开申请和参考文献的教导通过引用整体并入本文。

32.本文所述的实施方式涉及与金属化玻璃通孔(tgv)相关的钝化(或阻挡)层。如本

文所述,图1b示出了内衬有粘附层120、金属种子层122和金属镀层124的示例沙漏形tgv。该示例tgv在图3中示出,其中使用例如物理气相沉积(pvd)技术在玻璃基板的顶表面和/或底表面上沉积一个或多个金属膜。对于图3中示出的示例,钛钨(tiw)的第一金属层302沉积在金属镀层124上,并且金(au)的第二金属层304设置在第一金属层302上。外部金属化层304不仅可以用作芯片到芯片互连的导电路径,而且在使用晶圆键合技术(例如,通过热压键合)接合器件和盖基板时用作键合垫(bond pad)或密封环。对于与对置基板(counter substrate)的au密封环的热压键合,需要不含外来颗粒(foreign particles)的清洁au键合垫以实现牢固的au到au键合,从而实现气密密封。对金属填充的tgv进行适当的表面钝化可以减少或防止金属扩散和与o2的相互作用,从而防止不必要的金属氧化物颗粒形成。

33.所述实施方式允许显著减少在基板上产生的寄生金属氧化物。具体而言,具有金属填充的tgv的硅酸盐玻璃晶圆的表面涂覆有钝化层。此外,所述实施方式促使将钝化层设置在本文所述的tgv类型的非平面、3维(3d)形貌上。在某些应用中,tgv需要输送大量的电力,并且在物理上必须比典型的tgv大。所述实施方式促使完全覆盖tgv,以防止潜在的扩散路径。

34.在一个实施例中,如图4所示,钝化层包括使用本领域已知的原子层沉积(ald)方法沉积的导电金属氮化物膜402。在示例实施方式中,金属氮化物膜402包括氮化钛(tin),尽管在其他实施方式中可替代地使用其他金属氮化物材料,例如氮化钽(tan)。ald处理促使金属氮化物膜402在tgv的3d形貌内完全保形沉积。

35.在另一个实施方式中,钝化层可包括两个平行层,包括通过化学气相沉积(cvd)沉积在金属膜502(例如,钛钨(tiw))的表面上的绝缘氧化物基膜504,该金属膜502通过pvd沉积在金属镀层124上,如图5所示。在本文所述的示例实施方式中,绝缘氧化物基膜504包括二氧化硅(sio2),尽管可替代地使用本领域已知的其他绝缘氧化物基材料,例如无定形氧化铝(al2o3)。在本文所述的示例实施方式中,金属膜502包括钛钨(tiw),尽管在替代实施方式中,金属膜502可包括通过pvd沉积的其他过渡金属,例如钛(ti)和铬(cr),或者通过pvd沉积的过渡金属合金,例如tin和tan。

36.绝缘氧化物基膜504可以被图案化以在金属填充的tgv(即,金属镀层124)上形成扩散阻挡补片506,从而将下层金属膜502暴露在扩散阻挡补片的外部,如图5所示。该氧化物补片可以有效地用作阻碍金属-o2扩散和反应的阻挡层。

37.图6a和6b中所示的光学显微照片表明,金属氧化物颗粒在sio2/tiw扩散阻挡补片506的存在下基本消失,而图2a和2b中的那些显示,在没有钝化层的情况下,au表面上普遍存在氧化铜颗粒。

38.一个或多个额外金属涂层(例如,au和tiw)可以应用在通过关于图4和5所描述的任一技术实现的钝化层的顶部。附加金属涂层可以通过pvd沉积,然后通过标准光刻和蚀刻技术与钝化层一起进行图案化。在对应于图4所示的实施方式的图7所示的示例实施方式中,下层tin膜402上的附加金属涂层包括tiw膜702和au膜704。在对应于图5所示的实施方式的图8所示的示例实施方式中,在sio2/tiw扩散阻挡补片506外部的下层tiw膜502上的附加金属涂层同样包括tiw膜802和au膜804。附加金属涂层702、704、802、804可用于定义芯片到芯片互连的导电路径以及ic和mems封装中使用的键合垫和/或密封环。

39.在所述实施方式中,已经提出了金属氮化物和氧化物基薄膜,例如tin和sio2,以

对金属填充的tgv的表面进行钝化。金属氮化物和氧化物基薄膜可以用作有效的扩散阻挡层,并且可以抑制金属镀层内的非惰性金属原子扩散通过金属化层并因此与o2相遇并反应,从而能够制造出不含不期望的金属氧化物微米和纳米颗粒的清洁硅酸盐玻璃基板表面。金属氮化物和氧化物基薄膜可以用常规沉积方法(例如cvd、pvd和ald)容易地沉积到金属化tgv晶圆的表面,并且用标准光刻和蚀刻技术容易地进行图案化。

40.所述实施方式展示了在3维、2.5维和2维(分别为3d、2.5d和2d)ic和mems中应用的巨大潜力,这些ic和mems需要硅酸盐玻璃封装以获得优异的电气隔离、rf性能、光学透明度和结构柔性(flexibility)。

41.虽然已经具体示出并描述了示例实施方式,但本领域技术人员将理解,在不脱离所附权利要求书所涵盖的实施方式的范围的情况下,可以在其中对形式和细节进行各种改变。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。