1.实施例涉及一种电路板,并且更具体地,涉及一种能够使用阻焊剂在开口区域中支撑和保护最外层的电路图案的电路板及其制造方法。

背景技术:

2.随着电子组件的小型化、重量减少和集成化的加速,电路的线宽已经变得精细。特别地,因为半导体芯片的设计规则在纳米尺度上被集成,所以封装基板或安装有半导体芯片的印刷电路板的电路线宽已使精细到数微米或更小。

3.为了增加印刷电路板的电路集成度,即,减小电路线宽,已经提出了各种方法。为了防止在镀铜后形成图案的蚀刻步骤中电路线宽的损耗,已经提出了半加成工艺(sap)方法和改进的半加成工艺(msap)。

4.然后,在工业中已经使用了用于在绝缘层中嵌入铜箔以便于实现精细电路图案的嵌入式迹线基板(以下称为“ets”)方法。在ets方法中,代替在绝缘层表面上形成铜箔电路,将铜箔电路以嵌入形式制造在绝缘层中,并且因此不会由于蚀刻而造成电路损耗并且对于使电路节距精细是有利的。

5.同时,最近,为了满足对无线数据业务的需求,已经努力开发改进的5g(第5代)通信系统或前5g通信系统。在这里,5g通信系统使用超高频(毫米波)带(亚6ghz、28ghz、38ghz或更高频率)来实现高数据传输速率。

6.另外,为了减少无线电波的路径损耗并且增加无线电波在超高频带的传输距离,在5g通信系统中,已经开发了诸如波束成形、大规模多输入多输出(大规模mimo)、以及阵列天线的集成技术。考虑到它可能由频带中的数百个波长的有源天线组成,天线系统变得相对大。

7.因为这种天线和ap模块被图案化或安装在印刷电路板上,所以印刷电路板上的低损耗是非常重要的。这意味着组成有源天线系统的数个基板,即,天线基板、天线馈电基板、收发器基板和基带基板,应被集成到一个紧凑的单元中。

8.另外,上述应用于5g通信系统的电路板在制造中呈现轻薄紧凑的趋势,并且相应地,电路图案也变得逐渐地精细。

9.然而,包括传统精细电路图案的电路板具有其中设置在最外部处的电路图案在绝缘层的上方突出的结构,并且因此存在最外部的电路图案容易塌陷的问题。

技术实现要素:

10.技术问题

11.实施例提供了一种具有新结构的电路板及其制造方法。

12.此外,实施例提供一种能够使用阻焊剂支撑和保护sr开口区域中包括的最外电路图案的电路板及其制造方法。

13.此外,在实施例中,提供了一种包括通过执行阻焊剂的逐步曝光和显影工艺而具

有对每个区域具有不同高度的分层结构的阻焊剂的电路板以及制造方法。

14.提出的实施例要解决的技术问题不限于在上面提及的技术问题,并且其他未提及的技术问题可以通过以下描述提出的实施例所属的本领域的技术人员清楚地理解。

15.技术方案

16.根据实施例的电路板包括:绝缘层,其包括第一至第三区域;外层电路图案,其设置在绝缘层的第一至第三区域的上表面上;以及阻焊剂,其包括设置在绝缘层的第一区域中的第一部(part)、设置在绝缘层的第二区域中的第二部以及设置在绝缘层的第三区域中的第三部,其中该外层电路图案具有第一高度,阻焊剂的第三部被设置在外层电路图案的上表面上以具有第二高度,第一区域包括第一子区域和第二子区域,第一部包括设置在第一子区域中的第一子部和设置在第二子区域中的第二子部,第一子部的上表面被定位为高于外层电路图案的上表面并且低于第三部的上表面,第二子部的上表面被定位为低于外层电路图案的上表面,并且阻焊剂的第三部的表面粗糙度不同于阻焊剂的第一部的表面粗糙度。

17.此外,第一子区域是外层电路图案之中设置有迹线的区域,并且第二子区域是外层电路图案之中设置有第一焊盘的区域。

18.此外,第二区域是外层电路图案之中设置有第二焊盘的区域,并且第二焊盘的宽度大于第一焊盘的宽度。

19.此外,第二子部被设置为与第一焊盘的至少一个外表面接触。

20.此外,第二子部包括设置在第一焊盘的第一外表面上的第一部分(portion)和设置在第一焊盘的与第一外表面相对的第二外表面上的第二部分,第一部分的宽度等于第二部分的宽度,并且第一部分或第二部分的宽度处于10μm至12μm的范围内。

21.此外,第二子部包括设置在第一焊盘的第一外表面上的第一部分和设置在第一焊盘的与第一外表面相对的第二外表面上的第二部分,第一部分的宽度不同于第二部分的宽度,并且第一部和第二部的宽度之和处于20μm至24μm的范围内。

22.此外,第二子部包括设置在第一焊盘的第一外表面上的第一部分,第一焊盘的与第一外表面相对的第二外表面与第一子部直接接触,并且第一部分的宽度处于20μm至24μm的范围内。

23.此外,第二子部的高度满足第一焊盘的高度的70%至90%的范围。

24.此外,从外层电路图案突出的第三部的第二高度满足7μm至17μm的范围。

25.此外,阻焊剂的第三部被设置在第二焊盘的上表面上以具有第二高度并且包括暴露第二焊盘的上表面的开口,并且开口的宽度小于第二焊盘的宽度。

26.此外,第一子部或第二子部的上表面的中心线表面粗糙度ra大于第三部的上表面的中心线表面粗糙度ra。

27.此外,第一区域和第二区域是阻焊剂的开口区域。

28.此外,绝缘层包括多个绝缘层,外层电路图案被设置为在多个绝缘层之中的最上绝缘层的上表面上突出,并且电路板包括底漆层(primer layer),其设置在最上绝缘层、外层电路图案和阻焊剂之间。

29.同时,根据实施例的制造电路板的方法包括:制造内层基板,在内层基板上形成在其上表面上设置有底漆层的最上绝缘层,在最上绝缘层的底漆层上形成外层电路图案,在

底漆层上形成覆盖外层电路图案并且划分为第一区域、第二区域和第三区域的阻焊剂,初次曝光排除第一区域和第二区域的开口的阻焊剂的区域,对第一区域和排除初次曝光区域的开口进行初次显影,对初次显影的第一区域的第一子区域进行二次曝光,以及对第一区域的第二子区域和排除二次曝光的区域的开口进行二次显影,其中阻焊剂包括设置在第一子区域中的第一子部、设置在第二子区域中的第二子部、设置在第二区域中的第二部、以及设置在第三区域中的第三部,外层线路图案具有第一高度,阻焊剂的第三部被设置为在外层电路图案的上表面的上方具有第二高度,第一子部的上表面被设置为高于外层电路图案的上表面并且低于第三子部的上表面,第二子部的上表面低于外层电路图案的上表面,并且阻焊剂的第三部的表面粗糙度不同于阻焊剂的第一部的表面粗糙度。

30.此外,第一子区域是外层电路图案之中设置有迹线的区域,第二子区域是外层电路图案之中设置有第一焊盘的区域,并且第二区域是在外层电路图案之中设置第二焊盘的区域,第二焊盘的宽度大于第一焊盘的宽度,第一焊盘包括其上安装有器件的安装焊盘,并且第二焊盘包括bga焊盘或核心焊盘。

31.此外,第二子部被设置为与第一焊盘的至少一个外表面接触,第二子区域的宽度大于第一焊盘的宽度,并且第二子区域的宽度具有20μm至24μm的范围。

32.此外,第二子部的高度满足第一焊盘的高度的70%至90%的范围。

33.此外,阻焊剂的第三部被设置在第二焊盘的上表面上以具有第二高度并且包括暴露第二焊盘的上表面的开口,并且开口的宽度小于第二焊盘的宽度。

34.此外,第一子部或第二子部的上表面的中心线表面粗糙度ra大于第三部的上表面的中心线表面粗糙度ra。

35.有益效果

36.实施例中的电路板是具有带有8层或者更多层的多层结构的电路板,并且包括外层电路图案,该外层电路图案被设置在多层之中的最上部处被定位的外绝缘层上并且在外绝缘层的表面上方突出。在这种情况下,外层电路图案包括在未设置阻焊剂的第一区域和第二区域中定位的第一外层电路图案和在设置阻焊剂的第三区域中定位的第二外层电路图案。在这种情况下,第二外层电路图案可以由阻焊剂支撑和保护,但是第一外层电路图案不具有能够支撑第一外层电路图案的支撑层,并且因此存在由于各种因素而导致第一外层电路图案可能容易塌陷的问题。

37.因此,在实施例中,第一区域和第二区域中的阻焊剂没有被完全去除并且保留,从而由阻焊剂支撑和保护第一外层电路图案。因此,在实施例中,可以通过使外层电路图案精细化来解决诸如第一区域和第二区域的第一外层电路图案的塌陷或摩擦的问题,从而改进产品可靠性。特别地,在实施例中,能够解决诸如第一区域的第一外层电路图案中包括的迹线的塌陷或摩擦的问题,从而改进产品的可靠性。

38.同时,根据实施例的阻焊剂包括设置在第一区域中的第一部、设置在第二区域中的第二部和设置在第三区域中的第三部。此外,第二部可以具有开口并且具有与第三部相同的高度。此外,第一部包括具有的高度低于第二部和第三部的高度的第一子部和具有的高度低于第一子部的高度的子部。第一子部可以被形成为覆盖设置在第一区域中的第一外层电路图案的迹线的表面。此外,第二子部可以具有比第一焊盘的高度低的高度,同时暴露第一区域中设置的第一外层电路图案的第一焊盘的表面。也就是说,在实施例中,通过在两

个步骤中对阻焊剂进行曝光和显影来形成第一子部、第二子部、第二部和第三部。因此,在实施例中,可以改进曝光的分辨率。另外,在实施例中,可以通过第一区域的第一子部稳定地保护迹线的表面,从而改进产品的可靠性。

39.另外,在实施例中,绝缘层的表面和底漆层的表面都具有由阻焊剂覆盖的结构,并且因此,能够解决由于绝缘层的表面或底漆层的一部分的曝光而引起的可靠性问题。详细地,绝缘层的表面或底漆层的部分的曝光指的是外层电路图案与阻焊剂之间存在特定空间。另外,当存在特定空间时,在该空间中保留诸如粘附构件的残留溶液,或者由于该残留溶液而产生空隙(void),从而导致可靠性的问题。另一方面,在实施例中,可以用阻焊剂填充空间,从而解决可靠性问题。

40.另外,在实施例中,阻焊剂的第二子部被设置在第一焊盘的周围,并且第一子部被设置在第二子部的周围。此外,第一子部可以防止要设置在第一焊盘上的粘合构件(例如,焊球)的移动。也就是说,第一子部用作能够固定粘合构件的位置的屏障(dam)。因此,在实施例中,能够解决诸如由粘合构件的一部分向下流而引起的短路的可靠性问题。

41.此外,在实施例中,在去除阻焊剂时,使用曝光和显影方法来代替喷砂或等离子体方法。在这种情况下,当通过喷砂或等离子体法去除阻焊剂时,外层电路图案的变形可能发生,并且在一些情况下,外层电路图案的横截面可能具有三角形形状。此外,当外层电路图案的横截面为三角形形状时,粘合构件可能无法稳定地设置在外层电路图案上,从而导致可靠性问题。相反,在实施例中,可以在不使外层电路图案变形的情况下去除阻焊剂,从而改进可靠性。

42.另外,实施例中的电路板可以被应用于5g通信系统,并且因此,能够最小化高频的传输损耗,从而进一步改进可靠性。具体地,实施例中的电路板能够在高频处使用并且能够减少波损耗。

附图说明

43.图1是示出根据比较示例的通过sap方法制造的电路板的视图。

44.图2是示出在比较示例中通过ets方法制造的电路板的视图。

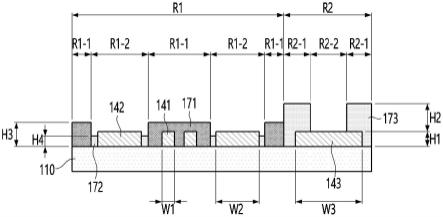

45.图3是示出根据实施例的电路板的视图。

46.图4是图3的区域b的放大图。

47.图5是根据实施例的第二子部的放大图。

48.图6a是用于描述根据实施例的第二子部的第一移位的视图。

49.图6b是用于描述根据实施例的第二子部的第二移位的视图。

50.图7是用于描述根据实施例和比较示例的阻焊剂结构的可靠性的视图。

51.图8是用于描述根据实施例的用于阻焊剂的每个部的表面粗糙度的视图。

52.图9至图19是示出按照工艺顺序制造在图3中所示的电路板的方法的视图。

具体实施方式

53.在下文中,将参考附图详细描述在本说明书中公开的实施例,但是无论附图标记如何,相同或相似的部件由相同的附图标记指定,并且将省略对其的重复描述。以下描述中使用的组件后缀“模块”和“部分”只是考虑到创建规范的容易程度而给出或混合在一起,并

且它们本身没有相互区分的含义或角色。此外,在描述本说明书中公开的实施例时,当确定相关公知技术的详细描述不必要地模糊本说明书中公开的实施例的主旨时,将省略其详细描述。进一步地,附图仅是为了便于理解本说明书所公开的实施例,本说明书所公开的技术范围不受附图的限制,并且应理解为包括落入在本发明的精神和范围内的所有修改、等效物和替代物。

54.将会理解,尽管术语“第一”、“第二”等可以在本文中用于描述各种元件,但是这些元件不应受这些术语的限制。这些术语仅用于区分一个元件与另一个元件。

55.将会理解,当元件被称为“连接”或“耦合”到另一个元件时,它能够被直接连接或耦合到另一个元件或者可以存在中间元件。相反,当元件被称为“直接连接”或“直接耦合”到另一个元件时,将理解不存在中间元件。

56.如本文所用,单数表达包括复数表达,除非上下文另有明确指示。

57.将会理解,术语“包括”、“包括”或“具有”指定在本说明书中公开的所述特征、整数、步骤、操作、元件、组件和/或组的存在,但是不排除存在或添加其一个或多个其他特征、整数、步骤、操作、元件、组件和/或组的可能性。

58.在下文中,将参考附图详细描述本发明的实施例。

59.在描述本实施例之前,将会描述与本实施例进行比较的比较示例。

60.图1是示出根据比较示例的电路板的视图。

61.参考图1a,根据比较示例的电路板包括通过一般sap方法制造的电路图案。

62.具体地,电路板包括绝缘层10、电路图案20和保护层30。

63.电路图案20分别被设置在绝缘层10的上表面和下表面上。

64.在这种情况下,设置在绝缘层10的表面上的至少一个电路图案20包括精细电路图案。

65.在图1中,设置在绝缘层10的上表面上的电路图案20包括精细电路图案。精细电路图案包括作为信号传输布线线路的迹线21和用于安装芯片等的焊盘22。

66.在这种情况下,在实施例中,因为形成使用阻焊剂的支撑层以保护精细电路图案,所以将描述比较示例中的形成精细电路图案的区域中的结构。

67.此外,用于保护电路图案20的保护层30被设置在绝缘层10的表面上。

68.在这种情况下,绝缘层10的上部区域包括设置有保护层30的第一区域和作为未设置有保护层30的开口区域的第二区域。

69.因此,绝缘层10的上表面上设置的电路图案20的一部分由保护层30覆盖,并且剩余部分被暴露于外部而不由保护层30覆盖。

70.在这种情况下,对应于上述精细电路图案的迹线21和焊盘22被设置在作为保护层30的开口区域的第二区域中。

71.例如,以15μm/15μm或更小的宽度/间隔形成迹线21和焊盘22中的至少一个。

72.在这种情况下,当保护层30的开口区域中形成的电路图案是具有超过15μm的宽度的图案而不是精细电路图案时,电路图案可以坚强抵抗外部冲击。

73.然而,如图1b中所示,随着电路图案逐渐变得精细,作为最外层的精细电路图案的迹线21和焊盘22的宽度和间隔逐渐减小,并且因此,当在绝缘层10的上表面上方突出的精细电路图案被设置在作为保护层的开口区域的第二区域中时,存在精细电路图案容易因外

部冲击而崩塌的问题。

74.即,如图1b的b中所示,与最外层的精细电路图案相对应的迹线21具有极其精细图案形状,并且因此即使具有小的外部冲击也会出现容易塌陷或摩擦的问题。

75.同时,最近,通过使用ets方法形成设置在保护层的开口区域中同时具有掩埋在绝缘层中的结构的精细电路图案。

76.图2是示出在比较示例中通过ets方法制造的电路板的视图。

77.参考图2,具体而言,电路板包括绝缘层10a、电路图案20a和保护层30a。

78.电路图案20a分别被设置在绝缘层10a的上表面和下表面上。

79.在这种情况下,设置在绝缘层10a的表面上的电路图案20a中的至少一个包括精细电路图案。

80.这里,当通过ets方法形成电路图案时,首先形成的电路图案具有掩埋在绝缘层10a中的结构。因此,当最初形成的电路图案被形成为精细电路图案时,即使在比较示例中,精细电路图案也可以具有其中精细电路图案被掩埋在绝缘层10a中的结构。

81.也就是说,通过ets方法制造的电路板包括具有掩埋在绝缘层10a的表面中的结构的精细电路图案。即,精细电路图案包括作为信号传输布线线路的迹线21a和用于安装芯片等的焊盘22a。

82.此外,当通过上述ets方法制造电路板时,因为精细电路图案具有掩埋在绝缘层中的结构,所以可以保护精细电路图案免受外部冲击。

83.在这种情况下,对于具有如图2中的两层结构(基于电路图案的层数)的基板,不存在通过ets方法制造电路板的主要问题。但是,在通过ets方法制造具有八层或者更多层的电路板,特别是十层或者更多层的电路板的情况下,用于制造其的前置时间(lead time)耗费至少2个月或者更多,并且因此存在生产率被降低的问题。

84.另外,为了通过ets方法制造被掩埋的结构的精细电路图案,应该在多层电路板的制造工艺期间首先形成精细电路图案。此外,近来,为了应用于具有高集成度/高规格等的ap模块,需要具有八至十层的电路板。在这种情况下,在ets工艺期间首先形成精细电路图案并且然后执行多层堆叠工艺的工艺中,损坏由于热应力等被施加到精细电路图案,并且因此存在难以正常实现精细电路图案的问题。

85.此外,当通过ets方法制造电路板时,单独需要ets核心层。在这种情况下,当通过ets方法制造电路板时,需要用于最终去除ets核心层的额外工艺。

86.此外,当通过ets方法制造电路板时,当层被堆叠超过一定次数时,存在由于累积容差而导致生产量降低的问题,并且因此,产品成本增加,并且因为ets核心层周围的两个表面上分别执行堆叠工艺,所以存在图案损坏由于应力而增加的问题。

87.此外,随着近年来5g技术的发展,对可能反映其的电路板的兴趣正在增加。在这种情况下,为了应用5g技术,电路板应具有高度的多层结构,并且因此应使电路图案精细。但是,在比较示例中,虽然能够形成精细图案,但存在不能稳定地保护精细图案的问题。

88.因此,实施例旨在提供一种能够解决最外部分处设置的精细图案的可靠性问题的新结构的电路板及其控制方法。

89.图3是示出根据实施例的电路板的视图,并且图4是图3的区域b的放大图。

90.在图3和图4的描述之前,本实施例的电路板、根据实施例的电路板可以具有多层

结构。优选地,根据实施例的电路板可以具有基于电路图案的层数的十层或更多层的结构。然而,这仅仅是示例并且实施例不限于此。即,实施例中的电路板的层数可以具有小于10层的层数,或者可替选地,电路板可以具有大于10层的层数。

91.然而,实施例中的电路板用于解决比较示例中的ets方法的问题。在这种情况下,比较示例中的ets方法具有制造具有八层或者更多层的电路板需要耗费大量时间的问题,并且因此,在实施例中,它将被描述为具有十层结构以与其进行比较。

92.参考图3至图4,电路板100包括绝缘层110。

93.优选地,电路板100可以包括第一至第九绝缘层111、112、113、114、115、116、117、118和119以便于实现十层结构。

94.在这种情况下,绝缘层110的第一绝缘层111、第二绝缘层112、第三绝缘层113、第四绝缘层114、第五绝缘层115、第六绝缘层116和第七绝缘层117可以是在堆叠的绝缘层结构中设置的内部的内部绝缘层,并且第八绝缘层118可以是在内绝缘层上设置的最上绝缘层(第一最外绝缘层),并且第九绝缘层119可以是在内绝缘层下方设置的最下绝缘层(第二最外绝缘层)。

95.第一绝缘层111可以是在绝缘层110的堆叠结构中设置的中央处的核心绝缘层。第二绝缘层112、第四绝缘层114、第六绝缘层116和第八绝缘层118可以是被顺序设置在第一绝缘层111上的上绝缘层。另外,第三绝缘层113、第五绝缘层115、第七绝缘层117和第九绝缘层119可以是被顺序设置在第一绝缘层111下方的下绝缘层。

96.绝缘层110可以是其上形成有能够改变布线的电路的基板,并且可以包括印刷电路板、布线板和由能够在其表面上形成电路图案的绝缘材料制成的绝缘基板的全部。

97.例如,绝缘层110可以是刚性的或柔性的。例如,绝缘层110可以包括玻璃或塑料。具体地,绝缘层110可以包括诸如钠钙玻璃、铝硅酸盐玻璃等的化学钢化/半钢化玻璃,诸如聚酰亚胺(pi)、聚对苯二甲酸乙二醇酯(pet)、丙二醇(ppg)、聚碳酸酯(pc)等的钢化或柔性塑料、或蓝宝石。

98.此外,绝缘层110可以包括光学各向同性膜。作为示例,绝缘层110可以包括环烯烃共聚物(coc)、环烯烃聚合物(cop)、光学各向同性pc、光学各向同性聚甲基丙烯酸甲酯(pmma)等。

99.此外,绝缘层110中的至少一个可以在具有弯曲表面的同时被部分地弄弯(bent)。也就是说,绝缘层110中的至少一个可以部分地具有平面并且可以在具有弯曲表面的同时部分地弄弯。具体地,绝缘层110中的至少一个的端部可以被弄弯同时具有弯曲表面,或者被弄弯或扭曲同时具有带有任意曲率的表面。

100.此外,绝缘层110中的至少一个可以是具有柔性的柔性基板。此外,绝缘层110中的至少一个可以是弯曲的或弄弯的基板。在这种情况下,绝缘层110中的至少一个可以形成用于基于电路设计连接电路组件的电布线的布线布局,并且电导体可以被设置在绝缘材料上。此外,电子组件可以被安装在绝缘层110的至少一个上,并且绝缘层110可以形成被配置以连接电子组件以成为电路的布线,并且除了起到电连接组件的作用之外,还可以机械地固定元件。

101.电路图案可以被设置在绝缘层110的表面上。

102.也就是说,电路图案可以被设置在组成绝缘层110的第一至第九绝缘层111、112、

113、114、115、116、117、118和119的相应表面上。

103.这里,电路图案可以包括内层电路图案120以及外层电路图案130和140。内层电路图案120可以是在电路板的堆叠结构中的绝缘层110内部设置的电路图案,并且外层电路图案130和140可以是在电路板的堆叠结构中的绝缘层110的最外侧设置的电路图案。

104.内层电路图案120可以包括第一电路图案121、第二电路图案122、第三电路图案123、第四电路图案124、第五电路图案125、第六电路图案126、以及第七电路图案127。

105.第一电路图案121可以被设置在第一绝缘层111的上表面上,并且因此第一电路图案121可以由第二绝缘层112覆盖。第二电路图案122可以被设置在第一绝缘层111的下表面上,并且因此第二电路图案122可以由第三绝缘层113覆盖。第三电路图案123可以被设置在第二绝缘层112的上表面上,并且因此第三电路图案123可以由第四绝缘层114覆盖。第四电路图案124可以被设置在第三绝缘层113的下表面上,并且因此第四电路图案124可以由第五绝缘层115覆盖。第五电路图案125可以被设置在第四绝缘层114的上表面上,并且因此第五电路图案125可以由第六绝缘层116覆盖。第六电路图案126可以被设置在第五绝缘层115的下表面上,并且因此第六电路图案126可以由第七绝缘层117覆盖。第七电路图案127可以被设置在第六绝缘层116的上表面上,并且因此第七电路图案127可以由第八绝缘层118覆盖。第八电路图案128可以被设置在第七绝缘层117的下表面上,并且因此第八电路图案128可以由第九绝缘层119覆盖。

106.外层电路图案可以被设置在绝缘层110的最外侧上设置的最外绝缘层的表面上。优选地,外层电路图案可以包括下外层电路图案130,下外层电路图案130被设置在绝缘层110的最下部处设置的第九绝缘层119的下表面上。

107.此外,外层电路图案可以包括上外层电路图案140,上外层电路图案140被设置在绝缘层110的最上部上设置的第八绝缘层118的上表面上。

108.在这种情况下,下外层电路图案130和上外层电路图案140中的至少一个可以被形成为在绝缘层的表面上方突出。优选地,下外层电路图案130可以被形成为在第九绝缘层119的下表面下方突出。此外,上外层电路图案140可以被形成为在第八绝缘层118的上表面的上方突出。

109.也就是说,下外层电路图案130的上表面可以被定位为与第九绝缘层119的下表面相同的平面上。此外,上外层电路图案140的下表面可以被定位为与第八绝缘层180的上表面上设置的底漆层150的上表面相同的平面上。

110.换言之,底漆层150可以被设置在上外层电路图案140和第八绝缘层180的上表面上。

111.也就是说,上外层电路图案140可以包括精细电路图案。优选地,上外层电路图案140可以是具有10μm或更小的线宽以及10μm或更小的图案间间隔的精细电路图案。因此,当上外层电路图案140被直接设置在第八绝缘层118上时,第八绝缘层118与上外层电路图案140的接触面积小,并且因此可能出现上外层电路图案140与第八绝缘层118分离的情形。

112.因此,在实施例中,底漆层150被设置在上外层电路图案140和第八绝缘层118之间。底漆层150可以改进上外层电路图案140和第八绝缘层之间的结合力。底漆层150可以被设置以完全覆盖第八绝缘层118的上表面。此外,上外层电路图案140可以部分地设置在底漆层150上。因此,第一实施例中的底漆层150的上表面可以包括与上外层电路图案140接触

的第一部分和与稍后描述的支撑绝缘层160的下表面接触的第二部分。也就是说,当通过sap工艺形成上外层电路图案140时,底漆层150可以用于加强第八绝缘层118和上外层电路图案140之间的结合力。这样的底漆层150可以包括聚氨酯基树脂、丙烯酸树脂或硅酮基树脂(silicone-based resin),但实施例不限于此。

113.同时,在图3中图示底漆层没有被设置在第九绝缘层119和下外层电路图案130之间,但底漆层也可以被形成在第九绝缘层119和下外层电路图案130之间。然而,下外层电路图案130可以不是精细电路图案,并且因此,可以选择性地省略第九绝缘层119和下外层电路图案130之间的底漆层。

114.因此,当精细电路图案被设置在内层上时,可以省略底漆层,因为电路图案由至少一个绝缘层110覆盖。另一方面,在实施例中,当精细电路图案被设置在最外层上时,因为不存在覆盖精细电路图案的绝缘层,所以设置底漆层150以便于改进精细电路图案和绝缘层之间的结合力。

115.在下文中,将描述上外层电路图案140由精细电路图案形成。然而,实施例不限于此,并且下外层电路图案130也可以由精细电路图案形成。将显然的是,用于改进可靠性的结构,诸如加强结合力和防止下述上外层电路图案140塌陷的结构,也可以被应用于下外层电路图案130。

116.内层电路图案120、下外层电路图案130和上外层电路图案140可以是发射电信号的布线并且可以由具有高导电性的金属材料形成。为此,内电路图案120、下外层电路图案130和上外层电路图案140可以由选自金(au)、银(ag)、铂(pt)、钛(ti)、锡(sn)、铜(cu)和锌(zn)之中的至少一个材料形成。此外,内电路图案120、下外层电路图案130和上外层电路图案140可以由包括选自在结合力方面优异的金(au)、银(ag)、铂(pt)、钛(ti)、锡(sn)、铜(cu)和锌(zn)之中的至少一个金属材料的膏或焊膏形成。优选地,内电路图案120、下外层电路图案130和上外层电路图案140可以由具有高导电性和相对低成本的铜(cu)形成。

117.内层电路图案120、下外层电路图案130和上外层电路图案140中的至少一个可以通过诸如加成工艺(additive process)、减成工艺(subtractive process)、改进的半加成工艺(msap)、半加成工艺(sap)等的制造电路板的一般工艺形成,并且在此将省略其详细描述。

118.优选地,下外层电路图案130和上外层电路图案140是在电路板的最外侧上设置的最外电路图案,并且因此它们可以通过sap(半加成工艺)方法形成。

119.同时,通孔v可以被设置在绝缘层110中。通孔v被设置在每个绝缘层中,并且因此该通孔v可以用作将设置在不同层中的电路图案彼此电连接。

120.第一通孔vl可以被设置在第一绝缘层111中。第一通孔vl可以电连接第一绝缘层111的上表面上设置的第一电路图案121和第一绝缘层111的下表面上设置的第二电路图案122。

121.第二通孔v2可以被设置在第二绝缘层112中。第二通孔v2可以电连接在第一绝缘层111的上表面上设置的第一电路图案121和在第二绝缘层112的上表面上设置的第三电路图案123。

122.第三通孔v3可以被设置在第三绝缘层113中。第三通孔v3可以电连接在第一绝缘层111的下表面上设置的第二电路图案122和在第三绝缘层113的下表面上设置的第四电路

图案124。

123.第四通孔v4可以被设置在第四绝缘层114中。第四通孔v4可以电连接在第二绝缘层111的上表面上设置的第三电路图案123和在第四绝缘层114的上表面上设置的第五电路图案125。

124.第五通孔v5可以被设置在第五绝缘层115中。第五通孔v5可以电连接在第三绝缘层113的下表面上设置的第四电路图案124和在第五绝缘层115的下表面上设置的第六电路图案126。

125.第六通孔v6可以被设置在第六绝缘层116中。第六通孔v6可以电连接在第四绝缘层114的上表面上设置的第五电路图案125和在第六绝缘层116的上表面上设置的第七电路图案127。

126.第七通孔v7可以被设置在第七绝缘层117中。第七通孔v7可以电连接在第五绝缘层115的下表面上设置的第六电路图案126和在第七绝缘层117的下表面上设置的第八电路图案128。

127.第八通孔v1可以被设置在第八绝缘层118中。第八通孔v8可以电连接在第六绝缘层116的上表面上设置的第七电路图案127和在底漆层150的上表面上设置的上外层电路图案140。

128.第九通孔v9可以被设置在第九绝缘层119中。第九通孔v9可以电连接在第七绝缘层117的下表面上设置的第八电路图案128和在第九绝缘层119的下表面上设置的下外层电路图案130。

129.可以通过用金属材料填充每个绝缘层中形成的通孔洞的内部来形成如上所述的通孔v。

130.通孔洞可以通过机械、激光和化学处理方法中的任意一个形成。当通过机械加工形成通孔洞时,可以使用诸如铣削(milling)、钻孔(drilling)和布线(routing)的方法,当通过激光加工形成时,可以使用uv或co2激光方法,并且当通过化学加工形成通孔洞时,可以使用包括氨基硅烷、酮等的化学制品来对绝缘层110进行开口。

131.同时,激光加工是一种将光能集中在表面处使部分材料熔化和蒸发以得到所预期的形状的切割方法。可以容易地加工通过计算机程序的复杂形成物,并且可以加工难以通过其他方法切割的复合材料。

132.此外,通过激光的加工可以具有至少0.005mm的切割直径,并且具有可以处理的宽厚度范围。

133.优选使用钇铝石榴石(yag)激光器或co2激光器或紫外(uv)激光器作为激光加工钻头。yag激光器是能够处理铜箔层和绝缘层这两者的激光器,并且co2激光器是只能处理绝缘层的激光器。

134.当形成通孔洞时,可以通过用导电材料填充通孔洞的内部来形成第一至第九通孔v1、v2、v3、v4、v5、v6、v7、v8和v9。形成第一至第九通孔v1、v2、v3、v4、v5、v6、v7、v8和v9的金属材料可以是选自铜(cu)、银(ag)、锡(sn)、金(au)、镍(ni)和钯(pd)之中的任意一个材料,并且导电材料可以通过化学镀(electroless plating)、电解镀(electrolytic plating)、丝网印刷、溅射、蒸发、喷墨和点胶或者其组合中的任何一种被填充。

135.同时,保护层可以被设置在电路板100的最外侧上。优选地,第一保护层170可以被

设置在第八绝缘层118上(优选地,在底漆层150上)。此外,第二保护层175可以被设置在第九绝缘层119下方。

136.第一保护层170和第二保护层175可以由使用阻焊剂(sr)、氧化物和au中的任何一个或多个的至少一层形成。优选地,第一保护层170和第二保护层175可以是阻焊剂。

137.同时,第一保护层170被设置在底漆层150上。第一保护层170可以用于在支撑底漆层150上设置的上外层电路图案140的同时保护上外层电路图案140的表面。

138.也就是说,第一保护层170可以与在底漆层150上设置的上外层电路图案140部分重叠。第一保护层170的面积可以小于第八绝缘层118的面积。第一保护层170的面积可以小于底漆层150的面积。第一保护层170被部分地或者全部地设置在底漆层150和上外层电路图案140上,并且因此第一保护层170可以包括暴露上外层电路图案140的表面的开口区域。

139.第一保护层170可以包括具有诸如凹槽的形状的开口区域。优选地,第一保护层170包括暴露第一区域r1和第二区域r2中设置的上外层电路图案140的开口区域。在这种情况下,第一区域r1和第二区域r2可以是其中暴露上外层电路图案140的表面的开口区域。即,在其上安装有芯片器件的器件安装焊盘、用作用于与外部板连接的管芯的核心焊盘或bga焊盘、以及用作信号传输线的迹线等被包括在第一区域r1和第二区域r2中。此外,第一保护层170具有暴露第一区域r1和第二区域r2中的器件安装焊盘、核心焊盘和bga焊盘的表面的开口区域。

140.因此,第一区域r1和第二区域r2可以指的是外层电路图案140的表面通过上外层电路图案140和底漆层150的上部区域中的第一保护层170被暴露的区域。

141.即,电路板包括第一区域r1、第二区域r2和第三区域r3。第一区域r1和第二区域r2是其中上外层电路图案140的表面应通过第一保护层170暴露的开口区域,并且第三区域r3可以是其中上外层电路图案140的表面应由保护层170覆盖的掩埋区域。

142.即,第一区域rl是上外层电路图案140的区域,其中第一焊盘142和用于电连接到诸如芯片的组件的迹线141被设置在上外层电路图案140之中。因此,第一保护层170可以具有暴露第一区域r1中包括的第一焊盘142的表面的开口区域。此外,第二区域r2是在上外层电路图案140之中设置与用作用于结合到外部板的管芯的核心焊盘或bga焊盘相对应的第二焊盘143的区域。

143.此外,如上所述被设置在第一区域rl中的上外层电路图案140可能由于各种因素而在诸如塌陷或摩擦的可靠性方面具有问题。此外,组成上外层电路图案140的迹线141为精细电路图案,并且因此迹线141具有10μm或者更少的线宽w1和10μm或者更少的间隔,并且被设置在底漆层150上。因此,设置在第一区域r1上的迹线141可能具有容易通过各种小外部冲击而塌陷或摩擦的问题。

144.因此,在实施例中,为了改进第一区域rl上设置的上外层电路图案140的可靠性,保护层170也被形成在与第一区域rl相对应的底漆层150上。

145.也就是说,第一保护层170可以被设置在没有设置上外层电路图案140的底漆层150的上表面的区域中。例如,第一保护层170可以被设置在底漆层150的上表面上,并且因此第一保护层170可以被设置在第一区域r1上的上外层电路图案140之间。

146.在这种情况下,上外层电路图案140包括设置在第一区域r1和第二区域r2中的第一外层电路图案以及形成在第三区域r3中的第二外层电路图案。

147.此外,底漆层150的上表面可以包括对应于第一区域rl的第一上表面、对应于第二区域r2的第二上表面、以及对应于第三区域的第三上表面r3。

148.在这种情况下,如图3和图4中所示,第一保护层170可以完全被设置在底漆层150上,而没有划分第一区域r1、第二区域r2和第三区域r3。也就是说,第一保护层170可以分别设置在第一外层电路图案之间的区域和第二外层电路图案之间的区域中。

149.因此,第一保护层170包括设置在第一区域r1中的第一部分、设置在第二区域r2中的第二部分和设置在第三区域r3中的第三部分。

150.在这种情况下,第一保护层170对于每个区域可以具有不同的高度。

151.在第一区域r1和第二区域r2中,上外层电路图案140的表面应被暴露在外面,并且在第三区域r3中,上外层电路图案140的表面应由保护层覆盖。

152.这里,设置在第一区域r1和第二区域r2中的上外层电路图案140可以根据功能而具有不同的宽度。例如,如上所述,设置在第一区域r1和第二区域r2中的上外层电路图案140可以包括第一焊盘142、第二焊盘143和迹线141。

153.在这种情况下,迹线141可以具有10μm或更小的宽度。此外,第一焊盘可以具有大约45μm的宽度。此外,第二焊盘143可以具有在100μm和300μm之间的宽度w3。

154.因此,在实施例中,在上述阻焊剂的开口区域中,相对于设置迹线141的区域、设置第一焊盘142的区域、以及设置第二焊盘143的区域的每个具有不同高度的第一保护层170被形成。

155.也就是说,第一保护层170可以包括设置在第一区域r1中的第一部、设置在第二区域r2中的第二部以及设置在第三区域r3中的第三部。此外,第一部、第二部和第三部中的至少一个可以具有与至少另一个不同的高度。

156.例如,设置在第一区域rl中的第一部的上表面可以被定位为低于设置在第二区域r2中的第二部和设置在第三区域r3中的第三部的上表面。

157.此外,第二部的上表面可以被定位为高于第一部的上表面。此外,第二部的上表面可以具有与第三部的上表面相同的高度。即,第二部的上表面可以被定位在与第三部的上表面相同的平面上。

158.此外,第一部可以包括第一子部和第二子部。此外,第一子部和第二子部的上表面的高度可以彼此不同。例如,第一子部的上表面可以被定位为高于第二子部的上表面。在这种情况下,第一子部可以对应于在第一区域r1中设置有迹线141的区域。此外,第二子部可以对应于在第一区域r1中设置有第一焊盘142的区域。

159.在下文中,将详细描述第一保护层170。

160.第一保护层170可以被设置在底漆层150上。第一保护层170是阻焊剂。

161.第一保护层170可以被设置在底漆层150上的上外层电路图案140之间。也就是说,上外层电路图案140被设置在底漆层150上以彼此隔开预先确定的间隔。此外,第一保护层170可以被设置在其中没有设置上外层电路图案140的底漆层150的上表面的区域上。此外,第一保护层170可以被选择性地设置在上外层电路图案140上。

162.在下文中,第一保护层170将被描述为阻焊剂170。

163.阻焊剂170可以被设置在其中没有设置上外层电路图案140的底漆层150的上表面的区域上。

164.因此,阻焊剂170的下表面可以与底漆层150的上表面直接接触。另外,阻焊剂170可以具有与上外层电路图案140直接接触的结构。

165.例如,设置在第一区域rl中的阻焊剂170的第一部可以与上外层电路图案140的侧表面直接接触。此外,设置在第一区域r1中的阻焊剂170的第一部的一部分可以与上外层电路图案140的上表面直接接触。此外,设置在第一区域r1中的阻焊剂170的第一部的至少一部分可以暴露上外层电路图案140的上表面和侧表面。

166.此外,设置在第二区域r2中的阻焊剂170的第二部可以与上外层电路图案140的侧表面直接接触。另外,设置在第二区域r2中的阻焊剂170的第二部可以与上外层电路图案140的上表面的一部分直接接触。此外,设置在第二区域r2中的阻焊剂170的第二部可以暴露上外层电路图案140的上表面。

167.此外,设置在第三区域r3中的阻焊剂170的第三部可以与上外层电路图案140的侧表面直接接触。此外,设置在第三区域r3中的阻焊剂170的第三部可以与上外层电路图案140的上表面直接接触。也就是说,设置在第三区域r3中的阻焊剂170的第三部可以在上外层电路图案140的上表面上方以预先确定的高度突出并且可以设置为覆盖上外层电路图案140。详细地,设置在第三区域r3中的阻焊剂170的第三部可以被设置为围绕上外层电路图案140的侧表面和上表面。

168.在这种情况下,阻焊剂170对于每个部来说可以具有不同的高度。这里,阻焊剂170的每个部的高度可以由上外层电路图案140的高度确定。

169.上外层电路图案140可以具有第一高度hl并且可以被设置在绝缘层110上。在这种情况下,绝缘层110可以指的是设置在多个绝缘层的最上侧上的绝缘层。然而,在下文中,为了便于描述,将此称为绝缘层110。同时,底漆层150可以被设置在绝缘层110和上外层电路图案140之间。在这种情况下,上外层电路图案140可以被设置在底漆层150上以具有第一高度h1。此外,下面描述的“高度”可以对应于“厚度”。

170.上外层电路图案140的第一高度h1可以是12μm

±

2μm。例如,上外层电路图案140的第一高度h1可以处于10μm至14μm的范围内。

171.阻焊剂170的第三部可以被设置在上外层电路图案140上以具有第二高度h2。在这种情况下,阻焊剂170的第三部被设置以覆盖上外层电路图案140,以便于稳定地保护上外层电路图案140。在这种情况下,第二高度h2可以是7μm至17μm。当第二高度h2小于7μm时,掩埋在阻焊剂170的第三部中的上外层电路图案140可能不会被稳定保护免受各种因素。此外,当第二高度h2大于17μm时,电路板的整体厚度可能会增加。此外,当第二高度h2大于17μm时,电路板的制造成本可能会增加。

172.同时,设置在第二区域r2中的阻焊剂170的第二部173包括开口区域(opening region)r2-2并且可以具有距阻焊剂170的上表面的第二高度h2。也就是说,阻焊剂170的第二部173可以被设置为覆盖边缘区域,同时暴露第二区域r2中设置的上外层电路图案140的上表面的中央区域。也就是说,第二部173可以包括暴露上外层电路图案140的上表面的第一部分的开口区域r2-2,并且可以设置为在上外层电路图案140的第二部分上方具有第二高度h2。在这种情况下,第二高度h2可以对应于阻焊剂170的第三部的高度。

173.在这种情况下,第二区域r2中包括的上外层电路图案140是第二焊盘143。第二焊盘143可以是如上所述的bga焊盘或核心焊盘。因此,第二焊盘143可以具有比其他焊盘相对

process)中初次显影的部分。此外,阻焊剂170的第一子部171可以是用于在精确位置中形成第二子部172的初次曝光和显影区域,这将在后面描述,同时稳定地保护第一区域r1中包括的迹线141的表面。

184.阻焊剂170的第二子部172可以被形成在设置有第一焊盘142的第一区域r1的第二子区域r1-2中。

185.第二子部172可以暴露第一焊盘142的上表面。也就是说,第二子部172可以具有小于第一焊盘142的第一高度h1的第四高度h4。因此,第二子部172的上表面可以被定位为低于第一焊盘142的上表面。

186.第二子部172可以是在阻焊剂170的减薄工艺中二次显影的部分。即,第二子部172可以是初次显影部分的一部分。即,第二子部172可以通过对初次显影部分进行二次显影而具有低于第一子部171的高度。

187.第四高度h4可以由第一高度h1确定。例如,第四高度h4可以是第一高度h1的70%至90%。例如,当第四高度h4小于第一高度h1的70%时,第一焊盘142可能不会被阻焊剂170的第二子部172稳定地支撑。例如,当第四高度h4小于第一高度h1的70%时,在形成阻焊剂的第二子部172时可能存在工艺困难。例如,当第四高度h4大于第一高度h1的90%时,包括在阻焊剂170中的一部分填料可能保留在第一焊盘142上。例如,当第四高度h4大于第一高度h1的90%时,可能由于形成阻焊剂160的工艺中的偏差而出现第一焊盘142的表面被覆盖的问题。

188.在这种情况下,第一焊盘142可以是在其上安装有芯片器件的安装焊盘并且通常可以具有大约45μm的宽度w2。例如,第一焊盘142在横轴方向中的宽度w2可以是大约45μm。因此,当需要对第一焊盘142进行曝光时,应仅在设置有第一焊盘142的区域精确地执行曝光和显影。在这种情况下,用于曝光和显影的分辨率(例如,相对于曝光和显影区域的大小和位置的精度)可以随着要被显影的部分中阻焊剂170的厚度减小而增加。因此,在实施例中,阻焊剂170被初次曝光和显影使得将第一区域r1中的阻焊剂170的高度降低到上述第三高度h3的水平。此外,在实施例中,对阻焊剂170进行二次曝光和显影使得将第一区域r1的第二子区域r1-2中的阻焊剂170降低到第四高度h4。

189.在实施例中,阻焊剂170的第一子部171、第二子部172、第二部173和第三部分别通过执行如上所述的两步曝光和显影工艺形成。因此,在实施例中,阻焊剂170的第一子部171被设置以在第一子区域r1-1中的迹线141的上表面上方突出,并且因此可以稳定地保护迹线141。此外,阻焊剂170的第二子部172可以暴露第二子区域r1-2中的第一焊盘142的整个上表面。

190.在这种情况下,在二次曝光和显影工艺中,当仅设置有第一焊盘142的部分可以被精确地曝光和显影时,第二子部172可以基本上不存在。也就是说,在这种情况下,阻焊剂170可以被设置为具有总体第三高度h3,同时包括暴露焊盘的上表面的开口。

191.然而,由于工艺偏差或各种原因,难以精确地仅对设置有第一焊盘142的部分进行曝光和显影,并且因此,曝光和显影位置会根据工艺偏差而被位移。在这种情况下,在二次曝光和显影工艺中,设置在第一焊盘142上的阻焊剂可能不会全部被显影,并且可能会保留一些。此外,因为第一焊盘142的上表面没有暴露,所以这导致可靠性问题。

192.因此,在实施例中,考虑到由于工艺偏差或各种原因可能发生的位置偏移,在二次

曝光和显影工艺中,大于第一焊盘142的宽度w2的宽度w4被曝光和显影。

193.因此,第二子部172可以被设置为围绕第一焊盘142的侧表面的至少一部分。另外,可以执行二次显影工艺使得第二子部172具有与第一焊盘142相同的高度。然而,在这种情况下,阻焊剂的一部分可能保留在第一焊盘142上,并且因此可能会出现可靠性问题。因此,在实施例中,第二子部172的上表面被定位为低于第一焊盘142的上表面使得解决上述可靠性问题。

194.阻焊剂170可以使用光阻焊剂膜。阻焊剂170可以具有其中树脂和填料被混合的结构。

195.例如,阻焊剂170可以包括诸如baso4、sio2和talc的填料,并且其含量可以是20wt%至35wt%。

196.在这种情况下,当包括在阻焊剂170中的填料的含量小于20wt%时,上外层电路图案140可能不会受到阻焊剂170的稳定保护。另外,当阻焊剂170中包括的填料的含量大于35wt%时,在阻焊剂170的显影期间,填料中的一些可能保留在上外层电路图案140上,并且因此,可能出现可靠性问题,或者应额外执行去除填料的工艺。

197.同时,在实施例中,阻焊剂170的第三部的上表面是未被曝光和显影的部分。

198.此外,阻焊剂170的第一子部171、第二子部172和第二部173是被曝光和显影的部分。

199.因此,填料可以部分地暴露在第一子部171、第二子部172和第二部173的上表面上。然而,在阻焊剂170的第三部中,填料可以不被直接暴露。

200.因此,第一子部171、第二子部172和第二部173中的每个的表面粗糙度可以不同于阻焊剂170的第三部的表面粗糙度。例如,第一子部171、第二子部172和第二部173中的每个的表面粗糙度可以大于阻焊剂170的第三部的表面粗糙度。

201.实施例中的电路板是具有带有8层或者更多层的多层结构的电路板,并且包括外层电路图案,其被设置在多层之中的最上部处定位的外绝缘层上并且在外绝缘层的表面上方突出。在这种情况下,外层电路图案包括未设置阻焊剂的第一和第二区域中定位的第一外层电路图案和设置有阻焊剂的第三区域中定位的第二外层电路图案。在这种情况下,第二外层电路图案可以由阻焊剂支撑和保护,但是第一外层电路图案不具有能够支撑第一外层电路图案的支撑层,并且因此存在由于各种因素而导致第一外层电路图案可能容易塌陷的问题。

202.因此,在实施例中,第一区域和第二区域中的阻焊剂没有被完全去除并且保留,从而由阻焊剂支撑和保护第一外层电路图案。因此,在实施例中,可以通过使外层电路图案精细化来解决诸如第一区域和第二区域的第一外层电路图案的塌陷或摩擦的问题,从而改进产品可靠性。特别地,在实施例中,能够解决诸如第一区域中的第一外层电路图案中包括的迹线的塌陷或摩擦的问题,从而改进产品的可靠性。

203.同时,根据实施例的阻焊剂包括设置在第一区域中的第一部、设置在第二区域中的第二部和设置在第三区域中的第三部。此外,第二部可以具有开口并且具有与第三部相同的高度。此外,第一部包括具有的高度低于第二部和第三部的高度的第一子部和具有的高度低于第一子部的高度的子部。第一子部可以被形成为覆盖设置在第一区域中的第一外层电路图案的迹线的表面。此外,第二子部可以具有比第一焊盘的高度低的高度,同时暴露

设置在第一区域中的第一外层电路图案的第一焊盘的表面。也就是说,在实施例中,通过在两个步骤中对阻焊剂进行曝光和显影来形成第一子部、第二子部、第二部和第三部。因此,在实施例中,可以改进曝光的分辨率。另外,在实施例中,可以通过第一区域的第一子部稳定地保护迹线的表面,从而改进产品的可靠性。

204.另外,在实施例中,绝缘层的表面和底漆层的表面具有由阻焊剂覆盖的结构,并且因此,能够解决由于绝缘层的表面或底漆层的一部分的曝光而引起的可靠性问题。详细地,绝缘层的表面或底漆层的一部分的曝光指的是外层电路图案与阻焊剂之间存在特定空间。另外,当存在特定空间时,在该空间中保留诸如粘附构件的残留溶液,或者由于该残留溶液而产生空隙(void),从而导致可靠性的问题。另一方面,在实施例中,可以利用阻焊剂填充空间,从而解决可靠性问题。

205.另外,在实施例中,阻焊剂的第二子部被设置在第一焊盘的周围,并且第一子部被设置在第二子部的周围。此外,第一子部可以防止要设置在第一焊盘上的粘合构件(例如,焊球)的移动。也就是说,第一子部用作能够固定粘合构件的位置的屏障。因此,在实施例中,能够解决诸如由粘合构件的一部分向下流而引起的短路的可靠性问题。

206.此外,在实施例中,在去除阻焊剂时,使用曝光和显影方法来代替喷砂或等离子体方法。在这种情况下,当通过喷砂或等离子体方法去除阻焊剂时,外层电路图案的变形可能发生,并且在一些情况下,外层电路图案的横截面可能具有三角形形状。此外,当外层电路图案的横截面为三角形形状时,粘合构件可能无法稳定地设置在外层电路图案上,从而导致可靠性问题。相反,在实施例中,可以在不使外层电路图案变形的情况下去除阻焊剂,从而改进可靠性。

207.另外,实施例中的电路板可以被应用于5g通信系统,并且因此,能够最小化高频的传输损耗,从而进一步改进可靠性。具体地,实施例中的电路板能够在高频处被使用并且能够减少波损耗。

208.同时,在实施例中,在形成如上所述的阻焊剂170时,可以使用各种方法以从第一区域rl和第二区域r2去除阻焊剂170的一部分。例如,可以通过物理方法或化学方法去除阻焊剂170的一部分。例如,可以通过诸如等离子体或喷砂的方法来去除阻焊剂170。

209.然而,当通过物理方法或化学方法去除阻焊剂170时,上外层电路图案140也在此工艺期间被去除,使得上外层电路图案140被变形。例如,因为上外层电路图案140的一部分在阻焊剂170的去除工艺期间被一起去除,所以上外层电路图案140可能具有三角形的横截面。另外,当上外层电路图案140的上部分具有三角形形状,诸如焊球的粘合构件可能不会稳定地固定在上外层电路图案140上,并且因此会出现可靠性问题。此外,为了通过物理或化学方法去除保护层,需要昂贵的设备,并且因此制造成本可能会增加。

210.另一方面,在实施例中,可以通过经由曝光和显影工艺应用减薄方法来去除阻焊剂170,使得对于每个区域具有预期的高度。此外,在曝光和显影工艺期间,上外层电路图案140不被变形,并且上外层电路图案140的横截面形状可以被维持为四边形形状。

211.在下文中,将详细描述根据实施例的阻焊剂170的第二子部172。

212.图5是根据实施例的第二子部的放大图,图6a是用于描述根据实施例的第二子部的第一移位的视图,并且图6b是用于描述根据实施例的第二子部的第二移位的视图。

213.参考图5、6a和6b,可以通过执行二次曝光和显影来形成第二子部172,使得被初次

曝光和显影的第一区域r1中的第一子部171的部分具有大于第一焊盘142的宽度w2的宽度w4。

214.在这种情况下,第二子部172可以具有的高度低于第一焊盘142的高度。也就是说,第二子部172的上表面可以被定位为低于第一焊盘142的上表面。

215.第二子部172可以被设置为与第一焊盘142的侧表面的至少一部分接触。

216.第一焊盘142可以包括长轴和短轴。此外,第一焊盘142的长轴的宽度w2-1可以是大约80μm。此外,第一焊盘142的短轴的宽度w2-2可以是大约45μm。

217.此外,要被二次曝光和显影的区域的宽度w4可以在第一焊盘142的纵向轴方向中具有4-1宽度w4-1,并且在第一焊盘142的横向轴方向中具有4-2宽度w4-2。在这种情况下,4-1宽度w4-1可以比第一焊盘142的长轴的宽度w2-1大10μm至12μm。另外,4-2宽度w4-2可以比第一焊盘142的短轴的宽度w2-2大10μm至12μm。

218.在这种情况下,第二子部172可以分别设置在第一焊盘142的多个侧表面上。例如,第二子部172可以设置为围绕第一焊盘142的外围。

219.例如,第二子部172可以被形成为在第一焊盘142的第一侧表面上具有5-1宽度w5-1。此外,第二子部172可以被形成为在第一焊盘142的第二侧表面上具有5-2宽度w5-2。此外,第二子部172可以被形成为在第一焊盘142的第三侧表面上具有5-3宽度w5-3。此外,第二子部172可以被形成为在第一焊盘142的第四侧表面上具有5-4宽度w5-4。

220.在这种情况下,作为示例,5-1宽度w5-1、5-2宽度w5-2、5-3宽度w5-3和5-4宽度w5-4可以是彼此相同。这是因为在二次曝光和显影工艺中在精确的位置处执行曝光和显影。在这种情况下,5-1宽度w5-1、5-2宽度w5-2、5-3宽度w5-3和5-4宽度w5-4可以是10μm至12μm。

221.同时,第一焊盘142的一个侧表面可以被直接地连接到迹线141。因此,第二子部172的一部分可以被设置为暴露迹线141的上表面的一部分。

222.也就是说,迹线141包括直接连接到第一焊盘142的侧表面的第一部分141a和除了第一部分141a之外的第二部分。此外,第一部分141a的表面可以被第二子部172暴露。另外,第二部分141b的表面可以由第一子部171覆盖。

223.同时,在实施例中,第二子部172的5-1宽度w5-1、5-2宽度w5-2、5-3宽度w5-3、5-3宽度w5-3和5-4宽度w5-4可以彼此不同。这是因为曝光和显影没有在与第一焊盘142的中心相对应的精确位置处执行,并且由于二次曝光和显影工艺中的工艺偏差而发生位置移位。另外,在实施例中,为针对这种情况的准备中,要被二次曝光和显影的区域的宽度大于第一焊盘142的宽度。

224.因此,如图6a中所示,设置在第一焊盘142的第三侧表面上的第二子部172的5-3宽度’w5-3’和设置在与第三侧表面相对的第四侧表面上的第二子部172的5-4宽度’w5-4’可以彼此不同。

225.在这种情况下,5-3宽度’w5-3’和5-4宽度’w5-4’的宽度之和可以是20μm至24μm。

226.另外,如图6b中所示,到第一焊盘142的一个侧表面的最大位置偏移可以发生在第二子部172中。在这种情况下,第二子部172可以被设置为仅在第一焊盘142的第三侧表面上具有5-3宽度”w5-3”。另外,第二子部172可以不被设置在第一焊盘142的第四侧表面上,但第一子部171可以被设置在其上。在这种情况下,5-3宽度”w5-3”可以是20μm至24μm。

227.图7是用于描述根据实施例和比较示例的阻焊剂结构的可靠性的视图。

228.如图7的(a)中所示,在比较示例中,阻焊剂可以被设置在迹线141a和第一焊盘142a周围,但是阻焊剂被形成为具有低于第一焊盘142a或迹线141a的高度。

229.因此,在比较示例中,当诸如焊球sb的粘合构件被设置在第一焊盘142a上时,不存在用于固定粘合构件的位置的结构,并且因此,在设置有第一焊盘142a的状态中,该位置可能通过各种因素被移动。作为示例,在粘合构件被设置在第一焊盘142a上的状态中,粘合构件可能通过各种因素(例如,温度或位置偏差等)被移动到设置有迹线141a的位置,并且因此,由于迹线141a与第一焊盘142a彼此电接触而会出现诸如短路的可靠性问题。

230.另一方面,如图7b中所示,在实施例中,阻焊剂170的第二子部172被设置在第一焊盘142的周围,并且第二子部172被设置在第一焊盘142的周围。第一子部171被设置在其周围。此外,第一子部171可以防止要设置在第一焊盘142上的粘合构件(例如,焊球sb)的移动。也就是说,第一子部171的上表面被定位为高于第一焊盘142的上表面,并且因此用作能够固定粘合构件的位置的屏障。因此,在实施例中,能够解决由粘合构件的一部分向下流动而引起的诸如短路的可靠性问题。

231.图8是用于描述根据实施例的用于阻焊剂的每个部的表面粗糙度的视图。

232.在实施例中,阻焊剂170可以针对每个部具有不同的表面粗糙度。例如,阻焊剂170的第三部的上表面或第二部173的上表面是未显影的表面。相反,阻焊剂170的第一部的上表面,具体地,第一子部171的上表面或第二子部172的上表面是已逐步显影的表面。此外,阻焊剂170中存在填料。因此,填料可以通过逐步显影被暴露于第一子部171的上表面或第二子部172的上表面上的表面。此外,第一子部171的上表面或第二子部172的上表面的表面粗糙度可以大于第三部或第二部173的上表面的表面粗糙度。

233.例如,阻焊剂170的第三部的上表面或第二部173的上表面可以具有与第一子部171的上表面或第二子部172的上表面的表面粗糙度不同的表面粗糙度。

234.也就是说,第一子部171的上表面或第二子部172的上表面是在执行曝光和显影工艺之后由显影剂减薄的表面。此外,阻焊剂170的第三部或第二部173是通过曝光而固化的表面。

235.因此,第一子部171的上表面或第二子部172的上表面的中心线表面粗糙度ra可以是1.0μm或更大。

236.此外,阻焊剂170的第三部或第二部173的上表面的中心线表面粗糙度ra可以处于0.01μm至0.1μm的范围内。

237.图9至图19是示出按照工艺的顺序制造图3中所示的电路板的方法的视图。

238.参考图9,在实施例中,首先,可以执行制造用于制造电路板100的内部的内部基板100-1的工艺。

239.将简要地描述用于制造内层基板100-1的工艺。

240.内层基板100-1可以包括一个绝缘层,或者可选地包括多个绝缘层。

241.在图9中图示了内层基板100-1具有带有七层的绝缘层结构,但实施例不以此为限。例如,内层基板100-1可以包括少于七层,或者可替选地多于七层的绝缘层。

242.内层基板100-1可以包括排除电路板100的最外层上设置的绝缘层之外的剩余绝缘层。例如,内层基板100-1可以包括电路板100的最上部上设置的绝缘层和排除电路板100的最下部上设置的绝缘层之外的剩余绝缘层。

243.简要地描述制备内层基板100-1的工艺,首先制备第一绝缘层111。

244.然后,当制备第一绝缘层111时,在第一绝缘层111中形成第一通孔v1,并且在第一绝缘层111的上表面和下表面上分别形成电路图案121和第二电路图案122。

245.此后,在第一绝缘层111上形成第二绝缘层112,并且在第一绝缘层111下方形成第三绝缘层113。

246.接下来,在第二绝缘层112中形成第二通孔v2,并且在第二绝缘层112的上表面上形成第三电路图案123。此外,在第三绝缘层113中形成第三通孔v3,并且第四电路图案124被形成在第三绝缘层113的下表面下方。

247.此后,在第二绝缘层112上形成第四绝缘层114,并且在第三绝缘层113下方形成第五绝缘层115。

248.接下来,在第四绝缘层114中形成第四通孔v4,并且在第四绝缘层114的上表面上形成第五电路图案125。此外,在第五绝缘层115中形成第五通孔v5,并且在第五绝缘层115的下表面下方形成第六电路图案126。

249.此后,在第四绝缘层114上形成第六绝缘层116,并且在第五绝缘层115下方形成第七绝缘层117。

250.接下来,在第六绝缘层116中形成第六通孔v6,并且在第六绝缘层116的上表面上形成第七电路图案127。此外,在第七绝缘层117中形成第七通孔v7,并且在第七绝缘层117的下表面下方形成第八电路图案128。

251.因为制造内层基板100-1的工艺是本发明所属的技术领域中的已知技术,所以将省略其详细描述。

252.参考图10,当制造内层基板100-1时,与第一最外绝缘层相对应的第八绝缘层118被形成在内层基板100-1的上表面上。此外,与第二最外绝缘层相对应的第九绝缘层119被形成在内层基板100-1的下表面下方。

253.在这种情况下,当第八绝缘层118和第九绝缘层119被堆叠时,底漆层150可以分别被设置在第八绝缘层118的上表面和第九绝缘层119的下表面上,并且金属层155可以被设置在底漆层150上。金属层155可以用作平坦化第八绝缘层118和第九绝缘层119以具有均匀的高度。例如,金属层155可以被设置以便于改进第八绝缘层118和第九绝缘层119的堆叠可靠性。

254.底漆层150可以用于增加在第八绝缘层118和第九绝缘层119上和下方分别设置的下外层电路图案130和上外层电路图案140之间的结合力。也就是说,当下外层电路图案130和上外层电路图案140被设置而没有底漆层150时,第八绝缘层118和上外层电路图案140之间的结合力低,并且因此它们可能互相分离。

255.同时,在图10中图示了底漆层150分别被设置在第八绝缘层118的上表面和第九绝缘层119的下表面上,但实施例不限于此。例如,底漆层150可以选择性地被设置在绝缘层的要设置有精细电路图案的表面上。也就是说,当只有下外层电路图案130是精细电路图案时,底漆层150可以只设置在第九绝缘层119的下表面上。另外,当只有上外层电路图案140是精细电路图案时,底漆层150可以仅被设置在第八绝缘层118的上表面上。此外,当下外层电路图案130和上外层电路图案140都是精细电路图案时,底漆层150可以被设置在第八绝缘层118的上表面和第九绝缘层119的下表面这两者上。

256.参考图11,当第八绝缘层118和第九绝缘层119被设置时,分别在第八绝缘层118和第九绝缘层119中形成通孔洞vh。在这种情况下,通孔洞vh可以分别不仅被形成在第八绝缘层118和第九绝缘层119中,而且被形成在底漆层150和金属层155中。

257.接下来,参考图12,当形成通孔洞vh时,可以执行去除底漆层150上设置的金属层155的蚀刻工艺。例如,在形成通孔洞vh之后,可以执行快速蚀刻工艺以去除金属层155,并且从而可以执行用于暴露底漆层150的表面的工艺。

258.接下来,参考图13,可以执行用于填充通孔洞vh的通孔v形成工艺,并且因此上外层电路图案140可以被形成在第八绝缘层118的上表面上,并且下外层电路图案130可以被形成在第九绝缘层119的下表面上。在这种情况下,在实施例中,图示了下外层电路图案130为普通电路图案而不是精细电路图案,但实施例不限于此,并且下外层电路图案130与第二外层电路图案一起可以是精细电路图案。因此,当下外层电路图案130是普通电路图案时,可以省略第九绝缘层119和下外层电路图案130之间的底漆层150。

259.上外层电路图案140被设置在第八绝缘层118的上表面上。在这种情况下,设置在第八绝缘层118的上表面上的上外层电路图案140可以包括第一保护层170的开口区域r1和r2中设置的部分和设置有第一保护层170的设置区域r3中设置的部分中。此外,可以在区域r1、r2和r3的每个中设置作为用于信号传输的布线线路的迹线和焊盘。

260.具体地,迹线141和第一焊盘142可以被设置在第一区域rl中。第一焊盘142可以是在其上要安装器件的安装焊盘。

261.此外,第二焊盘143可以被设置在第二区域r2中。第二焊盘143可以是bga焊盘或核心焊盘。特别地,第二焊盘143可以具有比第一焊盘142的宽度大的宽度。因此,第二焊盘143不受显影分辨率的显著影响,并且因此,具有与第一区域r1中设置的阻焊剂170的形状不同的形状的阻焊剂170可以被设置。

262.接下来,参考图14,阻焊剂被设置在底漆层150上使得覆盖上外层电路图案140。此时形成的阻焊剂可以被设置在第一区域r1、第二区域r2和第三区域r3中的所有区域中,并且可以被形成以便具有比上外层电路图案140的高度大的高度。

263.接下来,参考图15,可以执行初次曝光工艺。可以执行初次曝光工艺以将阻焊剂170的厚度降低到特定水平或更小。

264.可以相对于排除第一区域r1和第二区域r2中的开口r2-2之外的区域执行初次曝光。优选地,可以相对于第三区域和第二区域r2中的排除开口r2-2之外的区域r2-1执行初次曝光。

265.这里,通过初次曝光而曝光的部分被固化并且在随后的显影工艺中不被减薄。

266.接下来,参考图16,可以对在初次曝光工艺中未固化的部分执行初次显影工艺。在这种情况下,形成在初次显影部分中的阻焊剂170可以具有第三高度h3。

267.初级显影工艺可以包括使用含有四甲基氢氧化铵(tmah)或三甲基-2-羟乙基氢氧化铵(胆碱)的有机碱性化合物在未曝光区域上执行的减薄工艺。

268.接下来,参考图17,可以执行二次曝光工艺。可以执行二次曝光工艺以将初次曝光的阻焊剂170的一部分的厚度降低到特定水平或更小。

269.可以对第一区域rl中的第一子区域rl-l执行二次曝光。也就是说,可以仅对在初次曝光工艺中未曝光的部分之中的第一子区域r1-1执行二次曝光工艺。

270.即,可以对第二区域r2中的排除开口r2-2之外的区域和排除其中形成第一焊盘142的第二子区域r1-2之外的区域执行二次曝光工艺。

271.接下来,参考图18,可以对在二次曝光工艺中未曝光的部分执行二次显影工艺。在这种情况下,可以通过经由厚度控制仅去除一部分阻焊剂170,而不完全去除未曝光部分的阻焊剂170,来执行二次显影工艺。优选地,基于第一焊盘142的高度,可以通过减薄阻焊剂170以便具有低于第一焊盘142的上表面的高度和高于第一焊盘142的下表面的高度来执行二次显影工艺。

272.在二次显影工艺中,可以包括使用含有氢氧化四甲基铵(tmah)或氢氧化三甲基-2-羟乙基铵(胆碱)的有机碱性化合物对未曝光区域执行减薄的工艺。

273.接下来,参考图19,可以执行形成第二保护层175的工艺。在这种情况下,当形成对应于第一保护层的阻焊剂170时,可以一起形成第二保护层175。

274.同时,在实施例中,可以使用上述电路板制造封装基板。

275.例如,粘合部分(未示出)可以被设置在电路板的第一焊盘142上。此外,芯片可以被设置在粘合部分上。

276.例如,多个第一焊盘142可以被形成为在宽度方向中间隔开,并且多个芯片可以被安装在多个第一焊盘上。

277.例如,中央处理器(例如,cpu)、图形处理器(例如,gpu)、数字信号处理器、加密处理器、微处理器和微控制器中的任意一个芯片都可以被安装在焊盘142上。

278.例如,中央处理器(例如,cpu)、图形处理器(例如,gpu)、数字信号处理器、加密处理器、微处理器和微控制器之中的至少两个不同的芯片可以被安装在焊盘上。

279.实施例中的电路板是具有带有8层或者更多层的多层结构的电路板并且包括外层电路图案,外层电路图案被设置在多层之中的最上部处定位的外绝缘层上并且在外绝缘层的表面上方突出。在这种情况下,外层电路图案包括被定位在未设置阻焊剂的第一和第二区域中的第一外层电路图案和被定位在设置有阻焊剂的第三区域中的第二外层电路图案。在这种情况下,第二外层电路图案可以由阻焊剂支撑和保护,但是第一外层电路图案不具有能够支撑第一外层电路图案的支撑层,并且因此存在由于各种因素而导致第一外层电路图案可能容易塌陷的问题。

280.因此,在实施例中,第一区域和第二区域中的阻焊剂没有被完全去除并且保留,从而由阻焊剂支撑和保护第一外层电路图案。因此,在实施例中,可以通过使外层电路图案精细化来解决诸如第一区域和第二区域的第一外层电路图案的塌陷或摩擦的问题,从而改进产品可靠性。特别地,在实施例中,可以解决诸如第一区域中的第一外层电路图案中包括的迹线的塌陷或摩擦的问题,从而改进产品的可靠性。

281.同时,根据实施例的阻焊剂包括设置在第一区域中的第一部、设置在第二区域中的第二部和设置在第三区域中的第三部。此外,第二部可以具有开口并且具有与第三部相同的高度。此外,第一部包括具有的高度低于第二部和第三部的高度的第一子部和具有的高度低于第一子部的高度的子部。第一子部可以被形成为覆盖设置在第一区域中的第一外层电路图案的迹线的表面。此外,第二子部可以具有比第一焊盘的高度低的高度,同时暴露设置在第一区域中的第一外层电路图案的第一焊盘的表面。也就是说,在实施例中,通过在两个步骤中对阻焊剂进行曝光和显影来形成第一子部、第二子部、第二部和第三部。因此,

在实施例中,可以改进曝光的分辨率。另外,在实施例中,可以通过第一区域的第一子部稳定地保护迹线的表面,从而改进产品的可靠性。

282.另外,在实施例中,绝缘层的表面和底漆层的表面具有由阻焊剂覆盖的结构,并且因此,能够解决由于绝缘层的表面或底漆层的一部分的曝光而引起的可靠性问题。详细地,绝缘层的表面或底漆层的一部分的曝光指的是外层电路图案与阻焊剂之间存在特定空间。另外,当存在特定空间时,在该空间中保留诸如粘附构件的残留溶液,或者由于该残留溶液而产生空隙,从而导致可靠性的问题。另一方面,在实施例中,可以利用阻焊剂填充空间,从而解决可靠性问题。

283.另外,在实施例中,阻焊剂的第二子部被设置在第一焊盘的周围,并且第一子部被设置在第二子部的周围。此外,第一子部可以防止要设置在第一焊盘上的粘合构件(例如,焊球)的移动。也就是说,第一子部用作能够固定粘合构件的位置的屏障。因此,在实施例中,能够解决诸如由于粘合构件的一部分向下流而引起的短路的可靠性问题。

284.此外,在实施例中,在去除阻焊剂时,使用曝光和显影方法来代替喷砂或等离子体方法。在这种情况下,当通过喷砂或等离子体方法去除阻焊剂时,外层电路图案的变形可能发生,并且在一些情况下,外层电路图案的横截面可能具有三角形形状。此外,当外层电路图案的横截面为三角形形状时,粘合构件可能无法稳定地设置在外层电路图案上,从而导致可靠性问题。相反,在实施例中,可以在不使外层电路图案变形的情况下去除阻焊剂,从而改进可靠性。

285.另外,实施例的电路板可以被应用于5g通信系统,并且因此,能够最小化高频的传输损耗,从而进一步改进可靠性。具体地,实施例中的电路板能够在高频处被使用并且能够减少波损耗。

286.上述实施例中描述的特性、结构、效果等被包括在至少一个实施例中,但不仅限于一个实施例。此外,本领域的技术人员可以针对其他实施例来组合或修改每个实施例中说明的特性、结构和效果。因此,与这样的组合和修改相关的内容应理解为被包括在实施例的范围内。

287.以上对实施例进行了大部分描述,但这些实施例仅是示例并不限制实施例,并且本领域的技术人员可以领会,在不脱离实施例的本质特性的情况下,可以做出以上未提出的多种变化和应用。例如,可以变化实施例中具体表示的每个组件。此外,应理解与这样的变化和这样的应用相关的差异被包括在下述附权利要求中限定的实施例的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。