1.本发明实施例涉及集成电路技术领域,尤其涉及一种集成电路的测试结构。

背景技术:

2.闩锁效应(latch-up)是cmos工艺所特有的寄生效应,严重会导致电路的失效,甚至烧毁芯片。在cmos集成电路中,寄生的npn晶体管电性极不稳定,在静电或者相关电压瞬变的影响下,npn晶体管易发生闩锁效应。出现闩锁时,npn晶体管会处于放大状态,发射结正偏,集电结反偏,半导体元器件在电源电压和地端之间形成低抗通路的同时,正反馈回路会使电路一直保持低抗通路,从而产生大电流,使芯片产生永久性的破坏。

3.为保证芯片的可靠性,需要避免集成电路发生闩锁效应,因此,在芯片开发阶段,需要通过测试集成电路中可能存在的各种寄生npn晶体管结构,提取相应的规则参数来进行集成电路的设计,以避免闩锁效应的发生。

技术实现要素:

4.本发明实施例提供一种集成电路的测试结构,用以解决相关技术中缺少集成电路的测试结构的技术问题。

5.第一方面,本发明实施例提供一种集成电路的测试结构,包括:

6.第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;

7.其中,所述第一n型重掺杂区、所述第二n型重掺杂区和所述第一p型重掺杂区均位于p型衬底上;所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;

8.所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。

9.在一种可实现的方式中,所述第一n型重掺杂区、所述第二n型重掺杂区以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。

10.在一种可实现的方式中,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。

11.第二方面,本发明实施例提供一种集成电路的测试结构,包括:

12.第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;

13.其中,所述第一n型重掺杂区位于n阱内,所述第二n型重掺杂区和所述第一p型重掺杂区均位于p型衬底上,所述n阱位于所述p型衬底上;

14.所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;

15.所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。

16.在一种可实现的方式中,所述n阱、所述第二n型重掺杂区以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。

17.在一种可实现的方式中,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。

18.第三方面,本发明实施例提供一种集成电路的测试结构,包括:

19.第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;

20.其中,所述第一n型重掺杂区位于深n阱内,所述第二n型重掺杂区和所述第一p型重掺杂区均位于p型衬底上,所述深n阱位于n阱内,所述n阱位于所述p型衬底上;

21.所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;

22.所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。

23.在一种可实现的方式中,所述深n阱、所述第二n型重掺杂区以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。

24.在一种可实现的方式中,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。

25.第四方面,本发明实施例提供一种集成电路的测试结构,包括:

26.第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;

27.其中,所述第二n型重掺杂区位于n阱内,所述第一n型重掺杂区和所述第一p型重掺杂区均位于p型衬底上,所述n阱位于所述p型衬底上;

28.所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;

29.所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。

30.在一种可实现的方式中,所述n阱、所述第一n型重掺杂区以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。

31.在一种可实现的方式中,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。

32.第五方面,本发明实施例提供一种集成电路的测试结构,包括:

33.第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;

34.其中,所述第二n型重掺杂区位于深n阱内,所述第一n型重掺杂区和所述第一p型重掺杂区均位于p型衬底上,所述深n阱位于n阱内,所述n阱位于所述p型衬底上;

35.所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;

36.所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。

37.在一种可实现的方式中,所述深n阱、所述第一n型重掺杂区以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。

38.在一种可实现的方式中,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。

39.第六方面,本发明实施例提供一种集成电路的测试结构,包括:

40.第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;

41.其中,所述第一n型重掺杂区位于第一n阱内,所述第二n型重掺杂区位于第二n阱内,所述第一p型重掺杂区均位于p型衬底上,所述第一n阱和所述第二n阱位于所述p型衬底上;

42.所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;

43.所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。

44.在一种可实现的方式中,所述第一n阱、所述第二n阱以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。

45.在一种可实现的方式中,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。

46.第七方面,本发明实施例提供一种集成电路的测试结构,包括:

47.第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;

48.其中,所述第一n型重掺杂区位于第一n阱内,所述第二n型重掺杂区位于深n阱内,所述第一p型重掺杂区均位于p型衬底上,所述第一n阱位于所述p型衬底上,所述深n阱位于第二n阱内,所述第二n阱位于所述p型衬底上;

49.所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;

50.所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。

51.在一种可实现的方式中,所述第一n阱、所述深n阱以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。

52.在一种可实现的方式中,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。

53.第八方面,本发明实施例提供一种集成电路的测试结构,包括:

54.第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;

55.其中,所述第二n型重掺杂区位于第一n阱内,所述第一n型重掺杂区位于深n阱内,所述第一p型重掺杂区均位于p型衬底上,所述第一n阱位于所述p型衬底上,所述深n阱位于

第二n阱内,所述第二n阱位于所述p型衬底上;

56.所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;

57.所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。

58.在一种可实现的方式中,所述第一n阱、所述深n阱以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。

59.在一种可实现的方式中,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。

60.第九方面,本发明实施例提供一种集成电路的测试结构,包括:

61.第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;

62.其中,所述第一n型重掺杂区位于第一深n阱内,所述第二n型重掺杂区位于第二深n阱内,所述第一p型重掺杂区均位于p型衬底上,所述第一深n阱位于第一n阱内,所述第二深n阱位于第二n阱内,所述第一n阱和所述第二n阱位于所述p型衬底上;

63.所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;

64.所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。

65.在一种可实现的方式中,所述第一深n阱、所述第二深n阱以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。

66.在一种可实现的方式中,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。

67.本发明提供的集成电路的测试结构,包括第一n型重掺杂区、第一p型重掺杂区、以及位于第一n型重掺杂区和第一p型重掺杂区之间的第二n型重掺杂区,第一n型重掺杂区和第二n型重掺杂区之间具有第一距离,第二n型重掺杂区和第一p型重掺杂区之间具有第二距离;调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数,这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生npn晶体管的闩锁特性,据此闩锁特性可以设置具有该测试结构的集成电路的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

附图说明

68.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

69.图1为本发明实施例提供的一种晶圆的结构示意图;

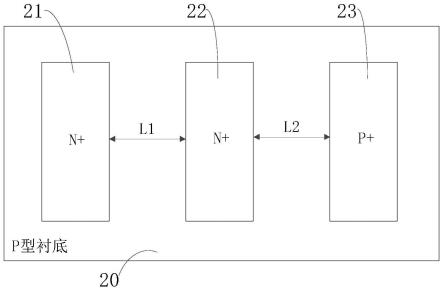

70.图2为本发明实施例提供的一种集成电路的测试结构的俯视图一;

71.图3为本发明实施例提供的一种集成电路的测试结构的剖面图一;

72.图4为本发明实施例提供的一种集成电路的测试结构的俯视图二;

73.图5为本发明实施例提供的一种集成电路的测试结构的剖面图二;

74.图6为本发明实施例提供的一种集成电路的测试结构的俯视图三;

75.图7为本发明实施例提供的一种集成电路的测试结构的剖面图三;

76.图8为本发明实施例提供的一种集成电路的测试结构的俯视图四;

77.图9为本发明实施例提供的一种集成电路的测试结构的剖面图四;

78.图10为本发明实施例提供的一种集成电路的测试结构的俯视图五;

79.图11为本发明实施例提供的一种集成电路的测试结构的剖面图五;

80.图12为本发明实施例提供的一种集成电路的测试结构的俯视图六;

81.图13为本发明实施例提供的一种集成电路的测试结构的剖面图六;

82.图14为本发明实施例提供的一种集成电路的测试结构的俯视图七;

83.图15为本发明实施例提供的一种集成电路的测试结构的剖面图七;

84.图16为本发明实施例提供的一种集成电路的测试结构的俯视图八;

85.图17为本发明实施例提供的一种集成电路的测试结构的剖面图八;

86.图18为本发明实施例提供的一种集成电路的测试结构的俯视图九;

87.图19为本发明实施例提供的一种集成电路的测试结构的剖面图九。

88.附图标记说明:

89.10:晶圆;11;晶粒;12:划片道;

90.20、30、40、50、60、70、80、90、100:p型基底;

91.21、31、41、51、61、71、81、91、101:第一n型重掺杂区;

92.22、32、42、52、62、72、82、92、102:第二n型重掺杂区;

93.311、412、521、622:n阱;

94.411、621、821、911:深n阱;

95.711、811、921、1012:第一n阱;

96.721、822、912、1022:第二n阱;

97.1011:第一深n阱;1021:第二深n阱;

98.23、33、43、53、63、73、83、93、103:第一p型重掺杂区;

99.24、34、44、54、64、74、84、94、104:寄生电阻。

具体实施方式

100.为保证芯片的可靠性,需要避免集成电路发生闩锁效应,因此,在芯片开发阶段,需要通过测试集成电路中可能存在的各种寄生npn晶体管结构,提取相应的规则参数来进行集成电路的设计,以避免闩锁效应的发生。

101.有鉴于此,本发明实施例提供一种集成电路的测试结构,包括第一n型重掺杂区、第一p型重掺杂区、以及位于第一n型重掺杂区和第一p型重掺杂区之间的第二n型重掺杂区,第一n型重掺杂区和第二n型重掺杂区之间具有第一距离,第二n型重掺杂区和第一p型重掺杂区之间具有第二距离;通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数,这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生npn晶体管的闩锁特性,据此闩锁特性可以设置具有该测试结构的集成电路

的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

102.下面结合附图对本发明的几种可选地实现方式进行介绍,当本领域技术人员应当理解,下述实现方式仅是示意性的,并非是穷尽式的列举,在这些实现方式的基础上,本领域技术人员可以对某些特征或者某些示例进行替换、拼接或者组合,这些仍应视为本发明的公开内容。

103.如图1所示,本发明实施例提供的一种集成电路的测试结构可以设置在晶圆10上。晶圆10包括多个晶粒11以及位于晶粒11之间的划片道12,具体地,本发明实施例提供的集成电路的测试结构可以设置在划片道12内。集成电路的测试结构所对应的等效电路与晶粒11上设置的集成电路相同,以便通过测试集成电路的测试结构即可测试晶粒11上集成电路的电学参数,进而避免晶粒11上的集成电路在工作过程中发生闩锁效应。

104.需要说明的是,测试的电学参数可以包括闩锁效应的触发电压(trigger voltage)、维持闩锁效应的维持电压(holding voltage)、闩锁效应触发时的电流(trigger current)和闩锁效应维持阶段的电流(holding current),触发电压越大,越不容易引起闩锁效应,维持电压越大,越不容易维持闩锁效应,假如正常工作电压是1.1v,如果触发电压为1.2v,那么引起闩锁效应的风险就非常大,如果触发电压为2v,那么引起闩锁效应的风险则比较小。同样的,维持电压具有相同的原理。需要注意的是,维持电压一般小于触发电压。

105.集成电路的测试结构包括第一n型重掺杂区、第一p型重掺杂区、以及位于第一n型重掺杂区和第一p型重掺杂区之间的第二n型重掺杂区,第一n型重掺杂区和第二n型重掺杂区之间具有第一距离,第二n型重掺杂区和第一p型重掺杂区之间具有第二距离;通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数,也即,上述的闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流。这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生npn晶体管的闩锁特性,据此闩锁特性可以设置具有该测试结构的集成电路的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

106.值得说明的是,可以通过传输线脉冲发生器(transmission line pulse,tlp)对该集成电路的测试结构进行测试:使输线脉冲发生器的接触端与集成电路的测试结构的引脚连接,向引脚注入电流,以测试这种集成电路的测试结构的闩锁效应的电学参数。

107.下面简要介绍9种集成电路的测试结构,如图2至图19所示,图中n 指代n型重掺杂区,p 指代p型重掺杂区。

108.参照图2和图3,本实施例提供的一种集成电路的测试结构,包括:第一n型重掺杂区21、第一p型重掺杂区23、以及位于第一n型重掺杂区21和第一p型重掺杂区23之间的第二n型重掺杂区22;其中,第一n型重掺杂区21、第二n型重掺杂区22和第一p型重掺杂区23均位于p型衬底20上;第一n型重掺杂区21和第二n型重掺杂区22之间具有第一距离,第二n型重掺杂区22和第一p型重掺杂区23之间具有第二距离;测试结构用于通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。

109.进一步的,第一n型重掺杂区21、第二n型重掺杂区22以及第一p型重掺杂区23构成寄生npn晶体管,测试结构用于测试寄生npn晶体管的闩锁特性。

110.进一步地,p型衬底20具有寄生电阻24,寄生电阻24的第一端连接第一p型重掺杂区23,寄生电阻24的第二端连接寄生npn晶体管的基极。

111.在对本实施例的集成电路的测试结构进行测试前,需要对其进行通电连接,具体的,如图3所示,可以将第一n型重掺杂区21连接电源电压vdd,将第二n型重掺杂区22以及第一p型重掺杂区23连接地端vss。

112.具体的,寄生npn晶体管的基极为p型衬底20,基极到集电极的增益可达数十倍。寄生npn晶体管和寄生电阻24构成的等效电路中,寄生npn晶体管存在两种状态:一种为高阻阻塞态,另一种为低阻闩锁态。当无外界干扰未引起触发时,寄生npn晶体管处于高阻阻塞态,也为寄生npn晶体管的初始状态,此时电流增益非常小,闩锁效应不会产生。当寄生npn晶体管的集电极电流或电压突然增加到预设值时,寄生npn晶体管可能会脱离高阻阻塞态进入低阻闩锁态,此时,寄生npn晶体管会在电源电压vdd和地端vss形成负阻状态,此时,只需要一个非常小的电流就可以持续驱动寄生npn晶体管的放大状态,发射结正偏,集电结反偏,也即形成了闩锁。

113.在对本实施例的集成电路的测试结构进行测试时,第一距离l1、第二距离l2为第一组设定值时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至2v,监测电源端vdd和接地端vss之间的电流,当电源端vdd和接地端vss之间的电流突然变大时判定此时发生闩锁效应,如此,即可得到第一组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系,也即得到了寄生npn晶体管的闩锁特性。调整第一距离l1和第二距离l2中的至少一个,可以得到第二组设定值,再通过上述的测试方法,即可得到第二组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系。以此类推,可以得到多组对应关系,可以依据得到的对应关系设置具有该测试结构的集成电路的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

114.本实施例提供的集成电路的测试结构,通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生npn晶体管的闩锁特性,据此闩锁特性可以定义具有该测试结构的集成电路的设计规则,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

115.参照图4和图5,本实施例提供的一种集成电路的测试结构,包括:第一n型重掺杂区31、第一p型重掺杂区33、以及位于第一n型重掺杂区31和第一p型重掺杂区33之间的第二n型重掺杂区32;其中,第一n型重掺杂区31位于n阱311内,第二n型重掺杂区32和第一p型重掺杂区33均位于p型衬底30上,n阱311位于p型衬底30上;第一n型重掺杂区31和第二n型重掺杂区32之间具有第一距离,第二n型重掺杂区32和第一p型重掺杂区33之间具有第二距离;测试结构用于通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。

116.进一步地,n阱311、第二n型重掺杂区32以及第一p型重掺杂区33构成寄生npn晶体管,测试结构用于测试寄生npn晶体管的闩锁特性。

117.进一步地,p型衬底30具有寄生电阻34,寄生电阻34的第一端连接第一p型重掺杂

区33,寄生电阻34的第二端连接寄生npn晶体管的基极。

118.在对本实施例的集成电路的测试结构进行测试前,需要对其进行通电连接,具体的,如图5所示,可以将第一n型重掺杂区31连接电源电压vdd,将第二n型重掺杂区32以及第一p型重掺杂区33连接地端vss。

119.具体的,寄生npn晶体管的基极为p型衬底30,基极到集电极的增益可达数十倍。寄生npn晶体管和寄生电阻34构成的等效电路中,寄生npn晶体管存在两种状态:一种为高阻阻塞态,另一种为低阻闩锁态。当无外界干扰未引起触发时,寄生npn晶体管处于高阻阻塞态,也为寄生npn晶体管的初始状态,此时电流增益非常小,闩锁效应不会产生。当寄生npn晶体管的集电极电流突然增加到预设值时,寄生npn晶体管可能会脱离高阻阻塞态进入低阻闩锁态,此时,寄生npn晶体管会在电源电压vdd和地端vss形成负阻状态,此时,只需要一个非常小的电流就可以持续驱动寄生npn晶体管的放大状态,发射结正偏,集电结反偏,也即形成了闩锁。

120.在对本实施例的集成电路的测试结构进行测试时,在第一距离l1、第二距离l2为第一组设定值时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至2v,监测电源端vdd和接地端vss之间的电流,当电源端vdd和接地端vss之间的电流突然变大时判定此时发生闩锁效应,如此,即可得到第一组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系,也即得到了寄生npn晶体管的闩锁特性。调整第一距离l1和第二距离l2中的至少一个,可以得到第二组设定值,再通过上述的测试方法,即可得到第二组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系。以此类推,可以得到多组对应关系,可以依据得到的对应关系设置具有该测试结构的集成电路的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

121.本实施例提供的集成电路的测试结构,通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生npn晶体管的闩锁特性,据此闩锁特性可以定义具有该测试结构的集成电路的设计规则,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

122.参照图6和图7,本实施例提供一种集成电路的测试结构,包括:第一n型重掺杂区41、第一p型重掺杂区43、以及位于第一n型重掺杂区41和第一p型重掺杂区43之间的第二n型重掺杂区42;其中,第一n型重掺杂区41位于深n阱411内,第二n型重掺杂区42和第一p型重掺杂区43均位于p型衬底40上,深n阱411位于n阱412内,n阱412位于p型衬底40上;第一n型重掺杂区41和第二n型重掺杂区42之间具有第一距离,第二n型重掺杂区42和第一p型重掺杂区43之间具有第二距离;测试结构用于通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。

123.进一步地,深n阱411、第二n型重掺杂区42以及第一p型重掺杂区43构成寄生npn晶体管,测试结构用于测试寄生npn晶体管的闩锁特性。

124.进一步的,p型衬底40具有寄生电阻44,寄生电阻44的第一端连接第一p型重掺杂区43,寄生电阻44的第二端连接寄生npn晶体管的基极。

125.在对本实施例的集成电路的测试结构进行测试前,需要对其进行通电连接,具体的,如图7所示,可以将第一n型重掺杂区41连接电源电压vdd,将第二n型重掺杂区42以及第一p型重掺杂区43连接地端vss。

126.具体的,寄生npn晶体管的基极为p型衬底40,基极到集电极的增益可达数十倍。寄生npn晶体管和寄生电阻44构成的等效电路中,寄生npn晶体管存在两种状态:一种为高阻阻塞态,另一种为低阻闩锁态。当无外界干扰未引起触发时,寄生npn晶体管处于高阻阻塞态,也为寄生npn晶体管的初始状态,此时电流增益非常小,闩锁效应不会产生。当寄生npn晶体管的集电极电流突然增加到预设值时,寄生npn晶体管可能会脱离高阻阻塞态进入低阻闩锁态,此时,寄生npn晶体管会在电源电压vdd和地端vss形成负阻状态,此时,只需要一个非常小的电流就可以持续驱动寄生npn晶体管的放大状态,发射结正偏,集电结反偏,也即形成了闩锁。

127.在对本实施例的集成电路的测试结构进行测试时,在第一距离l1、第二距离l2为第一组设定值时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至2v,监测电源端vdd和接地端vss之间的电流,当电源端vdd和接地端vss之间的电流突然变大时判定此时发生闩锁效应,如此,即可得到第一组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系,也即得到了寄生npn晶体管的闩锁特性。调整第一距离l1和第二距离l2中的至少一个,可以得到第二组设定值,再通过上述的测试方法,即可得到第二组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系。以此类推,可以得到多组对应关系,可以依据得到的对应关系设置具有该测试结构的集成电路的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

128.本实施例提供的集成电路的测试结构,通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生npn晶体管的闩锁特性,据此闩锁特性可以定义具有该测试结构的集成电路的设计规则,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

129.参照图8和图9,本实施例提供一种集成电路的测试结构,包括:第一n型重掺杂区51、第一p型重掺杂区53、以及位于第一n型重掺杂区51和第一p型重掺杂区53之间的第二n型重掺杂区52;其中,第二n型重掺杂区52位于n阱521内,第一n型重掺杂区51和第一p型重掺杂区53均位于p型衬底50上,n阱521位于p型衬底50上;第一n型重掺杂区51和第二n型重掺杂区52之间具有第一距离,第二n型重掺杂区52和第一p型重掺杂区53之间具有第二距离;测试结构用于通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。

130.进一步地,n阱521、第一n型重掺杂区51以及第一p型重掺杂区53构成寄生npn晶体管,测试结构用于测试寄生npn晶体管的闩锁特性。

131.进一步的,p型衬底50具有寄生电阻54,寄生电阻54的第一端连接第一p型重掺杂区53,寄生电阻54的第二端连接寄生npn晶体管的基极。

132.在对本实施例的集成电路的测试结构进行测试前,需要对其进行通电连接,具体

的,如图9所示,可以将第一n型重掺杂区51连接电源电压vdd,将第二n型重掺杂区52以及第一p型重掺杂区53连接地端vss。

133.具体的,寄生npn晶体管的基极为p型衬底50,基极到集电极的增益可达数十倍。寄生npn晶体管和寄生电阻54构成的等效电路中,寄生npn晶体管存在两种状态:一种为高阻阻塞态,另一种为低阻闩锁态。当无外界干扰未引起触发时,寄生npn晶体管处于高阻阻塞态,也为寄生npn晶体管的初始状态,此时电流增益非常小,闩锁效应不会产生。当寄生npn晶体管的集电极电流突然增加到预设值时,寄生npn晶体管可能会脱离高阻阻塞态进入低阻闩锁态,此时,寄生npn晶体管会在电源电压vdd和地端vss形成负阻状态,此时,只需要一个非常小的电流就可以持续驱动寄生npn晶体管的放大状态,发射结正偏,集电结反偏,也即形成了闩锁。

134.在对本实施例的集成电路的测试结构进行测试时,在第一距离l1、第二距离l2为第一组设定值时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至2v,监测电源端vdd和接地端vss之间的电流,当电源端vdd和接地端vss之间的电流突然变大时判定此时发生闩锁效应,如此,即可得到第一组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系,也即得到了寄生npn晶体管的闩锁特性。调整第一距离l1和第二距离l2中的至少一个,可以得到第二组设定值,再通过上述的测试方法,即可得到第二组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系。以此类推,可以得到多组对应关系,可以依据得到的对应关系设置具有该测试结构的集成电路的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

135.本实施例提供的集成电路的测试结构,通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生npn晶体管的闩锁特性,据此闩锁特性可以定义具有该测试结构的集成电路的设计规则,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

136.参照图10和图11,本实施例提供一种集成电路的测试结构,包括:第一n型重掺杂区61、第一p型重掺杂区63、以及位于第一n型重掺杂区61和第一p型重掺杂区63之间的第二n型重掺杂区62;其中,第二n型重掺杂区62位于深n阱621内,第一n型重掺杂区61和第一p型重掺杂区63均位于p型衬底60上,深n阱621位于n阱622内,n阱622位于p型衬底60上;第一n型重掺杂区61和第二n型重掺杂区62之间具有第一距离,第二n型重掺杂区62和第一p型重掺杂区63之间具有第二距离;测试结构用于通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。

137.进一步地,深n阱621、第一n型重掺杂区61以及第一p型重掺杂区63构成寄生npn晶体管;测试结构用于测试寄生npn晶体管的闩锁特性。

138.进一步地,p型衬底60具有寄生电阻64,寄生电阻64的第一端连接第一p型重掺杂区63,寄生电阻64的第二端连接寄生npn晶体管的基极。

139.在对本实施例的集成电路的测试结构进行测试前,需要对其进行通电连接,具体的,如图11所示,可以将第一n型重掺杂区61连接电源电压vdd,将第二n型重掺杂区62以及

第一p型重掺杂区63连接地端vss。

140.具体的,寄生npn晶体管的基极为p型衬底60,基极到集电极的增益可达数十倍。寄生npn晶体管和寄生电阻64构成的等效电路中,寄生npn晶体管存在两种状态:一种为高阻阻塞态,另一种为低阻闩锁态。当无外界干扰未引起触发时,寄生npn晶体管处于高阻阻塞态,也为寄生npn晶体管的初始状态,此时电流增益非常小,闩锁效应不会产生。当寄生npn晶体管的集电极电流突然增加到预设值时,寄生npn晶体管可能会脱离高阻阻塞态进入低阻闩锁态,此时,寄生npn晶体管会在电源电压vdd和地端vss形成负阻状态,此时,只需要一个非常小的电流就可以持续驱动寄生npn晶体管的放大状态,发射结正偏,集电结反偏,也即形成了闩锁。

141.在对本实施例的集成电路的测试结构进行测试时,在第一距离l1、第二距离l2为第一组设定值时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至2v,监测电源端vdd和接地端vss之间的电流,当电源端vdd和接地端vss之间的电流突然变大时判定此时发生闩锁效应,如此,即可得到第一组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系,也即得到了寄生npn晶体管的闩锁特性。调整第一距离l1和第二距离l2中的至少一个,可以得到第二组设定值,再通过上述的测试方法,即可得到第二组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系。以此类推,可以得到多组对应关系,可以依据得到的对应关系设置具有该测试结构的集成电路的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

142.本实施例提供的集成电路的测试结构,通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生npn晶体管的闩锁特性,据此闩锁特性可以定义具有该测试结构的集成电路的设计规则,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

143.参照图12和图13,本实施例提供一种集成电路的测试结构,包括:第一n型重掺杂区71、第一p型重掺杂区73、以及位于第一n型重掺杂区71和第一p型重掺杂区73之间的第二n型重掺杂区72;其中,第一n型重掺杂区71位于第一n阱711内,第二n型重掺杂区72位于第二n阱721内,第一p型重掺杂区73均位于p型衬底70上,第一n阱711和第二n阱721位于p型衬底70上;第一n型重掺杂区71和第二n型重掺杂区72之间具有第一距离,第二n型重掺杂区72和第一p型重掺杂区73之间具有第二距离;测试结构用于通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。

144.进一步地,第一n阱711、第二n阱721以及第一p型重掺杂区73构成寄生npn晶体管;测试结构用于测试寄生npn晶体管的闩锁特性。

145.进一步地,p型衬底70具有寄生电阻74,寄生电阻74的第一端连接第一p型重掺杂区73,寄生电阻74的第二端连接寄生npn晶体管的基极。

146.在对本实施例的集成电路的测试结构进行测试前,需要对其进行通电连接,具体的,如图13所示,可以将第一n型重掺杂区71连接电源电压vdd,将第二n型重掺杂区72以及第一p型重掺杂区73连接地端vss。

147.具体的,寄生npn晶体管的基极为p型衬底70,基极到集电极的增益可达数十倍。寄生npn晶体管和寄生电阻74构成的等效电路中,寄生npn晶体管存在两种状态:一种为高阻阻塞态,另一种为低阻闩锁态。当无外界干扰未引起触发时,寄生npn晶体管处于高阻阻塞态,也为寄生npn晶体管的初始状态,此时电流增益非常小,闩锁效应不会产生。当寄生npn晶体管的集电极电流突然增加到预设值时,寄生npn晶体管可能会脱离高阻阻塞态进入低阻闩锁态,此时,寄生npn晶体管会在电源电压vdd和地端vss形成负阻状态,此时,只需要一个非常小的电流就可以持续驱动寄生npn晶体管的放大状态,发射结正偏,集电结反偏,也即形成了闩锁。

148.在对本实施例的集成电路的测试结构进行测试时,在第一距离l1、第二距离l2为第一组设定值时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至2v,监测电源端vdd和接地端vss之间的电流,当电源端vdd和接地端vss之间的电流突然变大时判定此时发生闩锁效应,如此,即可得到第一组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系,也即得到了寄生npn晶体管的闩锁特性。调整第一距离l1和第二距离l2中的至少一个,可以得到第二组设定值,再通过上述的测试方法,即可得到第二组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系。以此类推,可以得到多组对应关系,可以依据得到的对应关系设置具有该测试结构的集成电路的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

149.本实施例提供的集成电路的测试结构,通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生npn晶体管的闩锁特性,据此闩锁特性可以定义具有该测试结构的集成电路的设计规则,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

150.参照图14和图15,本实施例提供一种集成电路的测试结构,包括:第一n型重掺杂区81、第一p型重掺杂区83、以及位于第一n型重掺杂区81和第一p型重掺杂区83之间的第二n型重掺杂区82;其中,第一n型重掺杂区81位于第一n阱811内,第二n型重掺杂区82位于深n阱821内,第一p型重掺杂区83均位于p型衬底80上,第一n阱811位于p型衬底80上,深n阱821位于第二n阱822内,第二n阱822位于p型衬底80上;第一n型重掺杂区81和第二n型重掺杂区82之间具有第一距离,第二n型重掺杂区82和第一p型重掺杂区83之间具有第二距离;测试结构用于通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。

151.进一步地,第一n阱811、深n阱821以及第一p型重掺杂区83构成寄生npn晶体管;测试结构用于测试寄生npn晶体管的闩锁特性。

152.进一步地,p型衬底80具有寄生电阻84,寄生电阻84的第一端连接第一p型重掺杂区83,寄生电阻84的第二端连接寄生npn晶体管的基极。

153.在对本实施例的集成电路的测试结构进行测试前,需要对其进行通电连接,具体的,如图15所示,可以将第一n型重掺杂区81连接电源电压vdd,将第二n型重掺杂区82以及第一p型重掺杂区83连接地端vss。

154.具体的,寄生npn晶体管的基极为p型衬底80,基极到集电极的增益可达数十倍。寄生npn晶体管和寄生电阻84构成的等效电路中,寄生npn晶体管存在两种状态:一种为高阻阻塞态,另一种为低阻闩锁态。当无外界干扰未引起触发时,寄生npn晶体管处于高阻阻塞态,也为寄生npn晶体管的初始状态,此时电流增益非常小,闩锁效应不会产生。当寄生npn晶体管的集电极电流突然增加到预设值时,寄生npn晶体管可能会脱离高阻阻塞态进入低阻闩锁态,此时,寄生npn晶体管会在电源电压vdd和地端vss形成负阻状态,此时,只需要一个非常小的电流就可以持续驱动寄生npn晶体管的放大状态,发射结正偏,集电结反偏,也即形成了闩锁。

155.在对本实施例的集成电路的测试结构进行测试时,在第一距离l1、第二距离l2为第一组设定值时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至2v,监测电源端vdd和接地端vss之间的电流,当电源端vdd和接地端vss之间的电流突然变大时判定此时发生闩锁效应,如此,即可得到第一组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系,也即得到了寄生npn晶体管的闩锁特性。调整第一距离l1和第二距离l2中的至少一个,可以得到第二组设定值,再通过上述的测试方法,即可得到第二组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系。以此类推,可以得到多组对应关系,可以依据得到的对应关系设置具有该测试结构的集成电路的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

156.本实施例提供的集成电路的测试结构,通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生npn晶体管的闩锁特性,据此闩锁特性可以定义具有该测试结构的集成电路的设计规则,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

157.参照图16和图17,本实施例提供一种集成电路的测试结构,包括:第一n型重掺杂区91、第一p型重掺杂区93、以及位于第一n型重掺杂区91和第一p型重掺杂区93之间的第二n型重掺杂区92;其中,第二n型重掺杂区92位于第一n阱921内,第一n型重掺杂区91位于深n阱911内,第一p型重掺杂区93均位于p型衬底90上,第一n阱921位于p型衬底90上,深n阱911位于第二n阱912内,第二n阱912位于p型衬底90上;第一n型重掺杂区91和第二n型重掺杂区92之间具有第一距离,第二n型重掺杂区92和第一p型重掺杂区93之间具有第二距离;测试结构用于通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。

158.进一步地,第一n阱921、深n阱911以及第一p型重掺杂区93构成寄生npn晶体管;测试结构用于测试寄生npn晶体管的闩锁特性。

159.进一步地,p型衬底90具有寄生电阻94,寄生电阻94的第一端连接第一p型重掺杂区93,寄生电阻94的第二端连接寄生npn晶体管的基极。

160.在对本实施例的集成电路的测试结构进行测试前,需要对其进行通电连接,具体的,如图17所示,可以将第一n型重掺杂区91连接电源电压vdd,将第二n型重掺杂区92以及第一p型重掺杂区93连接地端vss。

161.具体的,寄生npn晶体管的基极为p型衬底90,基极到集电极的增益可达数十倍。寄生npn晶体管和寄生电阻94构成的等效电路中,寄生npn晶体管存在两种状态:一种为高阻阻塞态,另一种为低阻闩锁态。当无外界干扰未引起触发时,寄生npn晶体管处于高阻阻塞态,也为寄生npn晶体管的初始状态,此时电流增益非常小,闩锁效应不会产生。当寄生npn晶体管的集电极电流突然增加到预设值时,寄生npn晶体管可能会脱离高阻阻塞态进入低阻闩锁态,此时,寄生npn晶体管会在电源电压vdd和地端vss形成负阻状态,此时,只需要一个非常小的电流就可以持续驱动寄生npn晶体管的放大状态,发射结正偏,集电结反偏,也即形成了闩锁。

162.在对本实施例的集成电路的测试结构进行测试时,在第一距离l1、第二距离l2为第一组设定值时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至2v,监测电源端vdd和接地端vss之间的电流,当电源端vdd和接地端vss之间的电流突然变大时判定此时发生闩锁效应,如此,即可得到第一组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系,也即得到了寄生npn晶体管的闩锁特性。调整第一距离l1和第二距离l2中的至少一个,可以得到第二组设定值,再通过上述的测试方法,即可得到第二组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系。以此类推,可以得到多组对应关系,可以依据得到的对应关系设置具有该测试结构的集成电路的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

163.本实施例提供的集成电路的测试结构,通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生npn晶体管的闩锁特性,据此闩锁特性可以定义具有该测试结构的集成电路的设计规则,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

164.参照图18和图19,本实施例提供一种集成电路的测试结构,包括:第一n型重掺杂区101、第一p型重掺杂区103、以及位于第一n型重掺杂区101和第一p型重掺杂区103之间的第二n型重掺杂区102;其中,第一n型重掺杂区101位于第一深n阱1011内,第二n型重掺杂区102位于第二深n阱1021内,第一p型重掺杂区103均位于p型衬底100上,第一深n阱1011位于第一n阱1012内,第二深n阱1021位于第二n阱1022内,第一n阱1012和第二n阱1022位于p型衬底100上;第一n型重掺杂区101和第二n型重掺杂区102之间具有第一距离,第二n型重掺杂区102和第一p型重掺杂区103之间具有第二距离;测试结构用于通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。

165.进一步地,第一深n阱1011、第二深n阱1021以及第一p型重掺杂区103构成寄生npn晶体管;测试结构用于测试寄生npn晶体管的闩锁特性。

166.进一步地,p型衬底100具有寄生电阻104,寄生电阻104的第一端连接第一p型重掺杂区103,寄生电阻104的第二端连接寄生npn晶体管的基极。

167.在对本实施例的集成电路的测试结构进行测试前,需要对其进行通电连接,具体的,如图19所示,可以将第一n型重掺杂区101连接电源电压vdd,将第二n型重掺杂区102以及第一p型重掺杂区103连接地端vss。

168.具体的,寄生npn晶体管的基极为p型衬底100,基极到集电极的增益可达数十倍。寄生npn晶体管和寄生电阻104构成的等效电路中,寄生npn晶体管存在两种状态:一种为高阻阻塞态,另一种为低阻闩锁态。当无外界干扰未引起触发时,寄生npn晶体管处于高阻阻塞态,也为寄生npn晶体管的初始状态,此时电流增益非常小,闩锁效应不会产生。当寄生npn晶体管的集电极电流突然增加到预设值时,寄生npn晶体管可能会脱离高阻阻塞态进入低阻闩锁态,此时,寄生npn晶体管会在电源电压vdd和地端vss形成负阻状态,此时,只需要一个非常小的电流就可以持续驱动寄生npn晶体管的放大状态,发射结正偏,集电结反偏,也即形成了闩锁。

169.在对本实施例的集成电路的测试结构进行测试时,在第一距离l1、第二距离l2为第一组设定值时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至2v,监测电源端vdd和接地端vss之间的电流,当电源端vdd和接地端vss之间的电流突然变大时判定此时发生闩锁效应,如此,即可得到第一组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系,也即得到了寄生npn晶体管的闩锁特性。调整第一距离l1和第二距离l2中的至少一个,可以得到第二组设定值,再通过上述的测试方法,即可得到第二组设定值与发生闩锁效应的触发电压、维持闩锁效应的维持电压、闩锁效应触发时的电流和闩锁效应维持阶段的电流具有的对应关系。以此类推,可以得到多组对应关系,可以依据得到的对应关系设置具有该测试结构的集成电路的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

170.本实施例提供的集成电路的测试结构,通过调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数。这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生npn晶体管的闩锁特性,据此闩锁特性可以定义具有该测试结构的集成电路的设计规则,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

171.本领域技术人员可以清楚地了解到,为描述的方便和简洁,仅以上述各功能模块的划分进行举例说明,实际应用中,可以根据需要而将上述功能分配由不同的功能模块完成,即将装置的内部结构划分成不同的功能模块,以完成以上描述的全部或者部分功能。上述描述的装置的具体工作过程,可以参考前述方法实施例中的对应过程,在此不再赘述。

172.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。