技术特征:

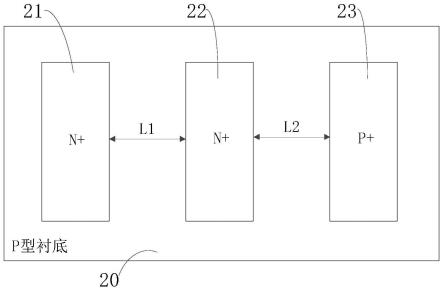

1.一种集成电路的测试结构,其特征在于,包括:第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;其中,所述第一n型重掺杂区、所述第二n型重掺杂区和所述第一p型重掺杂区均位于p型衬底上;所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。2.根据权利要求1所述的集成电路的测试结构,其特征在于,所述第一n型重掺杂区、所述第二n型重掺杂区以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。3.根据权利要求2所述的集成电路的测试结构,其特征在于,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。4.一种集成电路的测试结构,其特征在于,包括:第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;其中,所述第一n型重掺杂区位于n阱内,所述第二n型重掺杂区和所述第一p型重掺杂区均位于p型衬底上,所述n阱位于所述p型衬底上;所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。5.根据权利要求4所述的集成电路的测试结构,其特征在于,所述n阱、所述第二n型重掺杂区以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。6.根据权利要求5所述的集成电路的测试结构,其特征在于,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。7.一种集成电路的测试结构,其特征在于,包括:第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;其中,所述第一n型重掺杂区位于深n阱内,所述第二n型重掺杂区和所述第一p型重掺杂区均位于p型衬底上,所述深n阱位于n阱内,所述n阱位于所述p型衬底上;所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。8.根据权利要求7所述的集成电路的测试结构,其特征在于,所述深n阱、所述第二n型

重掺杂区以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。9.根据权利要求8所述的集成电路的测试结构,其特征在于,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。10.一种集成电路的测试结构,其特征在于,包括:第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;其中,所述第二n型重掺杂区位于n阱内,所述第一n型重掺杂区和所述第一p型重掺杂区均位于p型衬底上,所述n阱位于所述p型衬底上;所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。11.根据权利要求10所述的集成电路的测试结构,其特征在于,所述n阱、所述第一n型重掺杂区以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。12.根据权利要求11所述的集成电路的测试结构,其特征在于,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。13.一种集成电路的测试结构,其特征在于,包括:第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;其中,所述第二n型重掺杂区位于深n阱内,所述第一n型重掺杂区和所述第一p型重掺杂区均位于p型衬底上,所述深n阱位于n阱内,所述n阱位于所述p型衬底上;所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。14.根据权利要求13所述的集成电路的测试结构,其特征在于,所述深n阱、所述第一n型重掺杂区以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。15.根据权利要求14所述的集成电路的测试结构,其特征在于,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。16.一种集成电路的测试结构,其特征在于,包括:第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;其中,所述第一n型重掺杂区位于第一n阱内,所述第二n型重掺杂区位于第二n阱内,所

述第一p型重掺杂区均位于p型衬底上,所述第一n阱和所述第二n阱位于所述p型衬底上;所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。17.根据权利要求16所述的集成电路的测试结构,其特征在于,所述第一n阱、所述第二n阱以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。18.根据权利要求17所述的集成电路的测试结构,其特征在于,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。19.一种集成电路的测试结构,其特征在于,包括:第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;其中,所述第一n型重掺杂区位于第一n阱内,所述第二n型重掺杂区位于深n阱内,所述第一p型重掺杂区均位于p型衬底上,所述第一n阱位于所述p型衬底上,所述深n阱位于第二n阱内,所述第二n阱位于所述p型衬底上;所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。20.根据权利要求19所述的集成电路的测试结构,其特征在于,所述第一n阱、所述深n阱以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。21.根据权利要求20所述的集成电路的测试结构,其特征在于,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。22.一种集成电路的测试结构,其特征在于,包括:第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;其中,所述第二n型重掺杂区位于第一n阱内,所述第一n型重掺杂区位于深n阱内,所述第一p型重掺杂区均位于p型衬底上,所述第一n阱位于所述p型衬底上,所述深n阱位于第二n阱内,所述第二n阱位于所述p型衬底上;所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。23.根据权利要求22所述的集成电路的测试结构,其特征在于,所述第一n阱、所述深n阱以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶

体管的闩锁特性。24.根据权利要求23所述的集成电路的测试结构,其特征在于,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。25.一种集成电路的测试结构,其特征在于,包括:第一n型重掺杂区、第一p型重掺杂区、以及位于所述第一n型重掺杂区和所述第一p型重掺杂区之间的第二n型重掺杂区;其中,所述第一n型重掺杂区位于第一深n阱内,所述第二n型重掺杂区位于第二深n阱内,所述第一p型重掺杂区均位于p型衬底上,所述第一深n阱位于第一n阱内,所述第二深n阱位于第二n阱内,所述第一n阱和所述第二n阱位于所述p型衬底上;所述第一n型重掺杂区和所述第二n型重掺杂区之间具有第一距离,所述第二n型重掺杂区和所述第一p型重掺杂区之间具有第二距离;所述测试结构用于通过调整所述第一距离和所述第二距离中的至少一个,测试所述测试结构对应的集成电路的电学参数。26.根据权利要求25所述的集成电路的测试结构,其特征在于,所述第一深n阱、所述第二深n阱以及所述第一p型重掺杂区构成寄生npn晶体管;所述测试结构用于测试所述寄生npn晶体管的闩锁特性。27.根据权利要求26所述的集成电路的测试结构,其特征在于,所述p型衬底具有寄生电阻,所述寄生电阻的第一端连接所述第一p型重掺杂区,所述寄生电阻的第二端连接所述寄生npn晶体管的基极。

技术总结

本发明实施例涉及集成电路技术领域,具体涉及一种集成电路的测试结构。本发明实施例旨在解决相关技术中缺少集成电路的测试结构的问题。集成电路的测试结构中,第一N型重掺杂区和第二N型重掺杂区之间具有第一距离,第二N型重掺杂区和第一P型重掺杂区之间具有第二距离;调整第一距离和第二距离中的至少一个,测试测试结构对应的集成电路的电学参数,这些电学参数与对应的第一距离、第二距离之间的对应关系即可表征寄生NPN晶体管的闩锁特性,据此闩锁特性可以设置具有该测试结构的集成电路的第一距离和第二距离,从而避免具有该测试结构的集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。芯片的可靠性。芯片的可靠性。

技术研发人员:许杞安

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:2021.05.19

技术公布日:2022/11/22

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。