soc芯片内建测试电路、soc芯片及测试方法

技术领域

1.本发明涉及电子芯片技术领域,更具体地说,涉及一种soc芯片内建测试电路、soc芯片及测试方法。

背景技术:

2.芯片生产出来以后,要做详细的测试,满足标准才能够使用,其中cp(chipprobing)指的是晶圆测试,cp测试在整个芯片制作流程中处于晶圆制造和封装之间;封装以后的测试叫做ft(finaltest),是芯片在出厂前最后一道测试工序。

3.无论是cp还是ft测试,都会影响芯片的生产成本,影响的原因是cp和ft的测试时间,长的测试时间意味着高成本,测试时间越短,则测试成本越低,所以要尽可能的缩短芯片测试时间;soc芯片通常是由数字电路和模拟电路组成,数字电路例如mcu(microcontrollerunit)提供数字运算,模拟电路提供数字电路所需的电压和时钟,以及模拟信号处理等功能,模拟电路的性能除了和电路本身的功能有关,也受版图布局,半导体制造,封装等因素影响,这些因素使得模拟电路的性能指标在每颗芯片之间会存在差异,这些差异有大有小,需要在cp和ft的阶段对芯片进行校准,以使得经过校准后的芯片的片间差异足够小能够符合出货要求,如何减少校准时间,也就是如何快速校准模拟电压和时钟一直是业界难题。

4.芯片带有校准的模拟电路会有一组nbit的校准位,n为正整数,改变校准位,电路的性能会以最小的步进进行调整,校准位的默认值通常是中心值,这样上下的可调整的幅度是最大的;业界常用的校准方法是,在cp/ft阶段使用ate(automatictestequipment)自动测试机台,将需要校准的信号量,例如电压信号或者频率信号输出到测试机的测量端口,然后通过人工测量每个校准位的信号量的值,最终筛选最接近信号电压或者频率的校准值,即完成校准,这个过程一般会使用二分法来完成。

5.使用ate测试机二分法的测试流程如图1所示:对芯片写入校准值,等待信号输出后测量,再写入下一次的校准值,每次写校准值都是通过机台下发测试命令到芯片,命令的传输需要时间,信号输出后ate机台测量也需要时间,整个测试过程ate测试机台和芯片的交互次数过多,测量的次数过多,降低了测试效率;如图1所示,只有芯片输出待测量是芯片内部完成,其他步骤均需要ate测试机台参与,可以看出nbit的校准值,需要至少n/2次的测试交互测试,才能完成二分法测量,这里面需要机台发送n/2次校准值,测量n/2次。

6.因而,需要一种改进的soc芯片内建测试电路及方法解决上述问题,降低测试成本并提高生产效率。

技术实现要素:

7.本发明要解决的技术问题在于,针对现有技术的上述缺陷,提供一种soc芯片内建

测试电路,还提供了一种soc芯片及一种soc芯片测试方法。

8.本发明解决其技术问题所采用的技术方案是:构造一种soc芯片内建测试电路,其中,包括命令解析模块、二分法算法模块以及电压和频率比较器模块;所述命令解析模块,解析外部的校准测试命令、设置初始校准值和后续的校准值,以及读取校准结果和校准值;校准结果代表当前校准成功或者失败,当校准成功时校准值为二分法的正确校准结果;所述电压和频率比较器模块,包括模拟电压比较器和频率计数器;所述模拟电压比较器用于进行输入基准电压与所述命令解析模块设置的相应类型的校准值比对判断,以及控制所述二分法算法模块进行二分法校准计算;所述频率计数器用于进行输入基准时钟与所述命令解析模块设置的相应类型的校准值比对判断,以及控制所述二分法算法模块进行二分法校准计算;所述二分法算法模块,用于完成二分法校准算法的计算获得校准中间值;所述命令解析模块依据所述校准中间值设定后续的校准值。

9.本发明所述的soc芯片内建测试电路,其中,所述模拟电压比较器包括正端电压输入端口和负端电压输入端口;通过正端电压输入端口输入电压和负端电压输入端口输入电压的大小关系,输出高低电平来控制二分法算法模块进行二分法校准计算。

10.本发明所述的soc芯片内建测试电路,其中,所述频率计数器通过输入基准时钟频率量对待校准的时钟频率量进行计数,获得待校准的时钟频率量与基准时钟频率量的差值,通过差值控制二分法算法模块进行二分法校准计算。

11.本发明所述的soc芯片内建测试电路,其中,所述校准测试命令格式采用格式opcode dummy data;其中,opcode代表发送的校准指令,data为最终读取的校准结果和校准值,dummy是校准需要等待的时间。

12.一种soc芯片测试方法,应用于如上述的soc芯片内建测试电路,其包括以下步骤:接收外部输入的校准命令,接收外部输入基准值,基准值为基准电压或基准时钟;对校准命令进行解析,设置与基准值相应类型的校准初值,开始校准;判断校准初值与基准值之间差值是否在设定范围内,是则保存校准结果和校准初值,结束校准,否则判断二分法计算次数是否达到最大值,是则保存校准结果和校准初值,结束校准,否则进行二分法计算得到中间校准值,依据中间校准值确定下一校准值;判断校准值与基准值之间差值是否在设定范围内,是则保存校准结果和校准值,结束校准,否则判断二分法计算次数是否达到最大值,是则保存校准结果和校准值,结束校准,否则进行二分法计算得到中间校准值,依据中间校准值确定下一校准值;重复上一步骤至结束校准。

13.一种soc芯片,其中,所述soc芯片上设置有如上述的soc芯片内建测试电路。

14.本发明的有益效果在于:通过在soc芯片内部内置了一个est自动校准电路,即可在soc芯片内部完成电压和频率的二分法校准,与最好的现有技术相比,测量过程在soc芯片内部完成,有如下的优点:减少ate测试机台和芯片交互次数,减少外部ate机台连线噪声干扰,提高测量精度,减少待测量的测量时间。

附图说明

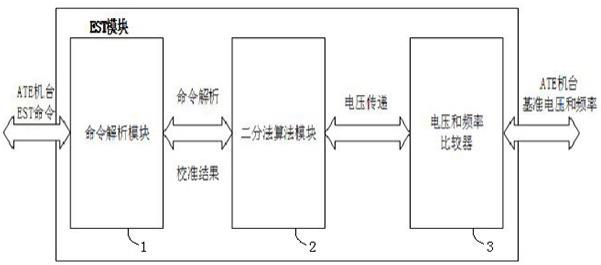

15.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将结合附图及实施例对本发明作进一步说明,下面描述中的附图仅仅是本发明的部分实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他附图:图1是现有的ate测试机二分法的测试流程图;图2是本发明较佳实施例的soc芯片内建测试电路;图3是本发明较佳实施例的soc芯片二分法的测试流程原理图。

具体实施方式

16.为了使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本发明的部分实施例,而不是全部实施例。基于本发明的实施例,本领域普通技术人员在没有付出创造性劳动的前提下所获得的所有其他实施例,都属于本发明的保护范围。

17.本发明较佳实施例的soc芯片内建测试电路,如图2所示,包括命令解析模块1、二分法算法模块2以及电压和频率比较器模块3;命令解析模块1、二分法算法模块2以及电压和频率比较器模块3构成est自动校准电路;命令解析模块1,解析外部的校准测试命令、设置初始校准值和后续的校准值,以及读取校准结果和校准值;校准结果代表当前校准成功或者失败,当校准成功时校准值为二分法的正确校准结果;电压和频率比较器模块3,包括模拟电压比较器和频率计数器;模拟电压比较器用于进行输入基准电压与命令解析模块设置的相应类型的校准值比对判断,以及控制二分法算法模块进行二分法校准计算;频率计数器用于进行输入基准时钟与命令解析模块设置的相应类型的校准值比对判断,以及控制二分法算法模块进行二分法校准计算;二分法算法模块2,用于完成二分法校准算法的计算获得校准中间值;命令解析模块依据校准中间值设定后续的校准值;通过在soc芯片内部内置了一个est自动校准电路,即可在soc芯片内部完成电压和频率的二分法校准,与最好的现有技术相比,测量过程在soc芯片内部完成,有如下的优点:1.减少ate测试机台和芯片交互次数;使用内建est的soc芯片的校准流程如下,ate机台和芯片的交互仅需要提供一个基准电压或者频率,然后下发一次校准命令,然后等待校准完成即可,使得ate机台和soc芯片的校准交互次数从n/2次,减少为1次,ate机台的测量变为soc芯片内测量;2.减少外部ate机台连线噪声干扰,提高测量精度;ate测试机台和芯片之间通过排线忽略,这些排线通常比较长,有寄生的电阻和电容,电感,再加上机台的噪声干扰,对信号量的测量精度有一定的影响。soc片内测量的好处是,待测信号不需要经过排线,soc芯片内部噪声较小,可以提升校准精度;3.减少待测量的测量时间;减少待测量的测试时间,因为ate测试机台的测量通道

是多个功能通过继电器进行切换,例如测量电压时,不能测量频率,测量频率时,不能测量电压,ate测试机台通过继电器切换功能时,也需要消耗时间。

18.例如以下代码,是某业界领先芯片自动化测试设备生产商的的ate测试机台的测试代码,功能是用来测量电压,每次测量时需要先将通道从pdcl(pindriver,comparatorandactiveload)普通io切换到pmu(precisionmeasurementunit)精确测量单元,然后设置pmu驱动-200ua电流,再测量电压是否在-1.2v和-0.2v之间,最后关闭pmu,切换至pdcl,这样做的原因是为了保护ate测试机台的测量通道不被误损坏,整个过程需要至少8个ms,这仅仅是测量一次的延迟,如果是二分法测量,则需要(n/2)*8ms。

19.relay_off(pin_defs,pdcl,1ms);//关闭pdcl继电器relay_on(pin_defs,pmu,1ms);//打开pmu继电器force_i_pmu(pmu,-200ua,@1ma,@6v,2v,on,1ms);judge_v_pmu(pmu,ifvm,-1.2v,-0.2v,2ms);force_i_pmu(pmu,0ua,@100ua,@6v,2v,off,1ms);relay_off(pin_defs,pmu,1ms);relay_on(pin_defs,pdcl,1ms);使用本发明的内建est模块测量电压,以上的测量步骤放在芯片内部完成,一个普通的电压比较器,在1ms的时间内比较出结果(可以更快),这样二分法的测试时间片内为n/2*1ms,比使用ate机台二分法减少了(n/2-1)*7ms的时间。

20.优选的,模拟电压比较器包括正端电压输入端口和负端电压输入端口;通过正端电压输入端口输入电压和负端电压输入端口输入电压的大小关系,输出高低电平来控制二分法算法模块进行二分法校准计算;模拟电压比较器有两个电压输入端口,一个为正端,一个为负端,当正端输入电压大于负端输入电压时,输出为电平1,当负端输入电压大于正端输入电压时输出为电平0,在est模块通过判断电压比较器的输出电平,自动决定二分法下次的校准值。

21.优选的,频率计数器通过输入基准时钟频率量对待校准的时钟频率量进行计数,获得待校准的时钟频率量与基准时钟频率量的差值,通过差值控制二分法算法模块进行二分法校准计算;频率计数器,是使用机台外灌的基准频率量对待校准的时钟频率量进行计数,从而可以得知待校准的时钟频率量与基准频率量的差值,例如待校准频率为1khz,外灌1mhz的基准时钟,那么理论上的计数值应该是1000,在est模块内部通过比较实际计数值和1000的差值,决定二分法下次的校准值。

22.模拟电压比较器和频率计数器采用业界通用的设备即可;优选的,校准测试命令格式采用格式opcode dummy data;其中,opcode代表发送的校准指令,data为最终读取的校准结果和校准值,dummy是校准需要等待的时间;ate机台发送的est命令可以使用任意的通讯接口,例如spi接口,校准测试命令的设计分为操作码opcode dummy data;opcode代表发送的校准指令,data为最终读取的校准结果和校准值。dummy是校准需要等待的时间,可以根据校准量的不同,动态调整,例如校准n=8的校准电压值和n=7的频率校准值,通过调整dummy的周期数,使得等待校准的时长最短最优。

23.一种soc芯片测试方法,如图3所示,应用于如上述的soc芯片内建测试电路,其包括以下步骤:接收外部输入的校准命令,接收外部输入基准值,基准值为基准电压或基准时钟;对校准命令进行解析,设置与基准值相应类型的校准初值,开始校准;判断校准初值与基准值之间差值是否在设定范围内,是则保存校准结果和校准初值,结束校准,否则判断二分法计算次数是否达到最大值,是则保存校准结果和校准初值,结束校准,否则进行二分法计算得到中间校准值,依据中间校准值确定下一校准值;判断校准值与基准值之间差值是否在设定范围内,是则保存校准结果和校准值,结束校准,否则判断二分法计算次数是否达到最大值,是则保存校准结果和校准值,结束校准,否则进行二分法计算得到中间校准值,依据中间校准值确定下一校准值;重复上一步骤至结束校准;通过在soc芯片内部内置了一个est自动校准电路,即可在soc芯片内部完成电压和频率的二分法校准,与最好的现有技术相比,测量过程在soc芯片内部完成,有如下的优点:减少ate测试机台和芯片交互次数,减少外部ate机台连线噪声干扰,提高测量精度,减少待测量的测量时间;一种soc芯片,其中,soc芯片上设置有如上述的soc芯片内建测试电路。

24.应当理解的是,对本领域普通技术人员来说,可以根据上述说明加以改进或变换,而所有这些改进和变换都应属于本发明所附权利要求的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。