1.本发明涉及集成电路,更具体地,涉及一种欠压锁定电路。

背景技术:

2.目前,当芯片的电源电压低于额定电压时,芯片的输出端会处于异常状态。通常,可以通过增加欠压锁定(uvlo,under voltage lock-out)电路,当识别到芯片的电源电压低于一个设定阈值时,将输出端锁定,从而确保了电路不会发生误动作的现象。

3.然而,现有技术中的欠压锁定电路,通常是采用分压电阻对电源电压进行分压,并将分压后得到的电压与基准电压进行比较。当分压大于基准电压时,uvlo电路会处于正常工作状态,当分压小于基准电压时,uvlo电路就会执行锁定功能。在这类电路中,由于采用了电阻进行分压,这使得芯片的版图面积难以减小,同时电阻又浪费了大量功耗,电源效率难以降低。

4.因此,亟需一种新的欠压锁定电路。

技术实现要素:

5.为解决现有技术中存在的不足,本发明的目的在于,提供一种欠压锁定电路,通过pmos管和次级电流源实现分压以及基本的欠压锁定逻辑。

6.本发明采用如下的技术方案。

7.本发明中涉及一种欠压锁定电路,电路包括分压锁定单元、反馈锁定单元和反相级联单元;其中,分压锁定单元,与带隙基准源电路、电源电压、反馈锁定单元和反相级联单元连接,用于基于电源电压和分压锁定单元中次级电流源的电压实现分压,并将分压信号输入至反相级联单元中;反馈锁定单元,分别与分压锁定单元、反相级联单元连接,用于提供滞回信号以稳定分压信号;反相级联单元,整形并放大稳定后的分压信号,以基于分压信号生成欠压锁定输出。

8.优选地,分压锁定单元包括pmos管和次级电流源;其中,pmos管,基于来自带隙基准源的参考电压和电源电压的比较,实现截止或导通状态;次级电流源,基于其所生成的电压和电源电压的比较,实现分压信号的输出。

9.优选地,pmos管的栅极与带隙基准源电路连接,接收来自带隙基准源电路的参考电压v

ref

;pmos管的源极与电源电压连接,接收电源电压;pmos管的漏极与次级电流源同时连接到锁定单元中。

10.优选地,次级电流源,一端接地,另一端与pmos管的漏极、锁定单元的输入端分别连接。

11.优选地,反馈锁定单元包括nmos管;其中,nmos管,基于反相级联单元中第一反相放大器输出的锁定信号实现截止或导通状态;在处于导通状态时,nmos管与次级电流源一同拉低来自分压锁定单元的分压信号的电位,以确保欠压锁定输出为闭锁信号;在处于截止时,次级电流源独自拉低分压锁定单元的分压信号的电位,用以设定欠压锁定输出的门

限电压。

12.优选地,nmos管的漏极分别与分压锁定单元的输出端、第一反相放大器的输入端连接;nmos管的栅极分别与第一反相放大器的输出端、第二反相放大器输入端的连接;nmos管的源极接地。

13.优选地,反相级联单元包括第一反相放大器和第二反相放大器;其中,第一反相放大器和第二反相放大器串联,第一反相放大器的输入端作为所述反相级联单元的输入端,第二反相放大器的输出端作为所述反相级联单元的输出端。

14.优选地,当电源电压v

in

与来自带隙基准源的参考电压v

ref

之差大于pmos管的栅源极导通电压时,pmos管处于导通状态;当电源电压v

in

与来自带隙基准源的参考电压v

ref

之差小于pmos管的栅源极导通电压时,pmos管处于截止状态。

15.优选地,次级电流源的输出电流为100na。

16.优选地,当分压锁定单元的输出电压大于或等于门限电压时,nmos管截止,反相级联单元输出开启信号;当分压锁定单元的输出电压低于门限电压时,nmos管导通,反相级联单元输出闭锁信号。

17.本发明的有益效果在于,与现有技术相比,本发明中的一种欠压锁定电路,能够通过pmos管和次级电流源实现对电源电压的分压,从而替代了现有技术中耗费芯片版图和电源功率的分压电阻。因此,本发明中的方法能够实现且适用于功耗低、面积小的芯片,从而扩大了uvlo电路的利用范围。

18.本发明的有益效果还包括:

19.1、本发明中一种欠压锁定电路,能够通过分压锁定单元和反馈锁定单元实现对欠压锁定逻辑的判定。并且,由于电路中增加了栅极与第一反相器输出端相连接的nmos管,起到滞回作用,从而防止了带隙基准源电路的参考电压vref在发生高低电平翻转时发生抖动所导致的欠压锁定输出信号的振荡。因此,本发明中的欠压锁定逻辑相比现有技术更加准确。

20.2、本发明电路中的反相级联单元中,串联有第一和第二反相器,并通过反相器的级联实现了对输入波形的整形,从而输出更为标准的欠压锁定电平信号。另外,两个反相器级联还平衡了输出信号的延时。

21.3、本发明电路中的nmos管,能够在输入并非欠压状态时处于截止状态,从而配合pmos管、电流源精确地确定出该电路中欠压锁定逻辑的门限电压。同时在输入欠压时,处于导通状态,进一步拉低电位,以实现电路的闭锁功能。

22.4、由于本发明中采用nmos管,因此可以将门限电压设置的更大或更小,同时也扩大了电流源的选型范围,例如即使采用基准电流较小的电流源,也能够充分实现欠压锁定的功能。

附图说明

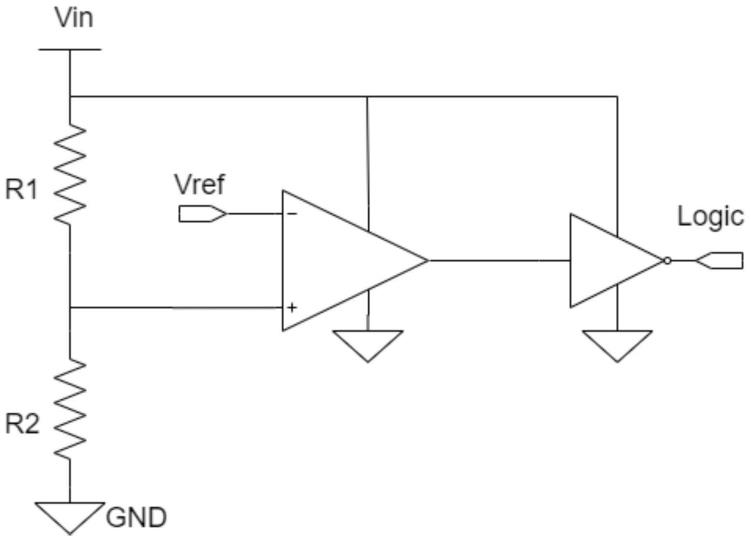

23.图1为本发明现有技术中的一种欠压锁定电路的电路结构示意图;

24.图2为本发明中一种新的欠压锁定电路的电路结构示意图。

具体实施方式

25.下面结合附图对本技术作进一步描述。以下实施例仅用于更加清楚地说明本发明的技术方案,而不能以此来限制本技术的保护范围。

26.图1为本发明现有技术中的一种欠压锁定电路的电路结构示意图。如图1所示,现有技术中通用的欠压锁定电路,通常是先经过分压电阻r1和r2对输入电压v

in

进行分压,而后将分压与参考基准电压v

ref

进行比较,在将比较放大结果输出至反相器中实现欠压锁定逻辑。

27.在图1中所示的现有技术中常用的欠压锁定电路中,由于电源电压通常要高于欠压锁定的参考基准电压,因此,需要采用电阻实现分压。通过生成一个合适的分压电位,实现该分压电位与参考基准电压进行比较,并通过比较的逻辑控制电路的输出。为了确保电路的安全,保证该欠压锁定电路的能量消耗足够小,需要为电路提供足够小的电流。

28.例如,预设该欠压锁定电路的工作电流为1ua左右,这就要求用于分压的电阻的阻值需要比较大才行。例如,当电源电压为3v左右时,如果希望工作电流在1ua左右,就需要两个分压电阻的电阻值之和为3m欧姆左右。若是还希望继续降低电路中的电流,电阻的取值就需要更大。这使得分压电阻大幅增加了芯片的静态功耗,大的电阻值也占用了过多的版图面积,使得芯片的面积无法进一步地缩小。

29.基于上述问题,本发明提供了一种欠压锁定电路的新方案。

30.图2为本发明中一种新的欠压锁定电路的电路结构示意图。如图2所示,一种欠压锁定电路,电路包括分压锁定单元、反馈锁定单元和反相级联单元;其中,分压锁定单元,与带隙基准源电路、电源电压、反馈锁定单元和反相级联单元连接,用于基于电源电压和分压锁定单元中次级电流源的电压实现分压,并将分压信号输入至反相级联单元中;反馈锁定单元,分别与分压锁定单元、反相级联单元连接,用于提供滞回信号以稳定分压信号;反相级联单元,整形并放大稳定后的分压信号,以基于分压信号生成欠压锁定输出。

31.具体来说,该电路中的分压锁定单元,用于对输入的较大的电压进行分压,同时实现欠压锁定逻辑的判断。例如,通过调节其pmos管的器件参数,设置出合理且准确的欠压锁定电路中的欠压锁定的阈值电压。即,当电路中的分压小于该阈值电压时,则输出锁定信号以闭锁后续电路,当电路中的分压大于该阈值电压时,则输出非锁定信号,使后续电路正常工作。

32.反馈锁定单元,则可以通过调节其nmos管的参数,限制欠压锁定信号值的上限。具体来说,分压锁定单元中的nmos管,用于滞回来自反相级联单元中第一反相放大器的输出端信号,并稳定反相级联单元输入端的信号抖动。分压锁定单元输出的信号,会随着电源电压的变化发生高低电平的翻转,并且,由于上级电路等的各种影响,在发生高低电平切换时,分压锁定单元输出的信号会发生一定程度的抖动。例如,在远小于高低电平转换周期的时间段内,输出信号可能会发生一次或多次振荡,信号可能会从接近于低电平的电压值迅速跃升到接近于高电平的电压值,或者从接近于高电平的电压值迅速降低到接近于低电平的电压值。该信号经过反相级联单元后,尽管会由两个级联的反相放大器提升信号的抗干扰能力,但也存在着该抖动导致的欠压锁定输出信号的振荡问题。

33.因此,反馈锁定单元,在接收到第一反相放大器的输出后,将其进一步的滞回反馈至分压锁定单元的输出端,从而通过滞回的方式稳定了分压锁定单元的输出端信号,降低

了抖动。

34.反相级联单元则是通过两个反相器级联的方式对信号进行整形,减少抖动的同时放大信号,以为后续电路提供足够的驱动信号。

35.优选地,分压锁定单元包括pmos管和次级电流源;其中,pmos管,基于来自带隙基准源的参考电压和电源电压的比较,实现截止或导通状态;次级电流源,基于其所生成的电压和电源电压的比较,实现分压信号的输出。

36.分压锁定单元中,可以选择合适型号的pmos管和次级电流源,并且将pmos管和次级电流源串联起来,且pmos管的源极接入电源电压,次级电流源的另一端与地电位连接。由于次级电流源生成的次级电压可以较小,因此经过该串联电路后,pmos管的漏极电压也可以实现对电源电压的分压。将该pmos管的漏极电压与后续的反馈锁定单元和反相级联单元依次连接后,可以将该管的漏极电压作为后续单元的输入。

37.优选地,pmos管的栅极与带隙基准源电路连接,接收来自带隙基准源电路的参考电压v

ref

;pmos管的源极与电源电压连接,接收电源电压;pmos管的漏极与次级电流源同时连接到所述锁定单元中。

38.可以理解的是,当pmos管接收到参考电压v

ref

和电源电压后,会基于电源电压v

in

和参考电压v

ref

进行比较。当栅源极电压差大于pmos管的门极开启电压后,pmos管就会导通并在pmos的漏极端生成一个分压电压。

39.优选地,次级电流源,一端接地,另一端与pmos管的漏极、锁定单元的输入端分别连接。

40.具体来说,pmos管与次级电流源之间采用上述的方式实现连接,可以参考欠压锁定电路的具体功能,以及欠压锁定的阈值电压选用合适的pmos管和次级电流源。优选地,次级电流源的输出电流为100na。通常来说,可以将次级电流源的输出电流设计的非常小,只要能够满足电路的分压功能即可。之所以将次级电流源的输出电流设计的非常小,是为了防止该电路消耗过多的无用功耗,从而提高电源的利用效率,节省功耗。

41.优选地,反馈锁定单元包括nmos管;其中,nmos管,基于反相级联单元中第一反相放大器输出的锁定信号实现截止或导通状态,并在处于导通状态时与次级电流源一同拉低来自分压锁定单元的分压信号的电位,以确保欠压锁定输出为闭锁信号;在处于截止时,次级电流源独自拉低分压锁定单元的分压信号的电位,用以设定欠压锁定输出的门限电压。

42.可以理解的是,当分压锁定单元输出的信号为低电平,第一反相放大器的输出为高电平时,nmos管就会导通,这使得nmos管的源漏极与电流源组成了并联电路,并生成并联电流,从而一通将分压锁定单元的分压信号拉至更低的状态。因此,电流源也可以设置的较小,也足够将分压信号拉低到完全满足欠压锁定逻辑中欠压时的门限电压。

43.优选地,nmos管的漏极分别与分压锁定单元的输出端、第一反相放大器的输入端连接;nmos管的栅极分别与第一反相放大器的输出端、第二反相放大器输入端的连接;nmos管的源极接地。

44.具体来说,在本发明中,该nmos管由于其栅极与第一反相放大器的输出端连接,其采集到的电压信号即为第一反相放大器输出的关于分压锁定单元输出端的反相电压信号。也就是说,例如,当分压锁定单元输出的电压为低电平时,第一反相放大器则会输出高电平,nmos管的栅极接收到该高电平时,基于其栅源极之间的高电平实现导通,从而与电流源

实现并联,并一同将来自分压锁定单元的部分电能,通过nmos管的源漏极导出至接地端。通过这种方式,实现了进一步地降低第一反相器的输入端电压,从而确保后续的欠压锁定输出为闭锁信号,能够闭锁下级电路。

45.另一方面,当来自分压锁定单元输出端的电压为高电平时,第一反相器将会输出低电平,或者电压为0v的电平,此时nmos管处于截止状态。此时,只有电流源来拉低来自分压锁定单元的分压信号,从而设定出欠压锁定电路在欠压时候的门限电压,并更好地实现了欠压锁定的逻辑。具体来说,这一门限电压是用于作为开启或闭锁后续电路的门限的。

46.优选地,反相级联单元包括第一反相放大器和第二反相放大器;其中,第一反相放大器和第二反相放大器串联,第一反相放大器的输入端作为反相级联单元的输入端,第二反相放大器的输出端作为反相级联单元的输出端。

47.具体来说,第一反相放大器和第二反相放大器级联组成的反相级联单元,其输出端并不与其输入端的信号状态完全相同。通常来说,通过级联的方式,可以实现对输入端信号的波形整形,同时平衡信号延时,使得通过反相级联单元后输出的欠压锁定电平信号更加符合标准。

48.优选地,当电源电压v

in

与来自带隙基准源的参考电压v

ref

之差大于pmos管的栅源极导通电压时,pmos管处于导通状态;当电源电压v

in

与来自带隙基准源的参考电压v

ref

之差小于pmos管的栅源极导通电压时,pmos管处于截止状态。

49.可以理解的是,电源电压v

in

与来自带隙基准源的参考电压v

ref

之差,也就是pmos管的栅源极之间的电压,当该电压大于pmos管的导通电压时,pmos管就导通,小于则截止。因此,根据电源电压v

in

与来自带隙基准源的参考电压v

ref

之间的大小关系,可以得到pmos管的导通或截止状态,从而进一步地获得分压锁定单元的输出电压的状态。即,当pmos管导通时,分压锁定单元具备输出,当pmos管截止时,分压锁定单元没有输出,从而不会开启后续的反馈锁定单元和反相级联单元。

50.优选地,当分压锁定单元的输出电压大于或等于门限电压时,nmos管截止,反相级联单元输出开启信号;当分压锁定单元的输出电压小于门限电压时,nmos管导通,反相级联单元输出闭锁信号。

51.具体来说,当电源电压v

in

与来自带隙基准源的参考电压v

ref

之间的差距较大,使得pmos导通,仍然能够在pmos管的漏极端产生较大的电压,则此时分压锁定单元的输出端电压就可被确认为大于或等于门限电压的高电平,这导致第一反相放大器输出反相的低电平,nmos管截止,反相级联单元输出较高的电平,通常来说是上文中所述的门限电压,即不会闭锁后续电路。

52.另一方面,当电源电压v

in

与来自带隙基准源的参考电压v

ref

之间的差距较小,这使得pmos管导通后,其漏极电压较低接近于0电位,此时反相级联单元将输入识别为低电平,经过第一反相放大器后,nmos管导通,进一步地将分压锁定单元输出端的电压拉低至较低的状态,甚至是0电位。容易理解的是,当分压锁定单元输出端的电压低于欠压锁定输出的门限电压时候,反相级联单元的输出端电压则为低或0v的闭锁信号,因此,反相级联单元能够准确的输出闭锁信号,从而闭锁后续的电路功能。通过上述电路,本发明实现了准确的欠压锁定功能。

53.本发明的有益效果在于,与现有技术相比,本发明中的一种欠压锁定电路,能够通

过pmos管和次级电流源实现对电源电压的分压,从而替代了现有技术中耗费芯片版图和电源功率的分压电阻。因此,本发明中的方法能够实现且适用于功耗低、面积小的芯片,从而扩大了uvlo电路的利用范围。

54.本发明申请人结合说明书附图对本发明的实施示例做了详细的说明与描述,但是本领域技术人员应该理解,以上实施示例仅为本发明的优选实施方案,详尽的说明只是为了帮助读者更好地理解本发明精神,而并非对本发明保护范围的限制,相反,任何基于本发明的发明精神所作的任何改进或修饰都应当落在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。