1.本发明属于微电子技术领域,具体涉及一种增强型氧化镓功率晶体管及制作方法。

背景技术:

2.由于β-ga2o3材料具有超宽的禁带宽度及较高的击穿场强,因此,利用β-ga2o3所制作的功率器件具有高耐压、大功率的特点,具备在电力电子领域应用的潜力,近些年来,吸引了众多学者对β-ga2o3晶体材料及功率器件进行研究。

3.但是由于氧化镓材料较难形成p型掺杂,严重地制约了氧化镓基增强型器件的实现。同时,由于材料层中的非故意掺杂(unintentionally doped,uid)层中通常具有杂质离子,在器件实际工作中,杂质离子有很大机率渗入到沟道层中,造成器件沟道电子迁移率和电流密度的降低。因此,提升氧化镓增强型功率晶体管的器件电流密度和迁移率是非常有必要的。

技术实现要素:

4.为了解决现有技术中存在的上述问题,本发明提供了一种增强型氧化镓功率晶体管及制作方法。本发明要解决的技术问题通过以下技术方案实现:

5.本发明实施例提供了一种增强型氧化镓功率晶体管,包括:β-ga2o3衬底、β-ga2o3非故意掺杂层、p型niox缓冲层、n型β-ga2o3沟道层、p型niox帽层、源电极、漏电极和栅电极,其中,

6.所述β-ga2o3衬底、所述β-ga2o3非故意掺杂层、所述p型niox缓冲层、所述n型β-ga2o3沟道层依次层叠;

7.所述源电极位于所述n型β-ga2o3沟道层的一端,所述漏电极位于所述n型β-ga2o3沟道层的另一端;

8.所述p型niox帽层位于所述n型β-ga2o3沟道层上,且位于所述源电极和所述漏电极之间;

9.所述栅电极位于所述p型niox帽层上。

10.在本发明的一个实施例中,所述β-ga2o3衬底的掺杂元素包括fe。

11.在本发明的一个实施例中,所述β-ga2o3非故意掺杂层的厚度为100~500nm,载流子浓度为1

×

10

14

cm-3

~1

×

10

16

cm-3

。

12.在本发明的一个实施例中,所述p型niox缓冲层的厚度为50~150nm,p型掺杂浓度为1

×

10

14

cm-3

~1

×

10

18

cm-3

。

13.在本发明的一个实施例中,所述n型β-ga2o3沟道层的厚度为200~600nm,掺杂浓度为1

×

10

17

cm-3

~1

×

10

19

cm-3

。

14.在本发明的一个实施例中,所述p型niox帽层的厚度为50~150nm,p型掺杂浓度为1

×

10

14

cm-3

~1

×

10

18

cm-3

。

15.本发明的另一个实施例提供了一种增强型氧化镓功率晶体管的制作方法,包括步骤:

16.在β-ga2o3衬底上生长β-ga2o3非故意掺杂层;

17.在所述β-ga2o3非故意掺杂层上生长p型niox缓冲层;

18.在所述p型niox缓冲层上生长n型β-ga2o3沟道层;

19.在所述n型β-ga2o3沟道层上生长p型niox材料,并选择性刻蚀栅区域外的p型niox材料,露出所述n型β-ga2o3沟道层,形成p型niox帽层;

20.在所述n型β-ga2o3沟道层上制备源电极和漏电极,使得所述源电极位于所述n型β-ga2o3沟道层的一端,所述漏电极位于所述n型β-ga2o3沟道层的另一端,且所述p型niox帽层位于所述源电极和所述漏电极之间;

21.在所述p型niox帽层上制备栅电极。

22.在本发明的一个实施例中,所述β-ga2o3非故意掺杂层的厚度为100~500nm,载流子浓度为1

×

10

14

cm-3

~1

×

10

16

cm-3

。

23.在本发明的一个实施例中,所述p型niox缓冲层的厚度为50~150nm,p型掺杂浓度为1

×

10

14

cm-3

~1

×

10

18

cm-3

。

24.在本发明的一个实施例中,所述n型β-ga2o3沟道层的厚度为200~600nm,掺杂浓度为1

×

10

17

cm-3

~1

×

10

19

cm-3

。

25.与现有技术相比,本发明的有益效果:

26.1、本发明的增强型氧化镓功率晶体管中p型niox缓冲层与上层的n型β-ga2o3沟道层之间形成pn结,可以阻止β-ga2o3非故意掺杂层中的杂质离子渗入沟道层,减小了渗入沟道层中的杂质离子的补偿作用,提升了沟道层电子迁移率,同时提升了沟道层中的电子浓度,提升了器件电流密度。

27.2、本发明通过引入p型niox帽层,使得器件阈值电压的正移,实现了增强型器件,解决了目前耗尽型氧化镓功率晶体管阈值电压过负的问题。

附图说明

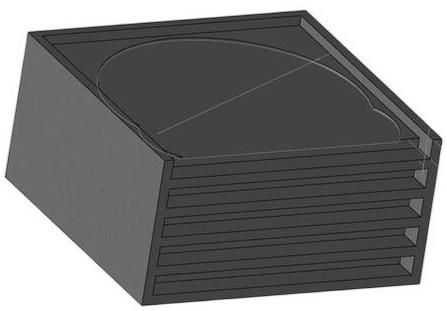

28.图1为本发明实施例提供的一种增强型氧化镓功率晶体管的结构示意图;

29.图2a-图2g为本发明实施例提供的一种增强型氧化镓功率晶体管的制作方法的过程示意图。

具体实施方式

30.下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

31.实施例一

32.请参见图1,图1为本发明实施例提供的一种增强型氧化镓功率晶体管的结构示意图。

33.该增强型氧化镓功率晶体管包括:β-ga2o3衬底1、β-ga2o3非故意掺杂层2、p型niox缓冲层3、n型β-ga2o3沟道层4、p型niox帽层5、源电极6、漏电极7和栅电极8。其中,β-ga2o3衬底1、β-ga2o3非故意掺杂层2、p型niox缓冲层3、n型β-ga2o3沟道层4依次层叠;源电极6位于n

型β-ga2o3沟道层4的一端,漏电极7位于n型β-ga2o3沟道层4的另一端;p型niox帽层5位于n型β-ga2o3沟道层4上,且位于源电极6和漏电极7之间;栅电极8位于p型niox帽层5上。

34.具体的,p型niox缓冲层3的禁带宽度约为3.7ev,ga2o3的禁带宽度约为4.8ev,二者禁带宽度相近,可以保证异质结的带差较小,不容易形成势阱。

35.具体的,p型niox帽层5、源电极6、漏电极7均位于n型β-ga2o3沟道层4上,p型niox帽层5位于n型β-ga2o3沟道层4的中间,源电极6位于n型β-ga2o3沟道层4的一端,漏电极7位于n型β-ga2o3沟道层4的另一端,且p型niox帽层5与源电极6、漏电极7之间均不接触。

36.在一个具体实施例中,β-ga2o3衬底1的掺杂元素包括fe,其晶向可以为(010)晶向,也可以为(100)晶向,本实施例不做进一步限制。β-ga2o3非故意掺杂层2的厚度为100~500nm,载流子浓度为1

×

10

14

cm-3

~1

×

10

16

cm-3

。p型niox缓冲层3的厚度为50~150nm,p型掺杂浓度为1

×

10

14

cm-3

~1

×

10

18

cm-3

。n型β-ga2o3沟道层4的厚度为200~600nm,掺杂浓度为1

×

10

17

cm-3

~1

×

10

19

cm-3

。p型niox帽层5的厚度为50~150nm,p型掺杂浓度为1

×

10

14

cm-3

~1

×

10

18

cm-3

。源电极6和漏电极7的材料包括ti、au中的一种或多种,栅电极的材料包括ni、au中的一种或多种。

37.本实施例中,可以形成p型的掺杂元素均可用于p型niox缓冲层3和p型niox帽层5的掺杂,可以形成n型的掺杂元素均可用于n型β-ga2o3沟道层4的掺杂。

38.本实施例的增强型氧化镓功率晶体管中p型niox缓冲层与上层的n型β-ga2o3沟道层之间形成pn结,可以阻止β-ga2o3非故意掺杂层中的杂质离子渗入沟道层,减小了渗入沟道层中的杂质离子的补偿作用,提升了沟道层电子迁移率,同时提升了沟道层中的电子浓度,提升了器件电流密度。

39.本实施例通过引入p型niox帽层,使得器件阈值电压的正移,实现了增强型器件,解决了目前耗尽型氧化镓功率晶体管阈值电压过负的问题。

40.实施例二

41.在实施例一的基础上,本实施例对增强型氧化镓功率晶体管的制作方法进行说明。

42.请参见图2a-图2g,图2a-图2g为本发明实施例提供的一种增强型氧化镓功率晶体管的制作方法的过程示意图。该制作方法包括步骤:

43.s1、在β-ga2o3衬底1上生长β-ga2o3非故意掺杂层2,请参见图2a。

44.具体的,在fe掺杂的(010)晶向的β-ga2o3衬底1上生长一层β-ga2o3非故意掺杂(uid)层,厚度为100~500nm,载流子浓度控制在1

×

10

14

cm-3

~1

×

10

16

cm-3

。

45.s2、在β-ga2o3非故意掺杂层2上生长p型niox缓冲层3,请参见图2b,其中,p型niox缓冲层3的禁带宽度与ga2o3的禁带宽度相近。

46.具体的,在β-ga2o3非故意掺杂层2上方沉积50~150nm的p型niox材料,p型niox材料的禁带宽度与ga2o3的禁带宽度相近,p型niox材料的掺杂浓度为1

×

10

14

cm-3

~1

×

10

18

cm-3

,得到p型niox缓冲层3。

47.s3、在p型niox缓冲层3上生长n型β-ga2o3沟道层4,请参见图2c。

48.具体的,在p型niox缓冲层3上方生长一层n掺杂的β-ga2o3材料作为n型β-ga2o3沟道层4,沟道层厚度为200~600nm,掺杂浓度为1

×

10

17

cm-3

~1

×

10

19

cm-3

。

49.s4、在n型β-ga2o3沟道层4上生长p型niox材料,请参见图2d,并选择性刻蚀栅区域

外的p型niox材料,露出n型β-ga2o3沟道层4,形成p型niox帽层5,请参见图2e。

50.具体的,在n型β-ga2o3沟道层4上生长50~150nm厚的p型niox材料,p型niox材料的掺杂浓度为1

×

10

14

cm-3

~1

×

10

18

cm-3

,然后选择性刻蚀栅区域外的p型niox材料,刻蚀深度为50~150nm,露出n型β-ga2o3沟道层4,形成位于n型β-ga2o3沟道层4中间位置的p型niox帽层5。

51.s5、在n型β-ga2o3沟道层4上制备源电极6和漏电极7,使得源电极6位于n型β-ga2o3沟道层4的一端,漏电极7位于n型β-ga2o3沟道层4的另一端,且p型niox帽层5位于源电极6和漏电极7之间,请参见图2f。

52.具体的,在刻蚀露出的n型β-ga2o3沟道层4上沉积ti/au金属叠层后进行退火形成欧姆接触,得到源电极6和漏电极7,其中,源电极6位于n型β-ga2o3沟道层4的一端,漏电极7位于n型β-ga2o3沟道层4的另一端,且p型niox帽层5位于源电极6和漏电极7之间。

53.s6、在p型niox帽层5上制备栅电极8,请参见图2g。

54.具体的,在p型niox帽层5上方沉积ni/au金属叠层形成栅电极8,得到增强型氧化镓功率晶体管。

55.本实施例的增强型氧化镓功率晶体管的制作方法制造工艺简单可控,与现有工艺兼容,制作成本较低。

56.实施例三

57.在实施例二的基础上,请结合图2a-图2g,本实施例以制备200nm厚的增强型氧化镓功率晶体管为例进行说明。

58.该增强型氧化镓功率晶体管的制作方法包括步骤:

59.s1、在β-ga2o3衬底1上生长β-ga2o3非故意掺杂层2,请参见图2a。

60.具体的,在fe掺杂的(010)晶向的β-ga2o3衬底1上生长一层β-ga2o3非故意掺杂层2,厚度为100nm,载流子浓度为1

×

10

14

cm-3

。

61.s2、在β-ga2o3非故意掺杂层2上生长p型niox缓冲层3,请参见图2b。

62.具体的,在β-ga2o3非故意掺杂层2上方溅射一层p型niox缓冲层3,厚度为50nm,掺杂浓度为1

×

10

14

cm-3

。

63.s3、在p型niox缓冲层3上生长n型β-ga2o3沟道层4,请参见图2c。

64.具体的,在p型niox缓冲层3上生长一层n型β-ga2o3沟道层4,厚度为200nm,掺杂浓度为1

×

10

17

cm-3

。

65.s4、在n型β-ga2o3沟道层4上制备p型niox帽层5,请参见图2d。

66.具体的,在n型β-ga2o3沟道层4上生长50nm厚的p型niox材料,p型niox材料的掺杂浓度为1

×

10

14

cm-3

,然后选择性刻蚀栅区域外的p型niox材料,刻蚀深度为50nm,露出n型β-ga2o3沟道层4,形成位于n型β-ga2o3沟道层4中间位置的p型niox帽层5。

67.s5、在n型β-ga2o3沟道层4上制备源电极6和漏电极7,请参见图2f。

68.具体的,在刻蚀露出的n型β-ga2o3沟道层4上沉积ti/au金属叠层,厚度分别为20/200nm,然后进行快速热退火,对欧姆金属进行合金化,得到源电极6和漏电极7,其中,源电极6位于n型β-ga2o3沟道层4的一端,漏电极7位于n型β-ga2o3沟道层4的另一端,且p型niox帽层5位于源电极6和漏电极7之间。

69.s6、在p型niox帽层5上制备栅电极8,请参见图2g。

70.具体的,在p型niox帽层5上方蒸镀ni/au金属叠层,厚度分别为45/400nm,得到栅电极8。

71.之后,在器件表面沉积互联金属并引出电极,完成增强型氧化镓功率晶体管的制作。

72.实施例四

73.在实施例二的基础上,请结合图2a-图2g,本实施例以制备400nm厚的增强型氧化镓功率晶体管为例进行说明。

74.该增强型氧化镓功率晶体管的制作方法包括步骤:

75.s1、在β-ga2o3衬底1上生长β-ga2o3非故意掺杂层2,请参见图2a。

76.具体的,在fe掺杂的(010)晶向的β-ga2o3衬底1上生长一层β-ga2o3非故意掺杂层2,厚度为300nm,载流子浓度为1

×

10

15

cm-3

。

77.s2、在β-ga2o3非故意掺杂层2上生长p型niox缓冲层3,请参见图2b。

78.具体的,在β-ga2o3非故意掺杂层2上方溅射一层p型niox缓冲层3,厚度为100nm,掺杂浓度为1

×

10

16

cm-3

。

79.s3、在p型niox缓冲层3上生长n型β-ga2o3沟道层4,请参见图2c。

80.具体的,在p型niox缓冲层3上生长n型β-ga2o3沟道层4,厚度为400nm,掺杂浓度为1

×

10

18

cm-3

。

81.s4、在n型β-ga2o3沟道层4上制备p型niox帽层5,请参见图2d。

82.具体的,在n型β-ga2o3沟道层4上溅射100nm厚的p型niox材料,p型niox材料的掺杂浓度为1

×

10

16

cm-3

,然后选择性刻蚀栅区域外的p型niox材料,刻蚀深度为100nm,露出n型β-ga2o3沟道层4,形成位于n型β-ga2o3沟道层4中间位置的p型niox帽层5。

83.s5、在n型β-ga2o3沟道层4上制备源电极6和漏电极7,请参见图2f。

84.具体的,在刻蚀露出的n型β-ga2o3沟道层4上沉积ti/au金属叠层,厚度分别为20/200nm,然后进行快速热退火,对欧姆金属进行合金化,得到源电极6和漏电极7,其中,源电极6位于n型β-ga2o3沟道层4的一端,漏电极7位于n型β-ga2o3沟道层4的另一端,且p型niox帽层5位于源电极6和漏电极7之间。

85.s6、在p型niox帽层5上制备栅电极8,请参见图2g。

86.具体的,在p型niox帽层5上方蒸镀ni/au金属叠层,厚度分别为45/400nm,得到栅电极8。

87.之后,在器件表面沉积互联金属并引出电极,完成增强型氧化镓功率晶体管的制作。

88.实施例五

89.在实施例二的基础上,请结合图2a-图2g,本实施例以制备600nm厚的增强型氧化镓功率晶体管为例进行说明。

90.s1、在β-ga2o3衬底1上生长β-ga2o3非故意掺杂层2,请参见图2a。

91.具体的,在fe掺杂的(010)晶向的β-ga2o3衬底1上生长一层β-ga2o3非故意掺杂层2,厚度为500nm,载流子浓度为1

×

10

16

cm-3

。

92.s2、在β-ga2o3非故意掺杂层2上生长p型niox缓冲层3,请参见图2b。

93.具体的,在β-ga2o3非故意掺杂层2上方溅射一层p型niox缓冲层3,厚度为150nm,掺

杂浓度为1

×

10

18

cm-3

。

94.s3、在p型niox缓冲层3上生长n型β-ga2o3沟道层4,请参见图2c。

95.具体的,在p型niox缓冲层3上生长一层n型β-ga2o3沟道层4,厚度为600nm,掺杂浓度为1

×

10

19

cm-3

。

96.s4、在n型β-ga2o3沟道层4上制备p型niox帽层5,请参见图2d。

97.具体的,在n型β-ga2o3沟道层4上生长150nm厚的p型niox材料,p型niox材料的掺杂浓度为1

×

10

18

cm-3

,然后选择性刻蚀栅区域外的p型niox材料,刻蚀深度为150nm,露出n型β-ga2o3沟道层4,形成位于n型β-ga2o3沟道层4中间位置的p型niox帽层5。

98.s5、在n型β-ga2o3沟道层4上制备源电极6和漏电极7,请参见图2f。

99.具体的,在刻蚀露出的n型β-ga2o3沟道层4上沉积ti/au金属叠层,厚度分别为20/200nm,然后进行快速热退火,对欧姆金属进行合金化,得到源电极6和漏电极7,其中,源电极6位于n型β-ga2o3沟道层4的一端,漏电极7位于n型β-ga2o3沟道层4的另一端,且p型niox帽层5位于源电极6和漏电极7之间。

100.s6、在p型niox帽层5上制备栅电极8,请参见图2g。

101.具体的,在p型niox帽层5上方蒸镀ni/au金属叠层,厚度分别为45/400nm,得到栅电极8。

102.之后,在器件表面沉积互联金属并引出电极,完成增强型氧化镓功率晶体管的制作。

103.以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。