技术特征:

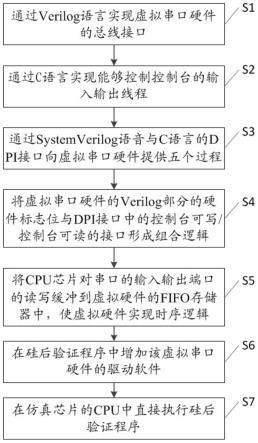

1.一种利用cpu和虚拟串口硬件实现交互仿真环境的芯片验证方法,其特征在于,包括:步骤s1:通过verilog语言实现虚拟串口硬件的总线接口;步骤s2:通过c语言实现能够控制控制台的输入输出线程,该输入输出线程为不同于芯片仿真过程而独立存在的线程;步骤s3:通过systemverilog语音与c语言的dpi接口向虚拟串口硬件提供以下五个过程:初始化、控制台可读、控制台可写、写控制台及读控制台;步骤s4:将虚拟串口硬件的verilog部分的硬件标志位与dpi接口中的控制台可写/控制台可读的接口形成组合逻辑;步骤s5:将cpu芯片对串口的输入输出端口的读写缓冲到虚拟硬件的fifo存储器中,使虚拟硬件实现时序逻辑,用以通过调用读控制台/写控制台的接口完成控制台的输入输出;步骤s6:在硅后验证程序中增加该虚拟串口硬件的驱动软件;步骤s7:在仿真芯片的cpu中直接执行硅后验证程序。2.根据权利要求1所述的利用cpu和虚拟串口硬件实现交互仿真环境的芯片验证方法,其特征在于,步骤s1中虚拟串口硬件的串口标准包括8250或者pl01x。3.根据权利要求1所述的利用cpu和虚拟串口硬件实现交互仿真环境的芯片验证方法,其特征在于,步骤s3中每个过程都实现为基于verilog语音的dpi-c接口的任务。

技术总结

本发明公开一种利用CPU和虚拟串口硬件实现交互仿真环境的芯片验证方法,其包括:S1:通过Verilog语言实现虚拟串口硬件的总线接口;S2:通过C语言实现能够控制控制台的输入输出线程;S3:通过SystemVerilog语音与C语言的DPI接口向虚拟串口硬件提供五个过程;S4:将虚拟串口硬件的Verilog部分的硬件标志位与DPI接口中的控制台可写/控制台可读的接口形成组合逻辑;S5:将CPU芯片对串口的输入输出端口的读写缓冲到虚拟硬件的FIFO存储器中,使虚拟硬件实现时序逻辑;S6:在硅后验证程序中增加该虚拟串口硬件的驱动软件;S7:在仿真芯片的CPU中直接执行硅后验证程序。直接执行硅后验证程序。直接执行硅后验证程序。

技术研发人员:郑律 范东睿

受保护的技术使用者:苏州睿芯集成电路科技有限公司

技术研发日:2022.09.16

技术公布日:2022/12/16

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。